### **Intelligent Frequency Synthesizers**

### **Preliminary Data Sheet**

# PNP-1050-L22

### **FEATURES:**

- \* 1000-1100 MHz Frequency Range

- \* Programmable Step Size

- Low Integrated Phase Noise

- Simplified Programming

#### **APPLICATIONS:**

- Wireless Infrastructure

- Test Equipment

- Wireless LAN

MICROWIRE is a trademark of National Semiconductor Corp. SPI is a trademark of Motorola, Inc.  $I^2C$  is a trademark of Philips Corp.

#### DESCRIPTION:

The PNP-1050-L22 is a complete low noise frequency synthesizer, comprised of VCO, PLL, loop filter and data interface. The PNP family of RF signal sources is the world's first truly configurable frequency synthesizer module. PNP technology offers the designer the ability to configure all of the synthesizer's vital functions 'on the fly' with simple strings of code that contain the commands of START, STOP, STEP, CHANNEL and REF. When new data is received, the PNP module optimizes its internal settings for best overall integrated phase noise, switching speed and spurious suppression, all automatically and in less than 100  $\mu$ S. Therefore, if the system requires 100 kHz steps in mode #1 and 1 MHz step size in mode #2, these smart synthesizers can make quick adjustments with amazing accuracy, speed and performance.

Control of the internal registers is accomplished through a serial data interface. Many industry standard protocols are supported, including  $I^2C$ , SPI, and MICROWIRE Serial Interfaces. The PNP-1050-L22 is powered from a +3V and +5V supply while dissipating less than 175 mW.

Universal Microwave Corporation, 2339 Destiny Way, Odessa, FL 33556 UMC Worldwide Customer Support Center: 4703 S. Lakeshore Drive, Suite 2, Tempe, AZ 85282 1.877.UMC.Xtreme / Fax 480.756.6026

# **PNP-1050-L22 Specifications**

V1 = +5.0, V2 = +3.0V, REF = 20 MHz, -40 to +85C

| Parameter                                           | Min                  | Тур  | Max              | Units  |

|-----------------------------------------------------|----------------------|------|------------------|--------|

| RF OUT Characteristics                              |                      |      |                  |        |

| Frequency Range                                     | 1000                 |      | 1100             | MHz    |

| Output Power                                        | -2                   | 0    | +2               | dBm    |

| Harmonics                                           |                      | -18  | -12              | dBc    |

| Noise Characteristics                               |                      |      |                  |        |

| 1 kHz offset $arnothing$ Noise                      |                      | -93  | -88              | dBc/Hz |

| 10 kHz offset $arnothing$ Noise                     |                      | -108 | -103             | dBc/Hz |

| 100 kHz offset Ø Noise                              |                      | -130 | -125             | dBc/Hz |

| 1 MHz offset Ø Noise                                |                      | -150 | -145             | dBc/Hz |

| Spurious Signals                                    |                      |      |                  |        |

| STEP = 62.5 kHz                                     |                      | -70  | -55 <sup>1</sup> | dBc    |

| STEP = 250 kHz                                      |                      | -70  | -60 <sup>1</sup> | dBc    |

| STEP = 10 MHz                                       |                      | -80  | -70              | dBc    |

| REF Feed-through                                    |                      | -80  | -70              | dBc    |

| <b>REF IN Characteristics</b>                       |                      |      |                  |        |

| REF Input Frequency                                 | 10                   | 20   | 250              | MHz    |

| REF Input Sensitivity <sup>2</sup>                  | -5                   | 0    | +5               | dBm    |

| REF Input Current                                   |                      |      | +/-100           | μA     |

| Logic Inputs                                        |                      |      |                  |        |

| V <sub>INH</sub> , Input High Voltage               | 1.35                 |      |                  | Vdc    |

| V <sub>INL</sub> , Input Low Voltage                |                      |      | 0.6              | Vdc    |

| I <sub>INH</sub> , I <sub>INL</sub> , Input Current |                      |      | +/- 1            | μA     |

| C <sub>IN</sub> , Input Capacitance                 |                      |      | 10               | pF     |

| Logic Outputs                                       |                      |      |                  |        |

| V <sub>OH</sub> , Output High Voltage               | V <sub>2</sub> - 0.4 |      |                  | Vdc    |

| V <sub>OL</sub> , Output Low Voltage                |                      |      | 0.4              | Vdc    |

| I <sub>OH</sub> , I <sub>OL</sub> , Output Current  |                      |      | 500              | μA     |

| Power Supplies                                      |                      |      |                  |        |

| Supply Voltage, V <sub>1</sub>                      | 4.9                  | 5.0  | 5.1              | Vdc    |

| Supply Voltage, V <sub>2</sub>                      | 2.7                  | 3.0  | 3.3              | Vdc    |

| Supply Current, I <sub>1</sub>                      |                      | 35   | 40               | mA     |

| Supply Current, I <sub>2</sub>                      |                      | 25   | 35               | mA     |

NOTES:

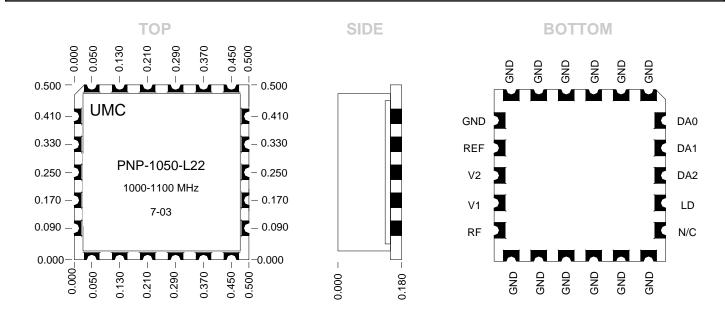

### **Pin Descriptions**

| Mnemonic | FUNCTION                                                                                                                                                                                                                   |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RF       | RF Output. This pin is AC coupled and should be connected to a non-reflective 50 ohm load.                                                                                                                                 |

| V1       | Supply Input. Decoupling capacitors to the ground plane should be placed as close as possible to this pin.                                                                                                                 |

| V2       | Supply Input. Decoupling capacitors to the ground plane should be placed as close as possible to this pin.                                                                                                                 |

| REF      | Reference Input. This is a CMOS input with a nominal threshold of $V_2/2$ and a dc equivalent input resistance of 100K ohms. This input can be driven from a CMOS or TTL crystal clock oscillator or it can be ac coupled. |

| GND      | Digital, Analog and RF Ground.                                                                                                                                                                                             |

| DA0      | Serial Interface. This input functions as $\overline{CS}$ in MICROWIRE/SPI Bus mode. This input functions as <b>SDA</b> in I <sup>2</sup> C BUS mode.                                                                      |

| DA1      | Serial Interface. This input functions as <b>DATA</b> in MICROWIRE/SPI BUS mode. This input functions as <b>SCL</b> in I <sup>2</sup> C BUS mode.                                                                          |

| DA2      | Serial Interface. This input functions as <b>CLOCK</b> in MICROWIRE/SPI BUS mode. This input must be connected to the <b>GROUND</b> in $I^2C$ BUS mode.                                                                    |

| LD       | Lock Detect. This output is active high and provides a continuous digital lock status.                                                                                                                                     |

### **Absolute Maximum Ratings**

| V1 to Ground          | -0.3 to +5.5 V <sub>dc</sub>                     |  |  |

|-----------------------|--------------------------------------------------|--|--|

| V2 to Ground          | -0.3 to +3.6 V <sub>dc</sub>                     |  |  |

| REF IN to Ground      | -0.3 to (D <sub>vdd</sub> + 0.3) V <sub>dc</sub> |  |  |

| RF OUT to Ground      | +/- 25 V <sub>dc</sub>                           |  |  |

| Digital I/O to Ground | -0.3 to V <sub>2</sub> + 0.3 V <sub>dc</sub>     |  |  |

| Operating Temperature | -40° to +85°C  |

|-----------------------|----------------|

| Storage Temperature   | -55° to +100°C |

Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only. Operation of the device above the conditions listed in the operational sections of this specification is not implied.

## **Ordering Guide**

# PNP-1050-L22

| Model         | I <sup>2</sup> C Address | Type Code |

|---------------|--------------------------|-----------|

| PNP-1050-L22  | Default                  | P001      |

| PNP-1050A-L22 | Default + 1              | P001      |

| PNP-1050B-L22 | Default + 2              | P001      |

| PNP-1050C-L22 | Default + 3              | P001      |

#### CAUTION!

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000V readily accumulate on the human body and test equipment and can discharge without detection. Although the PNP family of synthesizers feature ESD protection circuitry, permanent damage may occur on devices subjected to highenergy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality

### **Digital Interface**

#### Overview

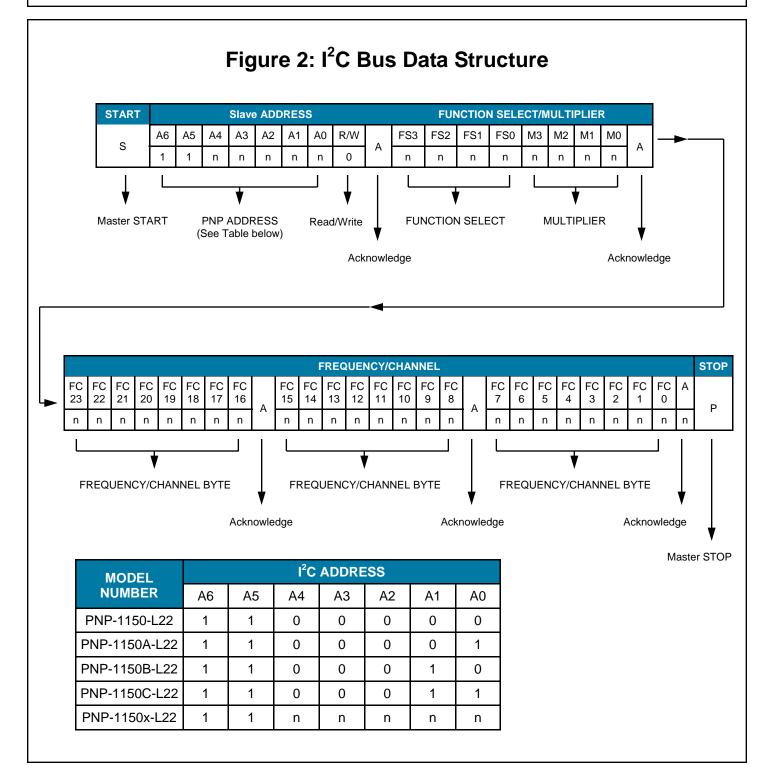

The PNP family of intelligent Frequency Synthesizers can be controlled through the use of a microprocessor interface or Bus. Several protocols are supported by PNP devices, although this specification will focus on SPI Bus, MICROWIRE-Interface and I<sup>2</sup>C Bus implementations. For SPI and MICROWIRE applications, PNP devices require a single 32 bit string of serial data to set frequency or to change its internal settings (Figure 1). I<sup>2</sup>C Bus utilizes some unique control bits and requires the addition of an ADDRESS byte, increasing the serial bit-stream for this protocol to 47 bits per command (Figure 2).

The PNP device is programmed at the factory with presets for the START, STOP, STEP and REFERENCE registers. It is not necessary to re-load any of these registers if the factory values are acceptable. If the application requires different values than the factory pre-sets, then the PNP device must first be initialized by loading data into each of the affected registers. It is not necessary to re-load any registers that are already set properly for the application. START defines the lowest desired frequency of operation. STOP defines the highest desired frequency of operation. STEP is used to channelize the band and REFERENCE defines the frequency of the external reference. Once the PNP device is initialized, a fixed number channels are available. Loading the CHAN-NEL register sets the operating frequency of the PNP device. The formula for calculating the operating frequency is:

START(Hz) + (CHANNEL \* STEP(Hz)) = Frequency(Hz)

#### **MICROWIRE Interface and SPI Bus**

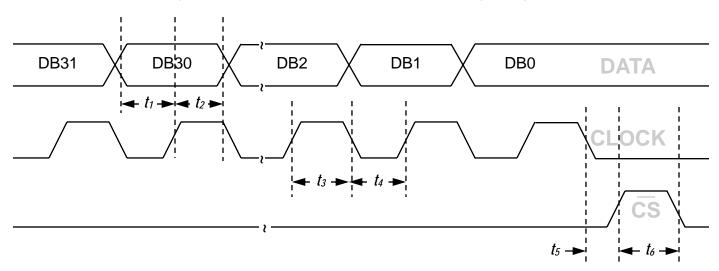

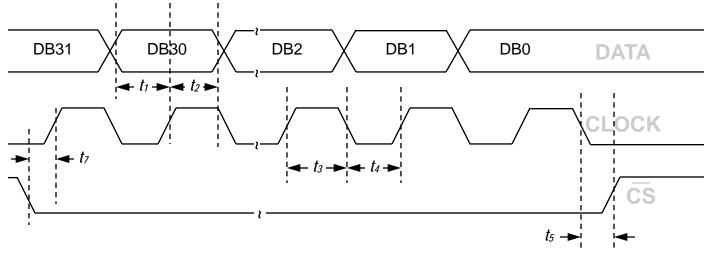

MICROWIRE-Interface and SPI Bus are extremely similar protocols (Figures 6 & 7). DATA bits are clocked into the PNP device on the rising edge of the CLOCK input.  $\overline{CS}$ , or chip select not, must be in a low state for the incoming DATA bits to be accepted. After all 32 bits have been clocked in, the  $\overline{CS}$  line must transition high for the DATA string to be latched. After the string is latched, the information in the FUNCTION block (Figure 5) determines where the data will be routed internally.

#### I<sup>2</sup>C Bus

The I<sup>2</sup>C Bus is a high-speed method of communicating over a two wire interface. PNP modules are configured as "slaves" or receive-only devices and can only listen for commands from the "master" which is typically a micro-processor. The I<sup>2</sup>C two wire Bus consists of SDA (serial data) and SCL (serial clock) lines. In order to use the I<sup>2</sup>C

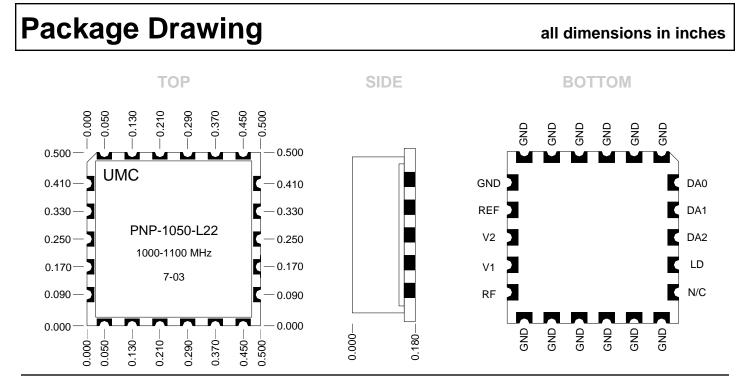

Bus for control of the PNP synthesizer module, the DA2 line (see Package Drawing, Page 1) must be tied to Digital Ground. Additionally, the SDA and SCL lines must be pulled up to  $D_{vdd}$  using external resistors. Multiple PNP devices can reside on the same two wire Bus without the danger of corrupted data or data collisions. Device selection is accomplished by sending a slave address preceding each string of data. If only one PNP device will be used on the I<sup>2</sup>C Bus, then the factory pre-set base address will operate properly. If more than one PNP device will reside on the same I<sup>2</sup>C Bus, then modules with unique address locations must be used. This should be specified when ordering (see Ordering Guide on page 3). For additional information refer to the I<sup>2</sup>C Bus specification (copyright Philips Corp).

#### I<sup>2</sup>C Implementation

Transferring data to PNP synthesizers using I<sup>2</sup>C protocol varies significantly from that of SPI or MICROWIRE. PNP modules operate as slaves on the I<sup>2</sup>C Bus and do not write to the Bus. However, due to the fact that many devices might reside on the same Bus, addressing must be used to direct the flow of data traffic. So, within the bit stream sent to the PNP device, there is a block of data that comprises the ADDRESS byte. Within this address byte there are 7 bits that are used for the address location and the eighth is used as a read/write (R/W) bit. Since PNPs are slaves and will never write to the I<sup>2</sup>C Bus, this bit will always be set to 0 (logic low).

Each data string is sent using a series of five single byte blocks.  $I^2C$  protocol requires that each string of data begin with a master generated START (S). Each byte within the string must end with a slave generated AC-KNOWLEDGE (A). Finally, after all five bytes are generated, the transfer is concluded with a master generated STOP (P). The master generated STOP must be executed following each data string for the values to be accepted by the PNP device. If this condition is not satisfied and a new master generated START occurs, the PNP device will purge the previous data without updating the desired attribute. REPEATED START (S<sub>r</sub>) operation is not allowed when sending data to the PNP device.

The flow of data bytes to the PNP device is outlined in Figure 2. Since FUNCTION SELECT and MULTIPLIER are 4 bits each, these blocks of data are combined into one byte. Additionally, since the FREQUENCY/ CHANNEL block of data is 24 bits long, it must be fragmented into three individual bytes as shown. FIGURE 2: **FREQUENCY/CHANNEL** (DB0 - DB23) This is a 24 bit string used to set the synthesizer's START Frequency, STOP Frequency, STEP Frequency, REF Frequency or CHANNEL number.

| <b>DB23</b> | DBn | DB3 | DB2 | DB1 | DB0 |                   |

|-------------|-----|-----|-----|-----|-----|-------------------|

| FC23        | FCn | FC3 | FC2 | FC1 | FC0 | FREQUENCY/CHANNEL |

| 0           | 0   | 0   | 0   | 0   | 0   | 0                 |

| 0           | 0   | 0   | 0   | 0   | 1   | 1                 |

| 0           | 0   | 0   | 0   | 1   | 0   | 2                 |

| 0           | 0   | 0   | 0   | 1   | 1   | 3                 |

| 0           | 0   | 1   | 1   | 1   | 1   | 15                |

FIGURE 3: **MULTIPLIER** (DB24 - DB27) The data in **FREQUENCY/CHANNEL** (DB0-DB23) is multiplied by 10<sup>n</sup> where the value of n is determined by the contents of **MULTIPLIER** (DB24-DB27) as shown below.

| DB27 | <b>DB26</b> | DB25 | DB24 |                                        |

|------|-------------|------|------|----------------------------------------|

| М3   | M2          | M1   | MO   | MULTIPLIER                             |

| 0    | 0           | 0    | 0    | 10 <sup>0</sup> X contents of DB0-DB23 |

| 0    | 0           | 0    | 1    | 10 <sup>1</sup> X contents of DB0-DB23 |

| 0    | 0           | 1    | 0    | 10 <sup>2</sup> X contents of DB0-DB23 |

| 0    | 0           | 1    | 1    | 10 <sup>3</sup> X contents of DB0-DB23 |

| n    | n           | n    | n    | 10 <sup>n</sup> X contents of DB0-DB23 |

FIGURE 4: **FUNCTION SELECT** (DB28 - DB31). After the data in **FREQUENCY/CHANNEL** (DB0 - DB23) is multiplied by 10<sup>n</sup> where the value of n is determined by the contents of **MULTIPLIER** (Figure 3), it is then routed internally to the START, STOP, STEP, REF or CHANNEL registers based on the contents of **FUNC-TION SELECT** as shown below.

| DB31    | DB30                                                                          | DB29  | DB28     |                                                                |  |  |  |

|---------|-------------------------------------------------------------------------------|-------|----------|----------------------------------------------------------------|--|--|--|

| FS3     | FS2                                                                           | FS1   | FS0      | FUNCTION SELECT                                                |  |  |  |

| 0       | 0                                                                             | 0     | 0        | CHANNEL. Routes data from DB0-DB23 to the CHANNEL REGISTER.    |  |  |  |

| 0       | 0                                                                             | 0     | 1        | START. Routes data from DB0-DB23 to the <b>START REGISTER.</b> |  |  |  |

| 0       | 0 0 1 0 STOP. Routes data from DB0-DB23 to the <b>STOP REGISTER.</b>          |       |          |                                                                |  |  |  |

| 0       | 0 0 1 1 STEP. Routes data from DB0-DB23 to the <b>STEP REGISTER.</b>          |       |          |                                                                |  |  |  |

| 0       | 0 1 0 0 REFERENCE. Routes data from DB0-DB23 to the <b>REFERENCE REGISTER</b> |       |          |                                                                |  |  |  |

| All FUN | ICTION                                                                        | SELEC | T values | not shown above are reserved for factory use.                  |  |  |  |

### **Data Structures**

### Figure 1: SPI Bus/Microwire-Interface Data Structure

| FUNCTION SELECT (4 BITS) |      |      | BITS) | MULTIPLIER (4 BITS) |      |      |      | FREQUENCY/CHANNEL (24 BITS) |      |     |     |     |     |

|--------------------------|------|------|-------|---------------------|------|------|------|-----------------------------|------|-----|-----|-----|-----|

| DB31                     | DB30 | DB29 | DB28  | DB27                | DB26 | DB25 | DB24 | DB23                        | DB22 | DBn | DB2 | DB1 | DB0 |

| FS3                      | FS2  | FS1  | FS0   | M3                  | M2   | M1   | M0   | FC23                        | FC22 | FCn | FC2 | FC1 | FC0 |

### **SPI Bus/MICROWIRE-Interface Timing Characteristics**

Figure 6: MICROWIRE Interface Timing Diagram

| Parameter      | Limit at $t_{min}$ to $t_{max}$ | Units  | Test Conditions/Comments                                                 |

|----------------|---------------------------------|--------|--------------------------------------------------------------------------|

| t <sub>1</sub> | 100                             | ns min | DATA to CLOCK setup time                                                 |

| t <sub>2</sub> | 100                             | ns min | DATA to CLOCK hold time                                                  |

| t <sub>3</sub> | 250                             | ns min | CLOCK high time                                                          |

| t <sub>4</sub> | 250                             | ns min | CLOCK low time                                                           |

| t <sub>5</sub> | 100                             | ns min | CLOCK to $\overline{CS}$ setup time                                      |

| t <sub>6</sub> | 200                             | ns min | $\overline{\text{CS}}$ pulse width (applies to MICROWIRE Interface only) |

| t <sub>7</sub> | 200                             | ns min | $\overline{CS}$ to CLOCK setup time (applies to SPI BUS only)            |

Figure 7: SPI BUS Timing Diagram

# **Package Drawing**

#### all dimensions in inches

## **Recommended Layout**

#### all dimensions in inches

|   | Recommended Layout Dimensions |       |       |  |  |  |  |  |  |  |

|---|-------------------------------|-------|-------|--|--|--|--|--|--|--|

|   | (min) (typ) (max)             |       |       |  |  |  |  |  |  |  |

| a | 0.040                         | 0.042 | 0.044 |  |  |  |  |  |  |  |

| b | 0.047                         | 0.050 | 0.053 |  |  |  |  |  |  |  |

| с | 0.375                         | 0.380 | 0.385 |  |  |  |  |  |  |  |

| d | 0.435                         | 0.440 | 0.445 |  |  |  |  |  |  |  |

| e |                               | 0.080 |       |  |  |  |  |  |  |  |

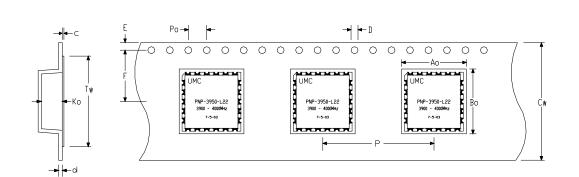

# **Tape and Reel Specifications**

#### all dimensions in mm

| Тар | Tape and Reel Dimensions |    |      |  |  |  |  |  |  |

|-----|--------------------------|----|------|--|--|--|--|--|--|

| Ao  | 13.0                     | E  | 1.75 |  |  |  |  |  |  |

| Bo  | 13.0                     | F  | 11.5 |  |  |  |  |  |  |

| P   | 16.0                     | с  | 0.06 |  |  |  |  |  |  |

| Po  | 4.0                      | d  | 0.30 |  |  |  |  |  |  |

| Cw  | 24.0                     | Tw | 21.2 |  |  |  |  |  |  |

| D   | 1.5                      | Ko | 5.2  |  |  |  |  |  |  |