## **AK2360A**

# Scrambler IC for two-way radio

#### **Features**

- ☐ Frequency inversion type scrambler for a voice encryption two-way radio

- ☐ High quality decoded voice: S/N=47dB(Typ), S/(N+D)=50dB(Typ)

- ☐ Allowing selection of an inverted frequency (3.397kHz or 3.039kHz) and voice passage band

- □ Scrambler bypass function included

- ☐ Based on <u>5.3125MHz</u> (1/4 for 21.25MHz) external clock supply

- ☐ Operating voltage: 2.6V to 3.3V

- ☐ Operating temperature: -30°C to +85°C

- ☐ Package: 8-pin SON

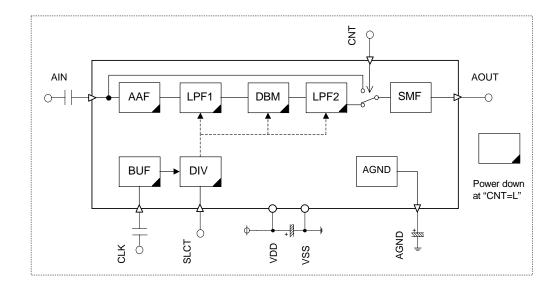

### **Block Diagram**

## Contents

-

| Features                                  | 1 |

|-------------------------------------------|---|

| Block Diagram                             | 1 |

| Contents                                  | 2 |

| General Description                       | 3 |

| Circuit Configuration                     | 3 |

| Pin Functions                             | 4 |

| Absolute Maximum Ratings                  | 5 |

| Recommended Operating Conditions          | 5 |

| Digital DC Characteristics                | 5 |

| Clock Input Characteristics               | 5 |

| Current Consumption                       | 6 |

| Analog Characteristics                    | 6 |

| Recommended External Application Circuits | 7 |

| Package                                   | 9 |

| Important Notice                          | 0 |

### **General Description**

The AK2360A is a radio scrambler IC device suitable for half-duplex communication. As the scrambler method, a simple frequency inversion method is used in which audio signal components are inverted about the carrier frequency by using the double balanced mixer (DBM).

The inverted frequency and voice passage band can be changed according to the input to the SLCT pin. The scrambler can be bypassed by using the CNT pin, and part of the circuit blocks is placed in the power-down state accordingly.

A signal-to-noise ratio of 40dB or more and a distortion of 43dB or more can be obtained by inserting filters before and after DBM as shown in the block diagram, therefore allowing less sound quality deterioration when the scrambler is used.

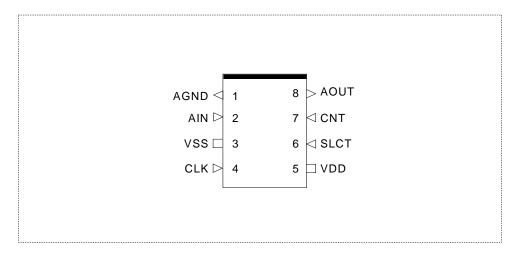

### ☐ Pin assignments (Top view)

### **Circuit Configuration**

| Block | Function                                                                                                                                         |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| AAF   | Active low-pass filter to prevent aliasing noise generated in the following switched capacitor filter (SCF) block                                |

| LPF1  | Low-pass filter for limiting the band of the audio signal input from the AIN pin                                                                 |

| DBM   | Double balanced modulator for performing frequency inversion. The carrier frequency can be changed according to the input level on the SLCT pin. |

| LPF2  | Low-pass filter for removing upper wave components generated by mixing by DBM                                                                    |

| SMF   | Smoothing filter for removing harmonics components generated in LPF2 and clock components                                                        |

| BUF   | Buffer circuit for adjusting the level of the clock signal input from the CLK pin                                                                |

| DIV   | Divides the clock signal and generates a clock signal for the SCF circuit and the carrier frequency for DBM.                                     |

| AGND  | A block for generating the reference voltage (1/2VDD) of the internal analog circuit                                                             |

### Pin Functions

| Pin No. | Pin name | Pin type | Function                                                                                                                                                                                                                      |  |  |  |  |  |

|---------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1       | AGND     | AO       | Analog ground output pin A capacitor is connected to this pin to stabilize the analog ground level.                                                                                                                           |  |  |  |  |  |

| 2       | AIN      | Al       | Audio signal input pin                                                                                                                                                                                                        |  |  |  |  |  |

| 3       | VSS      | PWR      | Negative power supply pin Apply 0V.                                                                                                                                                                                           |  |  |  |  |  |

| 4       | CLK      | Al       | Clock signal input pin See "Recommended External Application Circuits".                                                                                                                                                       |  |  |  |  |  |

| 5       | VDD      | PWR      | Positive power supply pin Connect this pin to a power supply ranging from 2.6V to 3.3V with less noise. Connect a bypass capacitor of 0.1µF or higher between this pin and the VSS pin.                                       |  |  |  |  |  |

| 6       | SLCT     | DI       | Carrier frequency switching pin This pin changes the carrier frequency and voice passage band for the scrambler.  Input level Carrier frequency Voice passage band High 3.397kHz 289Hz to 3197Hz Low 3.039kHz 258Hz to 2839Hz |  |  |  |  |  |

| 7       | CNT      | DI       | Scrambler bypass pin This pin causes the AAF block through LPF2 block to be bypassed. When bypassed, these blocks are placed in the power-down state.  Input level Setting High Scrambler enables. Low Scrambler bypasses.    |  |  |  |  |  |

| 8       | AOUT     | AO       | Audio signal output pin *2)                                                                                                                                                                                                   |  |  |  |  |  |

Note) A: Analog, D: Digital, PWR: Power, I: Input, O: Output

<sup>\*1)</sup> A pull-up resistor of  $50k\Omega$  or more is included.

<sup>\*2)</sup> Load impedance >  $10k\Omega$ , load capacitance < 50pF

## Absolute Maximum Ratings

| Parameter                                  | Symbol          | Min. | Max.    | Unit |

|--------------------------------------------|-----------------|------|---------|------|

| Power supply voltage                       | VDD             | -0.3 | 4.6     | V    |

| Ground level                               | VSS             | 0    | 0       | V    |

| Input voltage                              | V <sub>IN</sub> | -0.3 | VDD+0.3 | V    |

| Input current (excluding power supply pin) | I <sub>IN</sub> | -10  | +10     | mA   |

| Storage temperature                        | $T_{stg}$       | -55  | 130     | °C   |

Note) All voltages are relative to the VSS pin.

Caution) If the device is used in conditions exceeding these values, the device may be destroyed. Normal operations are not guaranteed in such extreme conditions.

### **Recommended Operating Conditions**

| Parameter                      | Symbol | Condition | Min. | Тур.   | Max. | Unit |

|--------------------------------|--------|-----------|------|--------|------|------|

| Operating temperature          | Ta     |           | -30  |        | 85   | °C   |

| Operating power supply voltage | VDD    |           | 2.6  | 3.0    | 3.3  | V    |

| Analog reference voltage       | AGND   |           |      | 1/2VDD |      | V    |

Note) All voltages are relative to the VSS pin.

### Digital DC Characteristics

| Parameter                | Symbol          | Condition                         | Min.   | Тур. | Max.   | Unit      |

|--------------------------|-----------------|-----------------------------------|--------|------|--------|-----------|

| High level input voltage | $V_{IH}$        | SLCT, CNT                         | 0.8VDD |      |        | V         |

| Low level input voltage  | $V_{IL}$        | SLCT, CNT                         |        |      | 0.2VDD | ٧         |

| High level input current | I <sub>IH</sub> | V <sub>IH</sub> =VDD<br>SLCT, CNT |        |      | 10     | μА        |

| Low level input current  | I <sub>IL</sub> | V <sub>IL</sub> =0V<br>SLCT, CNT  | -66    |      |        | μΑ        |

| Pull-up resistance       | $R_{UP}$        | SLCT, CNT                         | 50     |      |        | $k\Omega$ |

### **Clock Input Characteristics**

| Parameter       | Symbol    | Condition | Min. | Тур. | Max.    | Unit     | Remarks           |

|-----------------|-----------|-----------|------|------|---------|----------|-------------------|

| Clock cycle     | $T_WP$    | CLK       |      | 188  |         | ns       | f=5.3125MHz       |

| Input amplitude | $V_{CLK}$ | CLK       | 0.2  |      | VDD-0.1 | $V_{PP}$ | Clipped sine wave |

## **Current Consumption**

| Parameter   | Symbol | Condition                                                                                       | Min. | Тур. | Max. | Unit |

|-------------|--------|-------------------------------------------------------------------------------------------------|------|------|------|------|

| Current     | IDD0   | When scrambler is bypassed (CNT=V <sub>IL</sub> ) with CLK=5.3125MHz, V <sub>CLK</sub> =0.2Vpp  |      | 0.7  | 1.1  | m 1  |

| consumption | IDD1   | When scrambler is operating (CNT=V <sub>IH</sub> ) with CLK=5.3125MHz, V <sub>CLK</sub> =0.2Vpp |      | 1.65 | 2.6  | mA   |

## **Analog Characteristics**

Unless otherwise specified, the following apply: CLK = 5.3125MHz, SLCT =  $V_{IH}$ , CNT =  $V_{IH}$ , f = 1kHz@AIN, dBm = 0dBm (= 0.775Vrms) at 1mW with a  $600\Omega$  load.

| Parameter                       | Condition                                                                                            | Min.  | Тур.  | Max.  | Unit | Remarks |

|---------------------------------|------------------------------------------------------------------------------------------------------|-------|-------|-------|------|---------|

| Standard input level            | @AIN                                                                                                 |       | -11.5 |       | dBm  |         |

| Output level                    | AIN to AOUT<br>AIN=-11.5dBm                                                                          | -12.5 | -11.5 | -10.5 | dBm  |         |

|                                 | When CNT=V <sub>IH</sub> : (3.397-1.0)kHz<br>When CNT=V <sub>IL</sub> : 1.0kHz                       | -12.5 | -11.5 | -10.5 | авті |         |

| S/N ratio                       | AIN to AOUT AIN=-11.5dBm When CNT=V <sub>IH</sub> and CNT=V <sub>IL</sub> : 30kHz low-pass filtering | 40    | 47    |       | dB   |         |

| S/(N+D)                         | AIN to AOUT AIN=-2.7dBm When CNT=V <sub>IH</sub> and CNT=V <sub>IL</sub> : 30kHz low-pass filtering  | 43    | 50    |       | dB   |         |

| High frequency rejection level  | AIN to AOUT AIN=-11.5dBm Measurement frequency:(3.397+1.0)kHz                                        |       | -65   | -51.5 | dBm  |         |

| Carrier signal<br>leakage level | AIN to AOUT AIN=No input Measurement frequency: 3.397kHz                                             |       | -75   | -51.5 | dBm  |         |

| Original signal leakage level   | AIN to AOUT AIN=-11.5dBm Measurement frequency: 1.0kHz                                               |       | -85   | -51.5 | dBm  |         |

Note) Under connecting  $10k\Omega$  and 50pF load to AGND(=1/2VDD) equivalent offset level AOUT pin.

## Recommended External Application Circuits

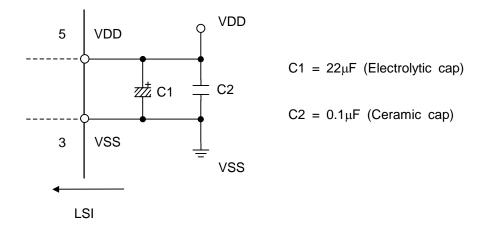

### 1) Power supply stabilizing capacitance

Connect capacitors between the VDD and VSS pins to eliminate ripple and noise included in power supply. For maximum effect, the capacitors should be placed at a shortest distance between the pins.

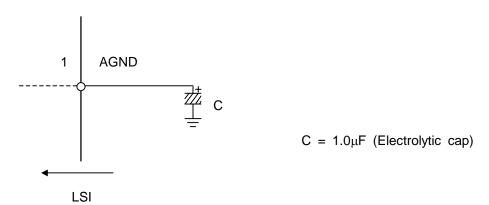

#### 2) AGND stabilizing capacitance

It is recommended that a capacitor with  $1.0\mu F$  or larger be connected between the AGND pin and VSS to stabilize the AGND signal. The capacitor should be placed as close to the AGND pin as possible.

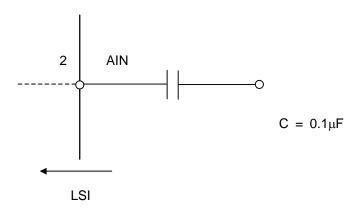

#### 3) External AIN capacitance

Connect a capacitor to the AIN pin to adjust the input signal DC offset and the internal operation point of the LSI device. This configures a high-pass filter with fc being about 3Hz.

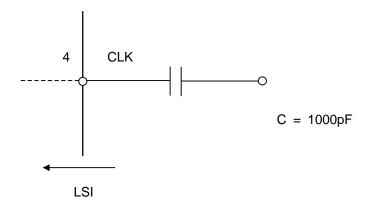

#### 4) External CLK capacitance

Connect a capacitor to the CLK pin to adjust the DC offset of the clipped sine signal and the internal operation point of the LSI device.

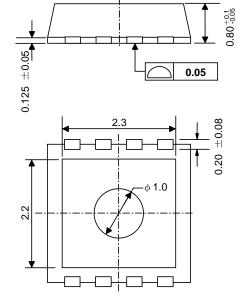

## Package

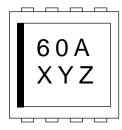

□ Marking

Date of manufacturing Date of manufacturing

Lowest 1 digit of the year Month

Production lot number

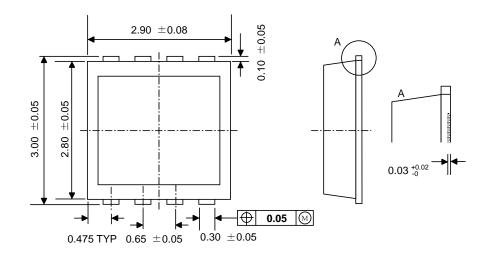

☐ Outline dimensions

#### Important Notice

#### IMPORTANT NOTICE —

- These products and their specifications are subject to change without notice. Before considering any use or application, consult the Asahi Kasei Microsystems Co., Ltd. (AKM) sales office or authorized distributor concerning their current status.

- AKM assumes no liability for infringement of any patent, intellectual property, or other right in the application or use of any information contained herein.

- Any export of these products, or devices or systems containing them, may require an

export license or other official approval under the law and regulations of the country of

export pertaining to customs and tariffs, currency exchange, or strategic materials.

- AKM products are neither intended nor authorized for use as critical components in any safety, life support, or other hazard related device or system, and AKM assumes no responsibility relating to any such use, except with the express written consent of the Representative Director of AKM. As used here:

(a) A hazard related device or system is one designed or intended for life support or maintenance of safety or for applications in medicine, aerospace, nuclear energy, or other fields, in which its failure to function or perform may reasonably be expected to result in loss of life or in significant injury or damage to person or property.

(b) A critical component is one whose failure to function or perform may reasonably be expected to result, whether directly or indirectly, in the loss of the safety or effectiveness of the device or system containing it, and which must therefore meet very high standards of performance and reliability.

- It is the responsibility of the buyer or distributor of an AKM product who distributes, disposes of, or otherwise places the product with a third party to notify that party in advance of the above content and conditions, and the buyer or distributor agrees to assume any and all responsibility and liability for and hold AKM harmless from any and all claims arising from the use of said product in the absence of such notification.