# 20 M BAUD HIGH CMR LOGIC GATE OPTOCOUPLER

HCPL-2400 HCPL-2411

### Features

- HIGH SPEED: 40 MBd TYPICAL DATA RATE

- HIGH COMMON MODE REJECTION

- HCPL-2400 = 1kV/μs @ 50 V<sub>CM</sub>

- HCPL-2411 = 1kV/μs @ 300 V<sub>CM</sub>

- AC PERFORMANCE GUARANTEED OVER TEMPERATURE

- COMPATIBLE WITH TTL, STTL, LSTTL, AND HCMOS LOGIC FAMILIES

- HIGH SPEED AIGAAS EMITTER

- THREE STATE OUTPUT (NO PULL-UP RESISTOR REQUIRED)

- HIGH POWER SUPPLY NOISE IMMUNITY

- RECOGNIZED UNDER THE COMPONENT PROGRAM OF U.L. (FILE NO. E55361) FOR DIELECTRIC WITHSTAND PROOF TEST VOLTAGES OF 2500 Vac. 1 MINUTE

- VDE 0883 APPROVAL AVAILABLE

- MIL-STD-1772 VERSION AVAILABLE (HCPL-5400/1)

## **Applications**

- ISOLATION OF HIGH SPEED LOGIC SYSTEMS

- COMPUTER-PERIPHERAL INTERFACES

- ISOLATED BUS DRIVER (NETWORKING APPLICATIONS)

- SWITCHING POWER SUPPLIES

- GROUND LOOP ELIMINATION

- HIGH SPEED DISK DRIVE I/O

- DIGITAL ISOLATION FOR A/D, D/A CONVERSION

- PULSE TRANSFORMER REPLACEMENT

# Description

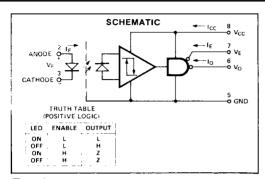

The HCPL-2400/11 high speed optocouplers combine an 820 nm AlGaAs light emitting diode with a high speed photo-detector. This combination results in very high data rate capability and low input current. The three state output eliminates the need for a pull-up resistor and allows for direct drive of data buses. The hysteresis provides differential mode noise immunity and minimizes the potential for output signal chatter. Improved power supply rejection minimizes the need for special power supply bypassing precautions.

The electrical and switching characteristics of the HCPL-2400/11 are guaranteed over the temperature range of 0°C to 70°C.

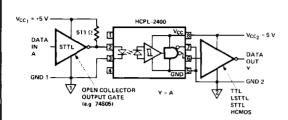

The HCPL-2400/11 are compatible with TTL. STTL, LSTTL and HCMOS logic families. When Schottky type TTL devices (STTL) are used, a data rate performance of 20 MBd over temperature is guaranteed when using the application circuit of Figure 13. Typical data rates are 40 MBd.

### **Recommended Operating Conditions**

| Parameter             | Symbol   | Min. | Max. | Units     |

|-----------------------|----------|------|------|-----------|

| Power Supply Voltage  | Vcc      | 4.75 | 5.25 | Volts     |

| Input Current (High)  | IF (ON)  | 4    | 8    | mA        |

| Input Voltage (Low)   | VF (OFF) | _    | 0.8  | Volts     |

| Enable Voltage (Low)  | VEL      | 0    | 08   | Volts     |

| Enable Voltage (High) | VEH      | 2.0  | Vcc  | Volts     |

| Operating Temperature | TA       | 0    | 70°  | °C        |

| Fan Out               | N        |      | 5    | TTL Loads |

# Absolute Maximum Ratings (No derating required up to 85°C)

| Parameter                          | Symbol | Min.             | Max.             | Units  | Note |

|------------------------------------|--------|------------------|------------------|--------|------|

| Storage Temperature                | Ts     | -55              | 125              | °C     |      |

| Operating Temperature              | TA     | -40              | 85               | °C     | T    |

| Lead Solder Temperature            | 260° C | for 10 s. (1.6 m | im below seating | plane) |      |

| Average Forward Input Current      | lF     |                  | 10.0             | mA     |      |

| Peak Forward Input Current         | IFPK   |                  | 20.0             | mA     | 9    |

| Reverse Input Voltage              | VR     |                  | 3.0              | V      |      |

| Supply Voltage                     | Vcc    | 0                | 7.0              | V      |      |

| Three State Enable Voltage         | VE     | -0.5             | 10.0             | V      | 1    |

| Average Output Collector Current   | 10     | -25.0            | 25.0             | mA     |      |

| Output Collector Voltage           | Vo     | -0.5             | 10.0             | V      |      |

| Output Collector Power Dissipation | Po     |                  | 40.0             | mW     |      |

| Parameter                              | Symbol           | Min.       | Тур.       | Max. | Units            | Test Conditions                               |                        | Figure | Note |

|----------------------------------------|------------------|------------|------------|------|------------------|-----------------------------------------------|------------------------|--------|------|

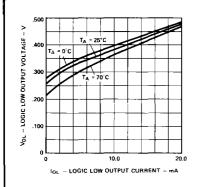

| Logic Low Output Voltage               | Vol              |            |            | 0.5  | Volts            | IOL = 8.0 mA (5 TTL Loads)                    |                        | 1      |      |

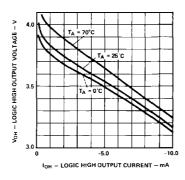

| Logic High Output Voltage              | Vон              | 2.4        |            |      | Volts            | Iон = −4.0 mA                                 |                        | 2      |      |

| Output Leakage Current                 | Іонн             | ļ          |            | 100  | μА               | V <sub>O</sub> = 5.25 V                       | V <sub>F</sub> = 0.8 V |        |      |

| Logic High Enable Voltage              | VEH              | 2.0        |            |      | Volts            |                                               |                        |        |      |

| Logic Low Enable Voltage               | VEL              |            |            | 0.8  | Volts            |                                               |                        |        |      |

| Logic High Enable Current              | JEH .            |            |            | 20   | μА               | V <sub>E</sub> = 2.4 V                        |                        |        |      |

|                                        |                  |            |            | 100  | μΑ               | V <sub>E</sub> = 5.25 V                       |                        | 1      |      |

| Logic Low Enable Current               | IEL              |            | -0.28      | -0.4 | mA               | V <sub>E</sub> = 0.4V                         |                        |        |      |

| Logic Low Supply Current               | ICCL             |            | 19         | 26   | mA               | V <sub>CC</sub> = 5.25 V                      |                        |        |      |

| Logic High Supply Current              | Іссн             |            | 17         | 26   | mA               | V <sub>E</sub> = 0 V                          |                        |        |      |

| High Impedance State                   | locz             |            | 22         | 28   | mA               | V <sub>CC</sub> = 5.25 V                      | _                      |        |      |

| Supply Current                         |                  |            |            |      |                  | V <sub>E</sub> = 5.25 V                       |                        |        |      |

| High Impedance State                   | lozu             |            |            | 20   | μΑ               | V <sub>O</sub> = 0.4V                         |                        |        |      |

| Output Current                         | lozh             |            |            | 20   | μА               | V <sub>O</sub> = 2.4 V                        | $V_E = 2 V$            |        |      |

|                                        | lozh             |            |            | 100  | μА               | V <sub>O</sub> = 5.25 V                       |                        | ľ      |      |

| Logic Low Short Circuit Output Current | lost             |            | 52         |      | mA               | V <sub>O</sub> = V <sub>CC</sub> = 5.25 V     | I <sub>F</sub> = 8 mA  |        | 1    |

| Logic High Short Circuit               | losн             |            | <b>-45</b> |      | mA               | V <sub>CC</sub> = 5.25 V                      | IF = 0 mA,             |        | 1    |

| Output Current                         |                  |            |            |      |                  |                                               | V <sub>O</sub> = GND   |        |      |

| Input Current Hysteresis               | IHYS             |            | 0.25       |      | mA               | V <sub>CC</sub> = 5 V                         |                        | 3      |      |

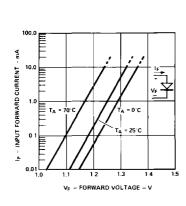

| Input Forward Voltage                  | VF               | 1.1        | 1.3        | 1.5  | Volts            | T <sub>A</sub> = 25°C                         | I <sub>F</sub> = 8 mA  | 4      |      |

|                                        |                  | 1.0        |            | 1.55 | ļ                | T <sub>A</sub> = 25°C                         |                        |        |      |

| Input Reverse Breakdown<br>Voltage     | BV <sub>R</sub>  | 3.0<br>2.0 | 5.0        |      | Volts            | 1A - 25 C                                     | i <sub>R</sub> = 10 μA |        |      |

| Input Diode Temperature                | ٦٧٤              |            | -1.44      |      | mV/°C            | I <sub>F</sub> = 6 mA                         |                        | 4      |      |

| Coefficient                            | -TA<br>AΤΔ       |            |            |      |                  |                                               |                        |        |      |

| Input-Output Insulation                | V <sub>ISO</sub> | 2500       |            |      | V <sub>RMS</sub> | RH ≤ 50%, t = 1 min.<br>T <sub>A</sub> = 25°C |                        |        | 2    |

| Input-Output Resistance                | R <sub>I-O</sub> |            | 1012       |      | ohms             | V <sub>I-O</sub> = 500 VDC                    |                        |        | 2    |

| Input-Output Capacitance               | C <sub>I-O</sub> |            | 0.6        |      | pF               | f = 1 MHz, V <sub>I-O</sub> = 0 V dc          |                        | 2      |      |

| Input Capacitance                      | CiN              |            | 20         |      | рF               | f = 1 MHz, V <sub>F</sub> = 0V, Pins 2 and 3  |                        |        |      |

Switching Specifications  $0^{\circ}C \le T_A \le 70^{\circ}C$ , 4.75 V  $\le V_{CC} \le 5.25$  V, 0.0 V  $\le V_{EN} \le 0.8$  V, 4 mA  $\le I_F \le 8.0$  mA. All typicals  $V_{CC} = 5$  V,  $T_A = 25^{\circ}C$ , I<sub>F</sub> = 6.0 mA except where noted.

| Parameter                                         | Symbo            | 4    | Min. | Typ.   | Max. | Units            | Test Conditio                                                         | ns                                         | Figure  | Note |

|---------------------------------------------------|------------------|------|------|--------|------|------------------|-----------------------------------------------------------------------|--------------------------------------------|---------|------|

| Propagation Delay Time to                         | t <sub>PHL</sub> |      |      |        | 55   | ns               | $I_{F(ON)} = 7.0 \text{ m}$                                           | Α                                          | 5, 6. 7 | 4    |

| Logic Low Output Level                            |                  |      | 15   | 33     | 60   | ns               |                                                                       |                                            | 5, 6, 7 | 3    |

| Propagation Delay Time to Logic High Output Level |                  |      |      |        | 55   | ns               | $I_{F(ON)} = 7.0 \text{ m}$                                           | A                                          | 5, 6, 7 | 4    |

|                                                   |                  |      | 15   | 30     | 60   | ns               |                                                                       |                                            | 5, 6, 7 | 3    |

| Pulse Width Distortion     tpHL-tpLH              |                  | PLH  |      | 2      | 15   | ns               | I <sub>F(ON)</sub> = 7.0 mA                                           |                                            | 5, 8    | 4    |

|                                                   |                  |      |      | 3      | 25   | ns               |                                                                       |                                            | 5, 8    |      |

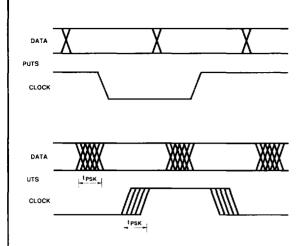

| Propagation Delay Skew                            | t <sub>PSK</sub> |      |      |        | 35   | ns               |                                                                       |                                            | 15, 16  | 5    |

| Output Rise Time                                  | t <sub>r</sub>   |      |      | 20     |      | ns               |                                                                       |                                            | 5       |      |

| Output Fall Time                                  | tf               |      |      | 10     |      | ns               |                                                                       |                                            | 5       | -    |

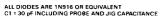

| Output Enable Time to<br>Logic High               | t <sub>PZH</sub> |      |      | 15     |      | ns               |                                                                       |                                            | 9, 10   |      |

| Output Enable Time to<br>Logic Low                | t <sub>PZL</sub> |      | _    | 30     |      | ns               |                                                                       | _                                          | 9, 10   |      |

| Output Disable Time from Logic High               | t <sub>PHZ</sub> |      |      | 20     |      | ns               | _                                                                     |                                            | 9, 10   |      |

| Output Disable Time from Logic Low                | t <sub>PLZ</sub> |      |      | 15     |      | ns               |                                                                       |                                            | 9, 10   |      |

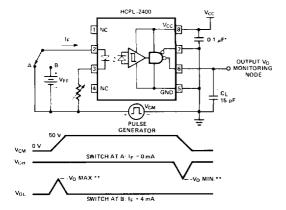

| Logic High Common Mode                            | CM <sub>H</sub>  | 2400 | 1000 | 10,000 |      | V/μs             | V <sub>CM</sub> = 50 V                                                |                                            |         |      |

| Transient Immunity                                |                  | 2411 | 1000 |        |      | V/μs             | V <sub>CM</sub> = 300 V                                               | $T_A = 25^{\circ}C, 1_F = 0$               | 11      | 6    |

| Logic Low Common Mode                             | CM <sub>L</sub>  | 2400 | 1000 | 10,000 |      | V/μs             | V <sub>CM</sub> = 50 V                                                | T <sub>A</sub> =25°C, I <sub>F</sub> =4 mA |         |      |

| Transient Immunity                                |                  | 2411 | 1000 |        |      | V/μs             | V <sub>CM</sub> = 300 V                                               |                                            | 11      | 6    |

| Power Supply Noise<br>Immunity                    | PSNI             |      |      | 0.5    |      | V <sub>p-p</sub> | $V_{CC} = 5.0 \text{ V}, 48 \text{ Hz} \le F_{AC} \le 50 \text{ MHz}$ |                                            |         | 7    |

# **Insulation Related Specifications**

| Parameter                             | Symbol | Value | Units | Conditions                                         |

|---------------------------------------|--------|-------|-------|----------------------------------------------------|

| Min. External Air Gap (Clearance)     | L(IO1) | ≥7    | mm    | Measured from input terminals to output terminals  |

| Min.External Tracking Path (Creepage) | L(IO2) | ≥7    | mm    | Measured from input terminals to output terminals  |

| Min. Internal Plastic Gap (Clearance) |        | 0.08  | mm    | Through insulation distance conductor to conductor |

| Tracking Resistance                   | CTI    | 175   | Volts | DIN IEC 112/VDE 0303 Part 1                        |

| Isolation Group (per DIN VDE 0109)    |        | IIIa  |       | Material Group DIN VDE 0109                        |

### Notes:

- 1. Duration of output short circuit time not to exceed 10 ms.

- 2. Device considered a two terminal device: pins 1-4 shorted together, and pins 5-8 shorted together.

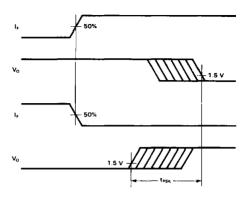

- 3. tPHL propagation delay is measured from the 50% level on the rising edge of the input current pulse to the 1.5 V level on the falling edge of the output pulse. The tPLH propagation delay is measured from the 50% level on the falling edge of the input current pulse to the 1.5 V level on the rising edge of the output pulse.

- 4. This specification simulates the worst case operating conditions of the HCPL-2400/11 over the recommended operating temperature and Vcc range with the suggested applications circuit of Figure 13.

- 5. Propagation delay skew is discussed later in this data sheet.

- 6. CMH is the maximum slew rate of common mode voltage that can be sustained with the output voltage in the logic high state (VO(MIN) > 2.0 V). CML is the maximum slew rate of common mode voltage that can be sustained with the output voltage in the logic low state  $(V_{O(MAX)} < 0.8 \text{ V})$ .

- 7. Power Supply Noise Immunity is the peak to peak amplitude of the ac ripple voltage on the V<sub>CC</sub> line that the device will withstand and still remain in the desired logic state. For desired logic high state,  $V_{OH(MIN)} > 2.0 \text{ V}$ , and for desired logic low state, V<sub>OL(MAX)</sub> < 0.8 volts.

- 8. Peak Forward Input Current pulse width < 50 μs at 1 KHz maximum repetition rate.

- 9. Use of a 0.1 µF bypass capacitor connected between pins 5 and 8 is recommended.

Figure 1. Typical Logic Low Output Voltage vs. Logic Low Output Current

Figure 2. Typical Logic High Output Voltage vs. Logic High Output Current

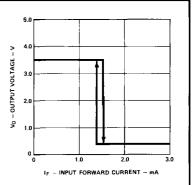

Figure 3. Typical Output Voltage vs. Input Forward Current

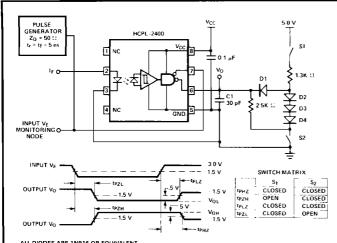

PULSE

GENERATOR

t<sub>1</sub> + 1 - 5 m

f - 1 MHz

HCPL-2400/11

INC

VCC

HCPL-2400/11

VCC

ANODE

NODE

OUTPUT

MONITORING

NODE

1 3 CATHODE OUTPUT

THE PROBE AND JIG CAPACITANCES ARE INCLUDED IN

C; AND C;

ALL DIODES ARE ECG 519 OR EQUIVALENT.

INPUT

INPUT

IF

OUTPUT

OUTPUT

OUTPUT

OUTPUT

OUTPUT

OUTPUT

OUTPUT

1.5 V

Figure 4. Typical Diode Input Forward Current Characteristic

Figure 5. Test Circuit for tpLH, tpHL, tr, and tr

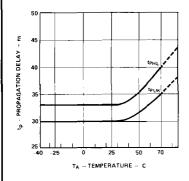

Figure 6. Typical Propagation Delay vs.

Ambient Temperature

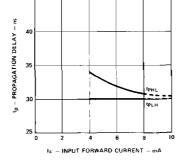

Figure 7. Typical Propagation Delay vs. Input Forward Current

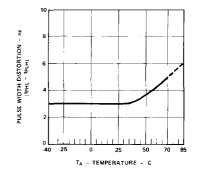

Figure 8. Typical Pulse Width Distortion vs.

Ambient Temperature

Figure 9. Test Circuit for  $t_{PHZ}$ ,  $t_{PZH}$ ,  $t_{PLZ}$  and  $t_{PZL}$ .

Figure 10. Typical Enable Propagation Delay vs. Ambient Temperature

- \*MUST BE LOCATED 1 cm FROM DEVICE UNDER TEST.

\*\*SEE NOTE 6

\*CL IS APPROXIMATELY 15 pF, WHICH INCLUDES PROBE AND STRAY WIRING CAPACITANCE.

Figure 11. Test Diagram for Common Mode Transient Immunity and Typical Waveforms

# **Applications**

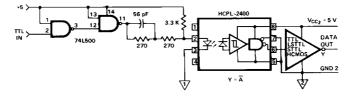

Figure 13. Recommended 20 MBd HCPL-2400/11 Interface Circuit

Figure 14. Alternative HCPL-2400/11 Interface Circuit

Figure 15. Illustration of Propagation Delay Skew - tpsk-

# Propagation Delay, Pulse-Width Distortion and Propagation Delay Skew

Propagation delay is a figure of merit which describes how quickly a logic signal propagates through a system. The propagation delay from low to high ( $t_{PLH}$ ) is the amount of time required for an input signal to propagate to the output, causing the output to change from low to high. Similarly, the propagation delay from high to low ( $t_{PHL}$ ) is the amount of time required for the input signal to propagate to the output, causing the output to change from high to low (see Figure 5).

Pulse-width distortion (PWD) results when  $t_{PLH}$  and  $t_{PHL}$  differ in value. PWD is defined as the difference between  $t_{PLH}$  and  $t_{PHL}$  and often determines the maximum data rate capability of a transmission system. PWD can be expressed in percent by dividing the PWD (in ns) by the minimum pulse width (in ns) being transmitted. Typically, PWD on the order of 20–30% of the minimum pulse width is tolerable; the exact figure depends on the particular application (RS232, RS422, T-1, etc.).

Propagation delay skew, t<sub>PSK</sub>, is an important parameter to consider in parallel data applications where synchronization of signals on parallel data lines is a concern. If the parallel data is being sent through a group of optocouplers, differences in propagation delays will cause the data to arrive at the outputs of the optocouplers at different times. If this difference in propagation delays is large enough, it will determine the maximum rate at which parallel data can be sent through the optocouplers.

Propagation delay skew is defined as the difference between the minimum and maximum propagation delays, either t<sub>PLH</sub> or t<sub>PHL</sub>, for any given group of optocouplers which are operating under the same conditions (i.e., the same drive current, supply voltage, output load, and operating temperature). As illustrated in Figure 15, if the inputs of a group of

optocouplers are switched either ON or OFF at the same time,  $t_{PSK}$  is the difference between the shortest propagation delay, either  $t_{PLH}$  or  $t_{PHL}$ , and the longest propagation delay, either  $t_{PLH}$  or  $t_{PHL}$ .

As mentioned earlier, t<sub>PSK</sub> can determine the maximum parallel data transmission rate. Figure 16 is the timing diagram of a typical parallel data application with both the clock and the data lines being sent through optocouplers. The figure shows data and clock signals at the inputs and outputs of the optocouplers. To obtain the maximum data transmission rate, both edges of the clock signal are being used to clock the data; if only one edge were used, the clock signal would need to be twice as fast.

Propagation delay skew represents the uncertainty of where an edge might be after being sent through an optocoupler. Figure 16 shows that there will be uncertainty in both the data and the clock lines. It is important that these two areas of uncertainty not overlap, otherwise the clock signal might arrive before all of the data outputs have settled, or some of the data outputs may start to change before the clock signal has arrived. From these considerations, the absolute minimum pulse width that can be sent through optocouplers in a parallel application is twice tpsk. A cautious design should use a slightly longer pulse width to ensure that any additional uncertainty in the rest of the circuit does not cause a problem.

The HCPL-2400/11 optocouplers offer the advantages of guaranteed specifications for propagation delays, pulsewidth distortion, and propagation delay skew over the recommended temperature, input current, and power supply ranges.

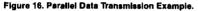

Figure 17. Modulation Code Selections

# **Application Circuit**

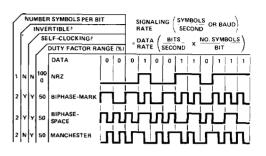

A recommended LED drive circuit is shown in Figure 13. This circuit utilizes several techniques to minimize the total pulse-width distortion at the output of the opto-coupler. By using two inverting TTL gates connected in series, the inherent pulse-width distortion of each gate cancels the distortion of the other gate. For best results, the two series-connected gates should be from the same package.

The circuit in Figure 13 also uses techniques known as prebias and peaking to enhance the performance of the optocoupler LED. Prebias is a small forward voltage applied to the LED when the LED is off. This small prebias voltage partially charges the junction capacitance of the LED, allowing the LED to turn on more quickly. The speed of the LED is further increased by applying momentary current peaks to the LED during the turn-on and turn-off transitions of the drive current. These peak currents help

to charge and discharge the capacitances of the LED more quickly, shortening the time required for the LED to turn on and off.

Switching performance of the HCPL-2400/11 optocouplers is not sensitive to the TTL logic family used in the recommended drive circuit. The typical and worst-case switching parameters given in the data sheet can be met using common 74LS TTL inverting gates or buffers. Use of faster TTL families will slightly reduce the overall propagation delays from the input of the drive circuit to the output of the optocoupler, but will not necessarily result in lower pulse-width distortion or propagation delay skew. This reduction in overall propagation delays is due to shorter delays in the drive circuit, not to changes in the propagation delays are not affected by the speed of the logic used in the drive circuit.

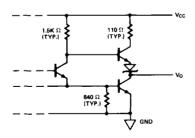

Figure 18, Typical HCPL-2400/11 Output Schematic