# Standard Products MIP7365

### 64-Bit Superscaler Microprocessor

**Preliminary**

November 16, 2005

#### **FEATURES**

- □ Upscreened PMC-Sierra RM7065C

- ☐ Military and Industrial Grades Available

- □ Dual issue symmetric superscalar microprocessor with instruction prefetch optimized for system level price/performance

- o 450MHz operating frequency

- □ High-performance system interface

- o Multiplexed address/data bus (SysAD) supports 2.5V, 3.3V I/O logic

- o Processor clock multipliers 2, 2.5, 3, 3.5, 4, 4.5, 5, 6, 7, 8, 9

- o Support for 64-bit or 32-bit external agents

- □ Integrated primary and secondary caches

- o All are 4-way set associative with 32-byte line size

- o 16-Kbytes instruction, 16-Kbytes data, 256-Kbytes on-chip secondary

- o Per line cache locking in primaries and secondary

- o Fast Packet Cache<sup>TM</sup> increases system efficiency in networking applications

- ☐ High-performance floating-point unit 1600MFLOPS maximum

- o Single cycle repeat rate for common single-precision operations and some double-precision operations

- o Single cycle repeat rate for single-precision combined multiply-add operations

- o Two cycle repeat rate for double-precision multiply and double-precision combined multiply-add operations

- □ MIPS IV superset instruction set architecture

- o Data PREFETCH instruction allows the processor to overlap cache miss latency and instruction execution

- o Single-cycle floating-point multiply-add

- □ Integrated memory management unit

- o Fully associative joint TLB (shared by I and D translations)

- o 64/48 dual entries map 128/96 pages

- o Variable page size

- □ Embedded application enhancements

- o Specialized DSP integer Multiply-Accumulate instructions, (MAD/MADU) and three-operand multiply instruction (MUL)

- o I&D Test/Break-point (Watch) registers for emulation & debug

- o Performance counter for system and software tuning & debug

- o Fourteen fully prioritized vectored interrupts 10 external, 2 internal, 2 software

- □ Fully static CMOS design with dynamic power down logic

- □ 216-ExposedPad<sup>TM</sup>, 24x24mm, is pin compatible with the RM7965 and RM5261A ExposedPad<sup>TM</sup> products

NOTE: 216-ExposedPad package, MIPS64 and Fast Packet Cache are Trademarks of PMC-Sierra

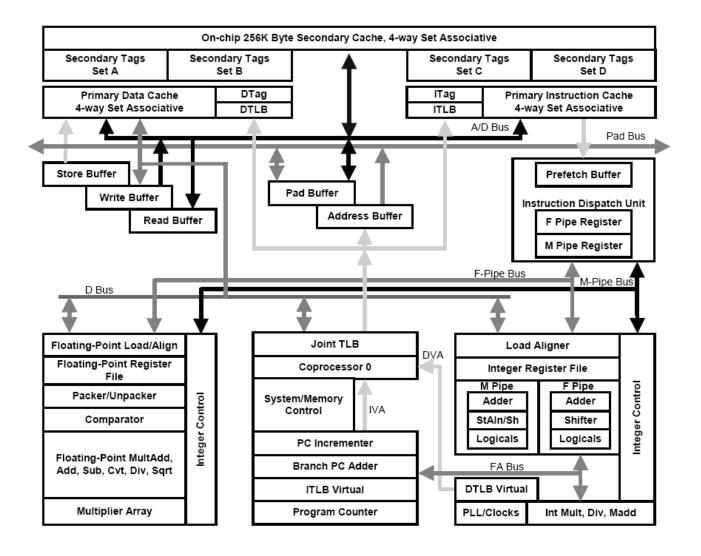

#### **BLOCK DIAGRAM**

#### **DESCRIPTION**

The MIP7365 Microprocessor is a highly integrated symmetric superscalar microprocessor capable of issuing two instructions each processor cycle. It has two highperformance 64-bit integer units as well as a high-throughput, fully pipelined 64-bit floating point unit.

The MIP7365 integrates 16 Kbytes 4-way set associative instruction and data caches along with an integrated 256 Kbytes 4-way set associative secondary cache. The primary data and secondary caches are write-back and non-blocking.

The memory management unit contains a 64/48-entry fully associative TLB and a 64-bit system interface supporting multiple outstanding reads with out-of-order return and hardware prioritized and vectored interrupts.

The MIP7365 is available in a 216-ExposedPad $^{\text{TM}}$  package. The 216-ExposedPad package is pin compatible with previous RM7965 and the RM5261A ExposedPad products.

The MIP7365 ideally suits high-end embedded control applications such as internetworking, high-performance image manipulation, high-speed printing, and 3-D visualization. The MIP7365 is also applicable to the low end workstation market where its balanced integer and floating-point performance provides outstanding price/performance.

For additional Detail Information regarding the operation of the PMC-Sierra see the latest PMC-Sierra datasheet for the RM7065C Family Microprocessors Data Sheet, Issue No. 3: January, 2004

#### **PIN DESCRIPTIONS**

The following is a list of control, data, clock, interrupt, and miscellaneous pins of MIP7365.

### **System Interface**

| PIN NAME    | TYPE         | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ExtRqst*    | Input        | External request Signals that the external agent is submitting an external request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Release*    | Output       | Release interface Signals that the processor is releasing the system interface to slave state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RdRdy*      | Input        | Read Ready Signals that an external agent can now accept a processor read.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| WrRdy*      | Input        | Write Ready Signals that an external agent can now accept a processor write request.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ValidIn*    | Input        | Valid Input Signals that an external agent is now driving a valid address or data on the bus and a valid command or data identifier on the SysCmd bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ValidOut*   | Output       | Valid output Signals that the processor is now driving a valid address or data on the SysAD bus and a valid command or data identifier on the SysCmd bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PRqst*      | Output       | Processor Request When asserted this signal requests that control of the system interface be returned to the processor. This is enabled by Mode Bit 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PAck*       | Input        | Processor Acknowledge When asserted, in response to PRqst*, this signal indicates to the processor that it has been granted control of the system interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RspSwap*    | Input        | Response Swap  RspSwap* is used by the external agent to signal the processor when it is about to return a memory reference out of order; i.e., of two outstanding memory references, the data for the second reference is being returned ahead of the data for the first reference. In order that the processor will have time to switch the address to the tertiary cache, this signal must be asserted a minimum of two cycles prior to the data itself being presented. Note that this signal works as a toggle; i.e., for each cycle that it is held asserted the order of return is reversed. By default, anytime the processor issues a second read it is assumed that the reads will be returned in order; i.e., no action is required if the reads are indeed returned in order. This is enabled by Mode Bit 26. |

| RdType      | Output       | Read Type  During the address cycle of a read request, RdType indicates whether the read request is an instruction read or a data read.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SysAD[63:0] | Input/Output | System address/data bus A 64-bit address and data bus for communication between the processor and an external agent.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SysADC[7:0] | Input/Output | System address/data check bus An 8-bit bus containing parity check bits for the SysAD bus during data cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SysCmd[8:0] | Input/Output | System command/data identifier bus  A 9-bit bus for command and data identifier transmission between the processor and an external agent.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SysCmdP     | Input/Output | System Command/Data Identifier Bus Parity For the MIP7365, unused on input and zero on output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### **Clock/Control Interface**

| PIN NAME     | TYPE  | DESCRIPTION                                                                                                                                                                                                                                                 |

|--------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Master Clock | Input | System clock  Master clock input used as the system interface reference clock. All output timings are relative to this input clock. Pipeline operation frequency is derived by multiplying this clock up by the factor selected during boot initialization. |

#### **Power Supply**

| PIN NAME | ТҮРЕ  | DESCRIPTION                                                                                                         |

|----------|-------|---------------------------------------------------------------------------------------------------------------------|

| VccInt   | Input | Power supply for core.                                                                                              |

| VccIO    | Input | Power supply for I/O.                                                                                               |

| VccP     | Input | Vcc for PLL  Quiet VccInt for the internal phase locked loop. Must be connected to VccInt through a filter circuit. |

| VccJ     | Input | Power supply used for JTAG.                                                                                         |

| Vss      | Input | Ground Return.                                                                                                      |

| VssP     | Input | Vss for PLL Quiet Vss for the internal phase locked loop. Must be connected to Vss through a filter circuit.        |

#### **Interrupt Interface**

| PIN NAME  | TYPE  | DESCRIPTION                                                                                                                    |

|-----------|-------|--------------------------------------------------------------------------------------------------------------------------------|

| INT[9:0]* | Input | Interrupt Ten general processor interrupts, bit-wise ORed with bits 9:0 of the interrupt register.                             |

| NMI*      | Input | Non-maskable interrupt Non-maskable interrupt, ORed with bit 15 of the interrupt register (bit 6 in R5000 compatibility mode). |

#### **JTAG Interface**

| PIN NAME | TYPE   | DESCRIPTION      |

|----------|--------|------------------|

| JTDI     | Input  | JTAG data in     |

| JTCK     | Input  | JTAG clock input |

| JTDO     | Output | JTAG data out    |

| JTMS     | Input  | JTAG command     |

| JTRST*   | Input  | JTAG reset.      |

#### Notes:

- 1. The **JTRST\*** input was added to the RM70xxC and RM79xx CPUs to directly control the reset to the JTAG state machine. JTAG boundary scan test equipment must be able to drive **JTRST\*** high to allow JTAG boundary scan operation.

- 2. The **JTRST\*** input must be connected to GND (**Vss**) through a  $220\Omega$  to 1 K $\Omega$  pull-down resistor to force the JTAG state machine into the reset state to allow normal operation (JTAG boundary scan mode disabled).

- 3. The JTAG interface electrical characteristics are dependent on the VccJ level chosen (2.5 V or 3.3 V).

### **Initialization Interface**

| PIN NAME   | ТҮРЕ   | DESCRIPTION                                                                                                                                                                                                                                                                      |

|------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BigEndian  | Input  | Big Endian / Little Endian Control Allows the system to change the processor addressing                                                                                                                                                                                          |

| VccOK      | Input  | Vcc is OK When asserted, this signal indicates to the MIP7365 that the VccInt power supply has been above the recommended value for more than 100 milliseconds and will remain stable. The assertion of VccOK initiates the reading of the boot-time mode control serial stream. |

| ColdReset* | Input  | Cold Reset  This signal must be asserted for a power on reset or a cold reset. ColdReset must be de-asserted synchronously with SysClock.                                                                                                                                        |

| Reset*     | Input  | Reset  This signal must be asserted for any reset sequence. It may be asserted synchronously or asynchronously for a cold reset, or synchronously to initiate a warm reset. Reset must be de-asserted synchronously with SysClock.                                               |

| ModeClock  | Output | Boot Mode Clock<br>Serial boot-mode data clock output at the system clock frequency divided by two hundred and fifty six.                                                                                                                                                        |

| Modein     | Input  | Boot Mode Data In<br>Serial boot-mode data input.                                                                                                                                                                                                                                |

#### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| SYMBOL           | RATING                                                                                | RANGE                                                   | UNITS                |

|------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------|

| $V_{TERM}$       | Terminal Voltage with respect to Vss                                                  | $-0.5^2$ to 3.9                                         | V                    |

| Тс               | Operating Temperature I = Industrial R = Extended T = Military M = Military, Screened | -40 to +85<br>-55 to +110<br>-55 to +125<br>-55 to +125 | °C<br>°C<br>°C<br>°C |

| T <sub>STG</sub> | Storage Temperature                                                                   | -55 to +125                                             | °C                   |

| $I_{IN}$         | DC Input Current                                                                      | ±20                                                     | mA                   |

| I <sub>OUT</sub> | DC Output Current <sup>4</sup>                                                        | ±20                                                     | mA                   |

#### Notes:

- 1. Stresses above those listed under "AbsoluteMaximums Rating" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2.  $\overline{V}$ IN minimum = -2.0 $\overline{V}$  for pulse width less than 15nS.  $\overline{V}$ IN maximum should not exceed +3.95 Volts.

- 3. When VIN < 0V or  $VIN > \hat{V}ccIO$ .

- 4. No more than one output should be shorted at one time. Duration of the short should not exceed more than 30 second.

#### RECOMMENDED OPERATING CONDITIONS

| GRADE      | CPU<br>SPEED | TEMP<br>(CASE)            | Vss | VccInt                              | VccIO                                                                          | VccP                                | VccJ                                                                           |

|------------|--------------|---------------------------|-----|-------------------------------------|--------------------------------------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------|

| Industrial | 450<br>MHz   | -40°C to+85°C             | 0 V | $1.3 \text{ V} \pm 50 \text{ mV}$   | $3.3 \text{ V} \pm 150 \text{ mV}$<br>or<br>$2.5 \text{ V} \pm 200 \text{ mV}$ | $1.3~\mathrm{V} \pm 50~\mathrm{mV}$ | $3.3 \text{ V} \pm 150 \text{ mV}$<br>or<br>$2.5 \text{ V} \pm 200 \text{ mV}$ |

| Extended   | 450<br>MHz   | -55°C to +110°C           | 0 V | $1.3~\mathrm{V} \pm 50~\mathrm{mV}$ | $3.3 \text{ V} \pm 150 \text{ mV}$<br>or<br>$2.5 \text{ V} \pm 200 \text{ mV}$ | $1.3~\mathrm{V} \pm 50~\mathrm{mV}$ | $3.3 \text{ V} \pm 150 \text{ mV}$<br>or<br>$2.5 \text{ V} \pm 200 \text{ mV}$ |

| Military   | 450<br>MHz   | -55°C to +125°C<br>Note 5 | 0 V | 1.3 V ± 50 mV                       | $3.3 \text{ V} \pm 150 \text{ mV}$<br>or<br>$2.5 \text{ V} \pm 200 \text{ mV}$ | $1.3 \text{ V} \pm 50 \text{ mV}$   | $3.3 \text{ V} \pm 150 \text{ mV}$<br>or<br>$2.5 \text{ V} \pm 200 \text{ mV}$ |

#### Notes

- 1. VccIO should not exceed VccInt by greater than 2.5 V during the power-up sequence.

- 2. Applying a logic high state to any I/O pin before VccInt becomes stable is not recommended.

- 3. As specified in IEEE 1149.1 (JTAG), the JTMS pin must be held high during reset to avoid entering JTAG test mode. Refer to the RM7000

- 4. VccP must be connected to VccInt through a passive filter circuit. See RM7000 User Manual fo recommended circuit.

- 5. Contact factory for extended military temperature range products (CQFP hermetic MCM packages will be screened at -55°C to + 125°C).

#### DC ELECTRICAL CHARACTERISTICS

#### VccIO = 3.15 - 3.45V

| PARAMETER | MINIMUM      | MAXIMUM      | CONDITIONS             |

|-----------|--------------|--------------|------------------------|

| Vol       | -            | 0.2V         | $ IOUT  = 100\mu A$    |

| Voн       | VccIO - 0.2V | -            |                        |

| Vol       | -            | 0.4V         | IOUT  = 2mA            |

| Voн       | 2.4V         | -            |                        |

| VIL       | -0.3V        | 0.8V         | -                      |

| Vih       | 2.0V         | VccIO + 0.3V | -                      |

| IIN       |              | ±5μΑ<br>±5μΑ | VIN = 0<br>VIN = VccIO |

#### VccIO = 2.3V - 2.7V

| PARAMETER | MINIMUM | MAXIMUM        | CONDITIONS             |

|-----------|---------|----------------|------------------------|

| Vol       | -       | 0.2V           | $ IOUT  = 100\mu A$    |

| Voн       | 2.1V    | -              |                        |

| Vol       | -       | 0.4V           | IOUT  = 1mA            |

| Voн       | 2.0V    | -              |                        |

| Vol       | -       | 0.7V           | Iout  = 2mA            |

| Voн       | 1.7V    | -              |                        |

| VIL       | -0.3V   | 0.7V           | -                      |

| Vih       | 1.7V    | VccIO + 0.3V   | -                      |

| IIN       | -<br>-  | ±15μΑ<br>±15μΑ | VIN = 0<br>VIN = VccIO |

#### **POWER CONSUMPTION**

|                         |  |                                            | CPU SPEED       |                 |  |

|-------------------------|--|--------------------------------------------|-----------------|-----------------|--|

| PARAMETER               |  | CONDITIONS                                 | 450MHz<br>(IND) | 450MHz<br>(MIL) |  |

|                         |  |                                            | MAX             | MAX             |  |

| VCCINT Standby<br>Power |  |                                            | 1350            | 1350            |  |

| (mWatts)                |  | Maximum with no FPU operation <sup>2</sup> | 3100            | 3250            |  |

|                         |  | Maximum worst case instruction mix         | 3250            | 3400            |  |

- $1. \ Worst\ case\ supply\ voltage\ (maximum\ VccInt)\ with\ worst\ case\ temperature\ (maximum\ TCASE).$

- 2. Dhrystone 2.1 instruction mix.3. I/O supply power is application dependant, but typically <20% of VccInt.</li>

#### **AC CHARACTERISTICS**

#### **CAPACITIVE LOAD DERATION**

| SYMBOL | PARAMETER   | MINIMUM | MAXIMUM | UNITS   | Mode  |

|--------|-------------|---------|---------|---------|-------|

| CLD    | Load Derate | -       | 2       | ns/25pF | LVTTL |

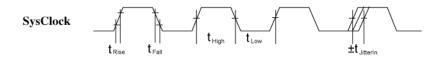

#### **CLOCK PARAMETERS**

|                                 |                       |                  | BUS SPEED CONDITIONS LVTTL |      |       |

|---------------------------------|-----------------------|------------------|----------------------------|------|-------|

| PARAMETER                       | SYMBOL                | TEST CONDITIONS  |                            |      | UNITS |

|                                 |                       |                  | MIN                        | MAX  |       |

| SysClock High                   | t <sub>SCHigh</sub>   | Transition ≤ 2ns | 3                          | -    | ns    |

| SysClock Low                    | t <sub>SCLow</sub>    | Transition ≤ 2ns | 3                          | -    | ns    |

| SysClock Frequency <sup>1</sup> |                       |                  | 33.3                       | 133  | MHz   |

| SysClock Period                 | t <sub>SCP</sub>      |                  | 7.5                        | 30   | ns    |

| Clock Jitter for SysClock       | t <sub>JitterIn</sub> |                  | -                          | ±150 | ps    |

| SysClock Rise Time              | t <sub>SCRise</sub>   |                  | -                          | 2    | ns    |

| SysClock Fall Time              | t <sub>SCFall</sub>   |                  | -                          | 2    | ns    |

| ModeClock Period                | t <sub>ModeCKP</sub>  |                  | -                          | 256  | ns    |

| JTAG Clock Period               | t <sub>JTAGCKP</sub>  |                  | 4                          | -    | ns    |

#### Notes:

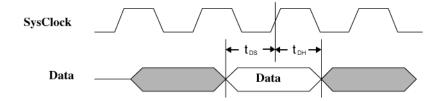

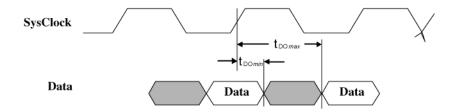

#### SYSTEM INTERFACE PARAMETERS

|                              |                 | TEST CONDITIONS <sup>5,6</sup>                            |      | I/O TYPE  |    |  |

|------------------------------|-----------------|-----------------------------------------------------------|------|-----------|----|--|

| PARAMETER <sup>1</sup>       | SYM             |                                                           |      | LVTTL I/O |    |  |

|                              |                 |                                                           | MIN  | MAX       |    |  |

| Data Output <sup>2,6,7</sup> | $t_{DO}$        | LVTTL (VccIO = 3.3V): mode[14:13] = 10 (fastest)          | 0.75 | 4.5       | ns |  |

|                              |                 | LVTTL (VccIO = $3.3$ V): mode[ $14:13$ ] = $01$ (slowest) | 0.75 | 5.5       | ns |  |

| Data Setup <sup>4</sup>      | $t_{DS}$        | $t_{RISE}$ = See above table                              | 2.5  | -         | ns |  |

| Data Hold <sup>4</sup>       | t <sub>DH</sub> | t <sub>FALL</sub> = See above table                       | 1.0  | -         | ns |  |

#### Notes

- 1. In LVTTL mode, timings are measured from 0.425 x **VccIO** of clock to 0.425 x **VccIO** of signal for 3.3V I/O, and from 0.48 x **VccIO** of clock to 0.48 x **VccIO** of signal for 2.5V I/O. Input Rise/Fall time = 1V/1ns.

- 2. Capacitive load for all LVTTL maximum output timings is 50 pF. Minimum output timings are for theoretical no load conditions untested.

- 4. Data Output timing applies to all signal pins whether tristate I/O or output only.

- 5. Setup and Hold parameters apply to all signal pins whether tristate I/O or input only.

- 6. Only mode 14:13 = 01 is tested and guaranteed.

- 7. Data shown is for 3.3 V I/O. For 2.5 V I/O: derate too min by 0.25 nS, and too max by 0.5 nS. Mode setting is mode [14:13] = 10 (fastest) or 01 (slowest).

<sup>1.</sup> Operation of the MIP7365 is only guaranteed with the Phase Loop enabled.

#### TIMING DIAGRAMS

#### **CLOCK TIMING**

#### SYSTEM INTERFACE TIMING

(SysAD, SysCmd, ValidIn\*, ValidOut\*, etc.)

#### **INPUT TIMING**

#### **OUTPUT TIMING**

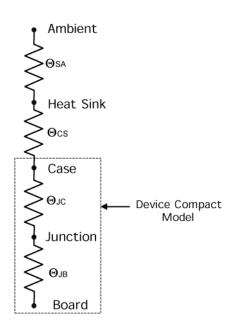

#### THERMAL INFORMATION

This product is designed to operate over a wide temperature range when used with a heat sink.

| Maximum long-term operating junction temperature to ensure adequate long-term life                      | TBD at 450 MHz |

|---------------------------------------------------------------------------------------------------------|----------------|

| Maximum junction temperature for short-term excursions with guaranteed continued functional performance | TBD at 450 MHz |

| Minimum ambient temperature                                                                             | TBD            |

| Device Compact Model <sup>2</sup> |       |  |  |

|-----------------------------------|-------|--|--|

| θ <sub>JC</sub> (°C/W)            | 0.28  |  |  |

| θлв (°С/W)                        | 3.60  |  |  |

| θја (°С/W)                        | 10.00 |  |  |

| Operating power is dissipated in any package (watts) offered at worst case power supply |                               |      |  |  |

|-----------------------------------------------------------------------------------------|-------------------------------|------|--|--|

| Power at 450MHz                                                                         | VccInt = 1.3 V, VccIO = 3.3 V | 2.8W |  |  |

#### Notes

- 1. Short-term is understood as the definition stated in Telcordia Generic Requirements GR-63-Core.

- 2.  $\theta_{JC}$ , the junction-to-case thermal resistance,  $\theta_{JB}$ , the junction-to-board thermal resistance are obtained from Package vendor.

- 3.  $\theta$ SA is the thermal resistance of the heat sink to ambient.  $\theta$ CS is the thermal resistance of the heat sink attached material.

- 4. The actual  $\theta$ SA required may vary according to the air speed at the location of the device in the system with all the components in place.

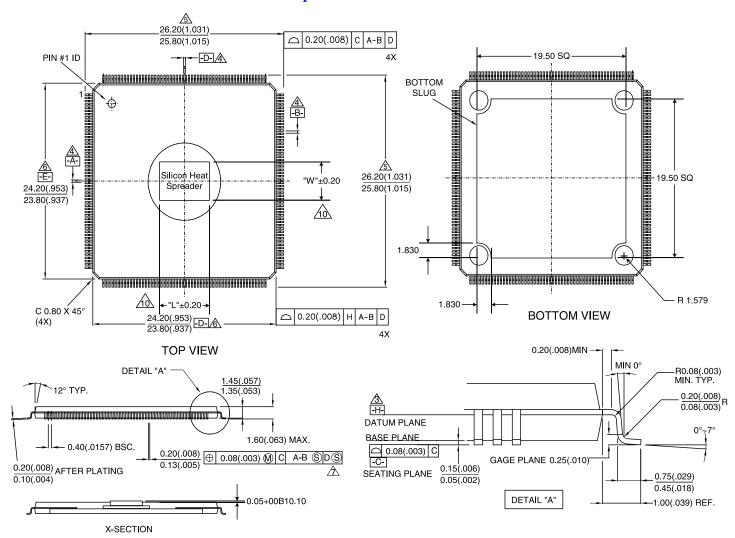

#### MIP7365 216-ExposedPad PACKAGE OUTLINE

#### Notes

1. Controlling dimensions: millimeters. Inches are shown in parentheses. [] is reference.

2. Dimensions and tolderancing per ASME Y 14.5M01994.

Datum plane "H" is located at mold parting line and is coincident where the lead exits the plastic body at the bottom of the parting line.

Datums "A-B" and "D" to be determined at datum plane "H".

To be determined at the seating plane "C".

These dimensions to be determined at datum plane "H". These dimensions to do not include mold protrusion. Allowable protrusion is 0.25 mm (.010") per side.

Lead width does not include dambar protrusion. Allowable dambar protrusion shall be 0.08 mm/0.003" total in excess of these dimensions at maximum material condition.

- 8. Top heat spreader is silicon.

- 9. Bottom heat spreader is copper, CDA-110.

10. Dimension is silicon heat slug. Die type RM7065C: W=3.67, L=4.25.

- 11. Leads plating: 85/15 Sn/Pb Alloy (standard), 99/1 Sn/Bi Alloy (lead-free).

- 12. Bottom slug plating: 85/15 Sn/Pb Alloy (standard), 99/1 Sn/Bi Alloy (lead-free).

## MIP7365 216-ExposedPad NUMERICAL PINOUT vs FUNCTION $^{1,2}$

| PIN | FUNCTION       | PIN | FUNCTION       | PIN | FUNCTION       | PIN | FUNCTION  |

|-----|----------------|-----|----------------|-----|----------------|-----|-----------|

| 1   | VccIO          | 39  | SysAD48        | 77  | VccIO          | 115 | JTDO      |

| 2   | Do Not Connect | 40  | SysAD16        | 78  | SysCmd5        | 116 | VccIO     |

| 3   | Do Not Connect | 41  | VccInt         | 79  | SysCmd4        | 117 | ModeClock |

| 4   | Do Not Connect | 42  | BigEndian      | 80  | SysCmd3        | 118 | VccInt    |

| 5   | Do Not Connect | 43  | VccIO          | 81  | SysCmd2        | 119 | PRQST*    |

| 6   | VccInt         | 44  | VccOK          | 82  | VccInt         | 120 | PACK*     |

| 7   | SysAD59        | 45  | ColdReset*     | 83  | SysCmd1        | 121 | RspSwap*  |

| 8   | SysAD27        | 46  | Reset*         | 84  | SysCmd0        | 122 | VccIO     |

| 9   | SysAD58        | 47  | ExtRqst*       | 85  | Do Not Connect | 123 | VccInt    |

| 10  | VccInt         | 48  | NMI*           | 86  | Do Not Connect | 124 | SysAD47   |

| 11  | VccIO          | 49  | VccInt         | 87  | Do Not Connect | 125 | SysAD15   |

| 12  | SysAD26        | 50  | INT9*          | 88  | VccInt         | 126 | VccInt    |

| 13  | VccInt         | 51  | INT8*          | 89  | Do Not Connect | 127 | SysAD46   |

| 14  | SysAD57        | 52  | INT7*          | 90  | Do Not Connect | 128 | SysAD14   |

| 15  | SysAD25        | 53  | INT6*          | 91  | VccInt         | 129 | SysAD45   |

| 16  | SysAD56        | 54  | VccIO          | 92  | Do Not Connect | 130 | SysAD13   |

| 17  | SysAD24        | 55  | VccJ           | 93  | Do Not Connect | 131 | SysAD44   |

| 18  | SysAD55        | 56  | VccIO          | 94  | Do Not Connect | 132 | SysAD12   |

| 19  | SysAD23        | 57  | INT5*          | 95  | VccInt         | 133 | VccInt    |

| 20  | VccInt         | 58  | INT4*          | 96  | Do Not Connect | 134 | SysAD43   |

| 21  | SysAD54        | 59  | INT3*          | 97  | Master Clock   | 135 | SysAD11   |

| 22  | SysAD22        | 60  | INT2*          | 98  | VssP           | 136 | VccIO     |

| 23  | SysAD53        | 61  | INT1*          | 99  | VccP           | 137 | VccIO     |

| 24  | SysAD21        | 62  | INT0*          | 100 | Release*       | 138 | SysAD42   |

| 25  | VccIO          | 63  | VccInt         | 101 | ValidOut*      | 139 | SysAD10   |

| 26  | VccIO          | 64  | VccInt         | 102 | ValidIn*       | 140 | SysAD41   |

| 27  | VccIO          | 65  | Do Not Connect | 103 | WrRdy*         | 141 | SysAD9    |

| 28  | SysAD52        | 66  | Do Not Connect | 104 | RdRdy*         | 142 | VccInt    |

| 29  | SysAD20        | 67  | Do Not Connect | 105 | Do Not Connect | 143 | SysAD40   |

| 30  | VccInt         | 68  | VccIO          | 106 | ModeIn         | 144 | SysAD8    |

| 31  | SysAD51        | 69  | Do Not Connect | 107 | RdType         | 145 | SysAD39   |

| 32  | SysAD19        | 70  | Do Not Connect | 108 | Do Not Connect | 146 | SysAD7    |

| 33  | SysAD50        | 71  | Do Not Connect | 109 | VccJ           | 147 | SysAD38   |

| 34  | SysAD18        | 72  | VccInt         | 110 | JTRST*         | 148 | SysAD6    |

| 35  | SysAD49        | 73  | SysCmdP        | 111 | VccIO          | 149 | VccInt    |

| 36  | SysAD17        | 74  | SysCmd8        | 112 | JTMS           | 150 | SysAD37   |

| 37  | VccIO          | 75  | SysCmd7        | 113 | JTCK           | 151 | SysAD5    |

| 38  | VccInt         | 76  | SysCmd6        | 114 | JTDI           | 152 | SysAD36   |

### MIP7365 216-ExposedPad NUMERICAL PINOUT vs FUNCTION <sup>1,2</sup> CON'T

| to-Expo | seaPaa NUMERIC | CAL PINC | JUI VS FUNCTIO         |

|---------|----------------|----------|------------------------|

| PIN     | FUNCTION       | PIN      | FUNCTION               |

| 153     | SysAD4         | 191      | VccIO                  |

| 154     | VccInt         | 192      | SysADC7                |

| 155     | Do Not Connect | 193      | SysADC3                |

| 156     | Do Not Connect | 194      | VccInt                 |

| 157     | VccInt         | 195      | SysADC6                |

| 158     | Do Not Connect | 196      | VccIO                  |

| 159     | Do Not Connect | 197      | SysADC2                |

| 160     | Do Not Connect | 198      | SysAD63                |

| 161     | Do Not Connect | 199      | SysAD31                |

| 162     | VccIO          | 200      | Do Not Connect         |

| 163     | Do Not Connect | 201      | SysAD62                |

| 164     | VccIO          | 202      | SysAD30                |

| 165     | VccIO          | 203      | VccIO                  |

| 166     | Do Not Connect | 204      | VccIO                  |

| 167     | Do Not Connect | 205      | VccInt                 |

| 168     | Do Not Connect | 206      | SysAD61                |

| 169     | Do Not Connect | 207      | SysAD29                |

| 170     | SysAD35        | 208      | VccInt                 |

| 171     | SysAD3         | 209      | SysAD60                |

| 172     | VccInt         | 210      | SysAD28                |

| 173     | SysAD34        | 211      | Do Not Connect         |

| 174     | SysAD2         | 212      | Do Not Connect         |

| 175     | VccInt         | 213      | Do Not Connect         |

| 176     | VccIO          | 214      | Do Not Connect         |

| 177     | VccInt         | 215      | VccIO                  |

| 178     | SysAD33        | 216      | VccIO                  |

| 179     | SysAD1         |          |                        |

| 180     | SysAD32        |          |                        |

| 181     | SysAD0         |          | Notes:                 |

| 182     | SysADC5        |          | 1. The expos           |

| 183     | SysADC1        |          | acts as the conduction |

| 184     | VccIO          |          | circuit boa            |

| 185     | VccInt         |          | 2. See PMC-            |

| 186     | SysADC4        |          | Application            |

| 187     | SysADC0        |          |                        |

| 188     | Do Not Connect |          |                        |

|         |                |          |                        |

- 1. The exposed pad on the bottom of the ExposedPad package acts as the sole device ground and as the primary heat conduction path. As such, it must be soldered to the printed circuit board.

- See PMC-2030256, 216-ExposedPad Design Guidelines Application Note for details.

189

190

VccInt VccIO

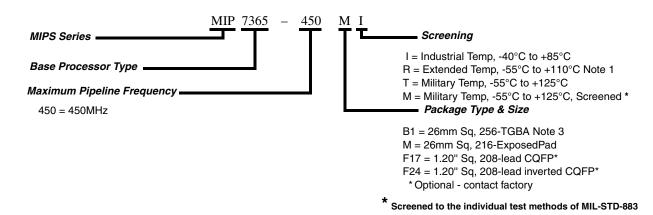

#### SAMPLE ORDERING INFORMATION

| PART NUMBER   | SCREENING                                                    | PIPELINE FREQ<br>(MHZ) Note 2 | PACKAGE        |

|---------------|--------------------------------------------------------------|-------------------------------|----------------|

| MIP7365-450MI | Industrial Temperature Range<br>-40°C to +85°C Testing       | 450                           | 216-ExposedPad |

| MIP7365-450MR | Extended Temperature Range<br>-55°C to +110°C Testing Note 1 |                               |                |

#### Notes

- 1. Contact factory for extended military temperature range products (CQFP hermetic MCM package will be screened at -55°C to + 125°C).

- 2. Contact factory for higher speed product options.

- 3. Contact factory for availability.

#### PART NUMBER BREAKDOWN

PLAINVIEW, NEW YORK

INTERNATIONAL

NORTHEAST

Toll Free: 800-THE-1553

Tel: 805-778-9229

Tel: 603-888-3975

Fax: 516-694-6715

Fax: 805-778-1980

Fax: 603-888-4585

SE AND MID-ATLANTIC

WEST COAST

CENTRAL

Tel: 321-951-4164

Tel: 949-362-2260

Tel: 719-594-8017

Fax: 321-951-4254

Fax: 949-362-2266

Fax: 719-594-8468

A passion for performance.

www.aeroflex.com info-ams@aeroflex.com

Aeroflex Microelectronic Solutions reserves the right to change at any time without notice the specifications, design, function, or form of its products described herein. All parameters must be validated for each customer's application by engineering. No liability is assumed as a result of use of this product. No patent licenses are implied. All trademarks are acknowledged. Parent company Aeroflex, Inc. 2003.

Our passion for performance is defined by three attributes represented by these three icons: solution-minded, performance-driven and customer-focused