# Standard Products UT22VP10 Universal RADPAL<sup>™</sup>

Data Sheet

### FEATURES

- □ High speed Universal RADPAL

- t<sub>PD</sub>: 15.5ns, 20ns, 25ns maximum

- f<sub>MAX1</sub>: 33MHz maximum external frequency

- Supported by industry-standard programmer

- Amorphous silicon anti-fuse

- □ Asynchronous and synchronous RADPAL operation

- Synchronous PRESET

- Asynchronous RESET

- □ Up to 22 input and 10 output drivers may be configured - CMOS & TTL-compatible input and output levels

- CMOS & TTL-compatible in

Three-state output drivers

- Three-state output unvers

- □ Variable product terms, 8 to 16 per output

- □ 10 user-programmable output macrocells

- Registered or combinatorial operation

- Output driver polarity control selectable

- Two feedback paths available

- Radiation-hardened process and design; total dose irradiation testing to MIL-STD-883, Method 1019

- Total dose: 1.0E6 rads(Si)

- Upset threshold 50 MeV-cm<sup>2</sup>/mg (min)

- Latchup immune(LET>109 MeV-cm<sup>2</sup>/mg)

- □ QML Q & V compliant

- □ Packaging options:

- 24-pin 100-mil center DIP (0.300 x 1.2)

- 24-lead flatpack (.45 x .64)

- 28-lead quad-flatpack (.45 x .45)

- □ Standard Military Drawing 5962-94754 available

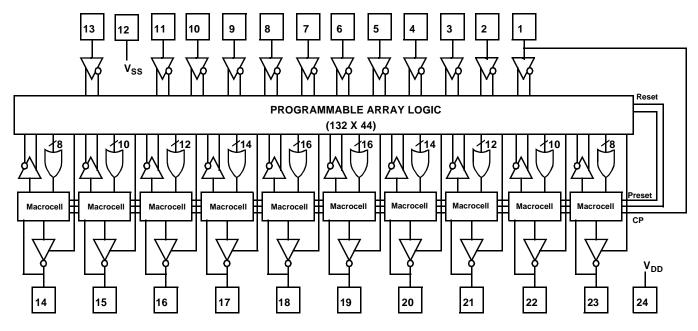

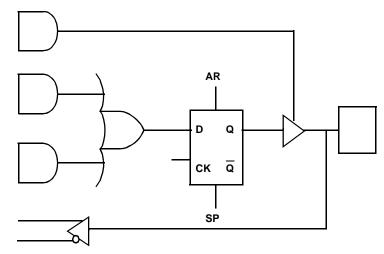

Figure 1. Block Diagram

November 2000

### PRODUCT DESCRIPTION

The UT22VP10 RADPAL is a fuse programmable logic array device. The familiar sum-of-products (AND-OR) logic structure is complemented with a programmable macrocell. The UT22VP10 is available in 24-pin DIP, 24-lead flatpack, and 28-lead quad-flatpack package offerings providing up to 22 inputs and 10 outputs. Amorphous silicon anti-fuse technology provides the programming of each output. The user specifies whether each of the potential outputs is registered or combinatorial. Output polarity is also individually selected, allowing for greater flexibility for output configuration. A unique output enable function allows the user to configure bidirectional I/O on an individual basis.

The UT22VP10 architecture implements variable sum terms providing 8 to 16 product terms to outputs. This feature provides the user with increased logic function flexibility. Other features include common synchronous preset and asynchronous reset. These features eliminate the need for performing the initialization function.

The UT22VP10 provides a device with the flexibility to implement logic functions in the 500 to 800 gate complexity. The flexible architecture supports the implementation of logic functions requiring up to 21 inputs and only a single output or down to 12 inputs and 10 outputs. Development and programming support for the UT22VP10 is provided by DATA I/O.

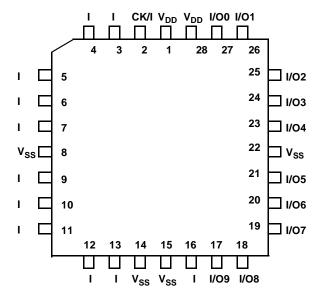

### **DIP & FLATPACK PIN CONFIGURATION**

#### **QUAD-FLATPACK PIN CONFIGURATION**

#### **PIN NAMES**

| CK/I            | Clock/Data Input  |

|-----------------|-------------------|

| Ι               | Data Input        |

| I/O             | Data Input/Output |

| V <sub>DD</sub> | Power             |

| V <sub>SS</sub> | Ground            |

### FUNCTION DESCRIPTION

The UT22VP10 RADPAL implements logic functions as sumof-products expressions in a one-time programmable-AND/ fixed-OR logic array. User-defined functions are created by programming the connections of input signals into the array. User-configurable output structures in the form of I/O macrocells further increase logic flexibility.

| C <sub>2</sub> | C <sub>1</sub> | C <sub>0</sub> Output Type Pola |               | Polarity                  | Feedback   |

|----------------|----------------|---------------------------------|---------------|---------------------------|------------|

| 0              | 0              | 0                               | Registered    | Active LOW                | Registered |

| 0              | 0              | 1                               | Registered    | Registered Active HIGH    |            |

| Х              | 1              | 0                               | Combinatorial | Combinatorial Active LOW  |            |

| Х              | 1              | 1                               | Combinatorial | Combinatorial Active HIGH |            |

| 1              | 0              | 0                               | Registered    | Registered Active LOW     |            |

| 1              | 0              | 1                               | Registered    | ed Active HIGH            |            |

Table 1. Macrocell Configuration Table<sup>1, 2, 3</sup>

#### Notes:

1.0 equals programmed low or programmed.

2. 1 equals programmed high or unprogrammed.

3. X equals don't care.

### **OVERVIEW**

The UT22VP10 RADPAL architecture (see figure 1) has 12 dedicated inputs and 10 I/Os to provide up to 22 inputs and 10 outputs for creating logic functions. At the core of the device is a one-time programmable anti-fuse AND array that drives a fixed OR array. With this structure, the UT22VP10 can implement up to 10 sum-of-products logic expressions.

Associated with each of the 10 OR functions is a macrocell which is independently programmed to one of six different configurations. The one-time programmable macro cells allow each I/O to create sequential or combinatorial logic functions with either Active-High or Active-Low polarity.

### LOGIC ARRAY

The one-time programmable AND array of the UT22VP10 RADPAL is formed by input lines intersecting product terms. The input lines and product terms are used as follows:

44 input lines:

- 24 input lines carry the true and complement of the signals applied to the input pins

- 20 lines carry the true and complement values of feedback or input signals from the 10 I/Os

132 product terms:

- 120 product terms (arranged in 2 groups of 8, 10, 12, 14, and 16) used to form logic sums

- 10 output enable terms (one for each I/O)

- 1 global synchronous preset term

- 1 global asynchronous reset term

At each input-line/product-term intersection there is an antifuse cell which determines whether or not there is a logical connection at that intersection. A product term which is connected to both the true and complement of an input signal will always be logical zero, and thus will not effect the OR function that it drives. When there are no connections on a product term a Don't Care state exists and that term will always be a logical one.

### PRODUCT TERMS

The UT22VP10 provides 120 product terms that drive the 10 OR functions. The 120 product terms connect to the outputs in two groups of 8, 10, 12, 14, and 16 to form logical sums.

### MACROCELL ARCHITECTURE

The output macrocell provides complete control over the architecture of each output. Configuring each output independently permits users to tailor the configuration of the UT22VP10 to meet design requirements.

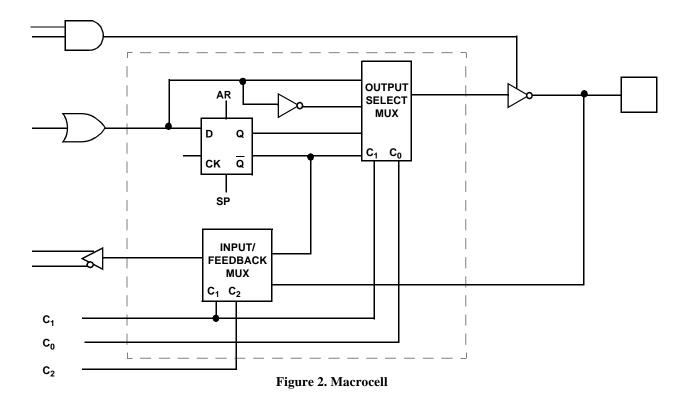

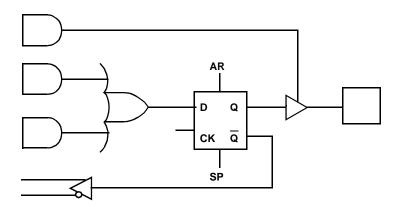

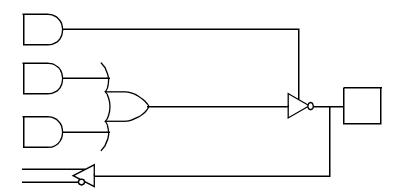

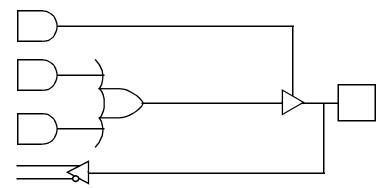

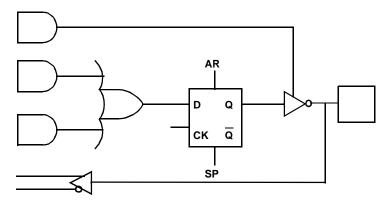

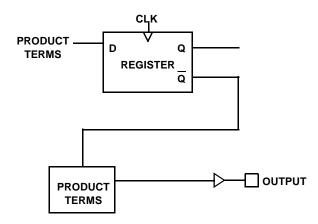

Each I/O macrocell (see figure 2) consists of a D flip-flop and two signal-select multiplexers. Three configuration select bits controlling the multiplexers determine the configuration of each UT22VP10 macrocell (see table 1). The configuration select bits determine output polarity, output type (registered or combinatorial) and input feedback type (registered or I/O). See figure 3 for equivalent circuits for the macrocell configurations.

### **OUTPUT FUNCTIONS**

The signal from the OR array may be fed directly to the output pin (combinatorial function) or latched in the D flip-flop (registered function). The D flip-flop latches data on the rising edge of the clock. When the synchronous preset term is satisfied, the Q output of the D flip-flop output will be set logical one at the next rising edge of the clock input. Satisfying the asynchronous clear term sets Q logical zero, regardless of the clock state. If both terms are satisfied simultaneously, the clear will override the preset.

### **OUTPUT POLARITY**

Each macrocell can be configured to implement Active-High or Active-Low logic. Programmable polarity eliminates the need for external inverters.

### OUTPUT ENABLE

The output of each I/O macrocell can be enabled or disabled under the control a programmable output enable product term. The output signal is propagated to the I/O pin when the logical conditions programmed on the output enable term are satisfied. Otherwise, the output buffer is driven to the high-impedance state.

The output enable term allows the I/O pin to function as a dedicated input, dedicated output, or bidirectional I/O. When every connection is unprogrammed, the output enable product term permanently enables the output buffer and yields a dedicated output. If every connection is programmed, the enable term is logically low and the I/O functions as a dedicated input.

### **REGISTER FEEDBACK**

The feedback signal to the AND array is taken from the Q output when the I/O macrocell implements a registered function  $(C_2 = 0, C_1 = 0)$ .

### **BIDIRECTIONAL I/O**

The feedback signal is taken from the I/O pin when the macrocell implements a combinatorial function ( $C_1 = 1$ ) or a registered function ( $C_2 = 1, C_1 = 0$ ). In this case, the pin can be used as a dedicated input, a dedicated output, or a bidirectional I/O.

### **POWER-ON RESET**

To ease system initialization, all D flip-flops will power-up to a reset condition and the Q output will be low. The actual output of the UT22VP10 will depend on the programmed output polarity. The reset delay time is  $5\mu$ s maximum. See the Power-up Reset section for a more descriptive list of POR requirements.

### ANTI-FUSE SECURITY

The UT22VP10 provides a security bit that prevents unauthorized reading or copying of designs programmed into the device. The security bit is set by the PLD programmer at the conclusion of the programming cycle. Once the security bit is set it is no longer possible to verify (read) or program the UT22VP10. **NOTE: UTMC does not recommend using the UT22VP10 unless the security fuse has been programmed. The security bit must be blown to ensure proper functionality of the UT22VP10.**

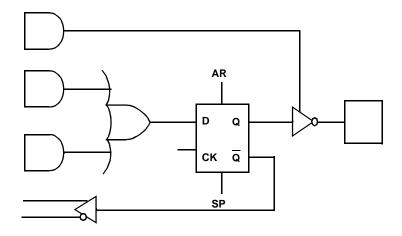

Registered Feedback, Registered, Active-Low Output  $(C_2 = 0, C_1 = 0, C_0 = 0)$

Registered Feedback, Registered, Active-High Output ( $C_2 = 0, C_1 = 0, C_0 = 1$ )

I/O Feedback, Combinatorial, Active-Low Output ( $C_2 = X, C_1 = 1, C_0 = 0$ )

Figure 3. Macrocell Configuration (continued on next page)

I/O Feedback, Combinatorial, Active-High Output ( $C_2 = X, C_1 = 1, C_0 = 1$ )

I/O Feedback, Registered, Active-Low Output ( $C_2 = 1, C_1 = 0, C_0 = 0$ )

I/O Feedback, Registered, Active-High Output  $(C_2 = 1, C_1 = 0, C_0 = 1)$ Figure 3. Macrocell Configuration

### ABSOLUTE MAXIMUM RATINGS<sup>1</sup>

| SYMBOL                        | PARAMETER                               | LIMIT        | UNITS |

|-------------------------------|-----------------------------------------|--------------|-------|

| V <sub>DD</sub>               | Supply voltage                          | -0.3 to 7.0  | V     |

| V <sub>I/O</sub> <sup>2</sup> | Input voltage any pin                   | -0.3 to +7.0 | V     |

| T <sub>STG</sub>              | Storage Temperature range               | -65 to +150  | °C    |

| TJ                            | Maximum junction temperature            | +175         | °C    |

| T <sub>S</sub>                | Lead temperature (soldering 10 seconds) | +300         | °C    |

| $\Theta_{\rm JC}$             | Thermal resistance junction to case     | 20           | °C/W  |

| II                            | DC input current                        | ±10          | mA    |

| P <sub>D</sub> <sup>3</sup>   | Maximum power dissipation               | 1.6          | W     |

| I <sub>O</sub>                | Output sink current                     | 12           | mA    |

Notes:

Stresses outside the listed absolute maximum ratings may cause permanent damage to the device. This is a stress rating only, functional operation of the device at these or any other conditions beyond limits indicated in the operational sections is not recommended. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Minimum voltage is -0.6V<sub>DD</sub> which may undershoot to -2.0V<sub>DD</sub> for pulses of less than 20ns. Maximum output pin voltage is V<sub>DD</sub> +0.75V<sub>DD</sub> which may overshoot to +7.0V<sub>DD</sub> for pulses of less than 20ns.

3.  $(I_{CC} \max + I_{OS}) 5.5V.$

### **RECOMMENDED OPERATING CONDITIONS**

| SYMBOL                       | PARAMETER             | LIMIT                | UNITS |

|------------------------------|-----------------------|----------------------|-------|

| V <sub>DD</sub> <sup>1</sup> | Supply voltage        | 4.5 to 5.5           | V     |

| V <sub>IN</sub>              | Input voltage any pin | 0 to V <sub>DD</sub> | V     |

| T <sub>C</sub>               | Temperature range     | -55 to + 125         | °C    |

Notes:

1. See page 12 for minimum  $V_{\mbox{\scriptsize DD}}$  requirements at power-up.

### DC ELECTRICAL CHARACTERISTICS 1,7

| SYMBOL                          | PARAMETER                                                                                         | CONDITION                                                     | MINIMUM               | MAXIMUM               | UNIT |

|---------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------|-----------------------|------|

| V <sub>IL</sub>                 | Low-level input voltage                                                                           | TTL                                                           |                       | .8                    | V    |

| V <sub>IH</sub>                 | High-level input voltage                                                                          | TTL                                                           | 2.2                   |                       | V    |

| V <sub>IL</sub>                 | Low-level input voltage                                                                           | CMOS                                                          |                       | .3*V <sub>DD</sub>    | V    |

| V <sub>IH</sub>                 | High-level input voltage                                                                          | CMOS                                                          | .7*V <sub>DD</sub>    |                       | V    |

| V <sub>OL</sub>                 | Low-level output voltage                                                                          | $I_{OL} = 12.0 \text{mA}, V_{DD} = 4.5 \text{V} (\text{TTL})$ |                       | .4                    | V    |

| V <sub>OH</sub>                 | High-level output voltage                                                                         | $I_{OH} = -12.0 \text{mA}, V_{DD} = 4.5 \text{V} (TTL)$       | 2.4                   |                       | V    |

| V <sub>OL</sub>                 | Low-level output voltage                                                                          | $I_{OL} = 200$ mÅ, $V_{DD} = 4.5V$ (CMOS)                     |                       | V <sub>SS</sub> +0.05 | V    |

| V <sub>OH</sub>                 | High-level output voltage                                                                         | $I_{OH} = -200$ mÅ, $V_{DD} = 4.5 V (CMOS)$                   | V <sub>DD</sub> -0.05 |                       | V    |

| I <sub>IN</sub>                 | Input leakage current                                                                             | $V_{IN} = V_{DD}$ and $V_{SS}$                                | -10                   | 10                    | μΑ   |

| I <sub>OZ</sub>                 | Three-state output leakage current                                                                | $V_{O} = V_{DD}$ and $V_{SS}$ , $V_{DD} = 5.5V$               | -10                   | 10                    | μΑ   |

| I <sub>OS</sub> <sup>4,5</sup>  | Short-circuit output cur-<br>rent                                                                 | $V_{DD} = 5.5V, V_O = V_{DD}$ $V_{DD} = 5.5V, V_O = 0V$       | -160                  | 160                   | mA   |

| C <sub>IN</sub> <sup>5,6</sup>  | Input capacitance                                                                                 | =1MHz @0V                                                     |                       | 15                    | pF   |

| C <sub>I/O</sub> <sup>5,6</sup> | Bidirectional capacitance                                                                         | ¦=1MHz @0V                                                    |                       | 15                    | pF   |

| I <sub>DD</sub> <sup>5</sup>    | Supply current: Output<br>three-state, worst-case pat-<br>tern programmed,<br> =f <sub>MAX1</sub> | V <sub>DD</sub> = 5.5V                                        |                       | 120                   | mA   |

| I <sub>DDQ</sub>                | Supply current:<br>Unprogrammed                                                                   | $V_{DD} = 5.5V$                                               |                       | 25                    | mA   |

Notes:

1. All specifications valid for radiation dose ≤ 1E6 rads(Si).

2. See page 12 for minimum V<sub>DD</sub> requirements at power-up.

3. Maximum allowable relative shift equals 50mV.

4. Duration not to exceed 1 second, one output at a time.

5. Tested initially and after any design or process changes that affect that parameter and, therefore, shall be guaranteed to the limit specified.

6. All pins not being tested are to be open

6. All pins not being tested are to be open.7. CMOS levels only tested on CMOS devices. TTL levels only tested on TTL devices.

## AC CHARACTERISTICS READ CYCLE (Post-Radiation) <sup>1,2</sup>

| $(V_{DD}^3 = 5.0V \pm 10\%; -55^{\circ}C < T_C < +125^{\circ}C)$ |

|------------------------------------------------------------------|

|------------------------------------------------------------------|

| SYMBOL                           | PARAMETER                                                            | 22VP<br>MIN | 10-15.5<br>MAX | 22VF<br>MIN | P10-20<br>MAX | 22VI<br>MIN | P10-25<br>MAX | UNIT |

|----------------------------------|----------------------------------------------------------------------|-------------|----------------|-------------|---------------|-------------|---------------|------|

| $t_{PD}^{4,5,6}$                 | Input to output propagation delay                                    |             | 15.5           |             | 20            |             | 25            | ns   |

| $t_{EA}^{4}$                     | Input to output enable delay                                         |             | 23             |             | 23            |             | 25            | ns   |

| $t_{\rm ER}^{4}$                 | Input to output disable delay                                        |             | 23             |             | 23            |             | 25            | ns   |

| $t_{\rm CO}^{4,6}$               | Clock to output delay                                                |             | 15             |             | 15            |             | 15            | ns   |

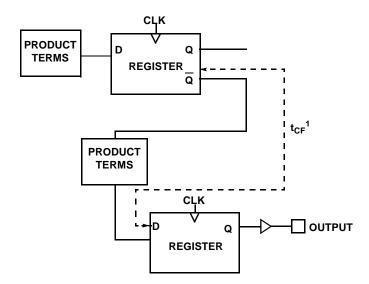

| t <sub>CO2</sub> <sup>4</sup>    | Clock to combinatorial output delay via internal registered feedback |             | 24             |             | 24            |             | 28            | ns   |

| $t_{\rm S}^{4,6}$                | Input or feedback setup time                                         | 15          |                | 15          |               | 18          |               | ns   |

| $t_{\rm H}^{4,6}$                | Input or feedback hold time                                          | 2           |                | 2           |               | 2           |               | ns   |

| $t_P^4$                          | External clock period $(t_{CO} + t_S)$                               | 30          |                | 30          |               | 33          |               | ns   |

| $t_{\rm WH, WL}^4$               | Clock width, clock high time, clock low time                         | 12          |                | 12          |               | 14          |               | ns   |

| f <sub>MAX1</sub> 4,6            | External maximum frequency $(1/(t_{CO} + t_S))$                      |             | 33             |             | 33            |             | 30            | MHz  |

| f <sub>MAX2</sub> <sup>4,6</sup> | Data path maximum frequency $(1/(t_{WH} + t_{WL}))$                  |             | 42             |             | 42            |             | 36            | MHz  |

| f <sub>MAX3</sub> <sup>4,6</sup> | Internal feedback maximum frequency $(1/(t_{CO} + t_{CF}))$          |             | 32             |             | 32            |             | 32            | MHz  |

| $t_{CF}^{4}$                     | Register clock to feedback input                                     |             | 13             |             | 13            |             | 13            | ns   |

| $t_{AW}^{4}$                     | Asynchronous reset width                                             | 20          |                | 20          |               | 25          |               | ns   |

| t <sub>AR</sub> <sup>4</sup>     | Asynchronous reset recovery time                                     | 20          |                | 20          |               | 25          |               | ns   |

| t <sub>AP</sub> <sup>4</sup>     | Input to asynchronous reset                                          |             | 20             |             | 20            |             | 25            | ns   |

| t <sub>SPR</sub> <sup>4,6</sup>  | Synchronous preset recovery time                                     | 20          |                | 20          |               | 25          |               | ns   |

| t <sub>PR</sub> <sup>4,6</sup>   | Power up reset time                                                  | 1.0         |                | 1.0         |               | 1.0         |               | μs   |

Notes:

1. Post-radiation performance guaranteed at 25°C per MIL-STD-883 Method 1019 at 1.0E6 rads(Si).

2. Guaranteed by characterization.

- 3. See page 12 for minimum  $V_{\mbox{\scriptsize DD}}$  requirements for power-up.

- Tested initially and after any design or process changes that affect.

Device 22VP10-15 tested at -55°C, +25°C and +50°C. At 125°C, tested to 20ns limit.

- 6. Tested on Programmed Test Ring only.

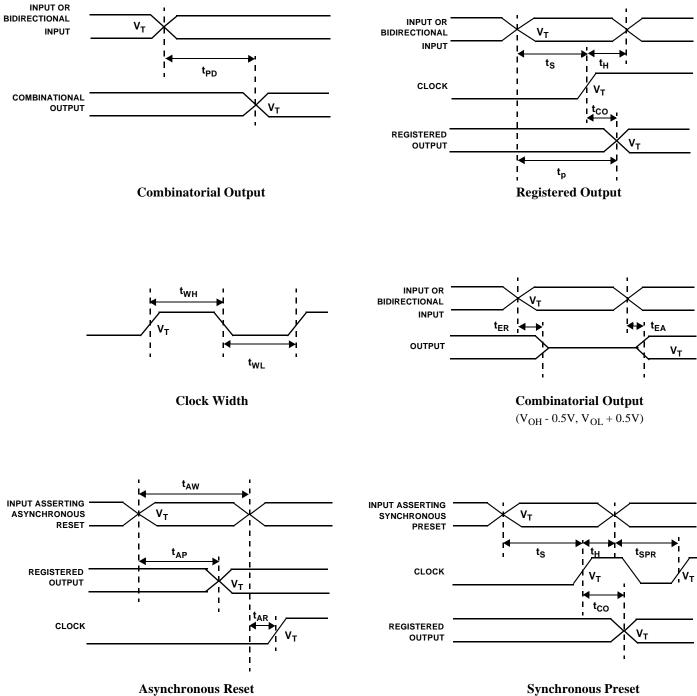

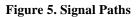

Figure 4. AC Electrical<sup>1,2,3</sup>

**Synchronous Preset**

### Notes:

- 1.  $V_T = 1.5V$ .

- 2. Input pulse amplitude 0V to 3.0V.

- 3. Input rise and fall times 3ns maximum.

Clock to Combinatorial Output (t<sub>CO2</sub>)

#### Note:

1.  $t_{CF}$  defined as the propagation delay from  $\overline{Q}$  to D register input.

$$\mathbf{f}_{\mathbf{MAX3}}$$

; Internal Feedback  $\left(\frac{1}{t_{CO} + t_{CF}}\right)$

### **POWER-UP RESET**

The power-up reset feature ensures that all flip-flops will be reset to LOW after the device has been powered up. The output state will depend on the programmed pattern. This feature is valuable in simplifying state machine initialization. See figure 6 for a timing diagram. Due to the synchronous operation of the power-up reset and the wide range of ways  $V_{DD}$  can rise to its steady state, the following five conditions are required to ensure a valid power-up reset.

- 1. The voltage supplied to the V<sub>DD</sub> pin(s) must be equal to 0V prior to the intended power-up sequence.

- 2. The voltage on V<sub>DD</sub> must rise from 0V to 1V at a rate of 0.1V/s or faster.

- 3. The V<sub>DD</sub> rise must be continuously increasing with respect to time, through 3V, and monotonic thereafter.

- 4. Following reset, the clock input must not be driven from LOW to HIGH until all applicable input and feedback setup times are met.

- 5. The power-up voltage must meet the minimum V<sub>DD</sub> requirements described by the following device dependent and temperature dependent equations:

| SMD Device types 01, 02, 03, 04, 08      | CMOS and TTL |

|------------------------------------------|--------------|

| $V_{DD} = 4.61 V - 0.0090 * (^{\circ}C)$ |              |

| SMD Device types 05, 06, 07              | CMOS         |

| V <sub>DD</sub> =4.41 -0.0090* (°C)      |              |

Note: The minimum  $V_{DD}$  requirement above is not applicable if the UT22VP10 application is purely combinatorial (i.e. no registered outputs).

Figure 6. Power-Up Reset Waveform

### **RADIATION HARDNESS**

The UT22VP10 RADPAL incorporates special design and layout features which allow operation in high-level radiation environments. UTMC has developed special low-temperature processing techniques designed to enhance the total-dose radiation hardness of both the gate oxide and the field oxide while maintaining the circuit density and reliability. For transient radiation hardness and latchup immunity, UTMC builds radiation-hardened products on epitaxial wafers using an advanced twin-tub CMOS process.

### **RADIATION HARDNESS DESIGN SPECIFICATIONS<sup>1</sup>**

| PARAMETER       | MINIMUM                           | UNIT   |                         |

|-----------------|-----------------------------------|--------|-------------------------|

| Total Dose      | +25°C per MIL-STD-883 Method 1019 | 1.0E6  | rads(Si)                |

| LET Threshold   | -55°C to +125°C                   | 50     | MeV-cm <sup>2</sup> /mg |

| Neutron Fluence | 1MeV equivalent                   | 1.0E14 | n/cm <sup>2</sup>       |

Note:

1. The RADPAL will not latchup during radiation exposure under recommended operating conditions.

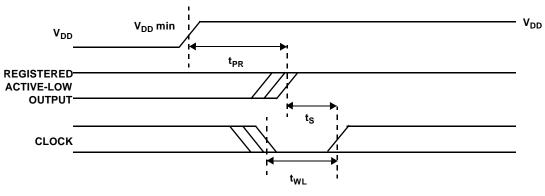

$\sqrt{5}$  Numbering and lettering on the ceramic are not subject to visual marking criteria.

Figure 7. 24-Pin 100-mil Center DIP (0.300 x 1.2)

#### Notes:

- 1. All exposed metalized areas are gold plated over electroplated nickel per MIL-PRF-38535.

- 2. The lid is electrically connected to  $V_{SS}$ .

- 3. Lead finishes are in accordance with MIL-PRF-38535.

- 4. Dimension letters refer to MIL-STD-1835.

- 5 Lead position and coplanarity are not measured.

- 6. ID mark symbol is vendor option.

- $\Delta$  For solder coated leads, increase maximum limit by 0.003 inch as measured at the center of the flat.

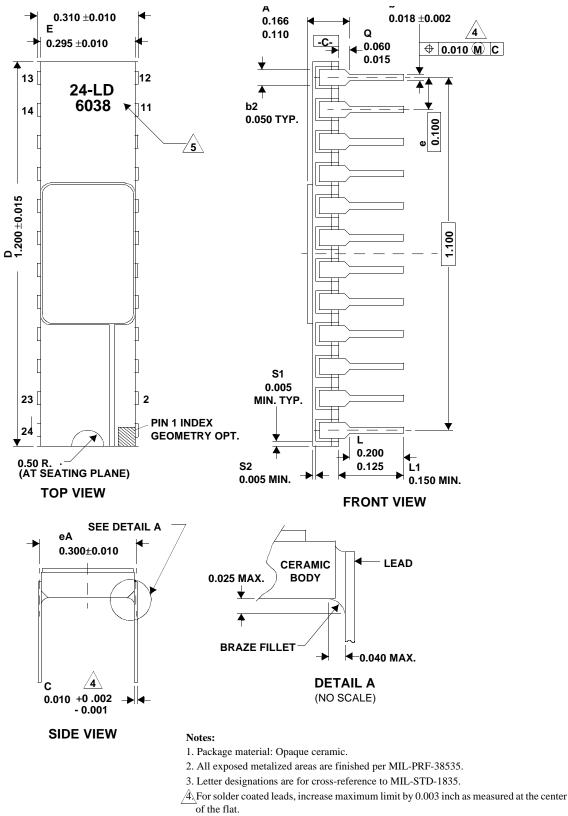

### Figure 8. 24-Lead Flatpack (0.45 x 0.64)

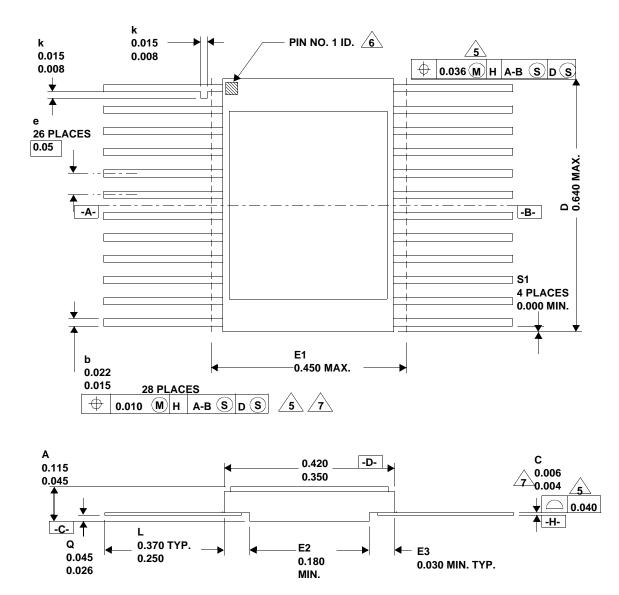

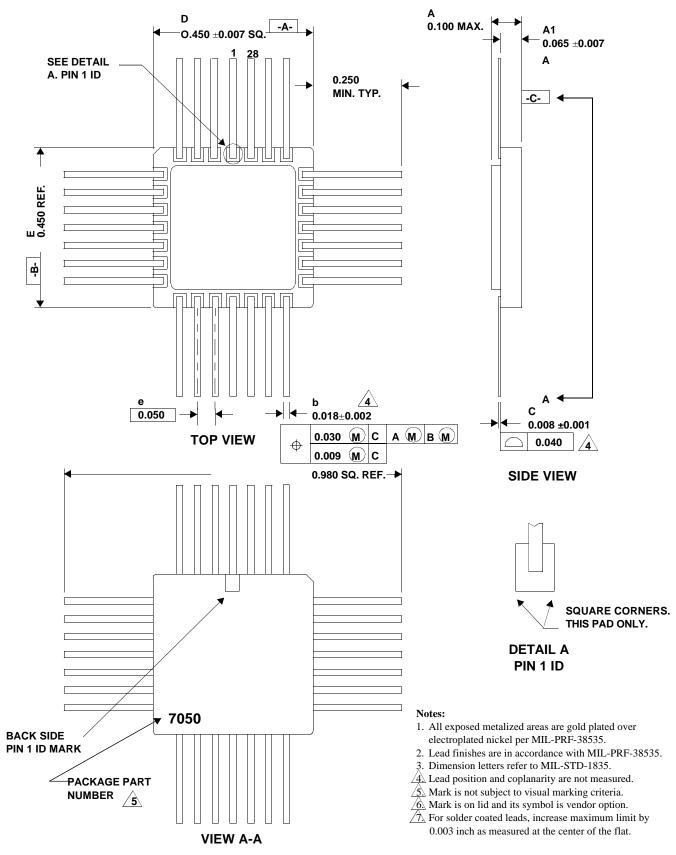

Figure 9. 28-Lead Quad-Flatpack (.45 x .45)

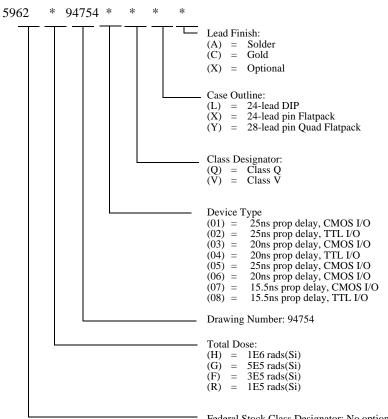

### **ORDERING INFORMATION**

#### **UT22VP10 Radiation Hardened PAL: SMD**

Notes:

Federal Stock Class Designator: No options

1. Lead finish (A, C, or X) must be specified.

2. If an "X" is specified when ordering, part marking will match the lead finish and will be either "A" (solder) or "C" (gold).

3. Total dose radiation must be specified when ordering. QML Q and QML V not available without radiation hardening.

4. (01-04, 08) is  $V_{DD}(min) = -0.009*(^{\circ}C)+4.61$ .

5. (05-07) is  $V_{DD}(min) = -0.009*(^{\circ}C)+4.41$ .

6. (07, 08) is tested at -55°C, +25°C, and +50°C to 15.5ns for tpD. At +125°C tested to 20ns limit for tpD.

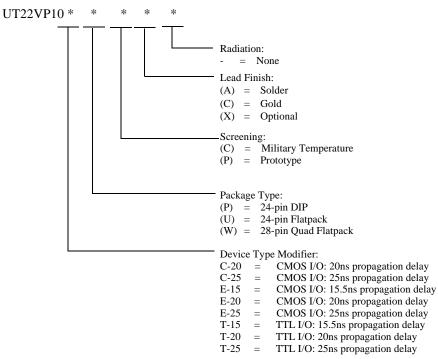

### **UT22VP10 Radiation Hardened PAL**

#### Notes:

- 1. Lead finish (A, C, or X) must be specified.

- 2. If an "X" is specified when ordering, part marking will match the lead finish and will be either "A" (solder) or "C" (gold).

- 3. Military Temperature range flow per UTMC's manufacturing flows document. Devices have 48 hours of burn-in and are tested at -55°C, room temperature, and 125°C. Radiation characteristics are neither tested nor guaranteed and may not be specified.

- Prototype flow per UTMC Manufacturing Flows Technical Description. Devices have prototype assembly and are tested at 25°C only. Radiation is neither tested nor guaranteed.

- 5. (T-15, C-25, T-25, C-20, T-20) is  $V_{DD}(min) = -0.009*(^{\circ}C)+4.61$ .

- 6. (E-15, E-20 and E-25) is  $V_{DD}(min) = -0.009*(^{\circ}C)+4.41$ .

- 7. (E-15 and T-15) is tested at at -55°C, +25°C, and +50°C to 15.5ns for  $t_{PD}$ . At +125°C tested to 20ns limit for  $t_{PD}$ .

### UT22VP10 RADPAL Power-On-Reset Ramp Rate Anomaly

UTMC has identified the following anomaly in the power up behavior of the UT22VP10 RADPAL (RC01 and RC02).

### Anomaly:

The anomaly was observed for a power-up application where a residual voltage between 200 and 500 mV was supplied to the  $V_{DD}$  pin(s) of the RADPAL for several milliseconds prior to the 5V power supply ramping to 5 volts. Consequently, the RADPAL enters a "test" mode (as opposed to a "user" mode). In the test mode, all output buffers are placed and remain in a high impedance state and the RADPAL does not function as programmed.

Through HSPICE simulation and laboratory tests, UTMC has found there exists a window in which a residual voltage of a few hundred millivolts on the  $V_{DD}$  pin(s) prevents the RADPAL from generating an internal POR signal for its security circuit. The lack of a reset signal allows the security circuit to power up in either the "user" or the "test" mode of operation. Entering the "test" mode prevents the RADPAL from functioning as programmed. The anomaly is seen at room temperature and above, where a residual voltage above 200mV is applied to  $V_{DD}$  before it transitions to  $V_{DD}$  minimum. The anomaly is *not seen* when the application of power to the RADPAL starts at zero volts and transitions monotonically to  $V_{DD}$  minimum and the slew rate is greater than 0.1V/S.

The anomaly is not wafer lot dependent and affects all date code shipped.

### Solution:

The UT22VP10 RAD<sub>PAL</sub> is susceptible to this POR anomaly whenever residual voltages of between 200mV and 500mV are on the  $V_{DD}$  pin(s) prior to the application of the 5V power supply.

In order to avoid powering up the UT22VP10 RAD<sub>PAL</sub> into a test mode, the following specifications must be met:

- 1) The application of voltages on the  $V_{DD}$  pin(s) of the RAD<sub>PAL</sub> must start at 0V and reach 1V at a rate of 0.1V/s or faster.

- 2) The power-up voltage must be <del>continuously increasing</del> with respect to time, through 3V, and monotonic thereafter.

- 3) No voltage can be applied to V<sub>DD</sub> prior to the intended power-up sequence.

An alternative or additional method to guarantee that the UT22VP10 RADPAL functions in the user mode of operation is to implement he following fix into the board level design:

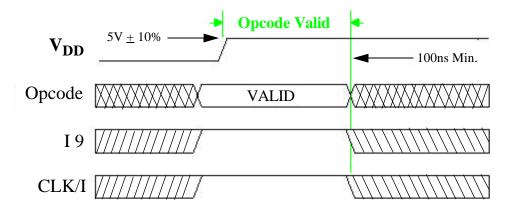

Apply one of the opcodes shown in Table 1 to the corresponding inputs of the RADPAL. Notice that the Clock and I9 inputs must have a logic "1" applied during the application of a valid opcode.

| Mode of   | Power-Up                     | RADPAL Input Pins |        |        |        |        |        |        |        |        |       |

|-----------|------------------------------|-------------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

| Operation | Opcode<br>(HEX) <sup>1</sup> | I<br>9            | I<br>8 | I<br>7 | I<br>6 | I<br>5 | I<br>4 | I<br>3 | I<br>2 | I<br>1 | Clk/I |

| 0         | DC                           | 1                 | 1      | 1      | 0      | 1      | 1      | 1      | 0      | 0      | 1     |

| 2         | DE                           | 1                 | 1      | 1      | 0      | 1      | 1      | 1      | 1      | 0      | 1     |

| 3         | DF                           | 1                 | 1      | 1      | 0      | 1      | 1      | 1      | 1      | 1      | 1     |

| 4         | E0                           | 1                 | 1      | 1      | 1      | 0      | 0      | 0      | 0      | 0      | 1     |

| 5         | E1                           | 1                 | 1      | 1      | 1      | 0      | 0      | 0      | 0      | 1      | 1     |

| 6         | E2                           | 1                 | 1      | 1      | 1      | 0      | 0      | 0      | 1      | 0      | 1     |

**Table 1: Valid Power-Up Opcodes**

Notes: 1. The Hexadecimal power-up opcode refers to the RADPAL inputs I8 - I1.

Apply one of the opcodes from Table 1 for at least 100ns anytime after V<sub>DD</sub> is within 5V ± 10% to ensure all test mode latches are cleared. Figure 1 shows the opcode timing diagram.

Figure 1. Opcode Timing

Applying one of the opcodes from Table 1 enables the programmed security fuse to reset the internal test latch, forcing the UT22VP10 RADPAL into the user mode of operation.

### **RADPAL<sup>TM</sup> Power-On-Reset Performance at Cold Temperatures**

UTMC has identified the following anomaly in the power up behavior of the UT22VP10 RADPAL<sup>TM</sup> .

### Anomaly:

The anomaly was observed for power-up applications where the voltage applied to the  $V_{DD}$  pin(s) of the RADPAL<sup>TM</sup> was within the specified voltage tolerance of  $5V \pm 10\%$ , yet, was not sufficient to turn off the internal reset pulse at cold temperature. Consequently, all programmed macro-cells would remain in reset until the power supply reached a minimum voltage.

UTMC has characterized this anomaly through HSPICE simulation, and laboratory testing. The characterization data shows that the minimum power-up voltage dependency on temperature fits a linear curve. Additionally, UTMC has identified distinct wafer lots that contain die with better cold temperature performance than the original supply of die. The wafer characterization is performed in the following manner:

- 1) Each wafer is evaluated for the transistor threshold voltages.

- 2) Each wafer showing satisfactory threshold voltages is then mapped to find die that have a high probability of representing the typical threshold voltage found across the wafer.

- 3) These selected die are then packaged, programmed, and characterized.

- 4) The test process ramps the voltage on the V<sub>DD</sub> pin(s) of the RADPAL<sup>TM</sup> and measures the minimum voltage required for the reset signal to turn off.

- 5) These voltage measurements are taken in five degree increments in temperature through  $-55^{\circ}$ C.

- 6) The characterization data is then plotted to verify that the samples fit the specified  $V_{DD}$  to temperature curve.

As a result of the characterization performed, UTMC has developed the following equations that UT22VP10 RADPAL<sup>TM</sup> device types will satisfy:

- 1) SMD device types 01, 02, 03, 04 (CMOS and TTL) satisfy  $V_{DD} = 4.61V - 0.0090 * (Temperature {}^{o}C)$

- 2) SMD device types 05, 06 (CMOS only) satisfy  $V_{DD} = 4.41V - 0.0090 * (Temperature {}^{o}C)$

### Solution:

To insure that the UT22VP10 RADPAL<sup>TM</sup> will power up in a usable mode, the following conditions must be met:

- 1) The voltage supplied to the V<sub>DD</sub> pin(s) must be equal to 0V prior to the intended power-up sequence.

- 2) The voltage on  $V_{DD}$  must rise from 0V to 1V at a rate of 0.1V/s or faster.

- 3) The V<sub>DD</sub> rise must be continuously increasing with respect to time, through 3V, and monotonic thereafter.

- 4) Following reset, the clock input must not be driven from LOW to HIGH until all applicable input and feedback setup times are met.

- 5) The power-up voltage must meet the minimum  $V_{DD}$  requirements described by the above device dependent equations. The customer can procure the specific device types meeting the respective equation via the SMD#5962-94754.

- NOTE: The minimum V<sub>DD</sub> requirement above is not applicable if the UT22VP10 application is purely combinatorial (i.e. no outputs are registered)