# CMOS 4-BIT HIGH-SPEED MICROPROCESSOR SLICE

### **KEY FEATURES**

- 2901 Architecture in CMOS

- Drop-In Replacement for 2901C

- Expandable in 4-Bit Increments

- DESC SMD No. 5962-88535

- High Speed

- Maximum Clock Frequency of 43 MHz (23 ns)

- Very Low Power

- 30 mA Maximum (Commercial Temperature)

- EPI Processing

- Latch-Up Immunity Over 200 mA

#### GENERAL DESCRIPTION

The WS5901 is a 4-bit high-speed microprocessor which contains the logic of a Bipolar 2901 bit slice processor.

This microprogrammable circuit has the flexibility to efficiently emulate almost any digital computing machine. It is an ideal candidate for such applications as peripheral controllers, CPUs, programmable microprocessors, and Digital Signal Processors.

The advanced CMOS process, with which the 5901 is manufactured, provides significant performance improvements over its counterpart. While operating as fast as a 2901C based system, the WS5901C requires less than 8% of the power consumed by its Bipolar equivalent. The WS5901D is a 25% speed enhancement over the "C" speed.

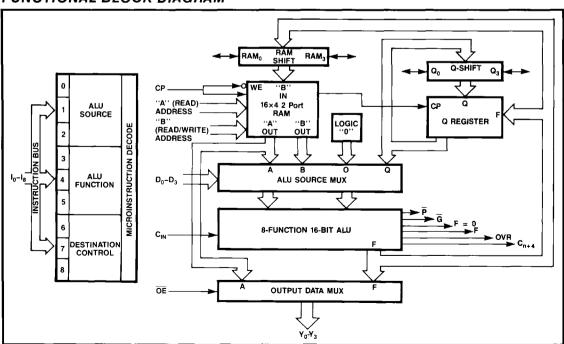

### **FUNCTIONAL BLOCK DIAGRAM**

# PIN DESCRIPTION

| Signal Name | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-3        | I   | Addresses which select the word of on board RAM which is to be displayed through the A port.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| B0-3        | 1   | Addresses which select the word of on board RAM which is to be displayed through the B port and into which data is written when the clock is low.                                                                                                                                                                                                                                                                                                                                                                              |

| 10-8        | ı   | Block of three instruction groups which are to select 1) which data sources will be applied to the ALU (I012), 2) what function the ALU will perform (I345), and 3) what data is to be written into the Q register or on board RAM(I678).                                                                                                                                                                                                                                                                                      |

| Q3, RAM3    | 1/0 | Signal paths at the MSB of the on-board RAM and the Q-register which are used for shifting data. When the destination code on 1678 indicates an up shift (Octal 6 or 7) the three state outputs are enabled and the MSB of the ALU output is available on the RAM 3 pin and the MSB of the Q-register is available on the Q3 pin. Otherwise, the pins appear as inputs. When the destination code calls for a down shift, the pins are used as the data inputs to the MSB of RAM (octal 4 and 5) and the Q register (octal 4). |

| Qo, RAMo    | 1/0 | Shift lines similar to Q3 and RAM3. However the description is applied to the LSB of RAM and the Q-register.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| D0-D3       | 1   | These four direct data inputs can be selected as a data source for the ALU. DO is the LSB.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Y0-Y3       | 0   | These four three state outputs, when enabled, display either the data on the A-port of the register stack or the outputs of the ALU as determined by the destination code 1678.                                                                                                                                                                                                                                                                                                                                                |

| ŌĒ          | ı   | When high, the Y outputs are in the high impedance state. When low, either the contents of the A-register or the outputs of the ALU are displayed on Y0-Y3, as determined by 1678.                                                                                                                                                                                                                                                                                                                                             |

| Ĝ, P        | 0   | The carry generate and propagate outputs of the ALU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| OVR         | 0   | This signal indicates that an overflow into the sign bit has occurred as a result of a two's complement operation.                                                                                                                                                                                                                                                                                                                                                                                                             |

| F = 0       | 0   | This output, when high, indicates the result of an ALU operation is zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| F3          | 0   | The most significant ALU output bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Cn          | ī   | The carry-in to the ALU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Cn + 4      | 0   | The carry-out of the ALU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| СР          | I   | This clock signal is applied to the A and B-port latches, RAM, and Q-register. The clock low time is the write enable to the on-board 16 x 4 RAM, including set-up time for the A and B port registers. The A and B port and Q-register outputs change on the clock low-to-high transition.                                                                                                                                                                                                                                    |

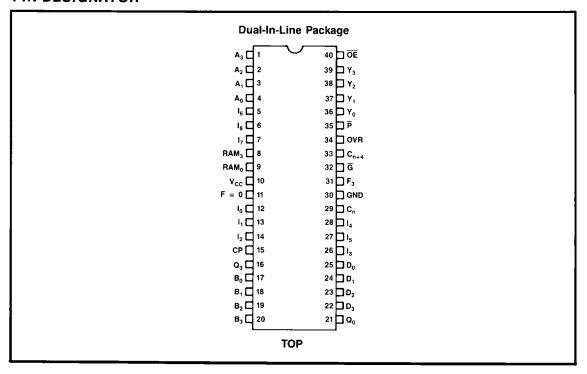

# PIN DESIGNATOR

### ABSOLUTE MAXIMUM RATINGS\*

| Operating Temp (Comm'l) | 0°C to +70°C   |

|-------------------------|----------------|

| (Mil)                   | 55°C to +125°C |

| Storage Temp. (No Bias) | 65°C to +150°C |

| Voltage on Any Pin with |                |

| Respect to GND          | 0.6V to +7V    |

| Latch-Up Protection     | >200 mA        |

| ESD Protection          | > +2000/       |

\*Notice: Stresses above those listed here may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect device reliability.

## DC READ CHARACTERISTICS Over Operating Temperature Range (Note 1)

| SYMBOL          | PARAMETER                        | TE                                                     | MIN                                   | MAX    | UNITS |    |

|-----------------|----------------------------------|--------------------------------------------------------|---------------------------------------|--------|-------|----|

| V <sub>OH</sub> | Output High Voltage              | $V_{CC} = Min$<br>$V_{IN} = V_{IH} \text{ or } V_{IL}$ | All Outputs $I_{OH} = -3.4 \text{ n}$ | nA 2.4 |       |    |

| V <sub>OL</sub> | Output Low Voltage               | V <sub>CC</sub> = Min                                  | $Y_0 - Y_3$ $I_{OL} = 20 \text{ mA}$  | Comm'l | 0.4   | V  |

| VOL             | Output Low Voltage               | $V_{IN} = V_{IH} \text{ or } V_{IL}$                   | All Others I <sub>OL</sub> = 16 mA    | Mil    | 0.4   |    |

| V <sub>IH</sub> | Input High Voltage               | Guaranteed Input Hi                                    | 2.0                                   |        | ]     |    |

| V <sub>IL</sub> | Input Low Voltage                | Guaranteed Input Lo                                    |                                       | 0.8    |       |    |

| I <sub>IX</sub> | Input Load Current               | $V_{CC} = Max, V_{IN} =$                               | -10                                   | 10     |       |    |

| l <sub>OZ</sub> | High Impedance<br>Output Current | $V_{CC} = Max, V_O = 0$                                | -4                                    | 40     | μА    |    |

| Icc             | Power Supply Current             | V <sub>CC</sub> = Max (Note 2)                         | Comm'l (0°C to +70°C)                 |        | 30    | mA |

**NOTES:** 1) Commercial:  $V_{CC} = +5V \pm 5\%$ ,  $T_A = 0^{\circ}C$  to 70°C.

2) 100 ns System Cycle

# LOGIC FUNCTIONS FOR $\overline{G}$ , $\overline{P}$ , $C_{n+4}$ , and OVR

The four signals, G, P,  $C_{n+4}$  and OVR are designed to indicate carry and overflow conditions when the WS5901 is in the add or subtract mode. The table below indicates the logic equations for these four signals for each of the eight ALU functions. The R and S inputs are the two inputs selected according to Table 1.

Definitions (+=OR)

$\begin{array}{lll} P_0 = R_0 + S_0 & G_0 = R_0 S_0 \\ P_1 = R_1 + S_1 & G_1 = R_1 S_1 \\ P_2 = R_2 + S_2 & G_2 = R_2 S_2 \\ P_3 = R_3 + S_3 & G_3 = R_3 S_3 \\ C_4 = G_3 + P_3 G_2 + P_3 P_2 G_1 + P_3 P_2 G_0 + P_3 P_2 P_1 P_0 C_n \\ C_3 = G_2 + P_2 G_1 + P_2 P_1 G_0 + P_2 P_1 P_0 C_n \end{array}$

| 1543 | Function | P                         | Ğ                                                                                               | C <sub>n + 4</sub>                                                                        | OVR                                                                            |  |  |  |  |  |  |

|------|----------|---------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|--|--|--|

| 0    | R+S      | $\overline{P_3P_2P_1P_0}$ | $G_3 + P_3G_2 + P_3P_2G_1 + P_3P_2P_1G_0$                                                       | C <sub>4</sub>                                                                            | C <sub>3</sub> ∀ C <sub>4</sub>                                                |  |  |  |  |  |  |

| 1    | S-R      |                           | Same as R + S equations, but substitute $\overline{R}_i$ for $R_i$ in definitions               |                                                                                           |                                                                                |  |  |  |  |  |  |

| 2    | R-S      |                           | Same as R + S equations, but substitute $\overline{S}_i$ for $S_i$ in definitions               |                                                                                           |                                                                                |  |  |  |  |  |  |

| 3    | RVS      | LOW                       | $P_3P_2P_1P_0$                                                                                  | $\overline{P_3P_2P_1P_0} + C_n$                                                           | $\overline{P_3P_2P_1P_0} + C_n$                                                |  |  |  |  |  |  |

| 4    | RAS      | LOW                       | $\overline{G_3 + G_2 + G_1 + G_0}$                                                              | $G_3 + G_2 + G_1 + G_0 + C_n$                                                             | G <sub>3</sub> +G <sub>2</sub> +G <sub>1</sub> +G <sub>0</sub> +C <sub>n</sub> |  |  |  |  |  |  |

| 5    | RAS      | LOW                       | LOW Same as R \( \Delta \) Sequations, but substitute $\overline{R_i}$ for $R_i$ in definitions |                                                                                           |                                                                                |  |  |  |  |  |  |

| 6    | R∀S      |                           | Same as R ♥ S equations, but substitute R i for R i in definitions                              |                                                                                           |                                                                                |  |  |  |  |  |  |

| 7    | R∀S      | $G_3 + G_2 + G_1 + G_0$   | $P_3G_2 + P_3P_2G_1 + P_3P_2P_1G_0$                                                             | $\frac{\overline{G}_3 + P_3 G_2 + P_3 P_2 G_1}{+ P_3 P_2 P_1 P_0 (G_0 + \overline{C}_n)}$ | See note 1                                                                     |  |  |  |  |  |  |

**NOTES:** 1)  $(P_2 + G_2P_1 + \overline{G}_2\overline{G}_1\overline{P}_0 + \overline{G}_2\overline{G}_1\overline{G}_0C_n) \forall (\overline{P}_3 + \overline{G}_3\overline{P}_2 + \overline{G}_3\overline{G}_2\overline{P}_1 + \overline{G}_3\overline{G}_2\overline{G}_1\overline{P}_0 + \overline{G}_3\overline{G}_2\overline{G}_1\overline{G}_0C_n)$ 2) + = OR

### **FUNCTIONAL TABLES**

| Mnemonic | М  | ICR            | 0 ( | CODE          | ALU SOURCE<br>OPERANDS |   |  |

|----------|----|----------------|-----|---------------|------------------------|---|--|

|          | 12 | l <sub>1</sub> | Ŀ   | Octal<br>Code | R                      | s |  |

| AQ       | ١  | L              | L   | 0             | Α                      | Q |  |

| AB       | L  | L              | Н   | 1             | Α                      | В |  |

| ZQ       | L  | н              | L   | 2             | 0                      | Q |  |

| ZB       | L  | н              | н   | 3             | 0                      | В |  |

| ZA       | н  | L              | L   | 4             | 0                      | Α |  |

| DA       | н  | L              | Н   | 5             | D                      | Α |  |

| DQ       | н  | Н              | L   | 6             | D                      | Q |  |

| DZ       | Н  | н              | Н   | 7             | D                      | 0 |  |

| Mnemonic                                          | МІ | CR | 0      | CODE                            | ALU                                                                          | SYMBOL                                           |  |

|---------------------------------------------------|----|----|--------|---------------------------------|------------------------------------------------------------------------------|--------------------------------------------------|--|

| in the third the                                  | 15 | 14 | 13     | Octal<br>Code                   | Function                                                                     | 311111111111111111111111111111111111111          |  |

| ADD<br>SUBR<br>SUBS<br>OR<br>AND<br>NOTRS<br>EXOR |    |    | LILILI | 0<br>1<br>2<br>3<br>4<br>5<br>6 | R Plus S<br>S Minus R<br>R Minus S<br>R OR S<br>R AND S<br>R AND S<br>R EXOR | R + > S<br>R R S S S S S S S S R R R R R R R R R |  |

| EXNOR                                             | Н  | Н  | Н      | 7                               | R EX-NOR S                                                                   | R∇S                                              |  |

Table 2. ALU Function Control.

| Mnemonic     | МІ | MICRO CODE |    | RAM<br>FUNCTION |       |         | Q-REG.<br>FUNCTION |         |          | AM<br>FTER       | Q SHI            | FTER            |                 |

|--------------|----|------------|----|-----------------|-------|---------|--------------------|---------|----------|------------------|------------------|-----------------|-----------------|

| wine in onic | 18 | 17         | 16 | Octal<br>Code   | SHIFT | LOAD    | SHIFT              | LOAD    | Y OUTPUT | RAM <sub>O</sub> | RAM <sub>3</sub> | $\mathbf{Q}_0$  | <b>Q</b> 3      |

| QREG         | ∟  | L          | L  | 0               | Х     | NONE    | NONE               | F→Q     | F        | Х                | X                | X               | Х               |

| NOP          | L  | L          | Н  | 1               | Х     | NONE    | Х                  | NONE    | F        | Х                | Х                | X               | Х               |

| RAMA         | L  | Н          | L  | 2               | NONE  | F→B     | Х                  | NONE    | Α        | Х                | Х                | Х               | X               |

| RAMF         | Ļ  | Τ          | Н  | 3               | NONE  | F→B     | Х                  | NONE    | F        | X                | X                | Х               | X               |

| RAMQD        | Н  | L          | L  | 4               | DOWN  | F/2 → B | DOWN               | Q/2 → Q | F        | F <sub>0</sub>   | IN <sub>3</sub>  | Q <sub>0</sub>  | IN <sub>3</sub> |

| RAMD         | H  | L          | Ή  | 5               | DOWN  | F/2 → B | Х                  | NONE    | F        | F <sub>0</sub>   | IN <sub>3</sub>  | Qo              | Х               |

| RAMQU        | Ι  | Ι          | L  | 6               | UP    | 2F→B    | UP                 | 2Q→Q    | F        | INO              | F <sub>3</sub>   | IN <sub>O</sub> | Q <sub>3</sub>  |

| RAMU         | Н  | Τ          | Н  | 7               | UP    | 2F→B    | Х                  | NONE    | F        | IN <sub>0</sub>  | F3               | Х               | Qз              |

X = Don't care.

Table 3. ALU Destination Control.

|                  |                                 |           | I <sub>210</sub> (Octal Code) |         |         |         |           |           |         |  |  |  |

|------------------|---------------------------------|-----------|-------------------------------|---------|---------|---------|-----------|-----------|---------|--|--|--|

|                  |                                 | 0         | 1                             | 2       | 3       | 4       | 5         | 6         | 7       |  |  |  |

| I <sub>543</sub> | ALU                             |           | ALU Source (R, S)             |         |         |         |           |           |         |  |  |  |

| (Octal Code)     | Function                        | A, Q      | A, B                          | O, Q    | О, В    | O, A    | D, A      | D, Q      | D, O    |  |  |  |

| 0                | C <sub>n</sub> = L<br>R Plus S  | A + Q     | A + B                         | Q       | В       | Α       | D + A     | D + Q     | D       |  |  |  |

|                  | C <sub>n</sub> = H              | A + Q + 1 | A + B + 1                     | Q + 1   | B + 1   | A + 1   | D + A + 1 | D + Q + 1 | D + 1   |  |  |  |

| 1                | C <sub>n</sub> = L<br>S Minus R | Q – A – 1 | B - A - 1                     | Q – 1   | B – 1   | A – 1   | A – D – 1 | Q - D - 1 | – D – 1 |  |  |  |

| '                | C <sub>n</sub> = H              | Q – A     | B - A                         | Q       | В       | Α       | A - D     | Q-D       | – D     |  |  |  |

| 2                | C <sub>n</sub> = L<br>R Minus S | A – Q – 1 | A – B – 1                     | - Q - 1 | - B - 1 | - A - 1 | D - A - 1 | D - Q - 1 | D – 1   |  |  |  |

|                  | $C_n = H$                       | A – Q     | A – B                         | - Q     | - B     | - A     | D – A     | D – Q     | D       |  |  |  |

| 3                | RORS                            | AvQ       | AvB                           | Q       | В       | Α       | DvA       | DvQ       | D       |  |  |  |

| 4                | RANDS                           | AΛQ       | A∧B                           | 0       | 0       | 0       | DΛA       | DΛQ       | 0       |  |  |  |

| 5                | RANDS                           | ĀΛQ       | ĀΛB                           | Q       | В       | Α       | DΛA       | Ū∧Q       | 0       |  |  |  |

| 6                | R EX-OR S                       | A⊽Q       | A⊽B                           | Q       | В       | Α       | D₹A       | D⊽Q       | D       |  |  |  |

| 7                | REX-NORS                        | Ā₹Q       | Ā₹B                           | ā       | B       | Ā       | D⊽A       | D⊽Q       | Ď       |  |  |  |

<sup>+ =</sup> Plus; - = Minus; v = OR;  $\Lambda = AND$ ;  $\nabla = EX-OR$ .

Table 4. Source Operand and ALU Function Matrix.

B = Register Addressed by B inputs.

DOWN is toward LSB. UP is toward MSB.

## SOURCE OPERANDS AND ALU FUNCTIONS

Eight source operand pairs are available to the ALU as determined by the IO, I1, and I2 instruction inputs. The ALU performs eight functions; three arithmetic and five logic. This function selection is controlled by the I3, I4, and I5 instruction inputs. When in the arithmetic mode, the ALU results are also affected by the carry, Cn. In the logic mode, the Cn input has no effect.

The matrix of Table 4 results when Cn and I0 through I5 are viewed together. Table 5 defines the logic operations which the WS5901 can perform and Table 6 shows the arithmetic operations of the device. Both carry-in HIGH (Cn=1) and carry-in LOW (Cn=0) are defined in these operations.

| 0-1-1                                        |        | · · · · · · · · · · · · · · · · · · ·                                        |

|----------------------------------------------|--------|------------------------------------------------------------------------------|

| Octal<br>I <sub>543</sub> , I <sub>210</sub> | Group  | Function                                                                     |

| 4 0<br>4 1<br>4 5<br>4 6                     | AND    | A ^ Q<br>A ^ B<br>D ^ A<br>D ^ Q                                             |

| 3 0<br>3 1<br>3 5<br>3 6                     | OR     | A v Q<br>A v B<br>D v A<br>D v Q                                             |

| 6 0<br>6 1<br>6 5<br>6 6                     | EX-OR  | A V Q<br>A V B<br>D V A<br>D V Q                                             |

| 7 0<br>7 1<br>7 5<br>7 6                     | EX-NOR | A <del>V</del> Q<br>A <del>V</del> B<br>D <del>V</del> A<br>D <del>V</del> Q |

| 7 2<br>7 3<br>7 4<br>7 7                     | INVERT | O N B D                                                                      |

| 6 2<br>6 3<br>6 4<br>6 7                     | PASS   | Q<br>B<br>A<br>D                                                             |

| 3 2<br>3 3<br>3 4<br>3 7                     | PASS   | Q<br>B<br>A<br>D                                                             |

| 4 2<br>4 3<br>4 4<br>4 7                     | "ZERO" | 0<br>0<br>0<br>0                                                             |

| 5 0<br>5 1<br>5 5<br>5 6                     | MASK   | Ā ^ Q<br>Ā ^ B<br>D ^ A<br>D ^ Q                                             |

| Table 5 | 5. ALU | Logic | Mode | Functions. |

|---------|--------|-------|------|------------|

|         | , ALO  | Logic | MOGE | i unchons. |

| Octal                                                | C <sub>n</sub> =        | · L                                                                                                  | C <sub>n</sub> = H      |                                                             |  |

|------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------------------------------------|--|

| I <sub>210</sub>                                     | Group                   | Function                                                                                             | Group                   | Function                                                    |  |

| 0 0<br>0 1<br>0 5<br>0 6                             | ADD                     | A + Q<br>A + B<br>D + A<br>D + Q                                                                     | ADD plus<br>one         | A + Q + 1<br>A + B + 1<br>D + A + 1<br>D + Q + 1            |  |

| 0 2<br>0 3<br>0 4<br>0 7                             | PASS                    | Q B A D                                                                                              | Increment               | Q + 1<br>B + 1<br>A + 1<br>D + 1                            |  |

| 12<br>13<br>14<br>27                                 | Decrement               | Q - 1<br>B - 1<br>A - 1<br>D - 1                                                                     | PASS                    | Q<br>B<br>A<br>D                                            |  |

| 2 2<br>2 3<br>2 4<br>1 7                             | 1's Comp.               | -Q - 1<br>-B - 1<br>-A - 1<br>-D - 1                                                                 | 2's Comp.<br>(Negate)   | -Q<br>-B<br>-A<br>-D                                        |  |

| 1 0<br>1 1<br>1 5<br>1 6<br>2 0<br>2 1<br>2 5<br>2 6 | Subtract<br>(1's Comp.) | Q - A - 1<br>B - A - 1<br>A - D - 1<br>Q - D - 1<br>A - Q - 1<br>A - B - 1<br>D - A - 1<br>D - Q - 1 | Subtract<br>(2's Comp.) | Q - A<br>B - A<br>A - D<br>Q - D<br>A - Q<br>A - B<br>D - Q |  |

Table 6. ALU Arithmetic Mode Functions.

## WS5901C COMMERCIAL RANGE AC CHARACTERISTICS

The tables shown here specify the guaranteed performance of the WS5901C over the Commercial operating temperature range of 0°C to +70°C and a power supply range of  $5V \pm 5$ %. Inputs are switching between 0 and 3V with rise and fall times of 1 V/ns and measurements made at 1.5V. All outputs have maximum DC load.

# CYCLE TIME AND CLOCK CHARACTERISTICS

| READ-MODIFY-WRITE (from select of A, B registers to end of cycle)   | 31 ns  |

|---------------------------------------------------------------------|--------|

| Maximum Clock Frequency to Shift Q (50% duty cycle, I = 432 or 632) | 32 MHz |

| Minimum Clock Low Time                                              | 15 ns  |

| Minimum Clock High Time                                             | 15 ns  |

| Minimum Clock Period                                                | 31 ns  |

### **OUTPUT ENABLE/DISABLE TIME**

Disable tests performed with  $C_L = 5 \text{ pF}$  and measured to 0.5V change of output voltage.

| From OE Low to Y output enable | 23 ns |

|--------------------------------|-------|

| From OE High to output disable | 23 ns |

### **COMBINATIONAL PROPAGATION DELAYS** $(C_L = 50 pF)$

|                                |    |    |                  | , -  | •     |     |               |           |       |

|--------------------------------|----|----|------------------|------|-------|-----|---------------|-----------|-------|

| FROM OUTPUT                    | Y  | F3 | C <sub>n+4</sub> | G, P | F = 0 | OVR | RAM0,<br>RAM3 | Q0,<br>Q3 | UNITS |

| A, B ADDRESS                   | 40 | 40 | 40               | 37   | 40    | 40  | 40            | _         |       |

| D <sub>0</sub> -D <sub>3</sub> | 30 | 30 | 30               | 30   | 38    | 30  | 30            | _         |       |

| Cn                             | 22 | 22 | 20               | _    | 25    | 22  | 25            | _         |       |

| I <sub>012</sub>               | 35 | 35 | 35               | 37   | 37    | 35  | 35            |           | ns    |

| l <sub>345</sub>               | 35 | 35 | 35               | 35   | 38    | 35  | 35            | _         | ,,,,  |

| I <sub>678</sub>               | 25 | _  | _                | _    | _     | _   | 26            | 26        |       |

| A BYPASS ALU<br>(I = 2XX)      | 35 | _  | _                | _    | _     |     | -             |           |       |

| CLOCK                          | 35 | 35 | 35               | 35   | 35    | 35  | 35            | 28        |       |

### SET-UP AND HOLD TIMES RELATIVE TO CLOCK (CP) INPUT

| CP                             | Set Up before H → L | Hold after H → L | Set Up before L → H | Hold after L → H | UNITS |

|--------------------------------|---------------------|------------------|---------------------|------------------|-------|

| A, B Source<br>Address         | 15                  | 1 (Note 3)       | 30 (Note 4)         | 1                |       |

| B Destination<br>Address       | 15                  | DO NOT CI        | HANGE (Note 2)      | 1                |       |

| D <sub>0</sub> -D <sub>3</sub> |                     |                  | 25                  | 0                |       |

| C <sub>n</sub>                 | _                   | _                | 20                  | 0                | ns    |

| I <sub>012</sub>               |                     | _                | 30                  | 0                |       |

| l <sub>345</sub>               |                     | _                | 30                  | 0                |       |

| l <sub>678</sub>               | 10                  | DO NOT CI        | HANGE (Note 2)      | 0                |       |

| RAM0, 3 and Q0, 3              | _                   |                  | 12                  | 0                |       |

- 2) The phrase "DO NOT CHANGE" indicates that certain signals must remain low for the duration of the clock Low time. Otherwise, erroneous operation may be the result.

- 3) Prior to clock H>L transition, source addresses must be stable to allow time for the source data to be set up before the latch closes. After this transition the A address may be changed. If it is not being used as a destination, the B address may also be changed. If it is being used as a destination, the B address must remain stable during the clock Low period.

- 4) Set-up time before H>L included here.

## WS5901CYM MILITARY RANGE AC CHARACTERISTICS

The tables shown here specify the guaranteed performance of the WS5901C over the Military operating temperature range of  $-55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  and a power supply range of 5V  $\pm$  10%. Inputs are switching between 0 and 3V with rise and fall times of 1 V/ns and measurements made at 1.5V. All outputs have maximum DC load.

# CYCLE TIME AND CLOCK CHARACTERISTICS

| READ-MODIFY-WRITE (from select of A, B registers to end of cycle)   | 32 ns  |

|---------------------------------------------------------------------|--------|

| Maximum Clock Frequency to Shift Q (50% duty cycle, I = 432 or 632) | 31 MHz |

| Minimum Clock Low Time                                              | 17 ns  |

| Minimum Clock High Time                                             | 15 ns  |

| Minimum Clock Period                                                | 32 ns  |

### **OUTPUT ENABLE/DISABLE TIME**

Disable tests performed with  $C_L = 5 \text{ pF}$  and measured to 0.5V change of output voltage.

| From OE Low to Y output enable | 25 ns |

|--------------------------------|-------|

| From OE High to output disable | 25 ns |

### COMBINATIONAL PROPAGATION DELAYS (C<sub>1</sub> = 50 pF)

| (of ook)                       |    |    |                  |      |       |     |               |           |       |

|--------------------------------|----|----|------------------|------|-------|-----|---------------|-----------|-------|

| TO<br>OUTPUT<br>INPUT          | Y  | F3 | C <sub>n+4</sub> | G, P | F = 0 | OVR | RAMO,<br>RAM3 | Q0,<br>Q3 | UNITS |

| A, B ADDRESS                   | 48 | 48 | 48               | 44   | 48    | 48  | 48            | _         |       |

| D <sub>0</sub> -D <sub>3</sub> | 37 | 37 | 37               | 34   | 40    | 37  | 37            | _         |       |

| C <sub>n</sub>                 | 25 | 25 | 21               | _    | 28    | 25  | 28            | _         |       |

| 1 <sub>012</sub>               | 40 | 40 | 40               | 44   | 44    | 40  | 40            | _         |       |

| l <sub>345</sub>               | 40 | 40 | 40               | 40   | 40    | 40  | 40            |           | ns    |

| l <sub>678</sub>               | 29 |    |                  |      | _     |     | 29            | 29        |       |

| A BYPASS ALU<br>(I = 2XX)      | 40 | _  | _                | _    | _     | _   | _             | _         |       |

| CLOCK                          | 40 | 40 | 40               | 40   | 40    | 40  | 40            | 33        |       |

# SET-UP AND HOLD TIMES RELATIVE TO CLOCK (CP) INPUT

| 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |                     |                  |                     |                  |       |  |  |  |  |  |  |  |

|---------------------------------------|---------------------|------------------|---------------------|------------------|-------|--|--|--|--|--|--|--|

| CP<br>INPUT                           | Set Up before H → L | Hold after H → L | Set Up before L → H | Hold after L → H | UNITS |  |  |  |  |  |  |  |

| A, B Source<br>Address                | 15                  | 1 (Note 3)       | 32 (Note 4)         | 2                |       |  |  |  |  |  |  |  |

| B Destination<br>Address              | 15                  | DO NOT CI        | HANGE (Note 2)      | 2                |       |  |  |  |  |  |  |  |

| D <sub>0</sub> -D <sub>3</sub>        |                     | _                | 25                  | 0                |       |  |  |  |  |  |  |  |

| C <sub>n</sub>                        |                     |                  | 20                  | 0                | ns    |  |  |  |  |  |  |  |

| l <sub>012</sub>                      |                     |                  | 30                  | 0                |       |  |  |  |  |  |  |  |

| l <sub>345</sub>                      |                     | 1                | 30                  | 0                |       |  |  |  |  |  |  |  |

| l <sub>678</sub>                      | 10                  | DO NOT C         | HANGE (Note 2)      | 0                |       |  |  |  |  |  |  |  |

| RAM0, 3 and Q0, 3                     | _                   | _                | 12                  | 0                |       |  |  |  |  |  |  |  |

- 2) The phrase "DO NOT CHANGE" indicates that certain signals must remain low for the duration of the clock Low time. Otherwise, erroneous operation may be the result.

- 3) Prior to clock H>L transition, source addresses must be stable to allow time for the source data to be set up before the latch closes. After this transition the A address may be changed. If it is not being used as a destination, the B address may also be changed. If it is being used as a destination, the B address must remain stable during the clock Low period.

- 4) Set-up time before H>L included here.

## WS5901D COMMERCIAL RANGE AC CHARACTERISTICS

The tables shown here specify the guaranteed performance of the WS5901D over the Commercial operating temperature range of 0°C to +70°C and a power supply range of 5V  $\pm$  5%. Inputs are switching between 0 and 3V with rise and fall times of 1 V/ns and measurements made at 1.5V. All outputs have maximum DC load.

# CYCLE TIME AND CLOCK CHARACTERISTICS

| READ-MODIFY-WRITE (from select of A, B registers to end of cycle)   | 23 ns  |

|---------------------------------------------------------------------|--------|

| Maximum Clock Frequency to Shift Q (50% duty cycle, I = 432 or 632) | 43 MHz |

| Minimum Clock Low Time                                              | 11 ns  |

| Minimum Clock High Time                                             | 11 ns  |

| Minimum Clock Period                                                | 23 ns  |

#### **OUTPUT ENABLE/DISABLE TIME**

Disable tests performed with  $C_L = 5 \text{ pF}$  and measured to 0.5V change of output voltage.

| From OE Low to Y output enable | 14 ns |

|--------------------------------|-------|

| From OE High to output disable | 16 ns |

### **COMBINATIONAL PROPAGATION DELAYS** (C<sub>1</sub> = 50 pF)

| FROM OUTPUT                    | Y  | F3 | C <sub>n+4</sub> | G, P | F = 0 | OVR | RAM0,<br>RAM3 | Q0,<br>Q3 | UNITS |

|--------------------------------|----|----|------------------|------|-------|-----|---------------|-----------|-------|

| A, B ADDRESS                   | 30 | 30 | 30               | 28   | 30    | 30  | 30            | _         |       |

| D <sub>0</sub> -D <sub>3</sub> | 21 | 20 | 20               | 20   | 24    | 21  | 22            | _         |       |

| C <sub>n</sub>                 | 17 | 17 | 14               | _    | 19    | 16  | 18            |           |       |

| l <sub>012</sub>               | 26 | 25 | 24               | 24   | 25    | 24  | 25            | _         | ns    |

| 1345                           | 26 | 24 | 24               | 24   | 26    | 24  | 26            | _         | 113   |

| l <sub>678</sub>               | 16 | _  |                  | _    | _     | _   | 21            | 21        |       |

| A BYPASS ALU<br>(I = 2XX)      | 24 | _  | _                | _    | _     | _   | _             |           |       |

| CLOCK                          | 24 | 23 | 23               | 23   | 24    | 24  | 24            | 19        | _     |

# SET-UP AND HOLD TIMES RELATIVE TO CLOCK (CP) INPUT

| CP<br>INPUT                    | Set Up before H → L | Hold after H → L | Set Up before L → H | Hold after L → H | UNITS |

|--------------------------------|---------------------|------------------|---------------------|------------------|-------|

| A, B Source<br>Address         | 10                  | 0 (Note 3)       | 21 (Note 4)         | 1                |       |

| B Destination<br>Address       | 10                  | DO NOT C         | HANGE (Note 2)      | 1                |       |

| D <sub>0</sub> -D <sub>3</sub> |                     | _                | 16                  | 0                |       |

| C <sub>n</sub>                 | _                   | _                | 13                  | 0                | ns    |

| l <sub>012</sub>               | _                   | _                | 19                  | 0                |       |

| l <sub>345</sub>               |                     |                  | 19                  | 0                |       |

| l <sub>678</sub>               | 7                   | DO NOT CH        | HANGE (Note 2)      | 0                |       |

| RAM0, 3 and Q0, 3              |                     |                  | 9                   | 1                |       |

- 2) The phrase "DO NOT CHANGE" indicates that certain signals must remain low for the duration of the clock Low time. Otherwise, erroneous operation may be the result.

- 3) Prior to clock H>L transition, source addresses must be stable to allow time for the source data to be set up before the latch closes. After this transition the A address may be changed. If it is not being used as a destination, the B address may also be changed. If it is being used as a destination, the B address must remain stable during the clock Low period.

- 4) Set-up time before H>L included here.

## WS5901DYM MILITARY RANGE AC CHARACTERISTICS

The tables shown here specify the guaranteed performance of the WS5901D over the Military operating temperature range of  $-55^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  and a power supply range of 5V  $\pm$  10%. Inputs are switching between 0 and 3V with rise and fall times of 1 V/ns and measurements made at 1.5V. All outputs have maximum DC load.

# CYCLE TIME AND CLOCK CHARACTERISTICS

| READ-MODIFY-WRITE (from select of A, B registers to end of cycle)   | 27 ns  |

|---------------------------------------------------------------------|--------|

| Maximum Clock Frequency to Shift Q (50% duty cycle, I = 432 or 632) | 37 MHz |

| Minimum Clock Low Time                                              | 15 ns  |

| Minimum Clock High Time                                             | 12 ns  |

| Minimum Clock Period                                                | 27 ns  |

### OUTPUT ENABLE/DISABLE TIME

Disable tests performed with  $C_L = 5$  pF and measured to 0.5V change of output voltage.

| From OE Low to Y output enable | 16 ns |

|--------------------------------|-------|

| From OE High to output disable | 18 ns |

### **COMBINATIONAL PROPAGATION DELAYS** (C<sub>1</sub> = 50 pF)

| FROM OUTPUT                    | Υ  | F3 | C <sub>n+4</sub> | G, P | F = 0 | OVR | RAMO,<br>RAM3 | Q0,<br>Q3 | UNITS |

|--------------------------------|----|----|------------------|------|-------|-----|---------------|-----------|-------|

| A, B ADDRESS                   | 33 | 33 | 33               | 33   | 33    | 33  | 33            | _         |       |

| D <sub>0</sub> -D <sub>3</sub> | 24 | 23 | 23               | 21   | 25    | 24  | 25            | _         |       |

| C <sub>n</sub>                 | 18 | 17 | 14               |      | 19    | 17  | 19            | _         |       |

| I <sub>012</sub>               | 28 | 27 | 26               | 28   | 29    | 27  | 27            | _         | ne    |

| I <sub>345</sub>               | 27 | 27 | 26               | 26   | 27    | 26  | 27            | _         | ns    |

| I <sub>678</sub>               | 18 |    |                  | _    | _     |     | 21            | 21        |       |

| A BYPASS ALU<br>(I = 2XX)      | 26 | _  | _                | _    | _     | _   | _             | _         |       |

| CLOCK                          | 27 | 26 | 26               | 25   | 27    | 26  | 27            | 20        |       |

# SET-UP AND HOLD TIMES RELATIVE TO CLOCK (CP) INPUT

| THE THE TIME THE TO SECON (SI) HAT OF |                     |                        |                     |                  |       |  |  |

|---------------------------------------|---------------------|------------------------|---------------------|------------------|-------|--|--|

| CP                                    | Set Up before H → L | Hold after H → L       | Set Up before L → H | Hold after L → H | UNITS |  |  |

| A, B Source<br>Address                | 12                  | 0 (Note 3)             | 25 (Note 4)         | 2                |       |  |  |

| B Destination<br>Address              | 12                  | DO NOT C               | HANGE (Note 2)      | 2                |       |  |  |

| D <sub>0</sub> -D <sub>3</sub>        |                     |                        | 16                  | 0                |       |  |  |

| C <sub>n</sub>                        |                     |                        | 13                  | 0                | ns    |  |  |

| I <sub>012</sub>                      |                     |                        | 19                  | 0                |       |  |  |

| l <sub>345</sub>                      |                     |                        | 19                  | 0                |       |  |  |

| l <sub>678</sub>                      | 9                   | DO NOT CHANGE (Note 2) |                     | 0                |       |  |  |

| RAM0, 3 and Q0, 3                     |                     | _                      | 9                   | 0                |       |  |  |

- 2) The phrase "DO NOT CHANGE" indicates that certain signals must remain low for the duration of the clock Low time. Otherwise, erroneous operation may be the result.

- 3) Prior to clock H>L transition, source addresses must be stable to allow time for the source data to be set up before the latch closes. After this transition the A address may be changed. If it is not being used as a destination, the B address may also be changed. If it is being used as a destination, the B address must remain stable during the clock Low period.

- 4) Set-up time before H>L included here.

## **ORDERING INFORMATION**

| PART NUMBER | SPEED<br>(ns) | PACKAGE<br>TYPE          | PACKAGE<br>DRAWING | OPERATING<br>TEMPERATURE<br>RANGE | WSI<br>MANUFACTURING<br>PROCEDURE |

|-------------|---------------|--------------------------|--------------------|-----------------------------------|-----------------------------------|

| WS5901CP    | С             | 40 Pin Plastic DIP, 0.6" | P1                 | Comm'l                            | Standard                          |

| WS5901CY    | С             | 40 Pin CERDIP, 0.6"      | Y1                 | Comm'l                            | Standard                          |

| WS5901CYM   | С             | 40 Pin CERDIP, 0.6"      | Y1                 | Military                          | Standard                          |

| WS5901CYMB  | С             | 40 Pin CERDIP, 0.6"      | Y1                 | Military                          | MIL-STD-883C                      |

| WS5901DP    | D             | 40 Pin Plastic DIP, 0.6" | P1                 | Comm'l                            | Standard                          |

| WS5901DY    | D             | 40 Pin CERDIP, 0.6"      | Y1                 | Comm'l                            | Standard                          |

| WS5901DYM   | D             | 40 Pin CERDIP, 0.6"      | Y1                 | Military                          | Standard                          |

| WS5901DYMB  | D             | 40 Pin CERDIP, 0.6"      | Y1                 | Military                          | MIL-STD-883C                      |