# COMMUNICATION SEMICONDUCTORS

## DATA BULLETIN

## **CMX625**

## ISDN TA POTS Interface

#### **ADVANCE INFORMATION**

### Features

- SPM and Ringing Voltage Generators

- Integrated DTMF Decoder/Encoder

- V.23/Bell 202 FSK/Tone Generator

- Selectable A-Law/µ-Law PCM Codec

- IOM-2 Interface Terminal Mode and Non-Terminal Mode (Line Card Mode)

## **Applications**

- ISDN NTUs with Analog Ports

- ISDN Line Cards

- Wireless Local Loop Termination Cards

- ISDN Terminals with Additional POTS Ports

- PC based ISDN Cards with Telephone Ports

- Billing/SPM Systems

The CMX625 is an integrated telecom tone generator, DTMF encoder/decoder and PCM Codec-Filter designed for ISDN interfaces, Wireless Local Loop and other digitized speech systems. The tone generator covers a wide range of pre-programmed tones used in analog phone systems. Three outputs are provided: Ringing signals, In-band tones or FSK data, and 12kHz/16kHz Subscriber Metering pulses.

The PCM Codec-Filter performs voice digitization and reconstruction and incorporates band limiting and smoothing with selectable A-law or  $\mu$ -law companding following CCITT recommendation G.711. The DTMF decoder presents the serial bus interface with the DTMF dialing information received from the telephone user and the tone generator sends the appropriate DTMF tones to this POTS interface. Other tone standards supported are: Fax and Modem 'answer' and 'originate', ITU (CCITT) 'R1' and 'R2' signals, dual tones for CIDCW and 'On-Hook' signaling systems and sufficient tones for simple melody generation.

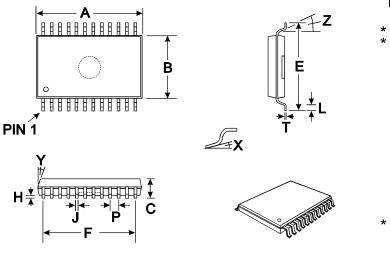

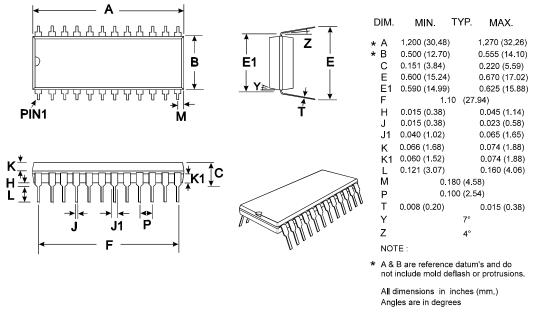

The IOM<sup>®</sup>-2 (ISDN Oriented Modular revision 2) industry standard serial bus provides the digital interface to other telecommunications ICs and supports both Terminal and non-Terminal (or Line Card) modes. The CMX625 is compatible with the CMX635 ISDN Subscriber Processor and can be used to provide the additional POTS port. It is available in both DIP and SSOP packages.

IOM<sup>®</sup> is a registered trademark of Seimens AG

## CONTENTS

#### Section

#### Page

| 4 | Diee | k Diaar  | am                                                                               | 4    |

|---|------|----------|----------------------------------------------------------------------------------|------|

| 1 |      |          |                                                                                  |      |

| 2 | •    |          |                                                                                  |      |

| 3 |      |          | mponents                                                                         |      |

| 4 | Gen  |          | scription                                                                        |      |

|   | 4.1  |          | 2 Serial Bus Interface                                                           |      |

|   | 4.2  |          | nal Mode                                                                         |      |

|   | 4.3  | Non-T    | erminal Modem (non-TE)                                                           | 11   |

|   | 4.4  | Monito   | or Channel Handshake Protocol                                                    | 12   |

|   | 4.5  | Monito   | or Channel Identification Command                                                | 14   |

|   | 4.6  | PCM      | Codec Filter                                                                     | 15   |

|   | 4.7  | Rx Inp   | out Amplifier                                                                    | .15  |

|   | 4.8  | Tx Ou    | Itput Buffer                                                                     | . 15 |

|   | 4.9  | Tone/    | FSK Encoder and Tone Encoder                                                     | 16   |

|   | 4.10 | SPM      | Generator                                                                        | .18  |

|   | 4.11 | Trans    | mit Signal Control                                                               | .19  |

|   | 4.12 | Tx UA    | RT                                                                               | 20   |

|   |      | 4.12.1   | Typical UART Timings                                                             | . 20 |

|   | 4.13 | DTMF     | Tone Decoder                                                                     | 21   |

|   | 4.14 | Regis    | ter Set                                                                          | .22  |

|   |      | 4.14.1   | Write Only Registers                                                             | . 22 |

|   |      | 4.14.2   | Read Only Registers                                                              | . 22 |

|   | 4.15 | Progra   | amming the CMX625                                                                | .23  |

|   | 4.16 | Gloss    | ary                                                                              | .24  |

| 5 | Appl | lication | Notes                                                                            | . 25 |

|   | 5.1  | Teleco   | om Tones                                                                         | 25   |

|   |      | 5.1.1    | Ringing Signals                                                                  | . 25 |

|   |      | 5.1.2    | On Hook 'CPE Alert Tones                                                         | . 26 |

|   |      | 5.1.3    | NYNEX (MRAA) - AMR Alert Tones (Single Tone)                                     | . 26 |

|   |      | 5.1.4    | Single Frequency Call Progress Tones                                             | . 26 |

|   |      | 5.1.5    | Dual Frequency Call Progress Tones                                               | . 27 |

|   |      | 5.1.6    | Dual Tone Multi Frequency Generation                                             | . 27 |

|   |      | 5.1.7    | Special Information Tones, Fax and Modem Tones and Customer Premises Alert Tones | . 27 |

|   |      | 5.1.8    | CCITT 'R1' Signaling Tones                                                       | . 28 |

|   |      | 5.1.9    | CCITT 'R2' Signaling Tones                                                       | . 28 |

| 6 | Perf | ormand | ce Specification          |  |

|---|------|--------|---------------------------|--|

|   | 6.1  | Electr | rical Performance         |  |

|   |      | 6.1.1  | Absolute Maximum Ratings  |  |

|   |      | 6.1.2  | Operating Limits          |  |

|   |      | 6.1.3  | Operating Characteristics |  |

|   |      |        | Timing                    |  |

|   | 6.2  | Packa  | aging                     |  |

MX-COM, Inc. reserves the right to changes specifications at any time and without notice.

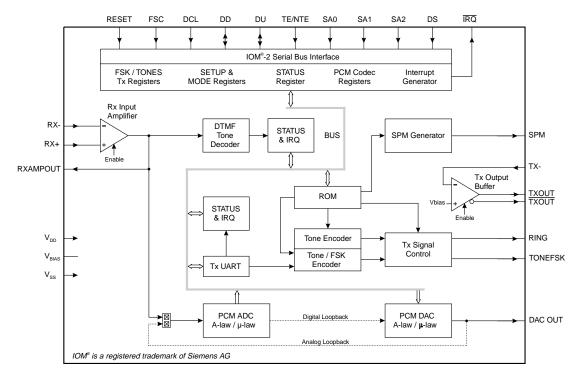

1 Block Diagram

Figure 1: Block Diagram

## 2 Signal List

| CMX625<br>D5/P4 | Si                | gnal           | Description                                                                                                                                                                                                                                                                                                                                          |

|-----------------|-------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.         | Name              | Туре           |                                                                                                                                                                                                                                                                                                                                                      |

| 1               | FSC               | input          | The IOM-2 Frame Synchronization Clock. This is an 8kHz clock indicating the start of the frame. FSC is generated by the upstream device. See section 4.1, 4.2, and 4.3.                                                                                                                                                                              |

| 2               | DCL               | input          | The IOM-2 Data Clock. It is used to clock data on and off the bus<br>and operates at 1.536MHz for Terminal mode (TE) or 4.096MHz<br>for non-Terminal mode (non-TE or Line Card mode). DCL is<br>generated by the upstream device. When the bus is deactivated,<br>DCL is held in a low state. See section 4.1, 4.2, and 4.3.                         |

| 3               | DD                | bi-directional | The IOM-2 Data Downstream, receives data from the network.<br>When the bus is deactivated or when data is not being<br>transmitted, DD is high impedance. The IC Channel Bus Reversal<br>(TE mode only) allows IC1 and IC2 data to be transmitted on the<br>DD pin. See section 4.1, 4.2, 4.3, and 4.6. An external pull-up<br>resistor is required. |

| 4               | DU                | bi-directional | The IOM-2 Data Upstream, transmits data to the network. When<br>the bus is deactivated or when data is not being transmitted, DU<br>is high impedance. The IC Channel Bus Reversal (TE mode only)<br>allows IC1 and IC2 data to be received on the DU pin. See<br>section 4.1, 4.2, 4.3, and 4.6. An external pull-up resistor is<br>required.       |

| 5               | TE/NTE            | input          | The IOM-2 two modes of operation: TE = 0 selects Terminal mode. NTE = 1 selects Non-Terminal mode or Line Card mode. See section 4.1, 4.2, and 4.3.                                                                                                                                                                                                  |

| 6               | SA0               | input          | The IOM-2 Slot Address, provides one of 8 unique addresses. It                                                                                                                                                                                                                                                                                       |

| 7               | SA1               | input          | allows the device to be individually addressed when more than one device is connected to the IOM-2 bus.                                                                                                                                                                                                                                              |

| 8               | SA2               | input          | See section 4.2 and 4.3.                                                                                                                                                                                                                                                                                                                             |

| 9               | DS                | input          | The IOM-2 Device Select pin (NTE mode only). Allows two CMX625 devices sharing a Slot Address to be individually addressed. DS = 0 selects device one. DS = 1 selects device two. See section 4.2 and 4.3.                                                                                                                                           |

| 10              | RESET             | input          | The external reset pin clears all the registers. (RESET=1)                                                                                                                                                                                                                                                                                           |

| 11              | ĪRQ               | output         | A 'wire-Orable' output Interrupt Request. This output is pulled down to $V_{SS}$ when active and is high impedance when inactive. An external pull-up resistor is required.                                                                                                                                                                          |

| 12              | V <sub>SS</sub>   | Power          | The negative supply rail (ground).                                                                                                                                                                                                                                                                                                                   |

| 13              | RX+               | input          | The non-inverting input of the receive op-amp.                                                                                                                                                                                                                                                                                                       |

| 14              | RX-               | input          | The inverting input of the receive op-amp.                                                                                                                                                                                                                                                                                                           |

| 15              | RXOUT             | output         | The output of the receive op-amp.                                                                                                                                                                                                                                                                                                                    |

| 16              | V <sub>BIAS</sub> | output         | An internally generated bias voltage of $V_{DD}/2$ , except when the device has been reset, $V_{BIAS}$ will discharge to $V_{SS}$ . It should be decoupled to $V_{SS}$ by a capacitor mounted close to the device pins.                                                                                                                              |

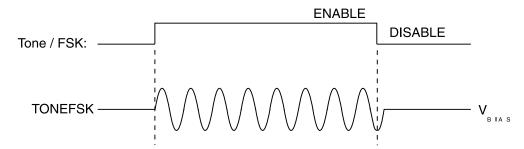

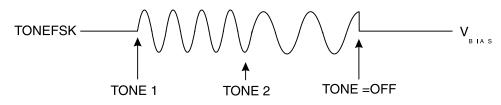

| 17              | TONEFSK           | output         | The sinewave output of the Tones and FSK signal generators.                                                                                                                                                                                                                                                                                          |

| 18              | TXOUT             | output         | The output of the buffer amplifier.                                                                                                                                                                                                                                                                                                                  |

| 19              | TX-               | input          | The inverting input to the buffer amplifier.                                                                                                                                                                                                                                                                                                         |

| 20              | TXOUT             | output         | The inverted output of the buffer amplifier.                                                                                                                                                                                                                                                                                                         |

| 21              | DAC OUT           | output         | The output from the digital-to-analog converter.                                                                                                                                                                                                                                                                                                     |

© 2001 MX-COM, Inc.

www.mxcom.com

Tel:

800 638 5577

336 744 5050

Fax:

336 744 5054

Doc. # 20480223.001

4800 Bethania Station Road, Winston-Salem, NC 27105-1201 USA

All trademarks and service marks are held by their respective companies.

All trademarks and service marks are held by their respective companies.

| CMX625<br>D5/P4 | Si              | gnal   | Description                                                                                                                                                                                 |

|-----------------|-----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.         | Name            | Туре   |                                                                                                                                                                                             |

| 22              | RING            | output | The square, trapezoidal and sinusoidal wave output from the Ringing Signal Generator.                                                                                                       |

| 23              | SPM             | output | The sinewave output of the SPM signal generator.                                                                                                                                            |

| 24              | V <sub>DD</sub> | Power  | The positive supply rail. Levels and thresholds within the device are proportional to this voltage. It should be decoupled to $V_{\rm SS}$ by a capacitor mounted close to the device pins. |

This device is capable of detecting and decoding small amplitude signals. To achieve this  $V_{DD}$  and  $V_{BIAS}$  decoupling and protecting the receive path from extraneous in-band signals are very important. It is recommended that the printed circuit board is laid out with a ground plane in the CMX625 area to provide a low impedance connection between the  $V_{SS}$  pin and the  $V_{DD}$  and  $V_{BIAS}$  decoupling capacitors.

## **3 External Components**

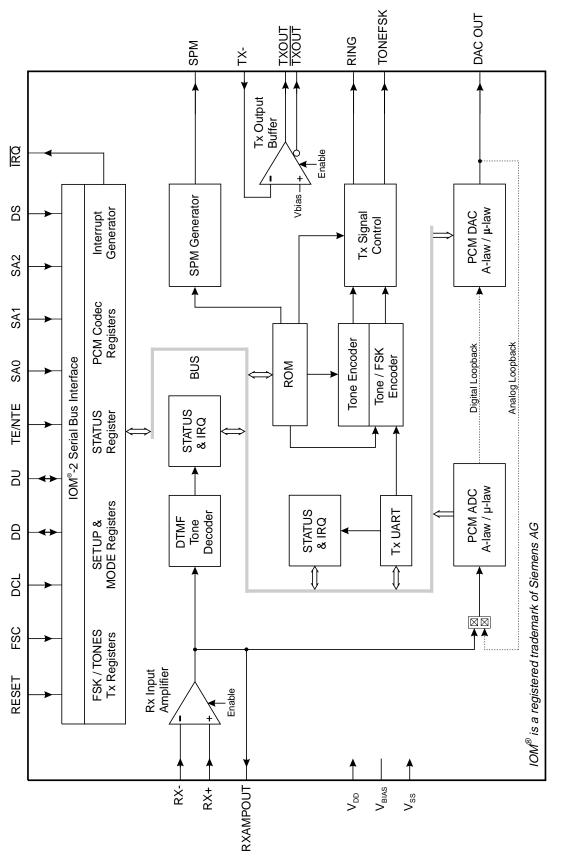

Figure 2: Recommended External Components

| R1, R3, R5 | 100kΩ  | 1 | C1, C2 | 1.0µF  |

|------------|--------|---|--------|--------|

| R2         | Note 1 |   | C3     | Note 1 |

| R4         | Note 2 |   | C4, C5 | 220pF  |

| R6, R7     | 1.5kΩ  |   |        |        |

Resistor ±5%, capacitors ±10% unless otherwise stated.

#### Table 1: Recommended External Components

#### Note:

1. R2, R3, C3 and C4 form the gain components for the Rx Input Amplifier. R2 should be chosen as required by the signal level, using the following formula:

Gain =

$$-\frac{R3}{R2}$$

C3 and R2 should be chosen so as not to compromise the low frequency performance.

2. R4 should be selected to give the desired transmit level.

data and an envelope control for SPM tones. The device also has an uncommitted Tx output buffer for filtering and impedance matching. The functions are controlled via an IOM-2 serial bus interface.

Frequency and timing accuracy of the CMX625 is supplied by the Data Clock (DCL) of the IOM-2 serial bus interface. If the bus is deactivated, DCL is held in a low state.

The CMX625 can be reset externally by driving the RESET pin low. It resets all the internal register bits and ensures that the interface always starts from a known state. The device can also be reset by issuing a RESET command. See section 4.14. Commands to enable and disable individual functions are also shown in this section. Approximately 50ms should be allowed for the Tx DC level to settle at  $V_{BIAS}$  before enabling the Tx functions (set bit 6 of the MODE Register to '1') after the CMX625 has been reset.

#### 4.1 IOM-2 Serial Bus Interface

The IOM<sup>®</sup>-2 (ISDN Oriented Modular revision 2) is an industry standard serial bus for interconnecting telecommunications IC's. (Refer to the IOM-2 Interface Reference Guide, Industry Standard Bus by Advanced Micro Devices). The bus is an evolution of the IOM® interface and is also known as the GCI (General Circuit Interface).

The IOM-2 bus provides a symmetrical full duplex communication link, containing user data, control/programming and status channels. There are two basic modes of operation known as Terminal mode (TE mode) and non-Terminal mode (non-TE or Line Card mode). These modes differ in the frame structure and data rate. The frame rate remains at 8kHz for each mode. The CMX625 acts as a timing and control slave to the upstream device.

The various channels are time multiplexed over a basic four wire serial interface, namely FSC, DCL, DD and DU. Frames are delimited by an 8kHz Frame Synchronization Clock (FSC) which is generated by the upstream device. The Data Clock (DCL) clocks data on and off the bus and runs at either 1.536MHz (TE mode) or 4.096MHz (non-TE mode). It is always generated by the upstream device. Data Downstream (DD) receives data from the network. Data Upstream (DU) transmits data to the network. When the bus is deactivated or when data is not being transmitted, DD and DU is held in a high impedance state. The DD and DU bus are driven by open drain transistors such that all DD's and DU's can be connected together. Bus reversal (in TE mode) allows the DD and DU pins to be both inputs and outputs in the IC1 and IC2 channels. It allows use of the CMX625 with post processing devices that are IOM-2 compliant. When other devices are connected to the IOM-2 bus the three Slot Address pins (SA0, SA1 and SA2) provide a unique address, allowing the CMX625 to be individually addressed. The Device Select pin (DS) allows two CMX625 devices sharing a slot address to be individually addressed in non-TE mode.

The remote digital IOM loopback is enabled when bit 3 of the IOM CONTROL Register is set to '1'. This loops back the data arriving on the IOM-2 bus and sends it back again. Unused bits in the frame structure are ignored if not required by the CMX625. These bits will be set to '1' when the frame is transmitted upstream.

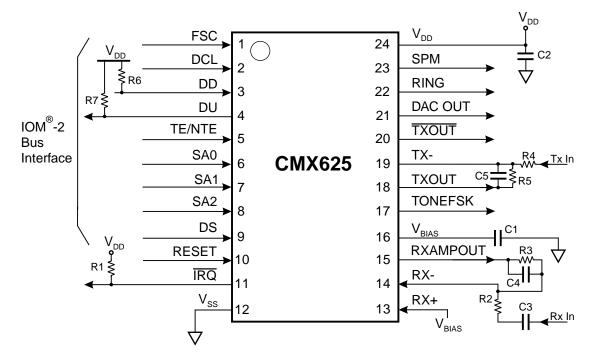

#### 4.2 Terminal Mode

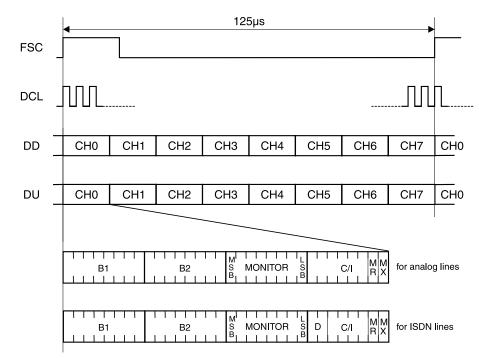

Terminal mode (TE) frame structure consists of 3 channels of 4 bytes each repeated at 8kHz, i.e. 96 bits in 125µs or a data rate of 768kbps. The Data Clock (DCL) operates at twice the data rate, i.e. 1.536MHz. Figure 3 shows the TE mode frame structure.

9

#### Figure 3: Terminal Mode Frame Structure

'Channel 0' is used for passing user data (2B+D channels) and controlling (MON0 and C/I0) the Layer 1 transceiver. Only 'Channel 1' is used by the CMX625. 'Channel 2' is reserved for D channel arbitration.

The 12 byte frame contains the following channels:

- (i) The 'B' channels consist of two 64kbps data channels, labeled B1 and B2, and transfer B channel data to and from the network.

- (ii) The 'Monitor' channels consist of two programming channels, labeled MON0 and MON1. Each channel consists of 8 bits of data and has two associated pair of handshake bits that control data flow, MX and MR (monitor transmit and receive). The handshake procedure is described in section 4.4. The MON1 channel is used for programming and controlling devices attached to the IOM-2 interface. The CMX625 is programmed via the MON1 channel (see section 4.15). The MON0 channel is not used. Monitor channel contention is avoided by a "speak when spoken to" system whereby the CMX625 is given a unique address, programmed with the 3 Slot Address pins (SA0 to SA2) and 1 Device Select pin (DS) and only responds when that address is broadcast by the master device (see section 4.14). The Monitor channel address byte is shown below:

| MON Channel     | Bit 7 | Bit 6                  | Bit 5                  | Bit 4                  | Bit 3                  | Bit 2 | Bit 1 | Bit 0 |

|-----------------|-------|------------------------|------------------------|------------------------|------------------------|-------|-------|-------|

| Address<br>Byte | 1     | Slot<br>Address<br>SA2 | Slot<br>Address<br>SA1 | Slot<br>Address<br>SA0 | Device<br>Select<br>DS | 0     | 0     | 0     |

The CMX625 cannot initiate MON communication directly in a multi-slave application. Each slave must monitor the MON channel for its unique address in the first byte before processing the following command. Each slave can therefore only drive the DU MON channel when specifically requested to by the master.

(iii) The 'D' channel consists of two bits providing 16kbps for carrying D channel user data. This channel is not used by the CMX625.

(iv) The 'Command/Indicate' channels, labeled C/I0 and C/I1, provide real time status information between devices connected via the IOM-2 bus. The C/I0 in channel 0 consists of 4 bits and the C/I1 in channel 1 is 6 bits wide. The C/I0 in channel 0 is not used.

The C/I1 channel is shared by all devices on the IOM-2 bus with no mechanism for determining and resolving contention. If multiple slave devices are expected to drive the C/I1 channel then care must be taken to allocate different bits to each device. An example of C/I1 channel usage would be 6 slave devices each allocated one of the 6 C/I1 bits. When a slave requires attention it asserts its own bit, which is detected by the master as a C/I1 value change (generating a processor interrupt). The processor would then initiate MON1 communications with the appropriate slave and service its request. This is an example of one usage, but the C/I1 bits may be used for any real time command/indicate purpose dependent on system design and number of slaves on the IOM-2 bus.

The C/I1 Channel Output Control Code is encoded as follows (bits 0, 1 and 2 of the IOM CONTROL Register):

| C/I1 Channel Output Control<br>Code (IOM Control Register,<br>Bits 2, 1 and 0) | C/I1 Channel Output Bit Content                                       |

|--------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| 0 0 0                                                                          | C/I1 bits 5-0 = all logic '1', i.e. C/I1 output disabled              |

| 0 0 1                                                                          | Interrupt Request (logic '0') on C/I1 bit 0)                          |

| 010                                                                            | Interrupt Request (logic '0') on C/I1 bit 1)                          |

| 0 1 1                                                                          | Interrupt Request (logic '0') on C/I1 bit 2) all other bits logic '1' |

| 100                                                                            | Interrupt Request (logic '0') on C/I1 bit 3)                          |

| 101                                                                            | Interrupt Request (logic '0') on C/I1 bit 4)                          |

| 1 1 0                                                                          | Interrupt Request (logic '0') on C/I1 bit 5)                          |

| 111                                                                            | Status Register bits 7-2 on C/I1 bits 5-0                             |

Code '000' is provided to disable drive of the C/I1 channel for use when multiple slaves have completely utilized the C/I1 channel resource. The Interrupt Mask Register settings are ignored and the C/I1 bits are set to logic '1'.

For codes '001' to '110' a logic '0' (Interrupt Request) is driven onto the appropriate C/I1 bit when the Status Register bits contain an unmasked logic '1' (set by the Interrupt Mask Register). This allows other devices to use the remaining C/I bits for their own purposes. The master device would use the change of the appropriate C/I bit to initiate a Status Register read from the CMX625.

Code '111' and an unmasked Status Register (INTERRUPT MASK bits 2 to 7 are set to '1') allows the most significant 6 bits of the Status Register to be driven onto the C/I1 channel directly for use when the CMX625 is the only slave utilizing the C/I channel. If any of the Status bits are masked, by setting the equivalent bit in the mask register to '0', then a logic '0' will be routed to the appropriate C/I1 bit and will not change.

- (v) The 'Intercommunication Channel' consists of two 64kbps data channels, labeled IC1 and IC2, and provide additional communications paths between devices other than the layer 1 device (data to and from the layer 1 device is transferred over the B channels).

- (vi) The 'TIC' (Terminal IC) bus is used for connecting more than one device to the D and C/I0 channels in Channel 0. The TIC bus is not used by the CMX625.

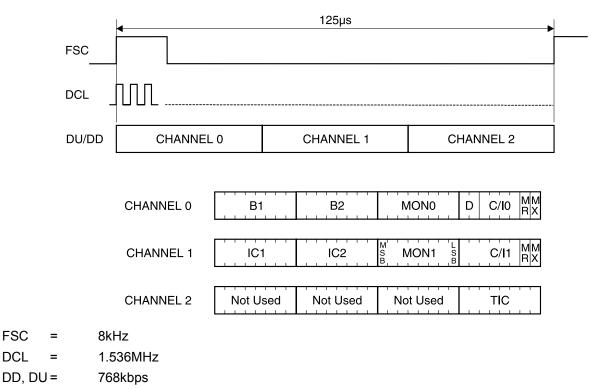

#### 4.3 Non-Terminal Mode (non-TE)

The non-TE mode (Line Card Mode) frame structure consists of up to 8 channels of 4 bytes each repeated at 8kHz, i.e. 256 bits in 125µs or a data rate of 2048kbps for 8 channel frames. The Data Clock (DCL) operates at twice the data rate, i.e. 4.096MHz. Figure 4 shows the non-TE mode frame structure.

11

FSC = 8kHz DCL = 4.096MHz DD, DU = 2048kbps

#### Figure 4: Non-Terminal Mode Frame Structure

In non-TE mode the IOM-2 bus time multiplexes data, control and status information for up to eight IOM-2 devices or up to 16 Codec-Filters over a single full duplex interface. The frames are subdivided into 8 channels, with one channel being dedicated to each IOM-2 device or pair of Codecs.

Each device on the IOM-2 bus is assigned a slot address and only transmits to and receives from that time slot. Pins SA0, SA1 and SA2 on the CMX625 are used to program the Slot Address. Outside the allocated slot the transmit drivers will be set to high impedance to allow other devices to transmit in their own time slot. To allow two CMX625 devices to share the same slot a Device Select pin (DS) is made available. This pin forms part of the Monitor Channel Address Byte along with the Slot Address pins and allows either of the two devices sharing a slot to be individually addressed. See section 4.2, part (ii) MON Channel Address Byte. This mechanism allows both the B1 and B2 data from the same time slot to be utilized by different devices.

Each channel consists of the following 4 bytes:

- (i) The first two bytes consist of two 64kbps data channels, labeled 'B1' and 'B2', and transfer B channel data to and from the network.

- (ii) The third byte, labeled 'Monitor', is used for programming and controlling devices attached to the IOM-2 interface. The data structure within the monitor channel is not defined and will be device specific. The CMX625 is programmed via the monitor channel (see section 4.15).

- (iii) In digital applications (ISDN line cards) the fourth byte contains two bits for the 16kbps 'D' channel, four 'Command/Indicate' (C/I) bits for real time status information and two handshake bits for supporting the handling of the monitor channel, labeled 'MR' and 'MX' (monitor transmit and receive). The handshake procedure is described in section 4.4. In analog applications (analog line cards) there is no 'D' channel in the fourth byte so the adjacent C/I channel is increased to 6 bits. The C/I1 channel bits are used in the same way as for Terminal Mode.

#### 4.4 Monitor Channel Handshake Protocol

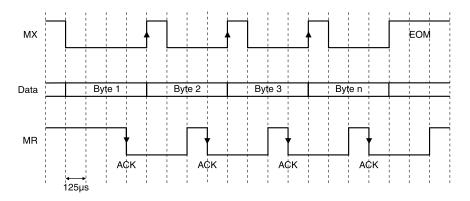

The Monitor channel operates on an event driven basis. While data transfers on the bus take place synchronized to the frame sync, the flow of data is controlled by a handshake procedure using the outgoing MX (monitor transmit) and incoming MR (monitor receive) bits. Data is placed onto the monitor channel and the MX bit is activated. This data will be transmitted repeatedly (once per 8kHz frame) until the transfer is acknowledged (ACK) via the MR bit. The actual data rate is not fixed but is dependent upon the response speed of the transmitter and receiver. The protocol is applicable to both TE and non-TE modes.

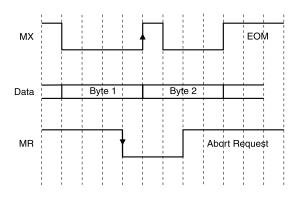

Figure 5: Monitor Handshake Timing (general case)

Figure 5 shows the general case for monitor handshake timing. The first byte of data is placed on the bus and MX is activated (low). MX remains active and the data remains valid until an inactive-to-active transition of MR is received, indicating that the receiver has read the data off the bus. The next byte is placed on the bus after the inactive-to-active transmission of MR, as early as the next frame (there is no limit to the maximum number of frames). At the time that the second byte is transmitted, MX is returned inactive (high) for one frame (MX inactive for more than one frame indicates an End of Message). In response to MX going active (low), MR will be deactivated (high) for one frame (the MX inactive to MR inactive delay can be any number of frames). This procedure is repeated for each additional byte. The transmitter sends an End of Message (EOM), after the last byte of data has been transmitted, by not reactivating MX after deactivating it.

The receiver can hold off the transmitter by keeping MR active until the receiver is ready for the next byte. The transmitter will not start the next transmission cycle until MR goes inactive.

The transmitter is able to abort a transmission by holding MX inactive (high) for two or more frames, this will generate an interrupt when the INTERRUPT MASK Register bit 3 is unmasked (logic '1') and bit 3 of the Status Register will be set to '1'.

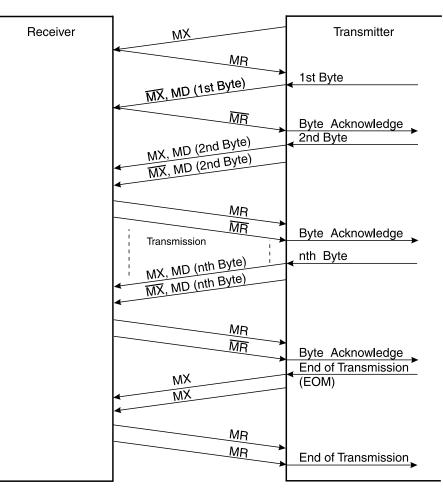

Figure 6 shows the monitor channel handshake procedure.

MX = Monitor Transmit Bit, active low.

MR = Monitor Receive Bit, active high.

MD = Monitor Data

#### Figure 6: Monitor Channel Handshake Procedure

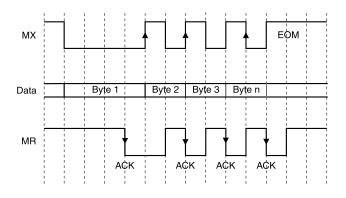

Figure 7 shows the maximum speed case for monitor handshake timing. The transmitter can be designed for a higher data throughput than is provided by the general case. The transmitter can deactivate (high) MX and transmit new data one frame after MR is deactivated. In this way, the transmitter is anticipating that MR will be reactivated one frame after it is deactivated, minimizing the delay between bytes. MR being held inactive (high) for two or more frames indicates an abort is being signaled by the receiver.

Figure 7: Monitor Handshake Timing (maximum speed case)

The abort is a signal from the receiver to the transmitter indicating that data has been missed. The receiver is able to abort a transmission by holding MR inactive (high) for two or more frames in response to MX going active. An abort from the receiver will generate an interrupt when the INTERRUPT MASK Register bit 2 is unmasked (logic '1') and bit 2 of the Status Register will be set to '1'. Figure 8 shows a monitor abort request from the receiver.

Figure 8: Abort Request from the Receiver

#### 4.5 Monitor Channel Identification Command

In order to be able to identify different devices on the IOM-2 bus, an identification command is sent. This allows the software to identify different manufacturer's devices on the bus. The identification sequence is usually done once, when the device is connected for the first time.

A device requesting the identity of a connected CMX625 will transmit the following 2 byte command:

|                         | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit 0 |

|-------------------------|------|------|------|------|------|------|------|-------|

| DD 1 <sup>st</sup> byte | 1    | SA2  | SA1  | SA0  | DS   | 0    | 0    | 0     |

| DD 2 <sup>nd</sup> byte | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0     |

The CMX625 responds by transmitting:

|                         | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit 0 |                              |

|-------------------------|------|------|------|------|------|------|------|-------|------------------------------|

| DU 1 <sup>st</sup> byte | 1    | SA2  | SA1  | SA0  | DS   | 0    | 0    | 0     | Monitor Channel Address Byte |

| DU 2 <sup>nd</sup> byte | 1    | 0    | 0    | 1    | 1    | 0    | 0    | 1     | Device Identification Byte   |

SA(2-0) = Slot Address, DS = Device Select (See sections 4.2 and 4.3). See section 4.14 for the Device Identification Register.

#### 4.6 PCM Codec Filter

The PCM Codec-Filter performs voice digitization and reconstruction and incorporates encoder bandpass and decoder lowpass filters with pre and post-filtering with selectable A-law and  $\mu$ -law companding. In each case the coder and decoder process a companded 8-bit PCM word following CCITT recommendation G.711 for A-law and  $\mu$ -law conversion. The encoder bandpass filter and decoder lowpass filter provide passband flatness and stopband rejection according to CCITT recommendation G.712. The lowpass filter contains the required (Sin X)/X compensation.

The PCM Codec-Filter block is enabled or disabled by bit 7 of the CODEC CONTROL Register. The companding law is selected by bit 6. When this bit is a '0', A-law companding is selected (used in Europe) and when this bit is a '1',  $\mu$ -law is selected (used in the USA and Japan).

The PCM Codec Channel routing is shown in the table below for normal operation and bus reversal. In 'normal' operation, bit 4 of the IOM Control Register is set to '0', the data is transmitted on the Data Upstream (DU) pin and received on the Data Downstream (DD) pin. Bits 6 and 7 of the IOM Control Register select whether the data is transmitted or received on the B1, B2, IC1 or IC2 channels of the IOM-2 bus. The B1 and B2 channels are available in TE and non-TE mode but the IC1 and IC2 channels are only available in TE mode.

|           | Codec Channel Input/Output Select      |                                                                 |                       |                     |  |  |  |  |  |  |  |

|-----------|----------------------------------------|-----------------------------------------------------------------|-----------------------|---------------------|--|--|--|--|--|--|--|

| (IOM Cont | Bus Reversal<br>trol Register<br>it 4) | Codec Channel Select<br>(IOM Control Register,<br>Bits 7 and 6) | Codec<br>Data<br>From | Codec<br>Data<br>To |  |  |  |  |  |  |  |

|           | 0                                      | 0 0                                                             | B1, DD                | B1, DU              |  |  |  |  |  |  |  |

| Normal    | 0                                      | 0 1                                                             | B2, DD                | B2, DU              |  |  |  |  |  |  |  |

| Normai    | 0                                      | 1 0                                                             | IC1, DD               | IC1, DU             |  |  |  |  |  |  |  |

|           | 0                                      | 11                                                              | IC2, DD               | IC2, DU             |  |  |  |  |  |  |  |

|           | 1                                      | 00                                                              | B1, DD                | B1, DU              |  |  |  |  |  |  |  |

| Reverse   | 1                                      | 01                                                              | B2, DD                | B2, DU              |  |  |  |  |  |  |  |

| Reveise   | 1                                      | 1 0                                                             | IC1, DU               | IC1, DD             |  |  |  |  |  |  |  |

|           | 1                                      | 1                                                               | IC2, DU               | IC2, DD             |  |  |  |  |  |  |  |

In Terminal mode (TE) it may also be necessary to transmit on the Data Downstream (DD) pin and receive on the Data Upstream (DU) pin during the IC1 and IC2 time slots. This can be achieved by selecting bus reversal and allows use of the CMX625 with post processing devices, such as speech scramblers, that are IOM-2 compliant. Bus Reversal is enabled when bit 4 of the IOM Control Register is set to '1' and programming the appropriate Codec Channel Select bits 6 and 7 of the IOM Control Register. When bus reversal is active, the master device and any other devices capable of bus reversal, are prohibited from broadcasting in the active IC channel.

The local codec loopback controls the internal paths such that loopback tests can be performed (see Figure 1). Local digital codec loopback is enabled when bit 4 of the CODEC CONTROL Register is set to '1'. This internally connects the ADC output to the DAC input.

Local analog codec loopback is enabled when bit 5 of the CODEC CONTROL Register is set to '1'. This internally connects the DAC output to the ADC input (the connection to the Rx Amp is broken). Data is loaded and read via the IOM-2 bus using the channels shown in the above table.

#### 4.7 Rx Input Amplifier

This amplifier, with suitable external components, is used for adjusting the received signal to the correct amplitude for the DTMF decoder and the PCM analog-to-digital converter. See Figure 2.

#### 4.8 Tx Output Buffer

This buffer is enabled by bit 7 of the SETUP register. With suitable external components it can be used for filtering and impedance matching. See Figure 2.

#### 4.9 Tone/FSK Encoder and Tone Encoder

These blocks are enabled or disabled by bit 6 of the SETUP register. When bit 5 of the MODE Register is set to '1' then these blocks generate FSK signals as determined by bit 0 of the SETUP Register and the Tx data bits from the UART block, as shown in the table below:

| SETUP Register<br>Bit 0 | Tone/FSK Generator   | FSK Signal Frequency<br>'0' (Space) | FSK Signal Frequency<br>'1' (Mark) |

|-------------------------|----------------------|-------------------------------------|------------------------------------|

| 0                       | V.23 1200bps FSK     | 2100Hz                              | 1300Hz                             |

| 1                       | Bell 202 1200bps FSK | 2200Hz                              | 1200Hz                             |

When bit 5 of the MODE Register is set to '0', these blocks generate single or dual tones from the range shown in the tables on the following pages. Bit 6 of the MODE Register is then used to enable or disable the block's output to the Tx Signal Control, RING and TONEFSK outputs. There are four tone fields addressed by bits 0 and 1 of the MODE Register.

| TX T | TX TONES Register Bits 4-7 |    |    | Frequency | TX <sup>-</sup> | TONES R | egister Bit | s 0-3 | Frequency |

|------|----------------------------|----|----|-----------|-----------------|---------|-------------|-------|-----------|

| D7   | D6                         | D5 | D4 | (Hz)      | D3              | D2      | D1          | D0    | (Hz)      |

| 0    | 0                          | 0  | 0  | 0 = OFF   | 0               | 0       | 0           | 0     | 0 = OFF   |

| 0    | 0                          | 0  | 1  | 252.4     | 0               | 0       | 0           | 1     | * 17.1    |

| 0    | 0                          | 1  | 0  | 268.7     | 0               | 0       | 1           | 0     | * 20.5    |

| 0    | 0                          | 1  | 1  | 285.3     | 0               | 0       | 1           | 1     | * 24.9    |

| 0    | 1                          | 0  | 0  | 315.5     | 0               | 1       | 0           | 0     | * 34.1    |

| 0    | 1                          | 0  | 1  | 330.5     | 0               | 1       | 0           | 1     | * 41.0    |

| 0    | 1                          | 1  | 0  | 375.2     | 0               | 1       | 1           | 0     | * 51.2    |

| 0    | 1                          | 1  | 1  | 404.3     | 0               | 1       | 1           | 1     | -         |

| 1    | 0                          | 0  | 0  | 468.0     | 1               | 0       | 0           | 0     | 262.9     |

| 1    | 0                          | 0  | 1  | 495.8     | 1               | 0       | 0           | 1     | 293.6     |

| 1    | 0                          | 1  | 0  | 520.6     | 1               | 0       | 1           | 0     | 348.2     |

| 1    | 0                          | 1  | 1  | 548.0     | 1               | 0       | 1           | 1     | 392.6     |

| 1    | 1                          | 0  | 0  | 562.8     | 1               | 1       | 0           | 0     | 1600      |

| 1    | 1                          | 0  | 1  | 578.4     | 1               | 1       | 0           | 1     | 1633      |

| 1    | 1                          | 1  | 0  | 595.0     | 1               | 1       | 1           | 0     | 1827      |

| 1    | 1                          | 1  | 1  | 612.5     | 1               | 1       | 1           | 1     | 587.2     |

Tone Field 0, MODE Register bit 1 and bit 0 = '0' and '0' respectively.

\* These outputs are routed to the RING digital output instead of the TONEFSK output. Any single tone output level at TONEFSK output is 0dBm.

| ΤΧ ΤΟΙ | NES Reg | ister Bits | s 4-7 | Frequency | TX | TONES R | egister Bit | s 0-3 | Frequency |

|--------|---------|------------|-------|-----------|----|---------|-------------|-------|-----------|

| D7     | D6      | D5         | D4    | (Hz)      | D3 | D2      | D1          | D0    | (Hz)      |

| 0      | 0       | 0          | 0     | 0 = OFF   | 0  | 0       | 0           | 0     | 0 = OFF   |

| 0      | 0       | 0          | 1     | 120       | 0  | 0       | 0           | 1     | 330       |

| 0      | 0       | 1          | 0     | 150       | 0  | 0       | 1           | 0     | 416       |

| 0      | 0       | 1          | 1     | 154       | 0  | 0       | 1           | 1     | 420       |

| 0      | 1       | 0          | 0     | 250       | 0  | 1       | 0           | 0     | 425       |

| 0      | 1       | 0          | 1     | 300       | 0  | 1       | 0           | 1     | 433       |

| 0      | 1       | 1          | 0     | 350       | 0  | 1       | 1           | 0     | 440       |

| 0      | 1       | 1          | 1     | 360       | 0  | 1       | 1           | 1     | 450       |

| 1      | 0       | 0          | 0     | 367       | 1  | 0       | 0           | 0     | 460       |

| 1      | 0       | 0          | 1     | 375       | 1  | 0       | 0           | 1     | 480       |

| 1      | 0       | 1          | 0     | 380       | 1  | 0       | 1           | 0     | 500       |

| 1      | 0       | 1          | 1     | 383       | 1  | 0       | 1           | 1     | 600       |

| 1      | 1       | 0          | 0     | 400       | 1  | 1       | 0           | 0     | 620       |

| 1      | 1       | 0          | 1     | 450       | 1  | 1       | 0           | 1     | 720       |

| 1      | 1       | 1          | 0     | 475       | 1  | 1       | 1           | 0     | 930       |

| 1      | 1       | 1          | 1     | 480       | 1  | 1       | 1           | 1     | -         |

#### Tone Field 1, MODE Register bit 1 and bit 0 = '0' and '1' respectively

#### Tone Field 2, MODE Register bit 1 and bit 0 = '1' and '0' respectively

| TX TON | ES Regis | ter Bits | 4-7 | Frequency | TX TO | NES Reg | ister Bits | 0-3 | Frequency |

|--------|----------|----------|-----|-----------|-------|---------|------------|-----|-----------|

| D7     | D6       | D5       | D4  | (Hz)      | D3    | D2      | D1         | D0  | (Hz)      |

| 0      | 0        | 0        | 0   | 0 = OFF   | 0     | 0       | 0          | 0   | 0 = OFF   |

| 0      | 0        | 0        | 1   | 700       | 0     | 0       | 0          | 1   | 700       |

| 0      | 0        | 1        | 0   | 900       | 0     | 0       | 1          | 0   | 900       |

| 0      | 0        | 1        | 1   | 1100      | 0     | 0       | 1          | 1   | 1100      |

| 0      | 1        | 0        | 0   | 1300      | 0     | 1       | 0          | 0   | 1300      |

| 0      | 1        | 0        | 1   | 1500      | 0     | 1       | 0          | 1   | 1500      |

| 0      | 1        | 1        | 0   | 1700      | 0     | 1       | 1          | 0   | 1700      |

| 0      | 1        | 1        | 1   | -         | 0     | 1       | 1          | 1   | -         |

| 1      | 0        | 0        | 0   | 950       | 1     | 0       | 0          | 0   | 2100      |

| 1      | 0        | 0        | 1   | 1400      | 1     | 0       | 0          | 1   | 2225      |

| 1      | 0        | 1        | 0   | 1800      | 1     | 0       | 1          | 0   | -         |

| 1      | 0        | 1        | 1   | 2130      | 1     | 0       | 1          | 1   | 2750      |

| 1      | 1        | 0        | 0   | 697       | 1     | 1       | 0          | 0   | 1209      |

| 1      | 1        | 0        | 1   | 770       | 1     | 1       | 0          | 1   | 1336      |

| 1      | 1        | 1        | 0   | 852       | 1     | 1       | 1          | 0   | 1477      |

| 1      | 1        | 1        | 1   | 941       | 1     | 1       | 1          | 1   | 1633      |

| TX TON | ES Regis | ter Bits | 4-7 | Frequency | тх то | ONES Re | gister Bits | 0-3 | Frequency |

|--------|----------|----------|-----|-----------|-------|---------|-------------|-----|-----------|

| D7     | D6       | D5       | D4  | (Hz)      | D3    | D2      | D1          | D0  | (Hz)      |

| 0      | 0        | 0        | 0   | 0 = OFF   | 0     | 0       | 0           | 0   | 0 = OFF   |

| 0      | 0        | 0        | 1   | 540       | 0     | 0       | 0           | 1   | 540       |

| 0      | 0        | 1        | 0   | 660       | 0     | 0       | 1           | 0   | 660       |

| 0      | 0        | 1        | 1   | 780       | 0     | 0       | 1           | 1   | 780       |

| 0      | 1        | 0        | 0   | 900       | 0     | 1       | 0           | 0   | 900       |

| 0      | 1        | 0        | 1   | 1020      | 0     | 1       | 0           | 1   | 1020      |

| 0      | 1        | 1        | 0   | 1140      | 0     | 1       | 1           | 0   | 1140      |

| 0      | 1        | 1        | 1   | -         | 0     | 1       | 1           | 1   | -         |

| 1      | 0        | 0        | 0   | 1380      | 1     | 0       | 0           | 0   | 1380      |

| 1      | 0        | 0        | 1   | 1500      | 1     | 0       | 0           | 1   | 1500      |

| 1      | 0        | 1        | 0   | 1620      | 1     | 0       | 1           | 0   | 1620      |

| 1      | 0        | 1        | 1   | 1740      | 1     | 0       | 1           | 1   | 1740      |

| 1      | 1        | 0        | 0   | 1860      | 1     | 1       | 0           | 0   | 1860      |

| 1      | 1        | 0        | 1   | 1980      | 1     | 1       | 0           | 1   | 1980      |

| 1      | 1        | 1        | 0   | -         | 1     | 1       | 1           | 0   | -         |

| 1      | 1        | 1        | 1   | -         | 1     | 1       | 1           | 1   | -         |

#### Tone Field 3, MODE Register bit 1 and bit 0 = '1' and '1' respectively

#### 4.10 SPM Generator

This block operates independently and has its own output pin. It can transmit 12kHz or 16kHz and is controlled by bit 4 of the SETUP Register. Bit 7 of the MODE Register is used to enable or disable this block. The signal has a rise and fall time each of about 4ms. The SPM signal rises from the bias level to 0dBm in 16 steps of  $\approx$ 2dB magnitude, and falls from 0dBm to bias level in 16 steps of  $\approx$ 2dB magnitude.

#### 4.11 Transmit Signal Control

This block adjusts the amplitude of the FSK transmit signal output level, the level skew between DTMF tones and the signal routing to the output ports.

Output signal levels are proportional to  $V_{DD}$ . The nominal output signal levels (at 0dB attenuation and  $V_{DD}$  = 5.0V) are:

| Single Tone              | 0dBm  |

|--------------------------|-------|

| Dual Tone (per tone)     | -3dBm |

| DTMF High Frequency Tone | -3dBm |

| DTMF Low Frequency Tone  | -5dBm |

| FSK Signal               | 0dBm  |

The level attenuator provides for level adjustment from 0dB to -14dB in -2dB steps. The typical level is determined by bits 2 to 4 of the MODE Register as shown in the table below:

| MO    | DE Regis | ster  | Signal Level Adjustment |

|-------|----------|-------|-------------------------|

| Bit 4 | Bit 3    | Bit 2 | (dB)                    |

| 0     | 0        | 0     | 0                       |

| 0     | 0        | 1     | -2                      |

| 0     | 1        | 0     | -4                      |

| 0     | 1        | 1     | -6                      |

| 1     | 0        | 0     | -8                      |

| 1     | 0        | 1     | -10                     |

| 1     | 1        | 0     | -12                     |

| 1     | 1        | 1     | -14                     |

The RING signal is a square, trapezoidal or sinusoidal wave. The square and trapezoidal wave have an amplitude of  $\approx V_{DD}$  peak to peak and the sinusoidal wave has an amplitude of  $\approx V_{DD}/2$  peak to peak. The trapezoidal ringing waveform has a crest factor (CF) of 1.35. Bits 2 and 3 of the SETUP Register select the waveform type as shown in the table below. When the RING signal is not selected, the RING output pin is connected to V<sub>SS</sub>.

| SETU  | TUP Register RING Signal Select |                  |  |  |

|-------|---------------------------------|------------------|--|--|

| Bit 3 | Bit 2                           |                  |  |  |

| 0     | 0                               | Square wave      |  |  |

| 0     | 1                               | Trapezoidal wave |  |  |

| 1     | 0                               | Sinusoidal wave  |  |  |

#### 4.12 Tx UART

This block connects the IOM-2 serial bus interface to the FSK Encoder.

The block can be programmed to convert transmit data from 8-bit bytes to asynchronous data characters by adding Start and Stop bits. The transmit data is then passed to the FSK Encoder.

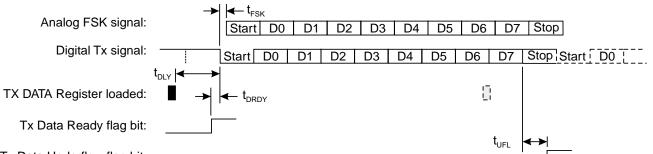

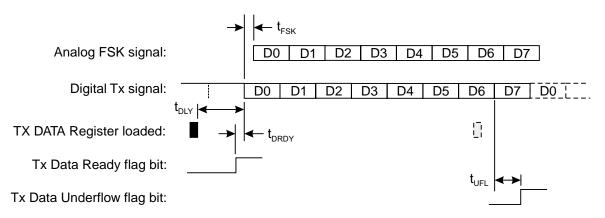

Data to be transmitted should be loaded, via the IOM-2 bus interface, into the TX DATA Register when the Tx Data Ready bit (bit 6) of the STATUS Register goes high. It will then be treated by the Tx UART block in one of two ways, depending on the setting of bit 1 of the SETUP Register:

If bit 1 of the SETUP Register is '0' (Tx Sync mode) then the 8 bits from the TX DATA Register will be transmitted sequentially at 1200bps, LSB (D0) first.

If bit 1 of the SETUP Register is '1' (Tx Async mode) then bits will be transmitted as asynchronous data characters at 1200 bps according to the following format:

One Start bit (Space) Eight Data bits (D0-D7) from the TX DATA Register, with the LSB (D0) transmitted first One Stop bit (Mark)

Failure to load the TX DATA Register with a new value when required will result in bit 7 (Tx Data Underflow) of the STATUS Register being set to '1'. If the 'Tx Async' mode of operation is selected then a continuous Mark ('1') signal will be transmitted until a new value is loaded into TX DATA. If the 'Tx Sync' mode is selected then the byte already in the TX DATA Register will be re-transmitted.

Tx Data Underflow flag bit:

Figure 10: Transmit UART Function (Sync)

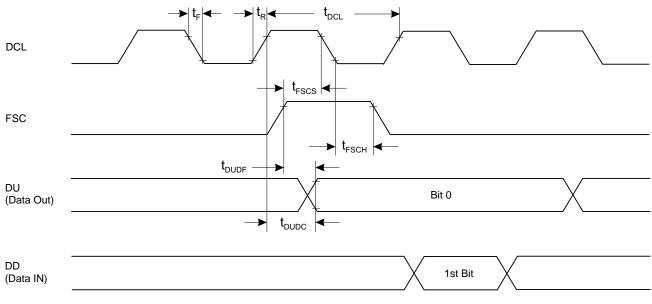

#### 4.12.1 Typical UART Timings

| Typical           | UART Timings (See Figure 9 and Figure 10 | Min. | Тур. | Max. | Unit |

|-------------------|------------------------------------------|------|------|------|------|

| t <sub>FSK</sub>  | delay through the modulator              | -    | 106  | -    | μs   |

| t <sub>DLY</sub>  | 1 bit period                             | -    | 833  | -    | μs   |

| t <sub>DRDY</sub> | 1/4 bit-period                           | -    | 208  | -    | μs   |

| t <sub>UFL</sub>  | ¾ bit-period                             | -    | 625  | -    | μs   |

<u>2</u>0

#### 4.13 DTMF Tone Decoder

This block is enabled or disabled by bit 5 of the SETUP register. If disabled, bit 4 and 5 of the STATUS Register and bit 0 to bit 3 of the DTMF RX DATA Register are set to '0' and no interrupts are generated. When enabled (set to '1'), a status change of the decoder will generate an interrupt when the INTERRUPT MASK Register bit 5 is unmasked (logic '1') and bit 5 of the STATUS Register will be set to '1'. The validity of the data is indicated by bit 4 of the STATUS Register. The decode truth table is shown below:

| DTMF I        | RX DATA F     | Register Bit  | s 0 - 3       | DTMF To                 | one Pairs               | Keypad |

|---------------|---------------|---------------|---------------|-------------------------|-------------------------|--------|

| Bit 3<br>(D3) | Bit 2<br>(D2) | Bit 1<br>(D1) | Bit 0<br>(D0) | Lower Frequency<br>(Hz) | Upper Frequency<br>(Hz) | Legend |

| 0             | 0             | 0             | 0             | 941                     | 1633                    | D      |

| 0             | 0             | 0             | 1             | 697                     | 1209                    | 1      |

| 0             | 0             | 1             | 0             | 697                     | 1336                    | 2      |

| 0             | 0             | 1             | 1             | 697                     | 1477                    | 3      |

| 0             | 1             | 0             | 0             | 770                     | 1209                    | 4      |

| 0             | 1             | 0             | 1             | 770                     | 1336                    | 5      |

| 0             | 1             | 1             | 0             | 770                     | 1477                    | 6      |

| 0             | 1             | 1             | 1             | 852                     | 1209                    | 7      |

| 1             | 0             | 0             | 0             | 852                     | 1336                    | 8      |

| 1             | 0             | 0             | 1             | 852                     | 1477                    | 9      |

| 1             | 0             | 1             | 0             | 941                     | 1336                    | 0      |

| 1             | 0             | 1             | 1             | 941                     | 1209                    | *      |

| 1             | 1             | 0             | 0             | 941                     | 1477                    | #      |

| 1             | 1             | 0             | 1             | 697                     | 1633                    | А      |

| 1             | 1             | 1             | 0             | 770                     | 1633                    | В      |

| 1             | 1             | 1             | 1             | 852                     | 1633                    | С      |

A status change of the decoder and the generation of an interrupt (when the INTERRUPT MASK Register bit 5 is unmasked) will occur both when a tone is first decoded and also when a tone, which was previously present, is no longer decoded. In the latter case, bit 4 of the STATUS Register will be set to '0' to indicate that no tone was detected.

#### 4.14 Register Set

#### 4.14.1 Write Only Registers

|       |                   |                                              |                                    |                                   | Data Byte                                                       | Structure                                                      |                                          |                                          |                                          |

|-------|-------------------|----------------------------------------------|------------------------------------|-----------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|

| Addr. | Register          | 7                                            | 6                                  | 5                                 | 4                                                               | 3                                                              | 2                                        | 1                                        | 0                                        |

| \$1   | RESET             | N/A                                          | N/A                                | N/A                               | N/A                                                             | N/A                                                            | N/A                                      | N/A                                      | N/A                                      |

| \$3   | SETUP             | Tx Output<br>Buffer<br>0=Disable<br>1=Enable | Tx Enable<br>0=Disable<br>1=Enable | DTMF Rx:<br>0=Disable<br>1=Enable | SPM:<br>0=12kHz<br>1=16kHz                                      | Ring Signal<br>Select [1]                                      | Ring Signal<br>Select [0]                | FSK Mode:<br>0=Sync<br>1=Async           | FSK Mode:<br>0=V.23<br>1=Bell 202        |

| \$4   | MODE              | SPM O/P:<br>0=Disable<br>1=Enable            | Tone/FSK:<br>0=Disable<br>1=Enable | Tone/FSK:<br>0=Tone<br>1=FSK      | Tx Level:<br>MSB                                                | Tx Level:<br>LSB                                               |                                          | Tone Fields:<br>MSB                      | Tone Fields:<br>LSB                      |

| \$5   | TX DATA           | D7<br>MSB                                    | D6                                 | D5                                | D4                                                              | D3                                                             | D2                                       | D1                                       | D0<br>LSB                                |

| \$6   | TX TONES          | D7<br>MSB                                    | D6                                 | D5                                | D4<br>LSB                                                       | D3<br>MSB                                                      | D2                                       | D1                                       | D0<br>LSB                                |

| \$8   | IOM<br>CONTROL    | Codec<br>Channel<br>Select [1]               | Codec<br>Channel<br>Select [0]     | 0                                 | IC Channel<br>Bus Reversal<br>0=Normal<br>1=Reverse             | Remote<br>Digital IOM<br>Loopback<br>0=No loopbk<br>1=Loopback | C/I1<br>Channel<br>Output<br>Control [2] | C/I1<br>Channel<br>Output<br>Control [1] | C/I1<br>Channel<br>Output<br>Control [0] |

| \$9   | INTERRUPT<br>MASK | Mask<br>Status [7]                           | Mask<br>Status [6]                 | Mask<br>Status [5]                | Mask<br>Status [4]                                              | Mask<br>Status [3]                                             | Mask<br>Status [2]                       | 0                                        | 0                                        |

| \$C   | CODEC<br>CONTROL  | Codec<br>Enable<br>0=Disable<br>1=Enable     | PCM Codec:<br>0=A-Law<br>1=µ-Law   |                                   | Local<br>Digital Codec<br>Loopback<br>0=No loopbk<br>1=Loopback | 0                                                              | 0                                        | 0                                        | 0                                        |

#### 4.14.2 Read Only Registers

| -     |                 |                                       | Data Byte Structure               |                              |                                                 |                              |                          |                          |                              |  |  |  |

|-------|-----------------|---------------------------------------|-----------------------------------|------------------------------|-------------------------------------------------|------------------------------|--------------------------|--------------------------|------------------------------|--|--|--|

| Addr. | Register        | 7                                     | 6                                 | 5                            | 4                                               | 3                            | 2                        | 1                        | 0                            |  |  |  |

| \$0   | DEVICE<br>ID    | 1                                     | 0                                 | 0                            | 1                                               | 1                            | 0                        | 0                        | 1                            |  |  |  |

| \$A   | STATUS          | FSK Mode:<br>FSK Tx Data<br>Underflow | FSK Mode:<br>FSK Tx Data<br>Ready | DTMF Rx:<br>Status<br>Change | DTMF Rx:<br>1=Detected<br>0=No Tone<br>Time Out | IOM:<br>Tx<br>Abort          | IOM:<br>Rx<br>Abort      | 0                        | 0                            |  |  |  |

| \$B   | DTMF RX<br>DATA | 0                                     | 0                                 | 0                            | 0                                               | DTMF:<br>Rx Data<br>(D3 MSB) | DTMF:<br>Rx Data<br>(D2) | DTMF:<br>Rx Data<br>(D1) | DTMF:<br>Rx Data<br>(D0 LSB) |  |  |  |

#### Notes:

- Accessing the RESET Register clears all of the bits in the SETUP, MODE, TX DATA, TX TONES, IOM CONTROL, INTERRUPT MASK, CODEC CONTROL, STATUS and DTMF RX DATA registers and will initialize the device. This a single-byte transaction consisting of the address byte value \$1.

- 2. If any of bits 2, 3, 4, 5, 6 or 7 of the STATUS Register is '1' then the IRQ output will be pulled low when the appropriate bit contains an unmasked logic '1' in the INTERRUPT MASK Register.

- **3.** Reading the STATUS Register clears the IRQ output and also clears bits 2, 3, and 5 of the STATUS Register, if set. Bits 6 and 7 of the STATUS Register are cleared on writing to the TX DATA Register.

#### 4.15 Programming the CMX625

The CMX625 is programmed via the 'MON1' (Monitor Channel 1) channel in TE mode and the 'Monitor' channel in non-TE mode. The programming sequence consists of 3 consecutive Monitor bytes: the IOM-2 address, the CMX625 command and data byte. Before executing a command, the CMX625 compares the received IOM-2 address byte with its own address. The MSB of the IOM-2 address is always a '1' (See section 4.2). A logical '1' in the MSB of the CMX625 command represents a write operation and a logical '0' represents a read operation.

Structure for Register read/write operations:

| IOM<br>Command<br>Register | R/W<br>0=Read<br>1=Write | 0 | х | х | Register<br>Address<br>A3 | Register<br>Address<br>A2 | Register<br>Address<br>A1 | Register<br>Address<br>A0 |

|----------------------------|--------------------------|---|---|---|---------------------------|---------------------------|---------------------------|---------------------------|

|----------------------------|--------------------------|---|---|---|---------------------------|---------------------------|---------------------------|---------------------------|

Example 1: Program the CMX625 to generate interrupt requests for DTMF RX Status Change on bit 5 of C/I channel, i.e. C/I1 Channel Output Control Code (2-0)=110. Set IOM-2 address to SA2-SA0=010 and device select, DS=1.

| MX<br>(DD) | MR<br>(DU) | DD<br>(hex) | MX<br>(DU) | MR<br>(DD) | DU<br>(hex) | Comment                                          |

|------------|------------|-------------|------------|------------|-------------|--------------------------------------------------|

| 1          | 1          | FF          | 1          | 1          | FF          | Monitor Channel Idle State                       |

| 0          | 1          | A8          | 1          | 1          | FF          | Transmit IOM-2 Address                           |

| 0          | 0          | A8          | 1          | 1          | FF          | Acknowledge Address                              |

| 1          | 0          | 88          | 1          | 1          | FF          | Transmit Command (Write IOM-2 Control, \$8)      |

| 0          | 1          | 88          | 1          | 1          | FF          |                                                  |

| 1          | 0          | 06          | 1          | 1          | FF          | Acknowledge Command/ Transmit IOM-2 Control Data |

| 0          | 1          | 06          | 1          | 1          | FF          |                                                  |

| 1          | 0          | FF          | 1          | 1          | FF          | Acknowledge Data                                 |

| 1          | 1          | FF          | 1          | 1          | FF          | End of Transmission                              |

| 0          | 1          | A8          | 1          | 1          | FF          | Transmit IOM-2 Address                           |

| 0          | 0          | A8          | 1          | 1          | FF          | Acknowledge Address                              |

| 1          | 0          | 89          | 1          | 1          | FF          | Transmit Command (Write Mask Register, \$9)      |

| 0          | 1          | 89          | 1          | 1          | FF          |                                                  |

| 1          | 0          | 20          | 1          | 1          | FF          | Acknowledge Command/ Transmit IOM-2 Control Data |

| 0          | 1          | 20          | 1          | 1          | FF          |                                                  |

| 1          | 0          | FF          | 1          | 1          | FF          | Acknowledge Data                                 |

| 1          | 1          | FF          | 1          | 1          | FF          | End of Transmission                              |

| 1          | 1          | FF          | 1          | 1          | FF          | Idle                                             |

If the command is a register read then only the address and command bytes are sent. The CMX625 will respond with an IOM-2 Register address byte followed by the read data. The IOM-2 Register address byte consists of the Register address that is being read in the least significant 4 bits and the IOM-2 address (less the device select bit) in the most significant 4 bits.

Example 2: Read the CMX625 DTMF RX DATA register, D3-D0=\$A. Set IOM-2 address to SA2-SA0 =100 and device select, DS=0.

| MX<br>(DD) | MR<br>(DU) | DD<br>(hex) | MX<br>(DU) | MR<br>(DD) | DU<br>(hex) | Comment                                     |

|------------|------------|-------------|------------|------------|-------------|---------------------------------------------|

| 1          | 1          | FF          | 1          | 1          | FF          | Monitor Channel Idle State                  |

| 0          | 1          | C0          | 1          | 1          | FF          | Transmit IOM-2 Address                      |

| 0          | 0          | C0          | 1          | 1          | FF          | Acknowledge Address                         |

| 1          | 0          | 0B          | 1          | 1          | FF          | Transmit Command (Write IOM-2 Control, \$B) |

| 0          | 1          | 0B          | 1          | 1          | FF          |                                             |

| 1          | 0          | FF          | 0          | 1          | СВ          | Acknowledge Command/ Send Address           |

| 1          | 1          | FF          | 0          | 0          | CB          | Address Acknowledged                        |

| 1          | 1          | FF          | 1          | 0          | 0A          | Send DTMF Read Data                         |

| 1          | 1          | FF          | 0          | 1          | 0A          |                                             |

| 1          | 1          | FF          | 1          | 0          | FF          | Data Acknowledged                           |

| 1          | 1          | FF          | 1          | 1          | FF          | End of Transmission                         |

| 1          | 1          | FF          | 1          | 1          | FF          | Idle                                        |

#### 4.16 Glossary

| ADC   | Analog to Digital Converter                                  |

|-------|--------------------------------------------------------------|

| CCITT | International Telegraph and Telephone Consultative Committee |

| CIDCW | Caller Identification During Call Waiting                    |

| CODEC | Coder/Decoder                                                |

| DAC   | Digital to Analog Converter                                  |

| DTMF  | Dual Tone Multiple Frequency                                 |

| FSK   | Frequency Shift Keying                                       |

| GCI   | General Circuit Interface                                    |

| IOM-2 | ISDN Oriented Modular revision 2                             |

| ISDN  | Integrated Services Digital Network                          |

| ITU   | International Telecommunication Union                        |

| NTU   | Network Termination Unit                                     |

| PC    | Personal Computer                                            |

| РСМ   | Pulse Code Modulation                                        |

| POTS  | Plain Old (Analog) Telephone Service                         |

| SPM   | Subscriber Pulse Metering                                    |

|       |                                                              |

## 5 Application Notes

When using the Tone/FSK bit (bit 6) of the MODE Register, each tone starts from  $V_{BIAS}$ , and returns to  $V_{BIAS}$  before ending:

Figure 11: Tone Starting and Stopping

When switching between tones in the same column (bits 4 - 7 or bits 0 - 3) of the TX TONES Register), the transition will be phase continuous. However, switching to the 'OFF' state will immediately take the output of that tone generator to  $V_{BIAS}$ .

#### Figure 12: Tone Changing

The TX TONES Register which does not have a frequency allocated is indicated by '-' in the Tone Field tables. These values should not be used.

#### 5.1 Telecom Tones

The following tables give the hex codes to be programmed into the particular tone field location for various telecommunications systems applications. The tables are not exhaustive, but list the more commonly used tones.

#### 5.1.1 Ringing Signals

| (f ±2.5%) (Hz) | Field 0 (Hex) |

|----------------|---------------|

| Off            | \$00          |

| 16.7           | \$01          |

| 20             | \$02          |

| 25             | \$03          |

| 35             | \$04          |

| 40             | \$05          |

| 50             | \$06          |

#### 5.1.2 On Hook CPE Alert Tones

| Single Tone (Hz) | Field 0 (Hex) |

|------------------|---------------|

| 375.2            | \$60          |

| 404.3            | \$70          |

| 468              | \$80          |

| 495.8            | \$90          |

| 520.6            | \$A0          |

| 548              | \$B0          |

| 562.8            | \$C0          |

| 578.4            | \$D0          |

| 1633             | \$0D          |

| I Tone (Hz) Field C                                                                                        | ) (Hex)                    |

|------------------------------------------------------------------------------------------------------------|----------------------------|

| 5.2+1827 \$6                                                                                               | 6E                         |

| 4.3+1827 \$7                                                                                               | 7E                         |

| 68+1827 \$8                                                                                                | 3E                         |

| 5.8+1827 \$9                                                                                               | )E                         |

| 0.6+1827 \$A                                                                                               | ٩Ε                         |

| 48+1827 \$E                                                                                                | 3E                         |

| 2.8+1827 \$0                                                                                               | СЕ                         |

| 8.4+1827 \$E                                                                                               | DE                         |