# WE® DSP32 Digital Signal Processor

## Description

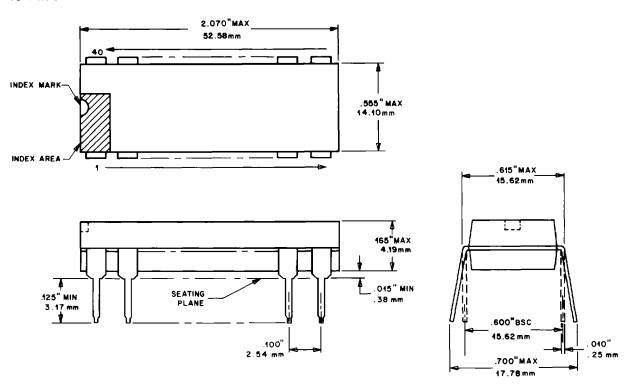

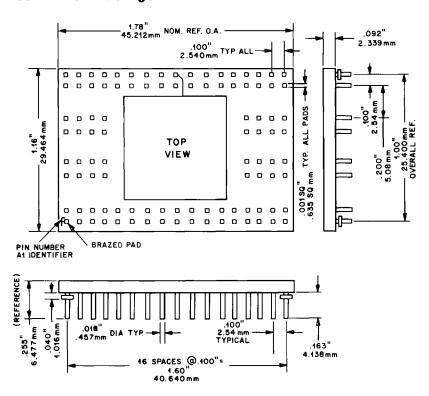

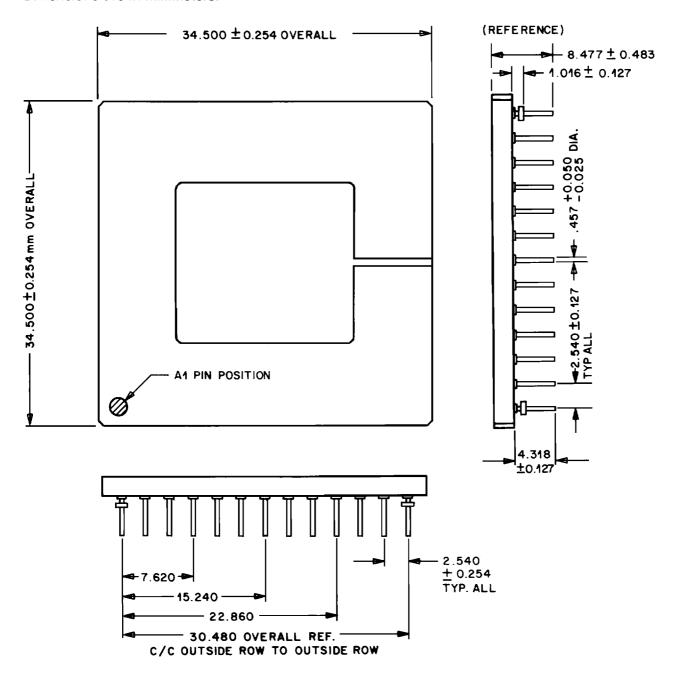

The WE DSP32 Digital Signal Processor integrated circuit is a 32-bit high-speed programmable digital signal processor. The device is available in two versions, at 16 MHz or 25 MHz. Both 16-MHz and 25-MHz parts are available in three packages: a standard 40-pin DIP, a 100-pin rectangular pin-grid-array (PGA) package, and a 13- x 13-pin square PGA package. High throughput is achieved by using two execution units, the control arithmetic unit (CAU) and the data arithmetic unit (DAU). The CAU is a 16-bit fixed-point unit for logic and control, and the DAU is a 32-bit floating-point unit for signal processing algorithms. The CAU includes twenty-one 16bit general-purpose registers and can execute 6.25 million instructions per second at 25 MHz. The DAU contains a floating-point multiplier

Photo is not actual size.

and adder, and four 40-bit accumulators. The DAU is configured for multiply/accumulate and can perform 12.5 million floating-point computations per second at 25 MHz. The on-chip memory includes 2048 bytes of ROM and 4096 bytes of RAM. Memory can be addressed as 8-, 16-, or 32-bit words and is organized to access 32-bit data at the same speed as 8-bit data. With the PGA packages, memory can be expanded off-chip with 56 Kbytes of directly accessible data. The device has three I/O ports: a serial port, a parallel port to interface with a microprocessor, and an external memory interface (PGA packages only) for memory-mapped I/O.

#### **Features**

- 16-MHz and 25-MHz parts are available

- 2048 bytes ROM, 4096 bytes RAM (on-chip)

- Memory can be addressed as 8, 16, or 32 bits

- Four 40-bit accumulators

- Off-chip memory expansion of up to 56 Kbytes (PGA packages only)

- Four memory accesses per instruction cycle

- 32-bit floating-point arithmetic

- 16-bit integer operations

- Interfaces to a microprocessor without any additional devices

- Serial and parallel I/O ports with DMA options

- Error control logic

- Single 5 V power supply required

- Supported by WE DSP32-CC C Language Compiler, WE DSP32-SL Support Software Library, WE DSP32-AL Application Software Library and WE DSP32-DS Digital Signal Processor Development System

### WE DSP32 Digital Signal Processor

| Description           | 1 | Pin Descriptions                            | 24 |

|-----------------------|---|---------------------------------------------|----|

| Features              |   | Characteristics                             | 42 |

| User Information      | 2 | Electrical Characteristics and Requirements | 42 |

| Architectural Summary | 2 | Timing Characteristics and Requirements     | 46 |

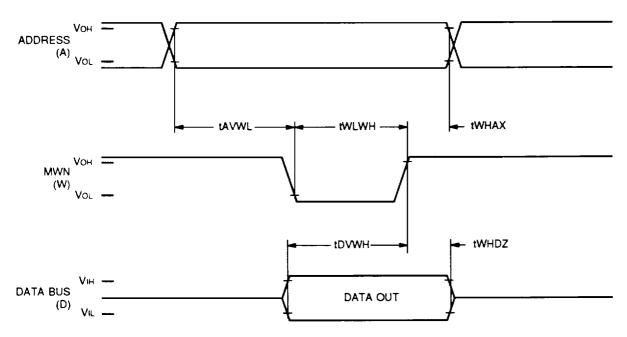

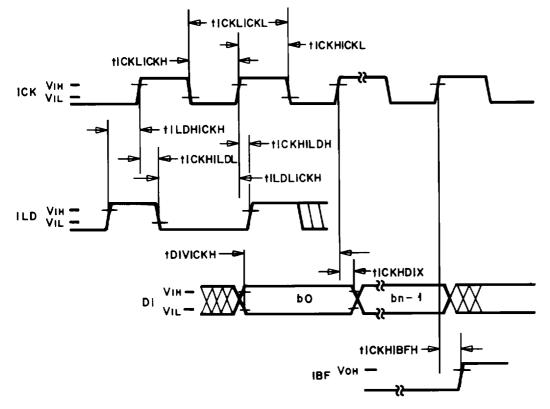

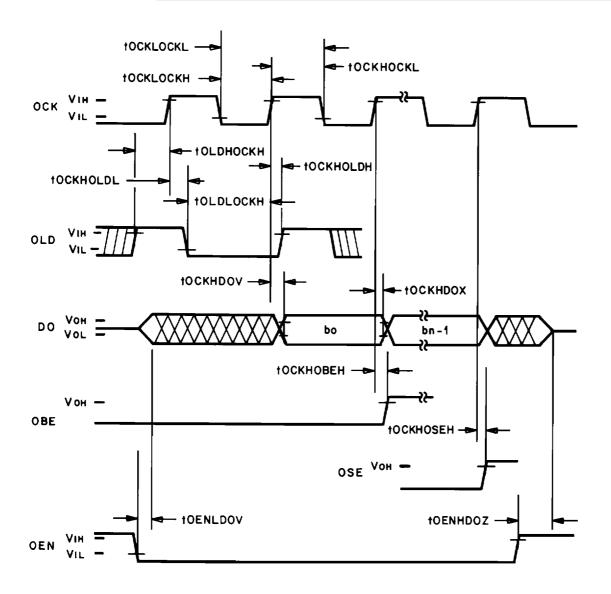

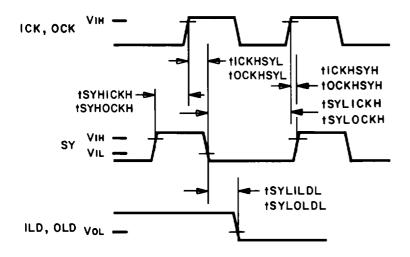

| Memory Addressing     | 4 | Timing Diagrams                             | 53 |

|                       |   | Outlines                                    | 61 |

| Instruction Set       |   |                                             |    |

## **User Information**

## **Architectural Summary**

The control arithmetic unit (CAU) is used to generate memory addresses and to execute 15-bit integer operations (see Figure 1). The CAU can execute 6.25 million instructions per second and has twenty-one 16-bit registers, a 16-bit program counter (PC), and an arithmetic logic unit (ALU). All CAU registers are static and do not require refreshing. When addressing 32-bit floating-point operands, registers r1—r14 are used as memory pointers (rP), and r15—r19 are used as increment registers (rl). Register r20, also called PIN (parallel input register), is used as the serial input/output (SIO) DMA input pointer. Register r21, also called POUT (parallel output register), is used as the SIO DMA output pointer. All registers can be general-purpose in the execution of the 16-bit integer operations.

The data arithmetic unit (DAU) is configured for multiply/accumulate operations and is the primary execution unit for signal processing algorithms. The DAU contains a floating-point multiplier and adder and four 40-bit accumulators (a0—a3). The DAU can perform 6.25 million instructions per second of the form a = b + c \* d. The DAU multiplier inputs are 32-bit floating-point numbers; each number is made up of a 24-bit mantissa and an 8-bit exponent. The adder inputs from memory or an accumulator are 32 or 40 bits. The 40-bit input comes from either an accumulator (a0—a3) or the multiplier (32 bits, plus 8 guard bits). The DAU performs floating-point to-and-from 16-bit integer and floating-point to-and-from  $\mu$ -law and A-law data type conversions.

The DSP32 device has on-chip memory – 2048 bytes of mask-programmable ROM and 4096 bytes of RAM. Data can be 8-, 16-, or 32-bits wide and memory is uniformly byte-addressable (see the Memory Addressing section). The RAM is dynamic and is refreshed either automatically or under program control. The ROM can be mask-programmed with application program(s) or constant data. Instructions can also be located in on-chip RAM or external memory. With the PGA packages, memory can be expanded off-chip by using standard byte-wide memory devices without any additional interfacing devices. The DSP32 device can directly address 14K instructions (32-bit words) when using off-chip memory.

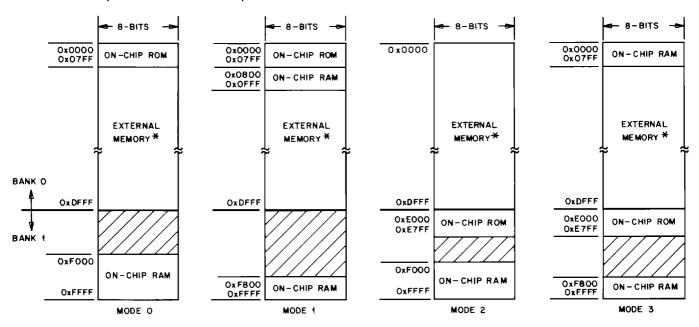

The DSP32 memory is divided into two banks — a lower bank (0) and an upper bank (1). Memory access can be made without regard to the upper and lower banks. However, to achieve maximum throughput, memory access must alternate between the two memory banks. As one memory bank is accessed, the other memory bank is addressed. This form of pipelining can reduce the effective memory access time by one-half. Only the lower memory bank address space is expandable off-chip. Therefore, the external address and data buses need to operate at only half the rate of the on-chip buses. Pins MMD0 and MMD1 allow the user to select the location of internal ROM and RAM in the memory address space.

Note: See Tables 21—27 for signal name definitions.

<sup>\*</sup> Not available on the 40-pin DIP.

| Legend: |                         |      |                           |        |                          |

|---------|-------------------------|------|---------------------------|--------|--------------------------|

| a0a3    | Accumulators 0—3        | FPM  | Floating-Point Multiplier | PCR    | PIO Control Register     |

| ALU     | Arithmetic Logic Unit   | IBUF | Input Buffer              | PDR    | PIO Data Register        |

| CAU     | Control Arithmetic Unit | IOC  | Input/Output Control      | PIO    | Parallel I/O Unit        |

| DAU     | Data Arithmetic Unit    |      | Register                  | PIR    | PIO Interrupt Register   |

| DAUC    | Data Arithmetic Unit    | ISR  | Input Shift Register      | r1—r19 | Registers 1—19           |

|         | Control Register        | OBUF | Output Buffer             | PIN    | Parallel Input Register  |

| EMR     | Error Mask Register     | OSR  | Output Shift Register     | POUT   | Parallel Output Register |

| ESR     | Error Source Register   | PAR  | PIO Address Register      | RAM    | Read/Write Memory        |

| FPA     | Floating-Point Adder    | PC   | Program Counter           | ROM    | Read-Only Memory         |

|         | _                       |      | -                         | SIO    | Serial I/O Unit          |

Figure 1. Block Diagram

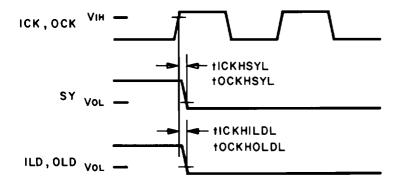

The serial I/O (SIO) unit is used for serial-to-parallel conversion of input data and parallel-to-serial conversion of output data. Input to the SIO is loaded into the input shift register (ISR) and then into the input buffer (IBUF). Outputs from the SIO are loaded into the output buffer (OBUF) and then into the output shift register (OSR). This double buffering is done so that back-to-back transfers are possible, which allows the DSP32 program to begin a second transfer before the first has been completed. Data widths can be 8, 16, or 32 bits. The input/output control (IOC) register in the SIO is used to select various I/O conditions, bit lengths, internal or external clock, and internal or external sync (see Table 2).

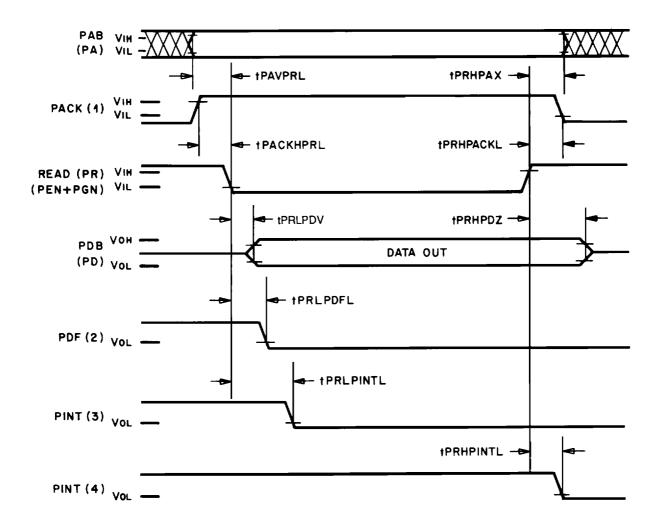

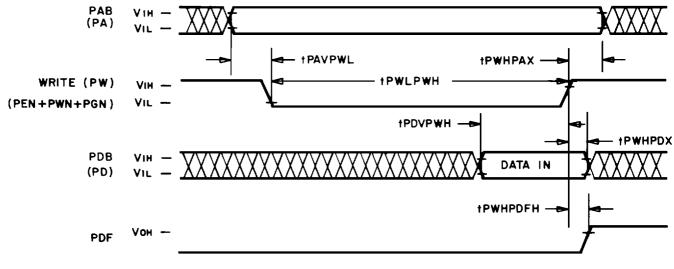

The parallel I/O (PIO) unit is used for bidirectional communication between the DSP32 device and an external microprocessor. The external PIO data bus is 8-bits wide, and transfers can be made under program or DMA control. The PIO DMA allows a microprocessor to download a program without interrupting the execution of a DSP32 program in progress. The PIO has three 16-bit registers (PAR, PDR, and PIR), a 10-bit register (EMR), an 8-bit register (PCR), and a 6-bit register (ESR). These registers are used to control PIO transfers and to check for errors.

## **Memory Addressing**

A 32-bit memory location can be addressed as one 32-bit floating-point word, two 16-bit integer words, or four 8-bit byte words. A 32-bit memory address is always divisible by four; a 16-bit memory address is divisible by two.

| 32-Bit Memory Locations    |                               |      |      |                   |  |  |  |  |  |

|----------------------------|-------------------------------|------|------|-------------------|--|--|--|--|--|

| 32-Bit Floating-Point Word |                               |      |      |                   |  |  |  |  |  |

| 16-Bit                     | 16-Bit Integer 16-Bit Integer |      |      |                   |  |  |  |  |  |

| Byte                       | Byte                          | Byte | Byte | Memory<br>Address |  |  |  |  |  |

| 3                          | 2                             | 1    | 0    | 0                 |  |  |  |  |  |

| 7                          | 6                             | 5    | 4    | 4                 |  |  |  |  |  |

| 11                         | 11 10 9 8 8                   |      |      |                   |  |  |  |  |  |

|                            | etc.                          |      |      |                   |  |  |  |  |  |

| Data Type Memory Select |      |      |      |      |  |  |  |  |  |  |  |

|-------------------------|------|------|------|------|--|--|--|--|--|--|--|

| Data Type               | MSN3 | MSN2 | MSN1 | MSN0 |  |  |  |  |  |  |  |

| Byte 0                  | 1    | 1    | 1    | 0    |  |  |  |  |  |  |  |

| Byte 1                  | 1    | 1    | 0    | 1    |  |  |  |  |  |  |  |

| Byte 2                  | 1    | 0    | 1    | 1    |  |  |  |  |  |  |  |

| Byte 3                  | 0    | 1    | 1    | 1    |  |  |  |  |  |  |  |

| Low integer             | 1    | 1    | 0    | 0    |  |  |  |  |  |  |  |

| High integer            | 0    | 0    | 1    | 1    |  |  |  |  |  |  |  |

| Float                   | 0    | 0    | 0    | 0    |  |  |  |  |  |  |  |

Each 32-bit word is organized as four bytes, e.g., 3, 2, 1, 0, where byte 3 is the MSByte (most significant byte) and byte 0 is the LSByte (least significant byte). A 16-bit word is 2 bytes, either 1, 0 with byte 1 the MSByte and byte 0 the LSByte, or 3, 2 with byte 3 the MSByte and byte 2 the LSByte. Memory address 0 can refer to an 8-bit word (byte 0), a 16-bit word (1, 0), or a 32-bit word (3, 2, 1, 0).

Memory addresses 00000—57343 (0x0000—0xDFFF)\* are in bank 0; memory addresses 57344—65535 (0xE000—0xFFF) are in bank 1. MMD0 and MMD1 are used to select the memory configuration, i.e., the location of the internal RAM and ROM within the address space. Table 1 and Figure 2 show how the memory is configured in the four different memory modes. In all four configurations, the first instruction executed after reset is at address 00000 (0x0000).

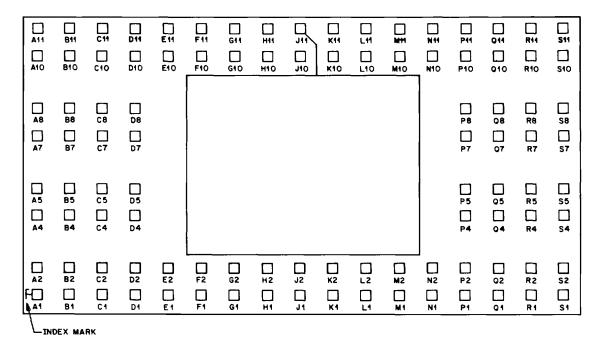

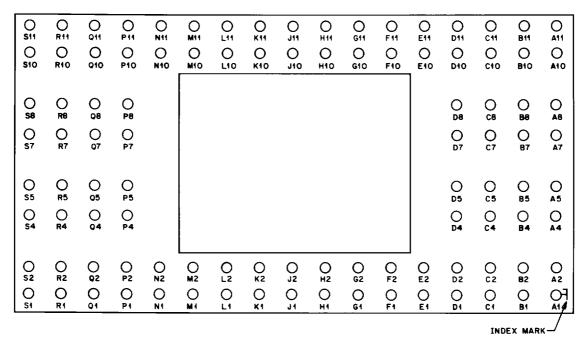

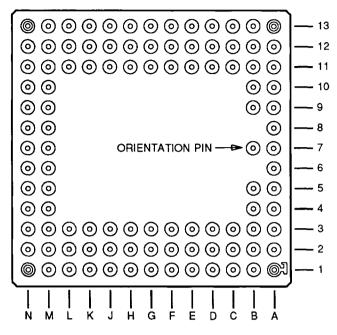

#### Pin-Grid-Array (PGA) Packages

The 14-bit address bus selects a 32-bit word. MSN0—MSN3 (active low) are derived internally according to the data type implied in the instruction and are used to select bytes within that 32-bit word. The two least significant bits of the register pointer (pc, r1—r21) or the direct address determine the values of the memory select lines (MSN0—MSN3). With 56 Kbytes of external memory attached, direct referencing can be made to 65536 bytes, 32768 integers, or 16384 floats. With no external memory, 6144 bytes, 3072 integers, or 1536 floats can be referenced.

<sup>\*</sup> The prefix "0x" indicates hexadecimal notation.

### 40-Pin Dual In-Line Package (DIP)

On the 40-pin package, the external memory interface (EMI) is not available, limiting total memory to the 512 32-bit words of ROM and 1024 32-bit words of RAM provided on-chip, which can store 4096 bytes, 2048 integers, or 1024 floats.

**Table 1. Memory Configuration Selection**

| Mode | MMD1 | MMD0 | Addresses                                                        | Assignments                                          |

|------|------|------|------------------------------------------------------------------|------------------------------------------------------|

| 0    | 0    | 0    | 0x0000—0x07FF<br>0x0800—0xDFFF<br>0xF000—0xFFFF                  | On-chip ROM<br>External memory*<br>On-chip RAM       |

| 1    | 0    | 1    | 0x0000—0x07FF<br>0x0800—0x0FFF<br>0x1000—0xDFFF<br>0xF800—0xFFFF | On-chip ROM On-chip RAM External memory* On-chip RAM |

| 2    | 1    | 0    | 0x0000—0xDFFF<br>0xE000—0xE7FF<br>0xF000—0xFFFF                  | External memory*<br>On-chip ROM<br>On-chip RAM       |

| 3    | 1    | 1    | 0x0000—0x07FF<br>0x0800—0xDFFF<br>0xE000—0xE7FF<br>0xF800—0xFFFF | On-chip RAM External memory* On-chip ROM On-chip RAM |

<sup>\*</sup> External memory not available on the 40-pin DIP.

<sup>\*</sup> External memory not available on the 40-pin DIP.

Figure 2. Memory Address Configurations

## **Register Operation**

The following tables show the register settings for various operating conditions of the WE DSP32 Digital Signal Processor.

## IOC and DAUC Registers

Tables 2 and 3 show the operating conditions that result after setting the IOC and DAUC registers.

Table 2. IOC Register

|       |       |                                                 |         |                                                                                                                                                                                 | _                      |                    |                     |              |         |           |        |         |         |

|-------|-------|-------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------|---------------------|--------------|---------|-----------|--------|---------|---------|

|       | Bit   | 1513                                            | 12      | 11,10                                                                                                                                                                           | 9                      | 8                  | 7,6                 | 5            | 4       | 3,2       | 1      | 0       |         |

|       | Field | d DMA SAN OLEN AOL AOC ILEN AIL AIC SLEN BC ASY |         |                                                                                                                                                                                 |                        |                    |                     |              |         |           | ]      |         |         |

|       |       |                                                 |         |                                                                                                                                                                                 |                        |                    |                     |              |         |           |        | _       |         |

| Bit   | Mne   | monic                                           |         | -                                                                                                                                                                               |                        |                    | F                   | unctio       | n       |           |        |         |         |

| 0     | A     | SY                                              |         | red (0),<br>ally, SY                                                                                                                                                            |                        |                    |                     |              |         |           |        |         |         |

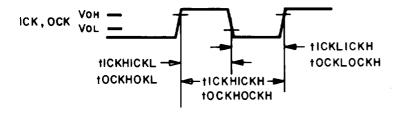

| 1     | В     | c                                               |         | red, ICK<br>s used t                                                                                                                                                            |                        |                    |                     |              | •       |           |        | locks;  | if set, |

| 3,2   | S     | LEN                                             | chip S  | bits sel<br>SY clock<br>00 – xx<br>01 – rati<br>10 – rati<br>11 – rati                                                                                                          | :<br> o = 8<br> o = 16 | •                  | ency ra             | tio of       | the or  | n-chip lo | oad c  | lock to | the on- |

| 4     | Α     | IC                                              | If clea | red, the<br>al.                                                                                                                                                                 | clock                  | ICK is             | externa             | ıl; if s     | et, the | clock l   | CK =   | CKI/8   | and is  |

| 5     | A     | <b>I</b> L                                      |         | red, clo<br>C]/(32) a                                                                                                                                                           |                        |                    |                     | set, c       | lock II | _D = {IC  | K, 00  | CK}/(32 | 2) =    |

| 7,6   | l IL  | .EN                                             | (       | bits sp<br>00 – xx<br>01 – ser<br>10 – ser<br>11 – ser                                                                                                                          | ial inp<br>ial inp     | ut leng<br>ut leng | th = 8 t<br>th = 16 | oits<br>bits | ut seri | al data:  |        |         |         |

| 8     | А     | oc                                              | If clea | red, OC                                                                                                                                                                         | K is ex                | kternal;           | if set,             | OCK -        | = CKI/  | 8 and is  | s inte | rnal.   |         |

| 9     | А     | OL                                              |         | red, OL<br>s interna                                                                                                                                                            |                        | ternal;            | if set,             | OLD =        | {ICK,   | OCK}/(    | 32) =  | IOC[B0  | C]/(32) |

| 11,10 |       | PLEN                                            | (<br>(  | These bits specify the length of the serial output data:  00 - xx  01 - serial output length = 8 bits  10 - serial output length = 16 bits  11 - serial output length = 32 bits |                        |                    |                     |              |         |           |        |         |         |

| 12    | S     | AN                                              | If clea | red, cle                                                                                                                                                                        | ar san                 | ity; if s          | et, set s           | sanity       | •       |           |        |         |         |

Table 2. IOC Register (Continued)

| Bit   | Mnemonic | Function                                                      |

|-------|----------|---------------------------------------------------------------|

| 15—13 | DMA[2-0] | These bits control DMA mode:                                  |

|       |          | 000 – no DMA                                                  |

|       |          | 001 – input DMA when IBF is high                              |

|       |          | 010 – output DMA when OBE is high                             |

|       |          | 011 – input DMA when IBF is high, output DMA when OBE is high |

|       |          | 100 – input and output DMA when both IBF and OBE are high     |

|       |          | 101 – input and output DMA when IBF is high                   |

|       |          | 110 – input and output DMA when OBE is high                   |

|       |          | 111 – input and output DMA when either IBF or OBE is high     |

Table 3. DAUC Register Settings

| DAUC* | Result                        |

|-------|-------------------------------|

| xx0   | μ-Law input conversion        |

| xx1   | A-law input conversion        |

| x0x   | μ-Law output conversion       |

| x1x   | A-law output conversion       |

| 0xx   | No parity check on X operands |

| 1xx   | Parity check on X operands    |

<sup>\*</sup> x = don't care.

#### **PIO Control**

The PIO has a processor address bus (PAB0—PAB2) to select the various PIO registers. Table 4 shows the register selection.

**Table 4. Register Selection**

| PAB2—PAB0 | Register Selected                            |

|-----------|----------------------------------------------|

| 000       | PAR(I) – lower byte                          |

| 001       | PAR(h) – upper byte                          |

| 010       | PDR(I) – lower byte                          |

| 011       | PDR(h) – upper byte                          |

| 100       | EMR(I) – lower byte; most significant 5 bits |

| 101       | EMR(h) – upper byte; most significant 5 bits |

| 110       | ESR – most significant 6 bits                |

| 111       | PCR                                          |

Tables 5 and 6 describe PCR and ESR, two of the PIO registers.

The PIO control register (PCR) is an 8-bit register used by an external microprocessor ( $\mu$ P) to set up various controlled transfer modes between the DSP32 device and the microprocessor.

Table 5. PCR Register

|     |          |        |                                                                                                           |       |        |                      |          |         |               |                                         | -               |

|-----|----------|--------|-----------------------------------------------------------------------------------------------------------|-------|--------|----------------------|----------|---------|---------------|-----------------------------------------|-----------------|

|     |          | Bit    | 7                                                                                                         | 6     | 5      | 4                    | 3        | 2       | 1             | 0                                       |                 |

|     |          | Field  | REF                                                                                                       | PIF   | PDF    | AUTO                 | DMA      | ENI     | Intmode       | Reset                                   |                 |

|     | T        | ,      |                                                                                                           |       |        |                      |          |         |               |                                         |                 |

| Bit | Mnemonic |        |                                                                                                           |       |        |                      | Fu       | nctio   | 1             |                                         |                 |

| 0   | Reset    |        | •                                                                                                         |       |        | 2 device<br>et seque |          | runs    | DSP32 dev     | vice. Ze                                | ro-to-one       |

| 1   | Intmode  | +      |                                                                                                           |       |        | •                    |          | if set. | 16-bit PIR    | interrup                                | t vector.       |

| 2   | ENI      | -      |                                                                                                           |       |        | •                    |          |         | -             |                                         | PINT due to PIR |

|     | 2.41     | 1      | rrupt.                                                                                                    | disai |        | 111 000              |          |         | pt, 11 00t, c | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |                 |

| 3   | DMA      | If cl  | eared,                                                                                                    | DMA   | disab  | led on P             | lO; if s | et, DM  | IA enabled    | on PIO.                                 |                 |

| 4   | AUTO     | If clo |                                                                                                           | PAR   | not au | ıtoincrer            | nented   | on DI   | MA; if set,   | PAR auto                                | oincremented on |

| 5   | PDF      | 1      | Set when PDR is written to by DSP32 or $\mu$ P; cleared when PDR is read by DSP32 or $\mu$ P (read only). |       |        |                      |          |         |               |                                         |                 |

| 6   | PIF      |        | Set when PIR is written to by DSP32 device; cleared when PIR is read by $\mu P$ (read only).              |       |        |                      |          |         |               |                                         |                 |

| 7   | REF      | If cl  | If cleared, enables RAM autorefresh; if set, disables RAM autorefresh.                                    |       |        |                      |          |         |               |                                         |                 |

The error source register (ESR) has 6 bits that can be read only by the external microprocessor. It is cleared after a read. This register is used to store error conditions (bits 3—7) in the DSP32 device.

Table 6. ESR Register

|     | Bit   | 7    | 6        | 5                                                                                                                                                                | 4       | 3     | 2         | 1           | 0       |        |

|-----|-------|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|-----------|-------------|---------|--------|

|     | Field | LOS' | Y LOS    | ADER                                                                                                                                                             | OVE     | PE    | WPIR      | Not Use     | ed      |        |

|     |       |      |          |                                                                                                                                                                  |         |       |           |             |         |        |

| Bit | Mnemo | onic |          |                                                                                                                                                                  |         | Name  | e/Descr   | iption      |         |        |

| 0   |       |      | Not use  | ed.                                                                                                                                                              |         |       |           |             |         |        |

| 1   | _     |      | Not use  | ed.                                                                                                                                                              |         |       |           |             |         |        |

| 2   | WPIF  | ٦    | PIR Wri  | i <b>te.</b> Set                                                                                                                                                 | when    | DSP3  | 2 devic   | e writes to | PIR.    |        |

| 3   | PE    |      | Parity E | Error. If                                                                                                                                                        | set, in | struc | tion me   | mory parity | y error |        |

| 4   | OVE   |      | Overflo  | w/Unde                                                                                                                                                           | rflow   | Error | . If set, | DAU overf   | low or  | underf |

| 5   | ADE   | R    | float va | Addressing Error. If set, an attempt was made to access a float variable or an integer variable with an address that was not a multiple of 4 or 2, respectively. |         |       |           |             |         |        |

| 6   | LOS   |      |          | Loss of Sanity. If set, sanity bit in the IOC register is set and SY changes state from high to low.                                                             |         |       |           |             |         |        |

| 7   | LOS   | Υ    | Loss of  | Loss of Sync. If set, loss of 8 kHz external sync.                                                                                                               |         |       |           |             |         |        |

#### **Instruction Set**

The DSP32 device has a powerful instruction set for signal processing algorithms, called data arithmetic (DA) instructions. It also supports instructions for logic and control arithmetic (CA) instructions.

DA instructions, which execute in the DAU, perform 32-bit floating-point multiply/accumulate operations for signal processing algorithms. DA instructions also include special functions for such data-type conversions as floating-point to-and-from integer and floating-point to-and-from  $\mu$ -law and A-law.

CA instructions, which execute in the CAU, are 16-bit integer microprocessor operations that include arithmetic and logic instructions and such control statements as conditional goto and call. CA instructions also include data move statements so that data can be moved between memory, I/O registers, and any of the CAU registers.

#### **Flags**

The DSP32 has internal flags that are affected by the results of certain DA, CA, or I/O instructions. These flags, although not directly visible to the user, can be tested by conditional instructions. Table 7 lists the flags, the names used in instructions (see the test column), and the meaning of each flag.

Note: DAU flags are represented with upper case letters, while CAU flags are represented with lower-case letters.

Table 7. DSP32 Flags

|      | DAU Flags           |                                  |                     |                        |  |  |  |  |  |  |  |

|------|---------------------|----------------------------------|---------------------|------------------------|--|--|--|--|--|--|--|

| Flag | Test<br>(State = 1) | Meaning                          | Test<br>(State = 0) | Meaning                |  |  |  |  |  |  |  |

| N    | alt                 | Result is negative               | age                 | Result not negative    |  |  |  |  |  |  |  |

| Z    | aeq                 | Result is zero                   | ane                 | Result not zero        |  |  |  |  |  |  |  |

| ٧    | avs                 | Result overflowed                | avc                 | No overflow            |  |  |  |  |  |  |  |

| U    | aus                 | Result underflowed               | auc                 | No underflow           |  |  |  |  |  |  |  |

|      |                     | CAU Flags                        |                     |                        |  |  |  |  |  |  |  |

| n    | mi                  | Result is negative               | pl                  | Result not negative    |  |  |  |  |  |  |  |

| Z    | eq                  | Result is zero                   | ne                  | Result not zero        |  |  |  |  |  |  |  |

| V    | vs                  | Result overflowed                | vc                  | No overflow            |  |  |  |  |  |  |  |

| С    | cs                  | Carry or borrow out of MSB       | СС                  | No carry or borrow     |  |  |  |  |  |  |  |

|      |                     | I/O Flags                        |                     |                        |  |  |  |  |  |  |  |

| i    | ibf                 | Input buffer full                | ibe                 | Input buffer empty     |  |  |  |  |  |  |  |

| 0    | obf                 | Output buffer full               | obe                 | Output buffer empty    |  |  |  |  |  |  |  |

| р    | pdf                 | Parallel data register full      | pde                 | PDR empty              |  |  |  |  |  |  |  |

| Р    | pif                 | Parallel interrupt register full | pie                 | PIR empty              |  |  |  |  |  |  |  |

| S    | sys                 | SY (I/O sync pulse) set          | syc                 | SY cleared             |  |  |  |  |  |  |  |

| b    | fbs                 | Serial I/O frame boundary        | fbc                 | Not SIO frame boundary |  |  |  |  |  |  |  |

For example, for testing the U flag (state is 1) there is an instruction:

if(aus) goto address

Flags shown at the end of an instruction indicate which flags are affected by the result of that instruction.

A zero (0) shown in place of a flag means that the flag is always 0; a dash (-) in place of a flag means that the flag is unaffected by the instruction.

#### Instructions

The following is the complete DSP32 instruction set, grouped as DA and CA instructions. Where braces, {}, are shown in an instruction, one of the enclosed items must be chosen. Items enclosed in brackets [] are optional.

Note: {} and [] are not part of the instruction syntax. Parentheses, (), are part of the syntax and must appear where shown in an instruction. Lower-case letters are part of the syntax. Upper-case letters are replaced by immediate data or by a register name (see tables following each instruction group).

#### Data Arithmetic (DA) Instructions

The DA instructions are divided into two functional groups: multiply/accumulate and special functions.

Table 8. DA Multiply/Accumulate Instructions

| Instruction                | DAU Flags<br>Affected | Description                                                                                                                                                                                 |

|----------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [Z=] aN = [-]aM {+,-} Y* X | NZVU                  | The product of the X and Y fields is added/subtracted to/from the accumulator (aM) and the result is stored in an accumulator (aN). The result can also be output according to the Z field. |

| aN = [-]aM {+,-} (Z=Y)* X  | NZVU                  | The Y field operand is output according to the Z field. The product of the X and Y fields is added to the accumulator (aM) and the sum is stored in an accumulator (aN).                    |

| [Z=] aN = [-]Y {+,-} aM* X | NZVU                  | The product of the X field and the accumulator (aM) is added/subtracted to/from the Y field. The result is placed in an accumulator (aM) and can also be output according to the Z field.   |

| [Z=] aN = [_]Y* X          | NZVU                  | The product of the X and Y fields is added/subtracted to/from zero. The result is stored in aN and can also be output according to the Z field.                                             |

| aN = [-](Z=Y)* X           | NZVU                  | The value of the Y field is output according to the Z field. The product of the Y and X fields is stored in an accumulator (aN).                                                            |

| [Z=] aN = [-]Y {+,-}X      | NZVU                  | The sum or difference of the Y and X fields is stored in an accumulator (aN) and the result output according to the Z field. <b>Note:</b> X is a multiplier input.                          |

| [Z=] aN = [_]Y             | NZVU                  | The value of the Y field is placed in accumulator (aN) and also output according to the Z field.                                                                                            |

Table 9. Replacement Table for DA Multiply/Accumulate Instructions

| Replace      | Value                       | Meaning                                                                                                        |

|--------------|-----------------------------|----------------------------------------------------------------------------------------------------------------|

| aN, aM, X, Y | a0—a3                       | One of four DAU accumulators                                                                                   |

| X,Y,Z        | *rP, *rP++,<br>*rP, *rP++rl | 32-bit memory location where rP is a memory pointer (P = 1 - 14) and rI is an increment register (1 = 15 - 19) |

| X, Y         | ibuf                        | SIO input buffer                                                                                               |

| Z            | obuf                        | SIO output buffer                                                                                              |

Table 10. DA Special Functions

| Instruction        | DAU Flags Affected | Description                               |  |  |

|--------------------|--------------------|-------------------------------------------|--|--|

| [Z=] aN = ic(Y)    | NZ00               | Input conversation: μ-law/A-law to float  |  |  |

| [Z=] aN = oc(Y)    |                    | Output conversation: float to μ-law/A-law |  |  |

| [Z=] aN = float(Y) | NZ00               | Conversion: integer to float              |  |  |

| [Z=] aN = int(Y)   | _                  | Conversion: float to integer              |  |  |

| [Z=] aN = round(Y) | NZVU               | Conversion: float(40) to float(32)        |  |  |

| [Z=] aN = ifalt(Y) | _                  | If(alt) then [Z=] aN=Y else [Z=] aN       |  |  |

Table 11. Replacement Table for DA Special Function Instructions

| Replace | Value                       | Meaning                                                                                                 |

|---------|-----------------------------|---------------------------------------------------------------------------------------------------------|

| aN, Y   | a0—a3                       | One of four DAU accumulators                                                                            |

| Y,Z     | *rP, *rP++,<br>*rP, *rP++rl | Memory location where rP is a memory pointer (P = 1 - 14) and r1 is an increment register (1 = 15 - 19) |

| Y,Z     | pdr                         | PIO data register                                                                                       |

| Υ       | ibuf                        | SIO input buffer                                                                                        |

| Z       | obuf                        | SIO output buffer                                                                                       |

## **Control Arithmetic (CA) Instructions**

The CA instructions are divided into three functional groups: control, arithmetic/logic, and data move.

**Table 12. CA Control Group Instructions**

| Instruction                                 | Flags Affected          | Description            |  |

|---------------------------------------------|-------------------------|------------------------|--|

| if (CA COND) goto {rH, N, rH+N, rH-N}       |                         | Conditional branch     |  |

| if $(rM >= 0)$ goto $\{rH, N, rH+N, rH-N\}$ |                         | Conditional branch     |  |

| if (DA COND) goto {rH, N, rH+N, rH-N}       |                         | Conditional branch     |  |

| if (IO COND) goto {rH, N, rH+N, rH-N}       | None Conditional branch |                        |  |

| call {rH, N, rH+N, rH-N} (rM)               |                         | Call subroutine        |  |

| return (rM)                                 |                         | Return from subroutine |  |

| goto {rH, N, rH+N, rH-N}                    |                         | Unconditional branch   |  |

| [L]*nop                                     |                         | No operation           |  |

Table 13. Replacement Table for CA Control Group Instructions, CA Conditions (CA COND)

| Value | CAU Flags*  | Meaning                        |

|-------|-------------|--------------------------------|

| pl    | n=0         | Result is nonnegative (plus)   |

| mi    | n=1         | Result is negative (minus)     |

| ne    | z=0         | Result not equal to zero       |

| eq    | z=1         | Result equal to zero           |

| vc    | v=0         | Overflow cleared, no overflow  |

| vs    | v=1         | Overflow set, overflowed       |

| СС    | c=0         | Carry cleared, no carry        |

| cs    | c=1         | Carry set, carry               |

| ge    | n^v=0       | Greater than or equal to       |

| lt    | n^v=1       | Less than                      |

| gt    | z   (n^v)=0 | Greater than                   |

| le    | z   (n^v)=1 | Less than or equal to          |

| hi    | c   z=0     | Greater than (unsigned number) |

| Is    | c   z=1     | Less than (unsigned number)    |

<sup>\*</sup> Symbol interpretation: ^ = XOR; | = OR.

Table 14. Replacement Table for CA Control Group Instructions, DA Conditions (DA COND)

| Value | DAU Flags | Meaning                         |

|-------|-----------|---------------------------------|

| ane   | Z=0       | Not equal to zero               |

| aeq   | Z=1       | Equal to zero                   |

| age   | N=0       | Greater than or equal to zero   |

| alt   | N=1       | Less than zero                  |

| avc   | V=0       | Overflow cleared, no overflow   |

| avs   | V=1       | Overflow set, overflowed        |

| auc   | U=0       | Underflow cleared, no underflow |

| aus   | U=1       | Underflow set, underflowed      |

| agt   | N   Z=0   | Greater than zero               |

| ale   | N   Z=1   | Less than or equal to zero      |

Table 15. Replacement Table for CA Control Group Instructions, I/O Conditions (IO COND)

| Mnemonic   | Condition      | Meaning                                                            |

|------------|----------------|--------------------------------------------------------------------|

| ibe<br>ibf | ibf=0<br>ibf=1 | Input buffer empty Input buffer full                               |

| obe<br>obf | obe=1<br>obe=0 | Output buffer empty Output buffer full                             |

| pde<br>pdf | pdf=0<br>pdf=1 | Parallel data register empty Parallel data register full           |

| pie<br>pif | pif=0<br>pif=1 | Parallel interrupt register empty Parallel interrupt register full |

| syc<br>sys | sy=0<br>sy=1   | Sync signal low<br>Sync signal high                                |

| fbc<br>fbs | fb=0<br>fb=1   | Serial frame boundary clear<br>Serial frame boundary set           |

Table 16. CA Arithmetic/Logic Group Instructions

| Instruction           | CAU Flags Affected | Description            |

|-----------------------|--------------------|------------------------|

| rD = rH+N             | nzvc               | Three operand add      |

| rD = rD+rS            | nzvc               | Add                    |

| rD = rD-rS            | nzvc               | Right subtract         |

| rD-{N,rS}             | nzvc               | Compare                |

| $rD = \{N, rS\}-rD$   | nzvc               | Left subtract          |

| $rD = rD&\{N, rS\}$   | nz00               | AND                    |

| rD&{N, rS}            | nz00               | Bit test               |

| $rD = rD   \{N, rS\}$ | nz00               | OR                     |

| $rD = rD^{N}, rS$     | nz00               | XOR                    |

| rD = rS/2             | nz0c               | Arithmetic right shift |

| rD = rS>>1            | 0z0c               | Logical right shift    |

| rD = -rS              | nzvc               | Negate                 |

| rD = rS*2             | nzvc               | Arithmetic left shift  |

**Table 17. CA Data Move Group Instructions**

| Instruction                       | CAU Flags Affected | Description                   |  |  |

|-----------------------------------|--------------------|-------------------------------|--|--|

| rD = N                            | nz00               |                               |  |  |

| {ioc, dauc} = VALUE               | _                  | <del>_</del>                  |  |  |

| $\{MEM,*N, obuf\} = \{rSh, rSl\}$ |                    | MEM, *N, and obuf are 8 bits  |  |  |

| {MEM,*N, obuf, pdr, pir} = rS     | _                  | MEM, *N, and obuf are 16 bits |  |  |

| $rD = \{MEM,*N, ibuf, pdr\}$      | nz00               | MEM, *N, and ibuf are 16 bits |  |  |

| $\{rDh, rDl\} = \{MEM,*N, ibuf\}$ | nz00               | MEM, *N, and ibuf are 8 bits  |  |  |

Table 18. Replacement Table for All CA Instructions

| Replace  | Value                                      | Meaning                                                                                                 |

|----------|--------------------------------------------|---------------------------------------------------------------------------------------------------------|

| rH       | pc, r1—r21                                 | One of 21 general-purpose CAU registers, or the program counter                                         |

| rM,rS,rD | r1—r21                                     | One of 21 CAU registers                                                                                 |

| rDh rSh  | r1—r21                                     | High-order bits (8—15) are moved; low-order bits (0—7) are cleared for rDh and remain unchanged for rSh |

| rDI, rSI | r1—r21                                     | Low-order bits (0—7) are moved; high-order bits are cleared for rDI and remain unchanged for rSI        |

| MEM      | *rP, *rP++,<br>*rP, *rP++rl<br>(P,l = 121) | 16-bit or 8-bit memory location                                                                         |

| L        | Positive Integer                           | _                                                                                                       |

| N        | 16-bit integer                             | _                                                                                                       |

| VALUE    | 16-bit integer or 3-bit integer            | VALUE is a 16-bit number for the ioc word or a 3-bit number for dauc word                               |

## **Summary of Instructions**

Tables 19 and 20 list DA and CA instructions, along with the encoding format numbers and the flags. The formats for each instruction are found in the next section.

Table 19. DA Instructions

| Instructions Format DAU Flags Affected |     |   |   |          |            |  |  |

|----------------------------------------|-----|---|---|----------|------------|--|--|

| Multiply/Accumulate:                   |     |   |   |          |            |  |  |

| [Z =] aN = [_]aM {+,_} Y* X            | 3   | N | Z | ٧        | J          |  |  |

| $aN = [-]aM \{+,-\} (Z=Y)* X$          | 2   | N | Z | <b>V</b> | د          |  |  |

| $[Z =] aN = [-]Y \{+,-\} aM*X$         | 1   | N | Z | <b>V</b> | <u>ر</u> ا |  |  |

| [Z =] aN = [_]Y* X                     | 3   | N | Z | ٧        | د          |  |  |

| aN = [_](Z=Y)* X                       | 2   | N | Z | ٧        | ٦          |  |  |

| [Z =] aN = [_]Y {+,_} X                | _ 1 | N | Z | ٧        | υ          |  |  |

| [Z =] aN = [_]Y                        | 1   | N | Z | V        | U          |  |  |

| Special Functions:                     |     |   |   |          |            |  |  |

| [Z=] aN = ic(Y)                        | 4   | N | Z | 0        | 0          |  |  |

| [Z=] aN = oc(Y)                        | 4   |   |   |          |            |  |  |

| [Z=] aN = float(Y)                     | 4   | N | Z | 0        | 0          |  |  |

| [Z=] aN = int(Y)                       | 4   |   |   |          | _          |  |  |

| [Z=] aN = round(Y)                     | 4   | N | Z | ٧        | U          |  |  |

| [Z=] aN = ifalt(Y)                     | 4   |   | _ | _        | -          |  |  |

Table 20. CA Instructions

| Instructions                          | Format | CAL | J Flags | Affe | cted |

|---------------------------------------|--------|-----|---------|------|------|

| Control Group:                        |        |     |         |      |      |

| if (CA COND) goto {rH, N, rH+N, rH-N} | 0      | _   | _       |      |      |

| if (rM>=0) goto {rH, N, rH+N, rH-N}   | 3      | _   |         | _    | _    |

| if (DA COND) goto {rH, N, rH+N, rH-N} | 0      |     | _       | _    | _    |

| if (IO COND) goto {rH, N, rH+N, rH-N} | 1      | _   | _       | _    |      |

| call {rH, N, rH+N, rH-N} (rM)         | 4      |     | _       |      |      |

| return (rM)                           | 0      | _   |         |      | _    |

| goto {rH, N, rH+N, rH-N}              | 0      | _   | _       |      | _    |

| [L]*nop                               | 0      | _   | _       | _    |      |

| Arithmetic Logical Group:             |        | -   |         | -    |      |

| rD = rH + N                           | 5      | n   | z       | v    | С    |

| rD = rD + rS                          | 6a     | n   | z       | ٧    | С    |

| $rD = rD - \{N, rS\}$                 | 6a,b   | n   | z       | V    | С    |

| rD-{N, rS}                            | 6a,b   | n   | z       | v    | С    |

| $rD = \{N, rS\} - rD$                 | 6a,b   | n   | Z       | ٧    | С    |

| $rD = rD&\{N, rS\}$                   | 6a,b   | n   | z       | 0    | 0    |

| rD&{N, rS}                            | 6a,b   | n   | z       | 0    | 0    |

| $rD = rD   \{N, rS\}$                 | 6a,b   | n   | z       | 0    | 0    |

| $rD = rD^{N}, rS$                     | 6a,b   | n   | z       | 0    | 0    |

| rD = rS/2                             | 6a     | n   | z       | 0    | С    |

| rD = rS>>1                            | 6a     | 0   | z       | 0    | С    |

| rD = -rS                              | 6a     | n   | z       | >    | С    |

| rD = rS*2                             | 6a     | n   | z       | ٧    | С    |

| Data Move Group:                      |        |     |         |      |      |

| rD = N                                | 5      | n   | z       | 0    | 0    |

| {ioc, dauc} = VALUE                   | 5      | _   | _       | _    | _    |

| $\{MEM, *N, obuf\} = \{rSh, rSI\}$    | 7a,b,c | _   |         |      |      |

| $\{MEM, *N, obuf, pdr, pir\} = rS$    | 7a,b,c | _   |         |      |      |

| $rD = \{MEM, *N, ibuf, pdr\}$         | 7a,b,c | n   | z       | 0    | 0    |

| ${rDh, rDl} = {MEM, *N, ibuf}$        | 7a,b,c | n   | z       | 0    | 0    |

## WE DSP32 Digital Signal Processor

#### **DA Instruction Formats**

There are four DA instruction formats. Refer to the section on DAU encoding for DA instruction formats for an explanation of each field, except where actual bit values (0, 1) are given.

#### Format 1.

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20—14 | 13—7 | 6—0 |  |

|-------|----|----|----|----|----|----|----|----|----|----|----|-------|------|-----|--|

| Field | Р  | 0  | 1  |    | М  |    |    | F  | S  | N  | 1  | Х     | Υ    | Z   |  |

#### Format 2.

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20—14 | 137 | 6—0 |

|-------|----|----|----|----|----|----|----|----|----|----|----|-------|-----|-----|

| Field | Б  | 1  | 0  |    | М  | -  |    | F  | S  |    | 1  | X     | Υ   | Z   |

#### Format 3.

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20—14 | 13—7 | 6—0 |

|-------|----|----|----|----|----|----|----|----|----|----|----|-------|------|-----|

| Field | Р  | 1  | 1  |    | М  |    | -  | F  | S  | 1  | 1  | Х     | Υ    | Z   |

#### Format 4.

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20—14 | 13—7 | 60 |

|-------|----|----|----|----|----|----|----|----|----|----|----|-------|------|----|

| Field | Р  | 1  | 1  | 1  | 1  |    | G  |    |    | ١  | 1  | _     | Υ    | Z  |

### **DAU Encoding for DA Instruction Formats**

P Field (Bit 31). Specifies the parity bit. This field maintains an odd number of 1s in the encoding format (odd parity). If the remaining 31 bits of the instruction contain an even number of 1s, the P bit is 1; otherwise, the P bit is 0.

Note: This P field (parity) is not to be confused with the p field used for memory pointers (rP).

**G Field.** Specifies a data type conversion operation.

| G    | Operation              |

|------|------------------------|

| 0000 | ic (input conversion)  |

| 0001 | oc (output conversion) |

| 0010 | float                  |

| 0011 | integer                |

| 0100 | round                  |

| 0101 | ifalt                  |

| 0110 |                        |

| 0111 |                        |

| 1000 |                        |

| 1001 |                        |

| 1010 | Reserved               |

| 1011 |                        |

| 1100 |                        |

| 1101 |                        |

| 1110 |                        |

| 1111 |                        |

**M Field**. Specifies the accumulator used or a constant value.

| М          | Operand  |

|------------|----------|

| 000        | a0       |

| 001        | a1       |

| 010        | a2       |

| 011        | a3       |

| 100        | 0.0      |

| 101        | 1.0      |

| 110<br>111 | Reserved |

F Field. Specifies sign of operation.

| F | Sign |

|---|------|

| 0 | +    |

| 1 | _    |

N Field. Specifies the accumulator used.

| N  | Operand |

|----|---------|

| 00 | a0      |

| 01 | a1      |

| 10 | a2      |

| 11 | a3      |

S Field. Specifies sign of operation.

| S | Sign |

|---|------|

| 0 | +    |

| 1 | _    |

X, Y, Z Fields. These fields indicate register direct or register indirect modes. The 7-bit fields are divided into two subfields, p and i (ppppiii). Bits 0—2 of the 7-bit field are labeled i; the i subfield specifies an rI register in the CAU. Bits 3—6 are labeled p; the p field specifies an rP register in the CAU.

p Field. Specifies register indirect: \*rP, \*rP++,

\*rP--, \*rP++rl.

| р    | Operand                  |

|------|--------------------------|

| 0000 | Selects register direct* |

| 0001 | r1                       |

| 0010 | r2                       |

| 0011 | r3                       |

| 0100 | r4                       |

| 0101 | r5                       |

| 0110 | r6                       |

| 0111 | r7                       |

| 1000 | r8                       |

| 1001 | r9                       |

| 1010 | r10                      |

| 1011 | r11                      |

| 1100 | r12                      |

| 1101 | r13                      |

| 1110 | r14                      |

| 1111 | Y(p) when $Y(p) = X(p)$  |

|      | Z(p) when $Z(p) = Y(p)$  |

<sup>\*</sup> See i field (p = 0000).

i Field (p = 0000). Specifies a register direct operation: REG. This is a special case of the i field (when p field equals 0).

| i   | Operand (p = 0000)                           |

|-----|----------------------------------------------|

| 000 | a0 – X, Y fields only                        |

| 001 | a1 - X, Y fields only                        |

| 010 | a2 – X, Y fields only                        |

| 011 | a3 – X, Y fields only                        |

| 100 | ibuf – X, Y fields only                      |

| 101 | obuf – Z field only                          |

| 110 | pdr – Y, Z fields<br>(special function only) |

| 111 | No write, Z field only                       |

i Field (p  $\neq$  0000). Specifies register indirect: rl, rP++rl.

| i   | <b>Operand (p ≠ 0000)</b> |

|-----|---------------------------|

| 000 | 0                         |

| 001 | r15                       |

| 010 | r16                       |

| 011 | r17                       |

| 100 | r18                       |

| 101 | r19                       |

| 110 | -4(f), -2(i), -1(b)       |

| 111 | +4(f), +2(i), +1(b)       |

#### **CA Instruction Formats**

There are seven CA instruction formats. Refer to the section on CAU encoding for CA instruction formats for an explanation of each field, except where actual bit values (0, 1) are given.

#### Formats 0 and 1. Conditional Branch

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15—0 |

|-------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|------|

| Field | P  | 0  | 0  | 0  | 0  |    |    | С  |    |    | G  |    |    | Н  | _  |    | N    |

#### Format 2. Reserved

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 |   |      |      |  | 0 |

|-------|----|----|----|----|----|----|----|---|------|------|--|---|

| Field | Р  | 0  | 0  | 0  | 1  | 0  |    | _ | Rese | rved |  |   |

#### Format 3. Loop Counter

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15—0 |

|-------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|------|

| Field | Р  | 0  | 0  | 0  | 1  | 1  |    |    | М  |    |    |    |    | Н  |    |    | N    |

#### Format 4. Call

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15—0 |   |

|-------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|------|---|

| Field | Р  | 0  | 0  | 1  | 0  | 0  |    |    | М  |    |    |    |    | Н  |    |    | N    | ĺ |

### Format 5. Three Operand Add

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23_ | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15—0 |

|-------|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|----|------|

| Field | P  | 0  | 0  | 1  | 0  | 1  |    |    | D   |    |    |    |    | Н  |    |    | N    |

## Format 6a. Arithmetic/Logic Group — Register Source

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15—10 | 9—5 | 40 |

|-------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-------|-----|----|

| Field | Р  | 0  | 0  | 1  | 1  | 0  | 0  |    |    | F  |    |    |    | D  |    |    |       | S   |    |

## Format 6b. Arithmetic/Logic Group — Immediate Operand

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15—0 |

|-------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|------|

| Field | Р  | 0  | 0  | 1  | 1  | 0  | 1  |    |    | F  |    |    |    | D  |    |    | N    |

## Format 7a. Data Move Group — Direct Memory Address

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15—0 |  |

|-------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|------|--|

| Field |    |    |    |    | 1  |    |    |    | Ť  | ٧  | 0  |    |    | Н  |    |    | N    |  |

## WE DSP32 Digital Signal Processor

### Format 7b. Data Move Group — Pointer Increment, Memory Address

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18  | 17 | 16 | 15—10 | 9—5 | 4—0 |

|-------|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|----|----|-------|-----|-----|

| Field | Р  | 0  | 0  | 1  | 1  | 1  | 1  | T  | v  | V  | 1  |    |    | _н_ |    |    | 1     | Р   | 1   |

### Format 7c. Data Move Group — I/O

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15—10 | 9—5   | 4—0 |  |

|-------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-------|-------|-----|--|

| Field | Р  | 0  | 0  | 1  | 1  | 1  | 1  | Т  | ٧  | ٧  | 0  |    |    | Н  | -  |    | _     | 00000 | R   |  |

### **CAU Encoding for CA Instruction Formats**

P Field (Bit 31). Specifies the parity bit. This field maintains an odd number of 1s in the encoding format (odd parity). If the remaining 31 bits of the instruction have an even number of 1s, the P bit is 1; otherwise, the P bit is 0.

Note: This P field (parity) is not to be confused with the p field used for memory pointers (rP).

C Field. Specifies a CA, DA, or I/O condition.

| С     | Condition    | С     | Condition | С     | Condition |

|-------|--------------|-------|-----------|-------|-----------|

| 00xxx | CA           | 01xxx | DA        | 10xxx | 1/0       |

| 00000 | No condition | 01000 | U         | 10000 | ibf       |

| 00001 | n            | 01001 | N         | 10001 | obe       |

| 00010 | z            | 01010 | Z         | 10010 | pdf       |

| 00011 | V            | 01011 | [ V [     | 10011 | pif       |

| 00100 | C            | 01100 | N Z       | 10100 | sy        |

| 00101 | n^v          | 01101 | Reserved  | 10101 | fb        |

| 00110 | z   (n^v)    | 01110 | Reserved  | 10110 | Reserved  |

| 00111 | C Z          | 01111 | Reserved  | 10111 | Reserved  |

**T Field.** Specifies the direction of a transfer: to or from a register.

| Т | Operation                               |  |  |

|---|-----------------------------------------|--|--|

| 0 | Data is moved to a register from memory |  |  |

| 1 | Data is moved to memory from a register |  |  |

**W Field.** Specifies the high or low byte or integer data.

| W  | Description |

|----|-------------|

| 00 | High byte   |

| 01 | Low byte    |

| 1x | Integer     |

G Field. Specifies whether to branch if the condition specified in the C Field is true or false.

| G  | Operation                       |

|----|---------------------------------|

| 0  | Branch if condition = 0 (false) |

| 1_ | Branch if condition = 1 (true)  |

**F Field.** Specifies the arithmetic/logic group function encoding.

| F    | Operation     |

|------|---------------|

| 0000 | rD=rD+rS      |

| 0001 | rD=rS∗2       |

| 0010 | rD={N,rS}_rD  |

| 0011 | Reserved      |

| 0100 | rD=rD-{N,rS}  |

| 0101 | rD=_rS        |

| 0110 | Reserved      |

| 0111 | rD-{N,rS}     |

| 1000 | rD=rD^{N,rS}  |

| 1001 | Reserved      |

| 1010 | rD=D   {N,rS} |

| 1011 | Reserved      |

| 1100 | rD=rS>>1      |

| 1101 | rD=rS/2       |

| 1110 | rD=rD&{N,rS}  |

| 1111 | rD&{N,rS}     |

S, D, M, or H Fields. Used for register encoding.

| S,D,M, or H | Operand              |

|-------------|----------------------|

| 00000       | 0                    |

| 00001       | r1                   |

| 00010       | r2                   |

| 00011       | r3                   |

| 00100       | r4                   |

| 00101       | r5                   |

| 00110       | r6                   |

| 00111       | r7                   |

| 01000       | r8                   |

| 01001       | r9                   |

| 01010       | r10                  |

| 01011       | r11                  |

| 01100       | r12                  |

| 01101       | r13                  |

| 01110       | r14                  |

| 01111       | Program counter (pc) |

| 10000       | 0                    |

| 10001       | r15                  |

| 10010       | r16                  |

| 10011       | r17                  |

| 10100       | r <b>1</b> 8         |

| 10101       | r19                  |

| 10110       | -4(f),-2(i),-1(b)    |

| 10111       | +4(f),+2(i),+1(b)    |

| 11000       | r20 (pin)            |

| 11001       | r21 (pout)           |

| 11010       | dauc                 |

| 11011       | ioc                  |

| 11100       |                      |

| 11101       | Reserved             |

| 11110       |                      |

| 11111       |                      |

**P Field.** Specifies a register indirect data move: \*rP, \*rP++, \*rP--, \*rP++rl.

| Р     | Operand           |

|-------|-------------------|

| 00000 | Selects Format 7C |

| 00001 | r1                |

| 00010 | r2                |

| 00011 | r3                |

| 00100 | r4                |

| 00101 | r5                |

| 00110 | r6                |

| 00111 | r7                |

| 01000 | r8                |

| 01001 | r9                |

| 01010 | r10               |

| 01011 | r11               |

| 01100 | r12               |

| 01101 | r13               |

| 01110 | r14               |

| 01111 | Reserved          |

| 10000 | Reserved          |

| 10001 | r15               |

| 10010 | r16               |

| 10011 | r17               |

| 10100 | r18               |

| 10101 | r19               |

| 10110 | Reserved          |

| 10111 | Reserved          |

| 11000 | r20 (pin)         |

| 11001 | r21 (pout)        |

| 11010 |                   |

| 11011 |                   |

| 11100 | Reserved          |

| 11101 |                   |

| 11110 |                   |

| 11111 |                   |

I Field. Specifies a register indirect operation.

| i     | Operand      |

|-------|--------------|

| 00000 | Reserved     |

| 00001 | r1           |

| 00010 | r2           |

| 00011 | r3           |

| 00100 | r4           |

| 00101 | r5           |

| 00110 | r6           |

| 00111 | r7           |

| 01000 | r8           |

| 01001 | r9           |

| 01010 | r10          |

| 01011 | r11          |

| 01100 | r12          |

| 01101 | r13          |

| 01110 | r14          |

| 01111 | Reserved     |

| 10000 | 0            |

| 10001 | r15          |

| 10010 | r16          |

| 10011 | r17          |

| 10100 | r18          |

| 10101 | r19          |

| 10110 | -2(i), -1(b) |

| 10111 | +2(i),+1(b)  |

| 11000 | r20 (pin)    |

| 11001 | r21 (pout)   |

| 11010 |              |

| 11011 |              |

| 11100 | Reserved     |

| 11101 |              |

| 11110 |              |

| 11111 |              |

N Field. Specifies a 16-bit integer included as immediate data or as an address.

R Field (P = 00000). Specifies a register direct operation. This field is valid when the P Field is 0.

| R              | Operand (P=00000) |  |

|----------------|-------------------|--|

| 00000          |                   |  |

| 00001          |                   |  |

| 00010          | Reserved          |  |

| 00011          |                   |  |

| 00100          | ibuf              |  |

| 00101          | obuf              |  |

| 00110          | pdr               |  |

| 00111          |                   |  |

| 01000          |                   |  |

| 01001          |                   |  |

| 01010          |                   |  |

| 01011          |                   |  |

| 01100          |                   |  |

| 01101          |                   |  |

| 01110          | Reserved          |  |

| 01111          |                   |  |

| 10000          |                   |  |

| 10001          |                   |  |

| 10010<br>10011 |                   |  |

| 101100         |                   |  |

| 10100          |                   |  |

| 10110          | pir               |  |

| 10111          | F.**              |  |

| 11000          |                   |  |

| 11001          |                   |  |

| 11010          |                   |  |

| 11011          | Reserved          |  |

| 11100          |                   |  |

| 11101          |                   |  |

| 11110          |                   |  |

| 11111          |                   |  |

## **Pin Descriptions**

In Tables 21—27, I = input, O = output, and P = power. All DSP32 output pins may be 3-stated. A microprocessor ( $\mu$ P) is used as an example of an external device connected to DSP32 device through the PIO interface.

### 40-Pin DIP

Figure 3. 40-Pin DIP Pin Diagram

Table 21. Pin Descriptions by Numerical Order — 40-Pin DIP

| Pin    | Symbol       | Туре | Name/Description                                                                                                                                                                                                                                                                                                                                                                                                |

|--------|--------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 2 3  | Vss          | Р    | Ground.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4      | ско          | 0    | Clock Out. Buffered clock at the same frequency as CKI. Synchronizes external devices to the DSP32.                                                                                                                                                                                                                                                                                                             |

| 5      | CKI          | ı    | Clock In. Input clock.                                                                                                                                                                                                                                                                                                                                                                                          |

| 6      | ZN           | 1    | 3-State (Active Low). When active, all DSP32 output pins are 3-stated (high impedance); when not connected, ZN is inactive.                                                                                                                                                                                                                                                                                     |

| 7<br>8 | MMD0<br>MMD1 | ı    | Memory Mode — Bits 0 and 1. Decoded to select the address of on-chip memory (see the Memory Addressing section).                                                                                                                                                                                                                                                                                                |

| 9      | PWN          | 1    | Processor Write Enable (Active Low). When active, enables on-chip registers to be written to by a $\mu P$ .                                                                                                                                                                                                                                                                                                     |

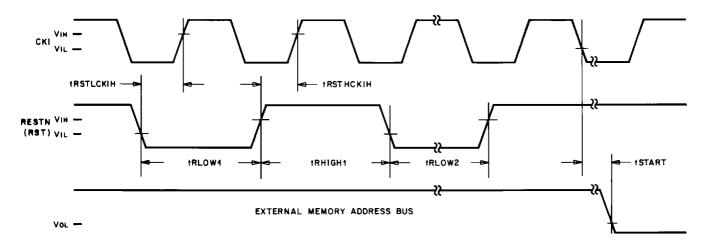

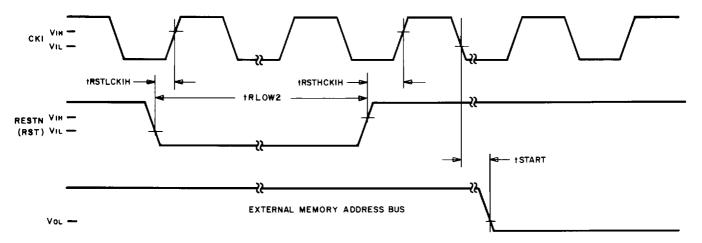

| 10     | RESTN        | I    | Reset (Active Low). Controls the DSP32 run/halt state. A high-to-low transition causes entry into the halt state; a low-to-high transition causes the reset sequence. The reset sequence stores the PC in r14; clears PC, IOC, ESR; and sets EMR to mask all errors. The PCR register bits, except PCR0, are cleared; PCR0 is set. CAU and DAU condition flags and the DAUC register are not affected by reset. |

Table 21. Pin Descriptions by Numerical Order — 40-Pin DIP (Continued)

| Pin                                          | Symbol                                                       | Туре | Name/Description                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------|--------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11<br>12<br>13<br>14<br>15<br>16<br>17<br>18 | PDB0<br>PDB1<br>PDB2<br>PDB3<br>PDB4<br>PDB5<br>PDB6<br>PDB7 | 1/0  | Parallel Data Bus — Bit 0.  Parallel Data Bus — Bit 1.  Parallel Data Bus — Bit 2.  Parallel Data Bus — Bit 3.  Parallel Data Bus — Bit 4.  Parallel Data Bus — Bit 5.  Parallel Data Bus — Bit 6.  Parallel Data Bus — Bit 7.  Bidirectional 8-bit  data bus for $\mu$ P interface.  This bus transfers  data into and out of the PIO registers for use by a $\mu$ P. |

| 19                                           | PINT                                                         | 0    | <b>Processor Interrupt.</b> Interrupt to $\mu$ P. PINT is set when a nonmasked error occurs or when the DSP32 writes to PIR and bit 2 of PCR is high; PINT is cleared by reading ESR or PIR.                                                                                                                                                                           |

| 20                                           | PDF                                                          | 0    | <b>Parallel Data Full.</b> Set when PDR is written to by the DSP32 or a $\mu$ P; cleared when PDR is read by the DSP32 or a $\mu$ P.                                                                                                                                                                                                                                   |

| 21                                           | оск                                                          | 1/0  | Output Clock. Clock for serial PCM output data. In internal mode OCK is an output; in external mode OCK is an input, depending on the I/O format.                                                                                                                                                                                                                      |