# MC68307 Integrated Multiple-Bus Processor User's Manual

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (*P*) are registered trademarks of Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

-----

## **Documentation Comments**

#### FAX 512-891-8593—Documentation Comments Only

The Motorola High-Performance Embedded Systems Technical Communications Department provides a fax number for you to submit any questions or comments about this document or how to order other documents. We welcome your suggestions for improving our documentation. Please do not fax technical questions.

Please provide the part number and revision number (located in upper right-hand corner of the cover) and the title of the document. When referring to items in the manual, please reference by the page number, paragraph number, figure number, table number, and line number if needed.

When sending a fax, please provide your name, company, fax number, and phone number including area code.

# **Applications and Technical Information**

For questions or comments pertaining to technical information, questions, and applications, please contact one of the following sales offices nearest you.

# - Sales Offices —

\_

Field Applications Engineering Available Through All Sales Offices

| UNITED STATES                                                        |                                                                      | GERMANY, Langenhagen/ Hanover                                                                                                                                | 49(511)789911                          |

|----------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| ALABAMA, Huntsville                                                  | (205) 464-6800                                                       | GERMANY, Munich                                                                                                                                              | 49 89 92103-0                          |

| ARIZONA. Tempe                                                       | (602) 897-5056                                                       | GERMANY, Nuremberg                                                                                                                                           | 49 911 64-3044                         |

| CALIFORNIA, Agoura Hills<br>CALIFORNIA, Los Angeles                  | (818) 706-1929<br>(310) 417-8848                                     | GERMANY, Sindelfingen                                                                                                                                        | 49 7031 69 910                         |

| CALIFORNIA. Irvine                                                   | (714) 753-7360                                                       | GERMANY, Nuremberg<br>GERMANY, Sindelfingen<br>GERMANY, Wiesbaden<br>HONG KONG, Kwai Fong<br>Tai Do                                                          | 49 611 761921                          |

| CALIFORNIA, RosevIlle                                                | (916) 922-7152                                                       | Tai Po                                                                                                                                                       | 852-4808333<br>852-6668333             |

| CALIFORNIA, San Diego                                                | (619) 541-2163                                                       | INDIA, Bangalore                                                                                                                                             | (91-812)627094                         |

| CALIFORNIA, Sunnyvale<br>COLORADO, Colorado Springs                  | (408) 749-0510<br>(719) 599-7497                                     | ISRAEL, Tel Aviv                                                                                                                                             | 972(3)753-8222                         |

| COLORADO, Denver                                                     | (719) 599-7497<br>(303) 337-3434                                     | ITALY, Milan                                                                                                                                                 | 39(2)82201                             |

| CONNECTICUT, Wallingford                                             | (203) 949-4100                                                       | JAPAN, Aizu                                                                                                                                                  | 81(241)272231                          |

| FLORIDA, Maitland<br>FLORIDA, Pompano Beach/                         | (407) 628-2636                                                       | JAPAN, Atsugi                                                                                                                                                | 81(0462)23-0761                        |

| Fort Lauderdale                                                      | (305) 486-9776                                                       | JAPAN, Kumagaya<br>JAPAN, Kyushu                                                                                                                             | 81(0485)26-2600<br>81(092)771-4212     |

| FLORIDA, Clearwater                                                  | (813) 538-7750<br>(404) 729-7100                                     | JAPAN, Mito                                                                                                                                                  | 81(0292)26-2340                        |

| GEORGIA, Atlanta<br>IDAHO, Boise                                     | (404) 729-7100<br>(208) 323-9413                                     | JAPAN, Nagova                                                                                                                                                | 81(052)232-1621                        |

| ILLINOIS. Chicago/Hoffman Estates                                    | (708) 490-9500                                                       | JAPAN, Nagoya<br>JAPAN, Osaka                                                                                                                                | 81(06)305-1801                         |

| INDIANA, Fort Wayne                                                  | (219) 436-5818                                                       | JAPAN, Sendai                                                                                                                                                | 81(22)268-4333                         |

| INDIANA, Indianapolis                                                | (317) 571-0400                                                       | JAPAN, Tachikawa                                                                                                                                             | 81(0425)23-6700                        |

| INDIANA, Kokomo<br>IOWA, Cedar Rapids                                | (317) 457-6634<br>(319) 373-1328                                     | JAPAN, Tokyo                                                                                                                                                 | 81(03)3440-3311                        |

| KANSAS, Kansas City/Mission<br>MARYLAND, Columbia                    | (913) 451-8555                                                       | <b>JAPAN</b> , Yokohama<br><b>KOREA</b> , Pusan                                                                                                              | 81(045)472-2751<br>82(51)4635-035      |

| MARYLAND, Columbia                                                   | (410) 381-1570                                                       | KOREA, Fusan                                                                                                                                                 | 82(2)554-5188                          |

| MASSACHUSETTS, Marborough<br>MASSACHUSETTS, Woburn                   | (508) 481-8100<br>(617) 932-9700                                     | MALAYSIA, Penang                                                                                                                                             | 60(4)374514                            |

| MICHIGAN, Detroit                                                    | (313) 347-6800                                                       | KOREA, Pusan<br>KOREA, Seoul<br>MALAYSIA, Penang<br>MEXICO, Mexico City                                                                                      | 52(5)282-2864                          |

| MINNESOTA, Minnetonka                                                | (612) 932-1500                                                       | MEXICO, Guadalajara                                                                                                                                          | 52(36)21-8977                          |

| MISSOURI, St. Louis<br>NEW JERSEY, Fairfield                         | (314) 275-7380<br>(201) 808-2400                                     | Marketing                                                                                                                                                    | 52(36)21-9023                          |

| NEW YORK Fairport                                                    | (716) 425-4000                                                       | NETHERI ANDS Best                                                                                                                                            | (31)49988 612 11                       |

| NEW YORK, Hauppauge<br>NEW YORK, Poughkeepsie/Fishkill               | (516) 361-7000                                                       | MEXICO, Mexico Ory<br>Mexico, Guadalajara<br>Marketing<br>Customer Service<br>NETHERLANDS, Best<br>PUERTO RICO, San Juan<br>SINGAPORE<br>SPAIN, Madrid<br>or | (809)793-2170                          |

| NEW YORK, Poughkeepsie/Fishkill<br>NORTH CAROLINA, Raleigh           | (914) 473-8102<br>(919) 870-4355                                     | SINGAPORE                                                                                                                                                    | (65)2945438                            |

| OHIO, Cleveland                                                      | (216) 349-3100                                                       | SPAIN, Madrid                                                                                                                                                | 34(1)457-8204                          |

| OHIO, Columbus/Worthington                                           | (614) 431-8492                                                       |                                                                                                                                                              | <b>e</b> .(.). <b>e</b> . <b>e</b> _e. |

| OHIO, Dayton<br>OKLAHOMA, Tulsa                                      | (513) 495-6800<br>(800) 544-9496                                     | SWEDEN, Solna                                                                                                                                                | 46(8)734-8800<br>41(22)7991111         |

| OREGON Portland                                                      | (503) 641-3681                                                       | SWITZERLAND, Zurich                                                                                                                                          | 41(1)730 4074                          |

| PENNSYLVANIA, Colmar                                                 | (215) 997-1020                                                       | TAIWAN, Taipei                                                                                                                                               | 886(2)717-7089                         |

| PENNSYLVANIA, Colmar<br>Philadelphia/Horsham<br>TENNESSEE, Knoxville | (503) 641-3681<br>(215) 997-1020<br>(215) 957-4100<br>(615) 690-5593 | THAILAND, Bangkok                                                                                                                                            | (66-2)254-4910                         |

| TEXAS, Austin                                                        | (512) 873-2000                                                       | SWITZERLAND, Geneva<br>SWITZERLAND, Zurich<br>TAIWAN, Taipei<br>THAILAND, Bangkok<br>UNITED KINGDOM, Aylesbury                                               | 44(296)395-252                         |

| TEXAS, Houston<br>TEXAS, Plano                                       | (800) 343-2692                                                       | FULL LINE REPRESENT                                                                                                                                          |                                        |

| VIRGINIA, Richmond                                                   | (214) 516-5100<br>(804) 285-2100                                     | COLORADO, Grand Junction                                                                                                                                     | (000) 040 0050                         |

| WASHINGTON, Bellevue                                                 | (206) 454-4160                                                       | Cheryl Lee Whltely<br>KANSAS, Wichita                                                                                                                        | (303) 243-9658                         |

| Seattle Access                                                       | (206) 622-9960                                                       | Melinda Shores/Kelly Greiving                                                                                                                                | (316) 838 0190                         |

| WISCONSIN, Milwaukee/Brookfield                                      | (414) 792-0122                                                       | NEVADA, Reno                                                                                                                                                 |                                        |

|                                                                      | (00.4) 000 7005                                                      |                                                                                                                                                              | (702) 746 0642                         |

| BRITISH COLUMBIA, Vancouver<br>ONTARIO, Toronto                      | (604) 293-7605<br>(416) 497-8181                                     | Galena Technology Group<br>NEW MEXICO, Albuquerque<br>S&S Technologies, Inc.                                                                                 | (505) 000 7477                         |

| ONTARIO, Ottawa                                                      | (613) 226-3491                                                       | S&S Lechnologies, Inc.                                                                                                                                       | (505) 298-7177                         |

| QUEBEC, Montreal                                                     | (514) 731-6881                                                       | UTAH, Salt Lake City<br>Utah Component Sales, Inc.                                                                                                           | (801) 561-5099                         |

| INTERNATIONAL                                                        |                                                                      | WASHINGTON, Spokane                                                                                                                                          |                                        |

| AUSTRALIA, Melbourne                                                 | (61-3)887-0711                                                       | Doug Kenley                                                                                                                                                  | (509) 924-2322                         |

| AUSTRALIA, Sydney                                                    | (61(2)906-3855                                                       | ARGENTINA, Buenos Aires                                                                                                                                      |                                        |

| BRAZIL, Sao Paulo                                                    | 55(11)815-4200                                                       | Argonics, S.A.                                                                                                                                               | (541) 343-1787                         |

| CHINA, Beijing<br>FINLAND, Helsinki                                  | 86 505-2180<br>358-0-35161191                                        | HYBRID COMPONENTS RE                                                                                                                                         |                                        |

| Car Phone                                                            | 358(49)211501                                                        | Elmo Semiconductor<br>Minco Technology Labs Inc.                                                                                                             | (818) 768-7400<br>(512) 834-2022       |

| FRANCE, Paris/Vanves                                                 | 33(1)40 955 900                                                      | Semi Dice Inc.                                                                                                                                               | (310) 594-4631                         |

|                                                                      |                                                                      |                                                                                                                                                              |                                        |

# PREFACE

The *MC68307 User's Manual* describes the programming, capabilities, and operation of the MC68307 and the *MC68000 Family Programmer's Reference Manual* provides instruction details for the MC68307.

The organization of this manual is as follows:

- Section 1 Introduction

- Section 2 Signal Description

- Section 3 Bus Operation

- Section 4 EC000 Core Processor

- Section 5 System Integration Module

- Section 6 Dual Timer Module

- Section 7 M-Bus Interface Module

- Section 8 Serial Module

- Section 9 IEEE 1149.1 Test Access Port

- Section 10 Applications Information

- Section 11 Electrical Characteristics

- Section 12 Ordering Information and Mechanical Data

# **TABLE OF CONTENTS**

#### Section 1 Introduction

| 1.1     | M68300 Family                         | 1-3 |

|---------|---------------------------------------|-----|

| 1.1.1   | Organization                          |     |

| 1.1.2   | Advantages                            | 1-3 |

| 1.2     | MC68307 Architecture                  | 1-4 |

| 1.2.1   | EC000 Core Processor                  | 1-4 |

| 1.2.2   | System Integration Module (SIM07)     | 1-4 |

| 1.2.2.1 | External Bus Interface                |     |

| 1.2.2.2 | Chip Select And Wait State Generation | 1-5 |

| 1.2.2.3 | System Configuration and Protection   | 1-5 |

| 1.2.2.4 | Parallel Input/Output Ports           |     |

| 1.2.2.5 | Interrupt Controller                  |     |

| 1.2.3   | Timer Module                          |     |

| 1.2.4   | UART Module                           |     |

| 1.2.5   | M-Bus Module                          |     |

| 1.2.6   | Test Access Port                      | 1-7 |

#### Section 2 Signal Description

| 2.1     | Bus Signals                              | 2-5 |

|---------|------------------------------------------|-----|

| 2.1.1   | Address Bus (A23–A0)                     |     |

| 2.1.1.1 | Address Bus (A23–A8)                     |     |

| 2.1.1.2 | Address Bus (AD7–AD0)                    |     |

| 2.1.2   | Data Bus (D15–D0)                        |     |

| 2.2     | Chip Selects                             |     |

| 2.2.1   | Chip Select 0 (CS0)                      |     |

| 2.2.2   | Chip Select 1 (CS1)                      |     |

| 2.2.3   | Chip Select 2 (CS2, CS2B, CS2C, CS2D)    |     |

| 2.2.4   | Chip Select 3 (CS3)                      |     |

| 2.3     | Bus Control Signals                      |     |

| 2.3.1   | Data Transfer Acknowledge (DTACK)        | 2-7 |

| 2.3.2   | Address Strobe (AS)                      | 2-8 |

| 2.3.3   | Read/Write (R/W)                         | 2-8 |

| 2.3.4   | Data Strobes, Upper and Lower (UDS, LDS) |     |

| 2.3.5   | 8051 Address Latch Enable (ALE)          |     |

| 2.3.6   | 8051-Compatible Bus Read (RD)            |     |

| 2.3.7   | 8051-Compatible Bus Write (WR)           |     |

| 2.3.8   | Bus Width Select for CS0 (BUSW0)         |     |

| 2.4     | Exception Control Signals                |     |

#### MC68307 USER'S MANUAL

· · · <del>·</del> · · · · · · ·

---- . .

| 2.4.1  | Reset (RESET)                         |      |

|--------|---------------------------------------|------|

| 2.4.2  | Power-On Reset (RSTIN)                |      |

| 2.4.3  | Halt (HALT)                           |      |

| 2.4.4  | Bus Request (BR/PA5)                  |      |

| 2.4.5  | Bus Grant (BG/PA6)                    |      |

| 2.4.6  | Bus Grant Acknowledge (BGACK /PA7)    |      |

| 2.5    | Clock Signals                         |      |

| 2.5.1  | Crystal Oscillator (EXTAL, XTAL)      |      |

| 2.5.2  | Clock Output (CLKOUT)                 | 2-11 |

| 2.6    | Test Signals                          | 2-11 |

| 2.6.1  | Test Clock (TCK)                      |      |

| 2.6.2  | Test Mode Select (TMS)                | 2-11 |

| 2.6.3  | Test Data In (TDI)                    |      |

| 2.6.4  | Test Data Out (TDO)                   | 2-11 |

| 2.7    | M-Bus I/O Signals                     |      |

| 2.7.1  | Serial Clock (SCL/PB0)                | 2-11 |

| 2.7.2  | Serial Data (SDA/PB1)                 |      |

| 2.8    | UART I/O Signals                      |      |

| 2.8.1  | Transmit Data (TxD/PB2)               |      |

| 2.8.2  | Receive Data (RxD/PB3)                |      |

| 2.8.3  | Request-To-Send (RTS/PB4)             |      |

| 2.8.4  | Clear-To-Send (CTS/PB5)               |      |

| 2.9    | Timer I/O Signals                     |      |

| 2.9.1  | Timer 1 Input (TIN1/PB6)              |      |

| 2.9.2  | Timer 2 Input (TIN2/PB7)              |      |

| 2.9.3  | Timer 1 Output (TOUT1/PA3)            |      |

| 2.9.4  | Timer 2 Output (TOUT2/PA4)            |      |

| 2.10   | Interrupt Request Inputs              |      |

| 2.10.1 | Interrupt Inputs (INT1-INT8/PB8-PB15) |      |

| 2.10.2 | Non-Maskable Interrupt Input (IRQ7)   |      |

| 2.11   | Use of Pullup Resistors               |      |

| 2.12   | Signal Index                          |      |

#### Section 3 Bus Operation

| 3.1   | Data Transfer Operations           |      |

|-------|------------------------------------|------|

| 3.1.1 | 16-Bit M68000 Bus Operation        |      |

| 3.1.2 | 16-Bit M68000 Bus Read Cycle       |      |

| 3.1.3 | 16-Bit M68000 Bus Write Cycle      |      |

| 3.1.4 | Read-Modify-Write Cycle            |      |

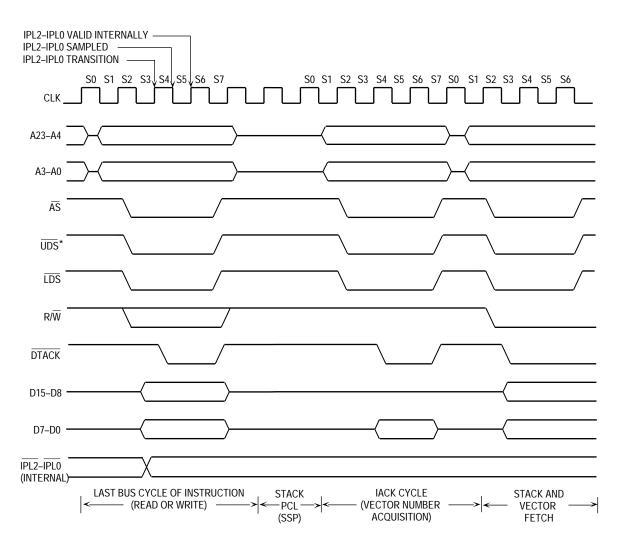

| 3.1.5 | CPU Space Cycle                    | 3-11 |

| 3.1.6 | 8-Bit M68000 Dynamically-Sized Bus | 3-11 |

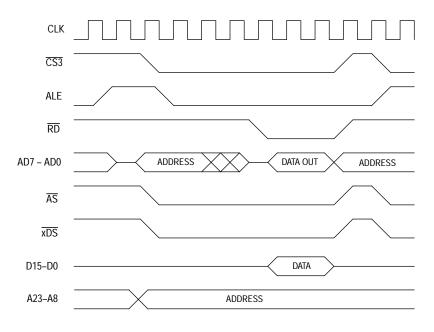

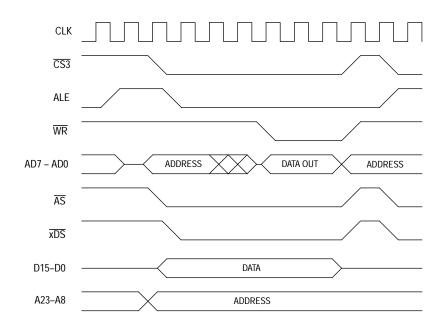

| 3.1.7 | 8051-Bus Operation                 | 3-13 |

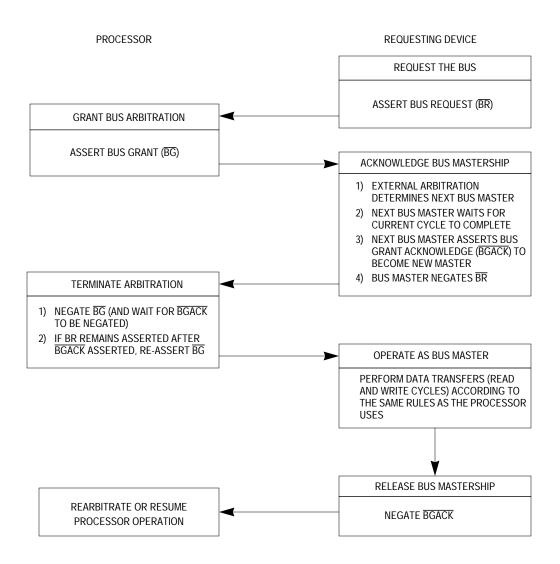

| 3.2   | Bus Arbitration                    | 3-15 |

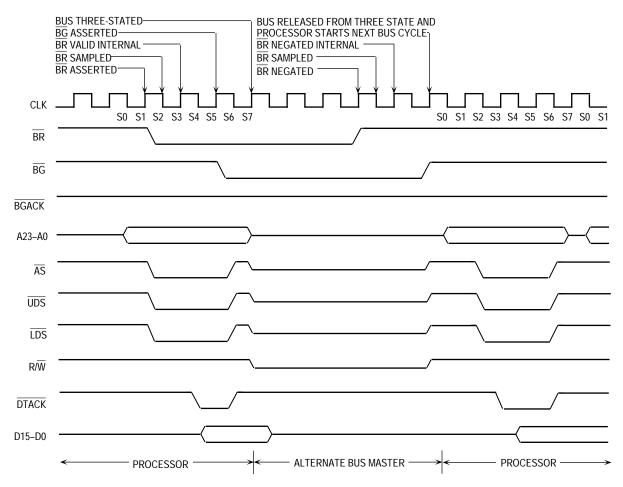

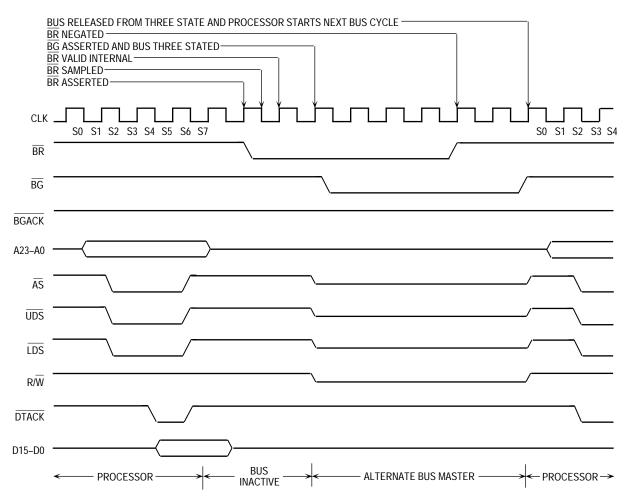

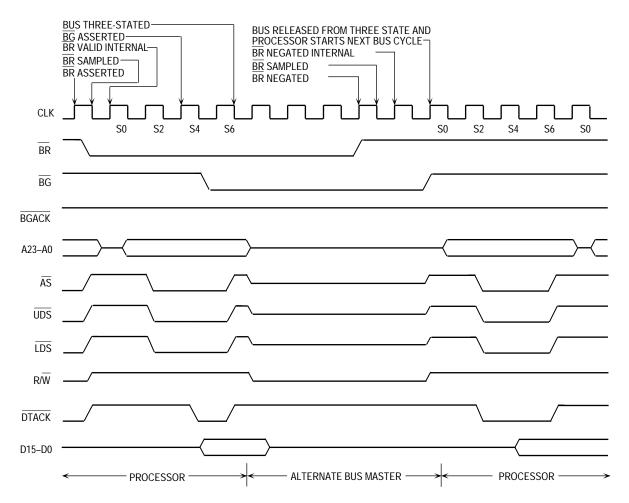

| 3.2.1 | Requesting the Bus                 | 3-17 |

| Receiving the Bus Grant                                        | 3-18                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Acknowledgment of Mastership (Three-Wire Bus Arbitration Only) | 3-18                                                                                                                                                                                                                                                          |

| Bus Arbitration Control                                        | 3-19                                                                                                                                                                                                                                                          |

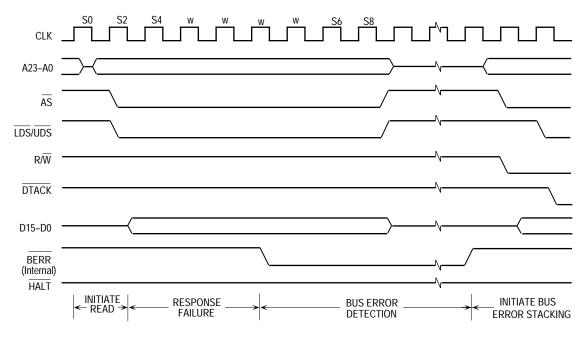

| Bus Error And Halt Operation                                   | 3-27                                                                                                                                                                                                                                                          |

| Bus Error Operation                                            | 3-27                                                                                                                                                                                                                                                          |

| Retrying the Bus Cycle                                         | 3-29                                                                                                                                                                                                                                                          |

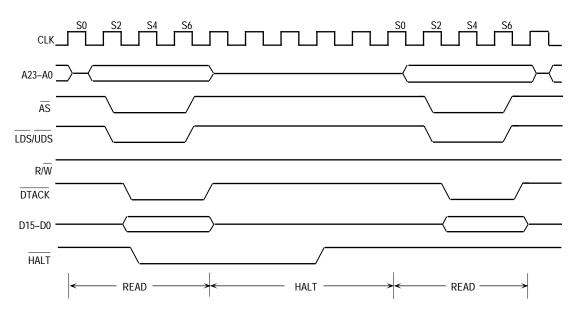

| Halt Operation                                                 | 3-30                                                                                                                                                                                                                                                          |

| Double Bus Fault                                               | 3-31                                                                                                                                                                                                                                                          |

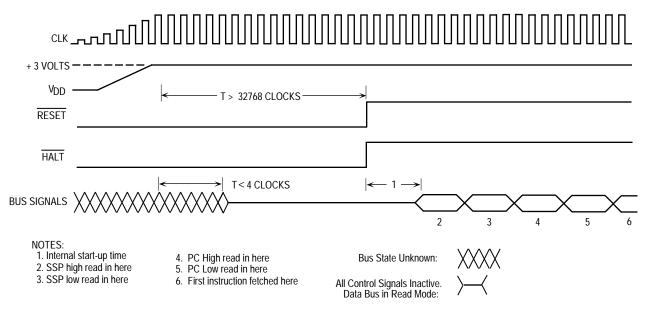

| Reset Operation                                                | 3-31                                                                                                                                                                                                                                                          |

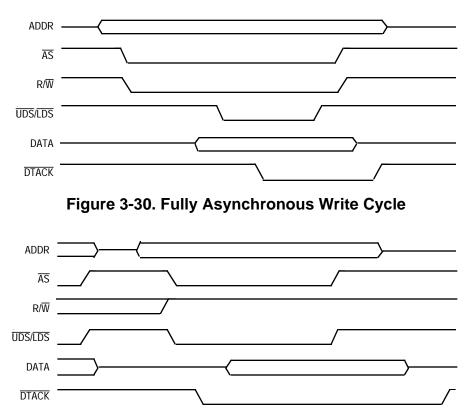

| Asynchronous Operation                                         | 3-32                                                                                                                                                                                                                                                          |

| Synchronous Operation                                          | 3-35                                                                                                                                                                                                                                                          |

|                                                                | Acknowledgment of Mastership (Three-Wire Bus Arbitration Only)<br>Bus Arbitration Control<br>Bus Error And Halt Operation<br>Bus Error Operation<br>Retrying the Bus Cycle<br>Halt Operation<br>Double Bus Fault<br>Reset Operation<br>Asynchronous Operation |

#### Section 4 EC000 Core Processor

| 4.1    | Features                               |  |

|--------|----------------------------------------|--|

| 4.2    | Processing States                      |  |

| 4.3    | Programming Model                      |  |

| 4.3.1  | Data Format Summary                    |  |

| 4.3.2  | Addressing Capabilities Summary        |  |

| 4.3.3  | Notation Conventions                   |  |

| 4.4    | EC000 Core Instruction Set Overview    |  |

| 4.5    | Exception Processing                   |  |

| 4.5.1  | Exception Vectors                      |  |

| 4.6    | Processing of Specific Exceptions      |  |

| 4.6.1  | Reset Exception                        |  |

| 4.6.2  | Interrupt Exceptions                   |  |

| 4.6.3  | Uninitialized Interrupt Exception      |  |

| 4.6.4  | Spurious Interrupt Exception           |  |

| 4.6.5  | Instruction Traps                      |  |

| 4.6.6  | Illegal and Unimplemented Instructions |  |

| 4.6.7  | Privilege Violations                   |  |

| 4.6.8  | Tracing                                |  |

| 4.6.9  | Bus Error                              |  |

| 4.6.10 | Address Error                          |  |

| 4.6.11 | Multiple Exceptions                    |  |

|        |                                        |  |

#### Section 5 System Integration Module

| 5.1     | Module Operation                       | 5-2 |

|---------|----------------------------------------|-----|

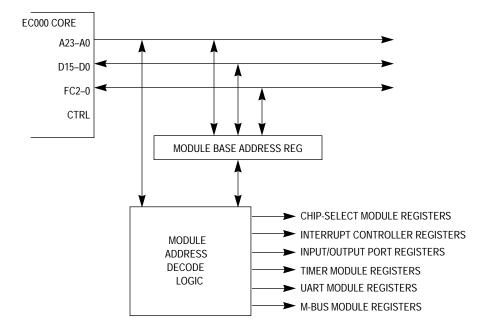

| 5.1.1   | MC68307 System Configuration           |     |

| 5.1.1.1 | Module Base Address Register Operation |     |

| 5.1.1.2 | System Control Register Functions      |     |

| 5.1.1.3 | System Protection Functions            | 5-5 |

| 5.1.2   | Chip Select and Wait-State Logic       | 5-5 |

| 5.1.2.1 | Programmable Data-Bus Size             |     |

| 5.1.2.2 | Peripheral Chip Selects                               | 5-7  |

|---------|-------------------------------------------------------|------|

| 5.1.2.3 | 8051-Compatible Bus Chip Select                       |      |

| 5.1.2.4 | Global Chip Select Operation (Reset Defaults)         |      |

| 5.1.2.5 | Overlap in Chip Select Ranges                         |      |

| 5.1.3   | External Bus Interface Logic                          |      |

| 5.1.3.1 | M68000 Bus Interface                                  | 5-9  |

| 5.1.3.2 | 8051-Compatible Bus Interface                         | 5-10 |

| 5.1.3.3 | Port A, Port B General-Purpose I/O Ports              | 5-10 |

| 5.1.4   | Interrupt Processing                                  |      |

| 5.1.4.1 | Interrupt Controller Logic                            | 5-14 |

| 5.1.4.2 | Interrupt Vector Generation                           |      |

| 5.1.4.3 | IRQ7 Non-Maskable Interrupt                           |      |

| 5.1.4.4 | General-Purpose Interrupt Inputs                      | 5-17 |

| 5.1.4.5 | Peripheral Interrupt Handling                         | 5-18 |

| 5.1.5   | Low-Power Sleep Logic                                 | 5-19 |

| 5.2     | Programming Model                                     | 5-20 |

| 5.2.1   | System Configuration and Protection Registers         |      |

| 5.2.1.1 | Module Base Address Register (MBAR)                   | 5-22 |

| 5.2.1.2 | System Control Register (SCR)                         |      |

| 5.2.1.3 | System Status Register Bits Description               | 5-23 |

| 5.2.1.4 | System Control Register Bits Description.             |      |

| 5.2.2   | Chip Select Registers                                 |      |

| 5.2.2.1 | Base Registers (BR3–BR0)                              | 5-30 |

| 5.2.2.2 | Option Registers (OR3–OR0)                            | 5-32 |

| 5.2.3   | External Bus Interface Control Registers              |      |

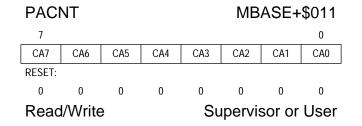

| 5.2.3.1 | Port A Control Register (PACNT)                       |      |

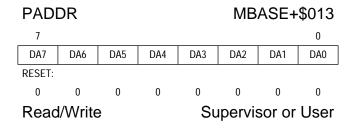

| 5.2.3.2 | Port A Data Direction Register (PADDR)                |      |

| 5.2.3.3 | Port A Data Register (PADAT)                          |      |

| 5.2.3.4 | Port B Control Register (PBCNT)                       | 5-36 |

| 5.2.3.5 | Port B Data Direction Register (PBDDR)                |      |

| 5.2.3.6 | Port B Data Register (PBDAT)                          |      |

| 5.2.4   | Interrupt Control Registers                           |      |

| 5.2.4.1 | Latched Interrupt Control Registers 1,2 (LICR1,LICR2) |      |

| 5.2.4.2 | Peripheral Interrupt Control Register (PICR)          |      |

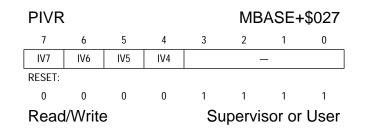

| 5.2.4.3 | Programmable Interrupt Vector Register (PIVR)         |      |

| 5.3     | MC68307 Initialization Procedure                      |      |

| 5.3.1   | Startup—Cold Reset                                    |      |

| 5.3.2   | SIM Configuration                                     | 5-41 |

#### Section 6 Dual Timer Module

| 6.1   | Overview                    | 6-1 |

|-------|-----------------------------|-----|

| 6.2   | Module Operation            | 6-1 |

| 6.2.1 | General-Purpose Timer Units |     |

| 6.2.2 | Software Watchdog Timer     | 6-3 |

| 6.3     | Programming Model                             | 6-4 |

|---------|-----------------------------------------------|-----|

| 6.3.1   | General Purpose Timer Units                   |     |

| 6.3.1.1 | Timer Mode Register (TMR1, TMR2)              |     |

| 6.3.1.2 | Timer Reference Registers (TRR1, TRR2)        | 6-5 |

| 6.3.1.3 | Timer Capture Registers (TCR1, TCR2)          | 6-5 |

| 6.3.1.4 | Timer Counter (TCN1, TCN2)                    | 6-5 |

| 6.3.1.5 | Timer Event Registers (TER1, TER2)            | 6-6 |

| 6.3.2   | Software Watchdog Timer                       | 6-7 |

| 6.3.2.1 | Watchdog Reference Register (WRR)             | 6-7 |

| 6.3.2.2 | Watchdog Counter Register (WCR)               | 6-7 |

| 6.4     | Timer Programming Examples                    | 6-8 |

| 6.4.1   | Initialization and Reference Compare Function | 6-8 |

| 6.4.2   | Event Counting Function and Interrupts        | 6-9 |

| 6.4.3   | Input Capture Function                        | 6-9 |

| 6.4.4   | Watchdog Usage Example                        |     |

#### Section 7 M-Bus Interface Module

| 7.1   | M-Bus System Configuration              | 7-2  |

|-------|-----------------------------------------|------|

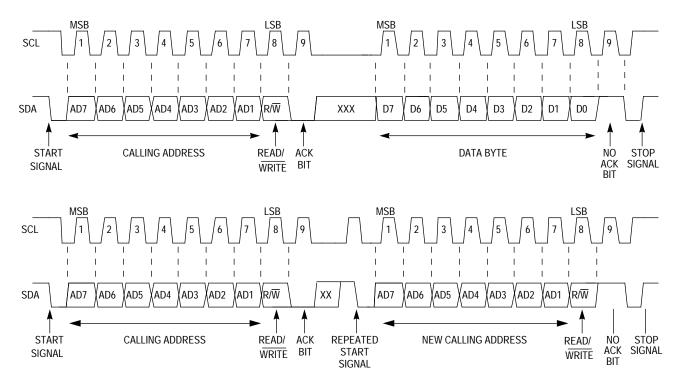

| 7.2   | M-Bus Protocol                          |      |

| 7.2.1 | START Signal                            | 7-3  |

| 7.2.2 | Slave Address Transmission              | 7-3  |

| 7.2.3 | Data Transfer                           | 7-3  |

| 7.2.4 | Repeated START Signal                   | 7-4  |

| 7.2.5 | STOP Signal                             | 7-4  |

| 7.2.6 | Arbitration Procedure                   | 7-4  |

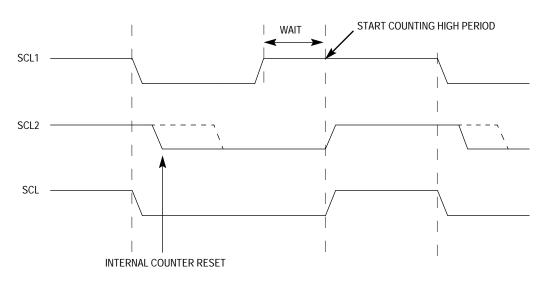

| 7.2.7 | Clock Synchronization                   | 7-4  |

| 7.2.8 | Handshaking                             | 7-5  |

| 7.2.9 | Clock Stretching                        | 7-5  |

| 7.3   | Programming Model                       | 7-5  |

| 7.3.1 | M-Bus Address Register (MADR)           | 7-6  |

| 7.3.2 | M-Bus Frequency Divider Register (MFDR) | 7-6  |

| 7.3.3 | M-Bus Control Register (MBCR)           | 7-7  |

| 7.3.4 | M-Bus Status Register (MBSR)            | 7-9  |

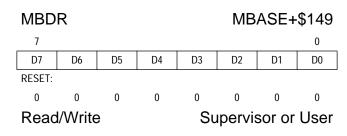

| 7.3.5 | M-Bus Data I/O Register (MBDR)          | 7-10 |

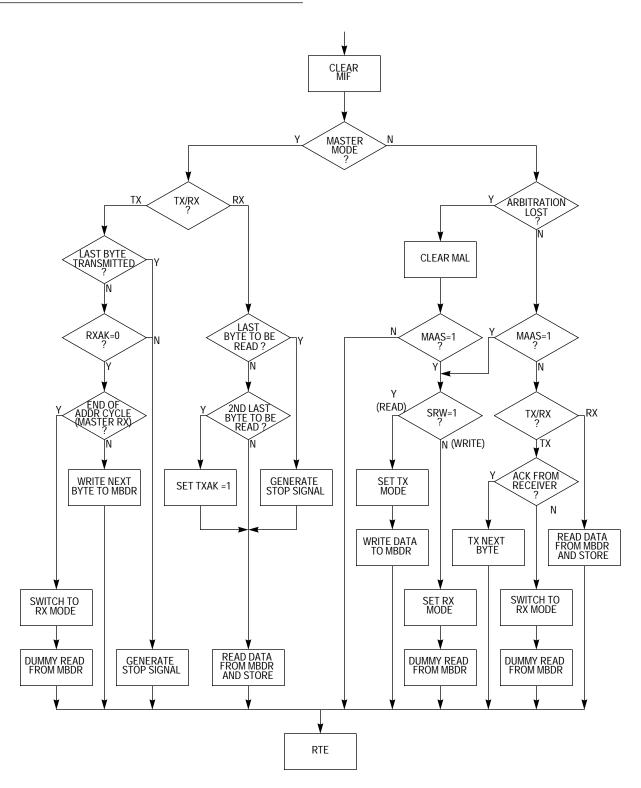

| 7.4   | M-Bus Programming Examples              | 7-10 |

| 7.4.1 | Initialization Sequence                 | 7-10 |

| 7.4.2 | Generation of START                     | 7-11 |

| 7.4.3 | Post-Transfer Software Response         | 7-11 |

| 7.4.4 | Generation of STOP                      | 7-12 |

| 7.4.5 | Generation of Repeated START            | 7-13 |

| 7.4.6 | Slave Mode                              | 7-13 |

| 7.4.7 | Arbitration Lost                        | 7-13 |

#### Section 8 Serial Module

| 8.1      | Module Overview                          | 8-2  |

|----------|------------------------------------------|------|

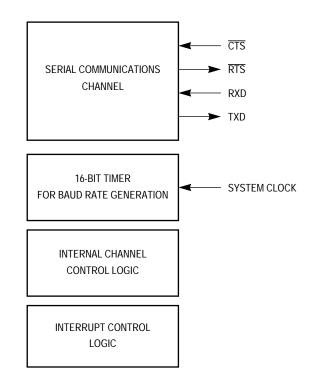

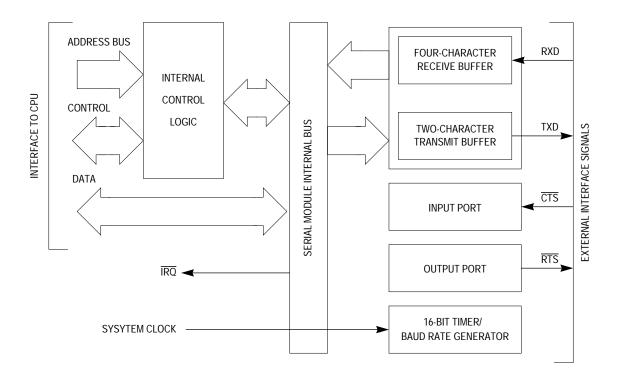

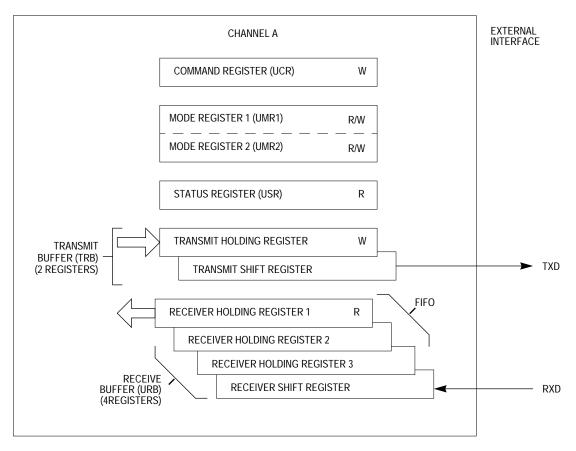

| 8.1.1    | Serial Communication Channel             | 8-2  |

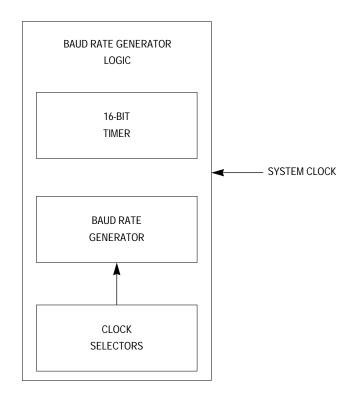

| 8.1.2    | Baud Rate Generator Logic                | 8-3  |

| 8.1.3    | Baud Rate Generator/Timer                | 8-3  |

| 8.1.4    | Interrupt Control Logic                  | 8-3  |

| 8.1.5    | Comparison of Serial Module to MC68681   | 8-3  |

| 8.2      | Serial Module Signal Definitions         |      |

| 8.2.1    | Transmitter Serial Data Output (TxD)     | 8-4  |

| 8.2.2    | Receiver Serial Data Input (RxD)         |      |

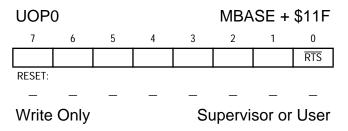

| 8.2.3    | Request-To-Send (RTS)                    | 8-4  |

| 8.2.4    | Clear-To-Send (CTS)                      |      |

| 8.3      | Operation                                |      |

| 8.3.1    | Baud Rate Generator/Timer                |      |

| 8.3.2    | Transmitter and Receiver Operating Modes | 8-5  |

| 8.3.2.1  | Transmitter                              |      |

| 8.3.2.2  | Receiver                                 | 8-8  |

| 8.3.2.3  | FIFO Stack                               | 8-8  |

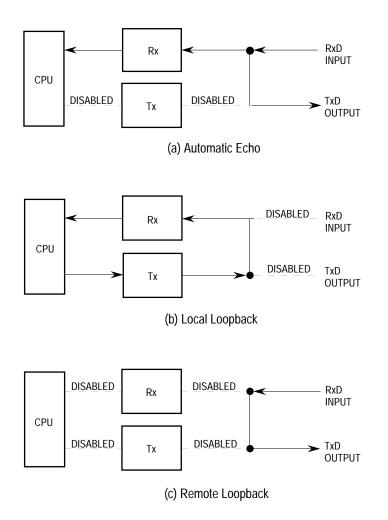

| 8.3.3    | Looping Modes                            | 8-10 |

| 8.3.3.1  | Automatic Echo Mode                      |      |

| 8.3.3.2  | Local Loopback Mode                      | 8-11 |

| 8.3.3.3  | Remote Loopback Mode                     |      |

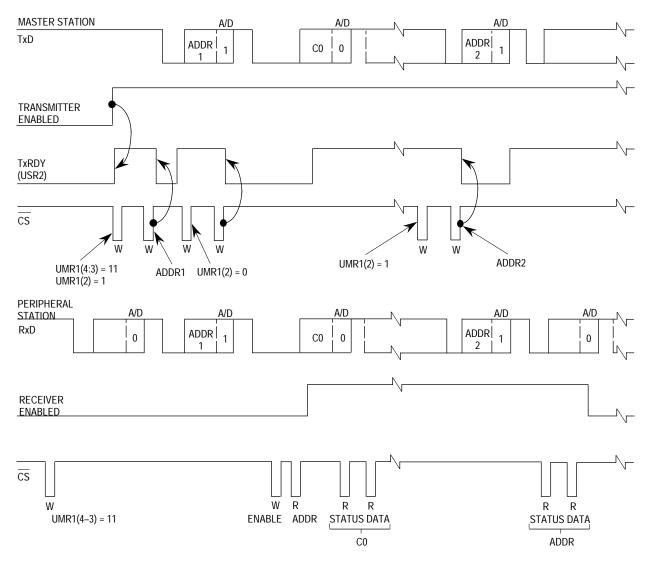

| 8.3.4    | Multidrop Mode                           | 8-12 |

| 8.3.5    | Bus Operation                            | 8-14 |

| 8.3.5.1  | Read Cycles                              | 8-14 |

| 8.3.5.2  | Write Cycles                             |      |

| 8.3.5.3  | Interrupt Acknowledge Cycles             | 8-14 |

| 8.4      | Register Description and Programming     |      |

| 8.4.1    | Register Description                     |      |

| 8.4.1.1  | Mode Register 1 (UMR1)                   | 8-15 |

| 8.4.1.2  | Mode Register 2 (UMR2)                   |      |

| 8.4.1.3  | Status Register (USR)                    |      |

| 8.4.1.4  | Clock-select Register (UCSR)             | 8-21 |

| 8.4.1.5  | Command Register (UCR)                   | 8-23 |

| 8.4.1.6  | Receiver Buffer (URB)                    | 8-25 |

| 8.4.1.7  | Transmitter Buffer (UTB)                 | 8-25 |

| 8.4.1.8  | Input Port Change Register (UIPCR)       | 8-26 |

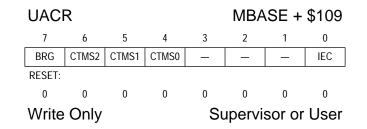

| 8.4.1.9  | Auxiliary Control Register (UACR)        | 8-26 |

| 8.4.1.10 | Interrupt Status Register (UISR)         | 8-27 |

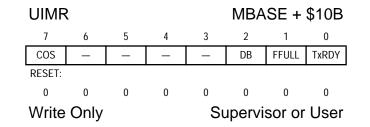

| 8.4.1.11 | Interrupt Mask Register (UIMR)           |      |

| 8.4.1.12 | Timer Upper Preload Register (UBG1)      |      |

| 8.4.1.13 | Timer Upper Preload Register (UBG2)      |      |

| 8.4.1.14 | Interrupt Vector Register (UIVR)         | 8-29 |

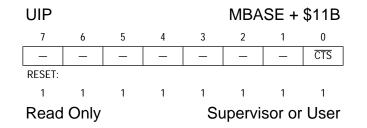

| 8.4.1.15 | Input Port Register (UIP)                |      |

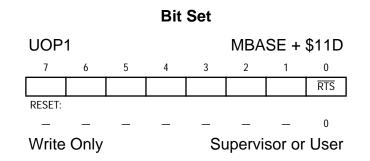

| 8.4.1.16 | Output Port Data Registers (UOP1, UOP0) |      |

|----------|-----------------------------------------|------|

| 8.4.2    | Programming                             |      |

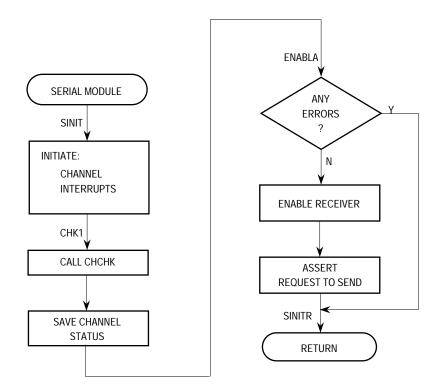

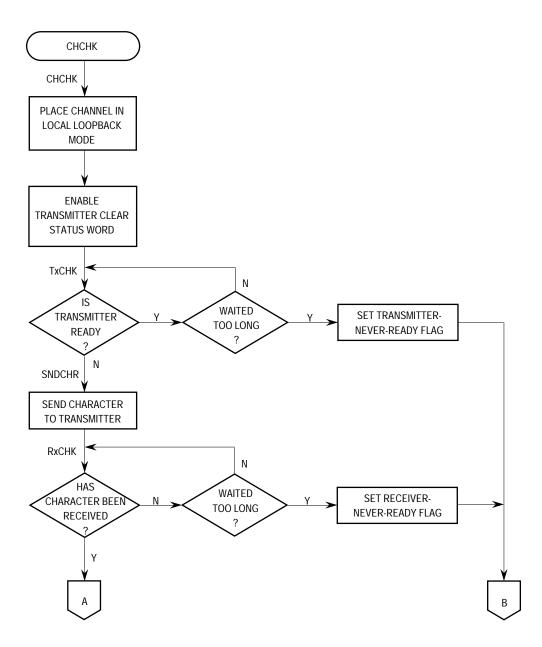

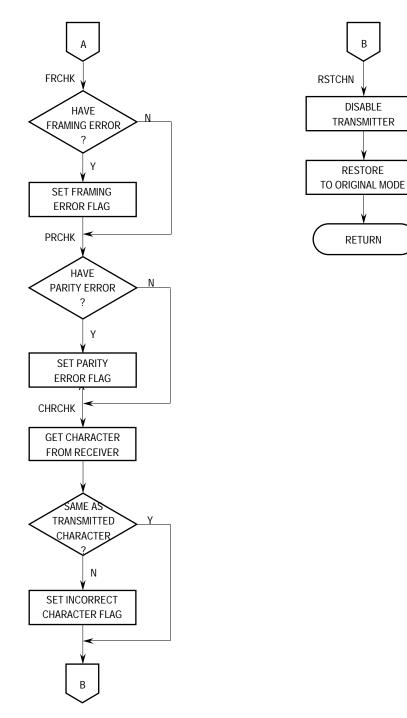

| 8.4.2.1  | Serial Module Initialization            |      |

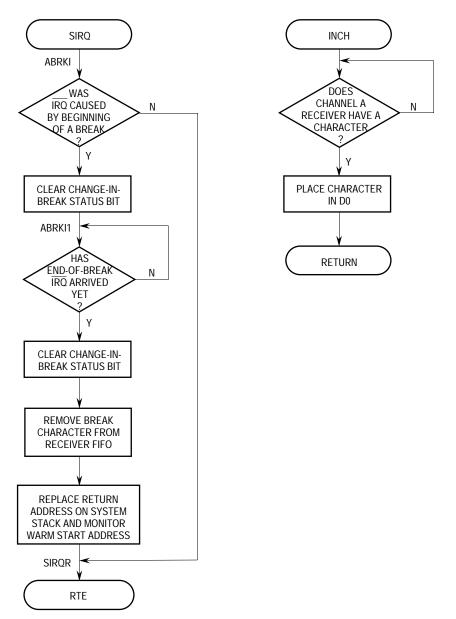

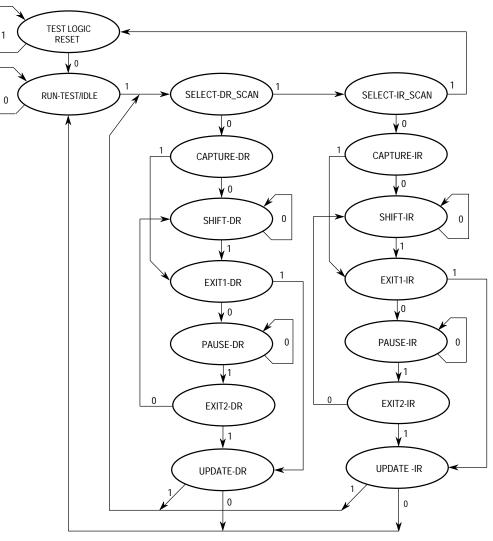

| 8.4.2.2  | I/O Driver Example                      | 8-31 |

| 8.4.2.3  | Interrupt Handling                      | 8-31 |

| 8.5      | Serial Module Initialization Sequence   | 8-31 |

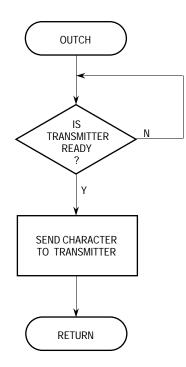

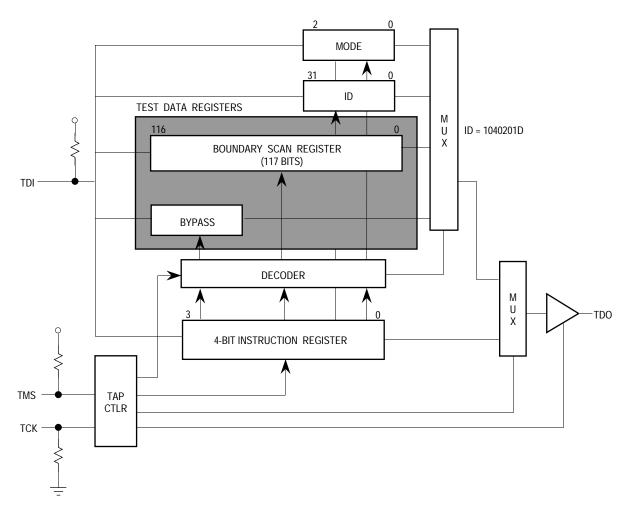

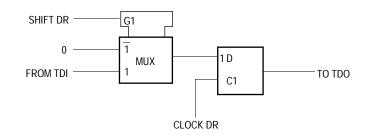

#### Section 9 IEEE 1149.1 Test Access Port

| 9.1   | Overview                  | 9-1  |

|-------|---------------------------|------|

| 9.2   | Tap Controller            | 9-3  |

| 9.3   | Boundary Scan Register    | 9-4  |

| 9.4   | Instruction Register      | 9-9  |

| 9.4.1 | EXTEST (0000)             | 9-10 |

| 9.4.2 | SAMPLE/PRELOAD (0010)     | 9-10 |

| 9.4.3 | BYPASS (1111)             | 9-10 |

| 9.4.4 | CLAMP (1100)              | 9-11 |

| 9.5   | MC68307 Restrictions      | 9-11 |

| 9.6   | Non-IEEE 1149.1 Operation | 9-11 |

#### Section 10 Applications Information

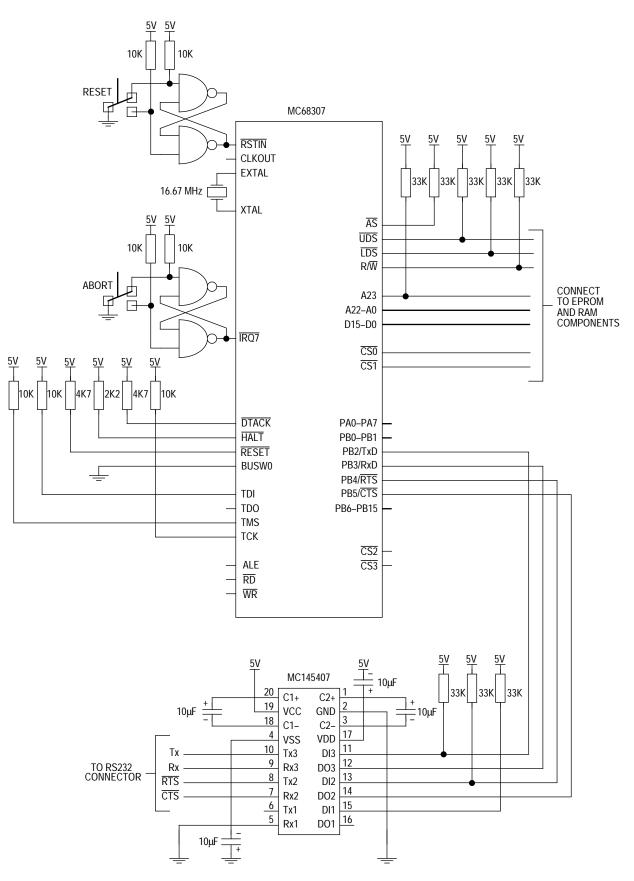

| 10.1     | MC68307 Minimum Stand-Alone System Hardware                 | 10-1      |

|----------|-------------------------------------------------------------|-----------|

| 10.1.1   | MC68307 Signal Configuration                                | 10-1      |

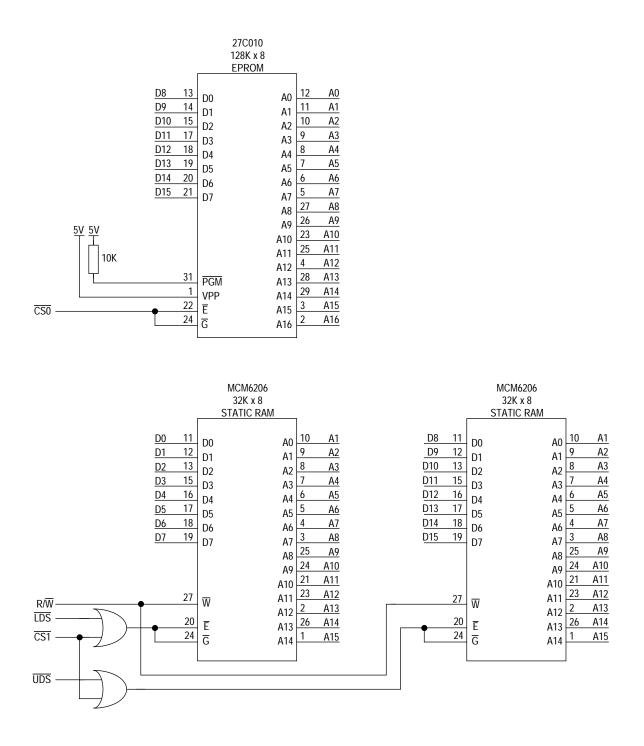

| 10.1.2   | EPROM Memory Interface                                      | 10-5      |

| 10.1.3   | RAM Memory Interface                                        | 10-5      |

| 10.1.4   | RS232 UART Port                                             | 10-5      |

| 10.1.5   | EPROM Timing                                                |           |

| 10.1.6   | RAM Timing                                                  | 10-6      |

| 10.2     | Power Management                                            |           |

| 10.2.1   | Fully Static Operation                                      |           |

| 10.2.2   | Prescalable CPU Clock                                       | 10-8      |

| 10.2.3   | Wake-Up                                                     | 10-8      |

| 10.2.4   | Low-Power Sleep Mode                                        | 10-9      |

| 10.2.5   | Low-Power Stop Mode                                         | 10-9      |

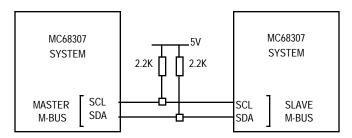

| 10.3     | Using M-Bus Software to Communicate Between Processor Syste | ems 10-10 |

| 10.3.1   | Overview of M-Bus Software Transfer Mechanism               |           |

| 10.3.2   | M-Bus Master Mode Operation                                 | 10-12     |

| 10.3.3   | M-Bus Slave Mode Operation                                  |           |

| 10.3.4   | Description of Setup                                        |           |

| 10.3.5   | Software Flow                                               |           |

| 10.3.6   | Transfer Blocks                                             |           |

| 10.3.7   | Software Implementation                                     |           |

| 10.3.7.1 | Software Listing 1—M-Bus Master Software                    | 10-17     |

| 10.3.7.2 | Software Listing 2—M-Bus Slave Software                     | 10-21     |

| 10.4     | MC68307 UART Driver Examples                |  |

|----------|---------------------------------------------|--|

| 10.4.1   | Software Listing 3                          |  |

| 10.5     | Swapping ROM and RAM Mapping on the MC68307 |  |

| 10.5.1   | Software Implementation                     |  |

| 10.5.1.1 | Software Listing 4                          |  |

#### Section 11 Electrical Characteristics

| 11.1  | Maximum Ratings                                          | 11-1  |

|-------|----------------------------------------------------------|-------|

| 11.2  | Thermal Characteristics                                  | 11-1  |

| 11.3  | Power Considerations                                     | 11-2  |

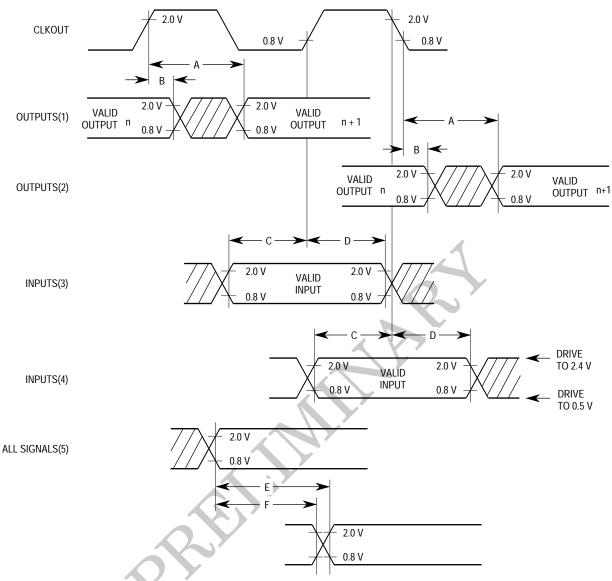

| 11.4  | AC Electrical Specification Definitions                  | 11-2  |

| 11.5  | DC Electrical Specifications                             | 11-4  |

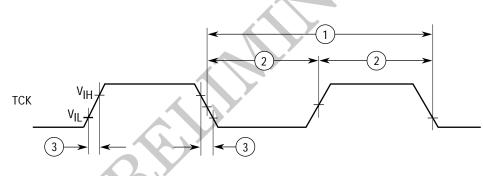

| 11.6  | AC Electrical Specifications—Clock Timing                | 11-4  |

| 11.7  | AC Electrical Specifications—Read and Write Cycles       | 11-5  |

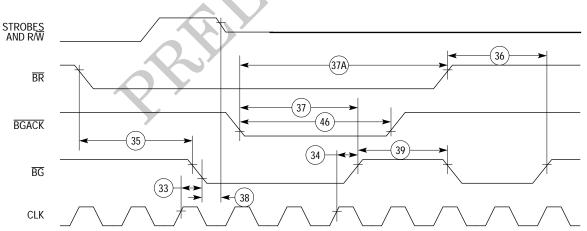

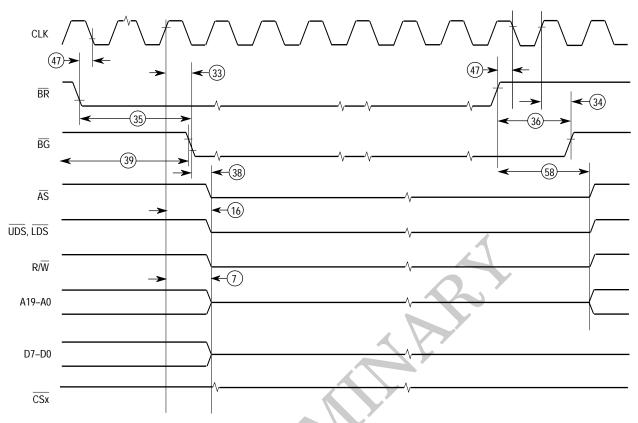

| 11.8  | AC Electrical Specifications—Bus Arbitration             | 11-9  |

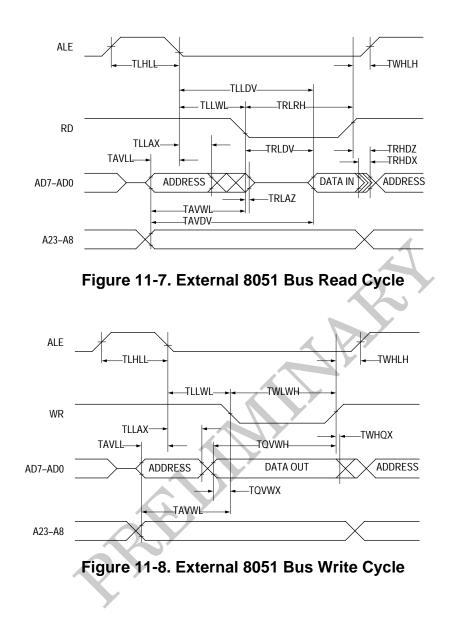

| 11.9  | AC Electrical Specifications—8051 Bus Interface Module   |       |

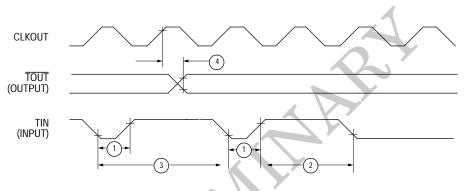

| 11.10 | Timer Module Electrical Characteristics                  | 11-13 |

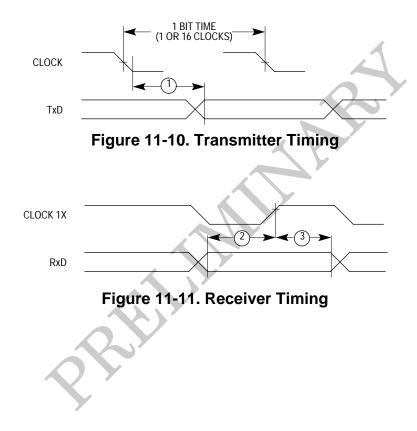

| 11.11 | UART Electrical Characteristics                          |       |

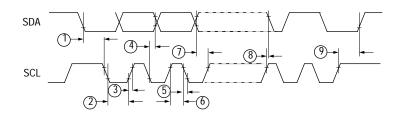

| 11.12 | AC Electrical Characteristics—M-Bus Input Signal Timing  |       |

| 11.13 | AC Electrical Characteristics—M-Bus Output Signal Timing | 11-15 |

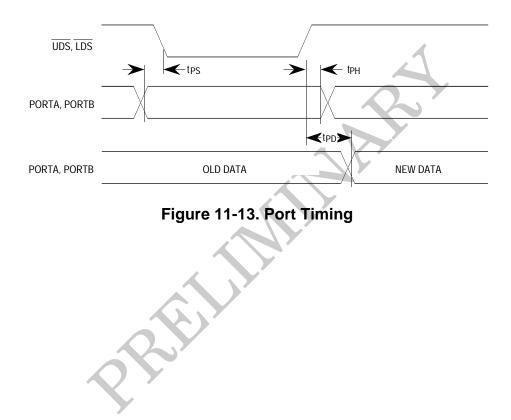

| 11.14 | AC Electrical Characteristics—Port Timing                | 11-16 |

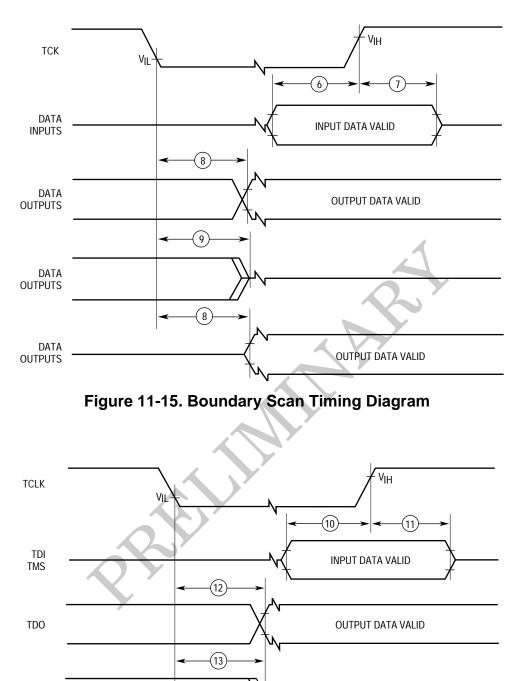

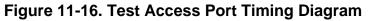

| 11.15 | IEEE 1149.1 Electrical Characteristics                   | 11-17 |

#### Section 12

#### **Ordering Information and Mechanical Data**

| 12.1 | Standard Ordering Information   |  |

|------|---------------------------------|--|

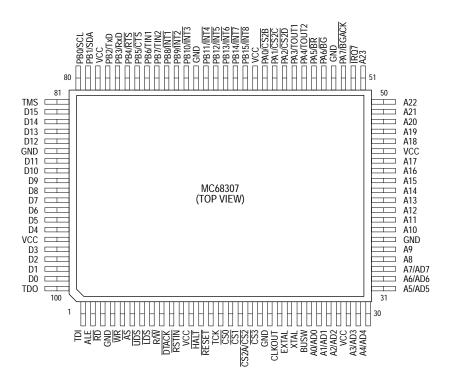

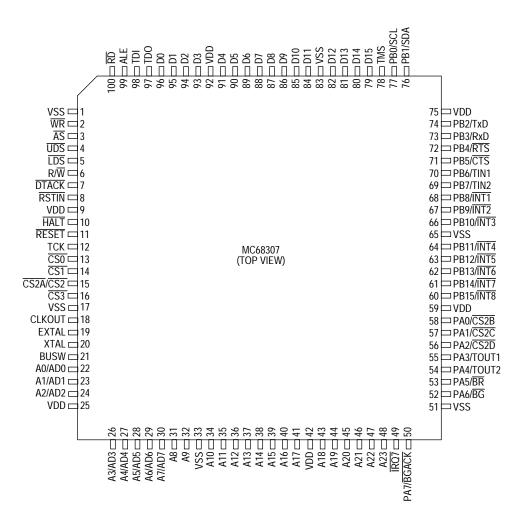

| 12.2 | 100-Pin PQFP Pin Assignments    |  |

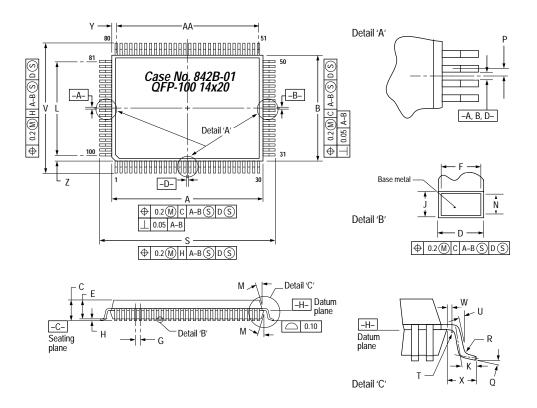

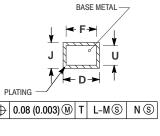

| 12.3 | 100-Pin PQFP Package Dimensions |  |

| 12.4 | 100-Pin TQFP Pin Assignments    |  |

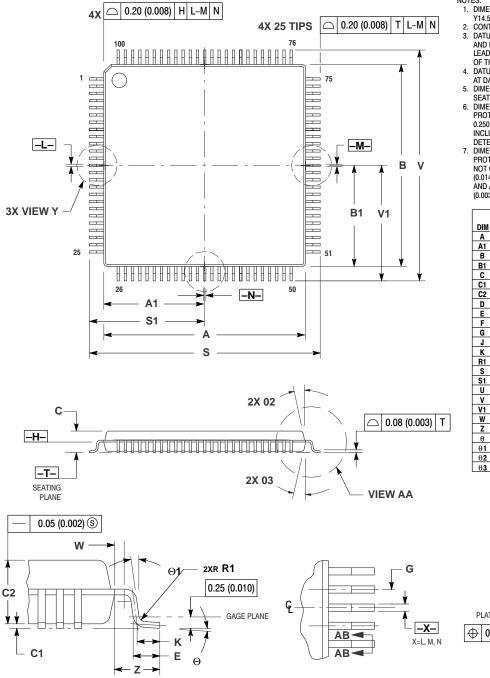

| 12.5 | 100-Pin TQFP Package Dimensions |  |

#### Index

# LIST OF ILLUSTRATIONS

| 1-1  | MC68307 Block Diagram                                      | 1-1  |

|------|------------------------------------------------------------|------|

| 2-1  | MC68307 Detailed Block Diagram                             | 2-2  |

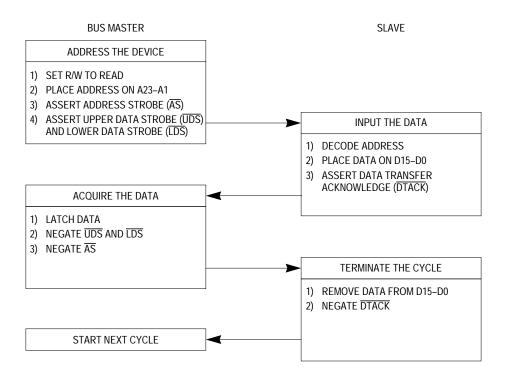

| 3-1  | Word Read Cycle Flowchart (16-Bit Bus)                     |      |

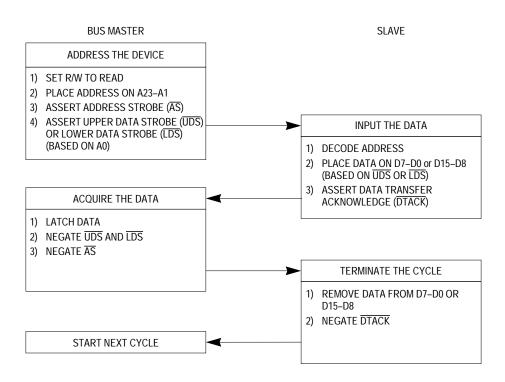

| 3-2  | Byte Read Cycle Flowchart (16-Bit Bus)                     |      |

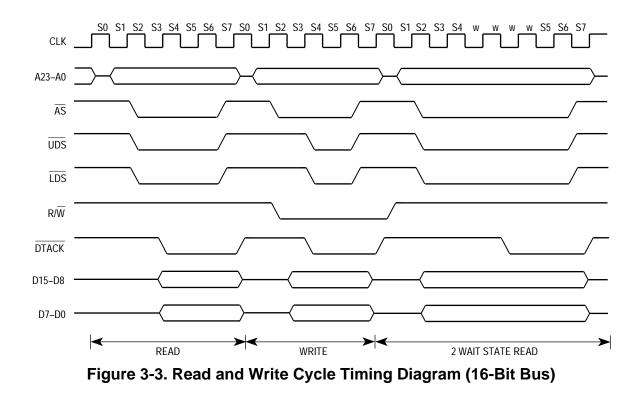

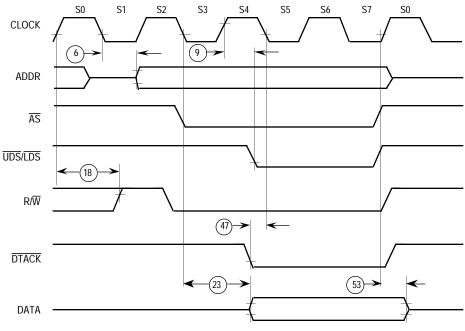

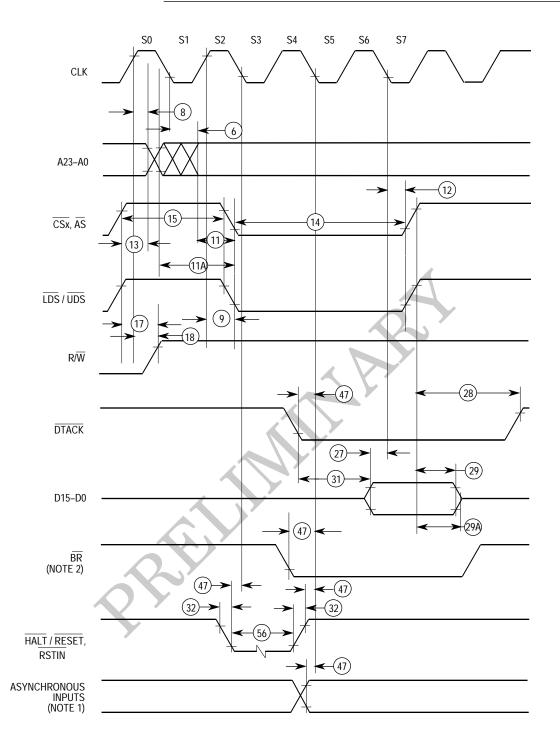

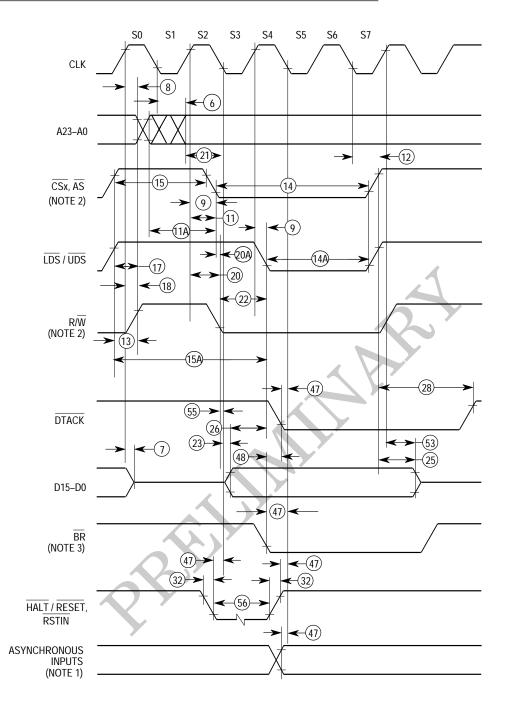

| 3-3  | Read and Write Cycle Timing Diagram (16-Bit Bus)           | 3-3  |

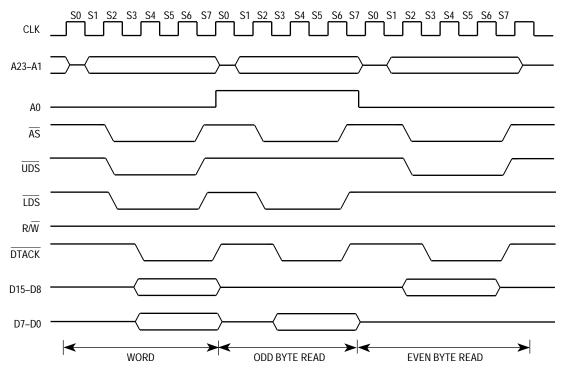

| 3-4  | Word and Byte Read Cycle Timing Diagram (16-Bit Bus)       |      |

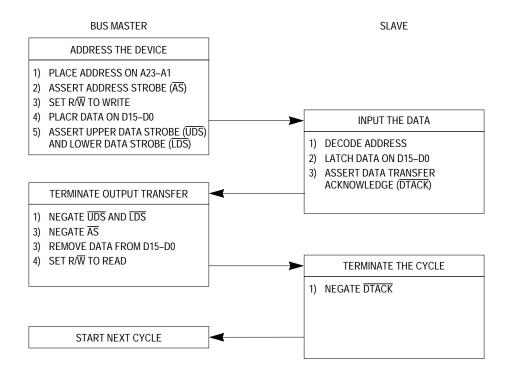

| 3-5  | Word Write Cycle Flowchart (16-Bit Bus)                    |      |

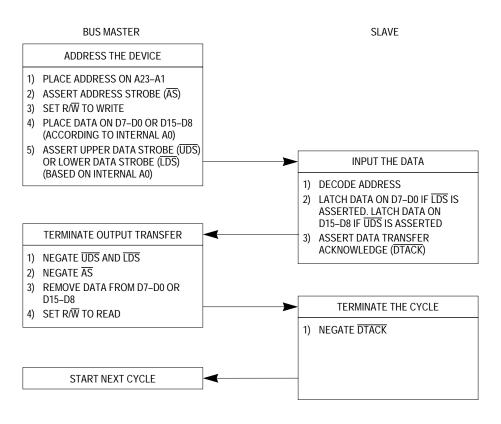

| 3-6  | Byte Write Cycle Flowchart (16-Bit Bus)                    |      |

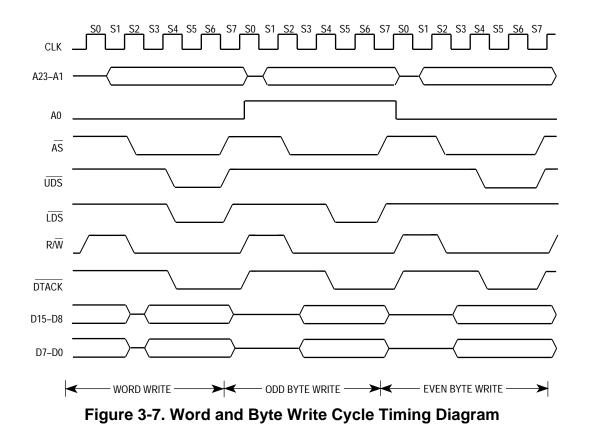

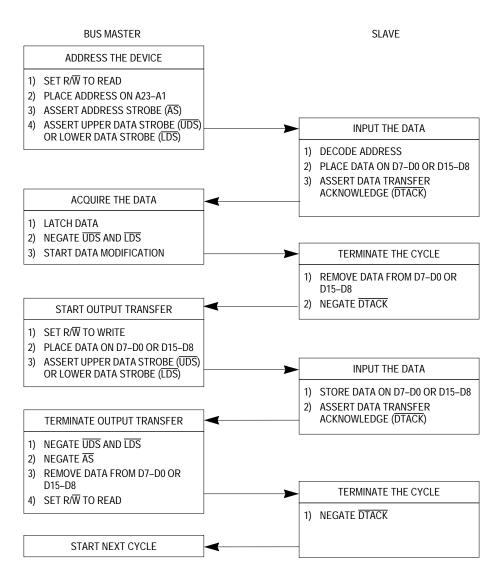

| 3-7  | Word and Byte Write Cycle Timing Diagram                   |      |

| 3-8  | Read-Modify-Write Cycle Flowchart                          | 3-8  |

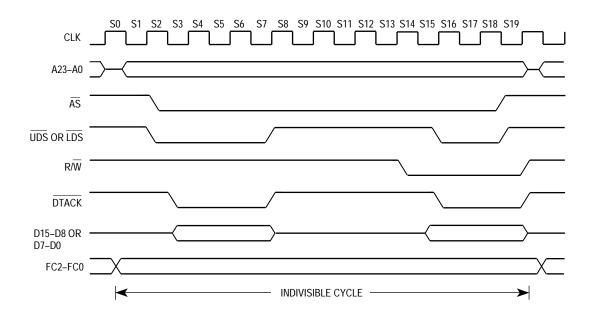

| 3-9  | Read-Modify-Write Cycle Timing Diagram                     | 3-9  |

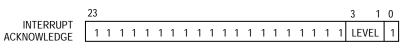

| 3-10 | Interrupt Acknowledge Cycle – Address Bus                  |      |

| 3-11 | Interrupt Acknowledge Cycle Timing Diagram                 | 3-12 |

| 3-12 | 8051-Compatible Read Cycle Signals                         |      |

| 3-13 | 8051-Compatible Write Cycle Signals                        | 3-14 |

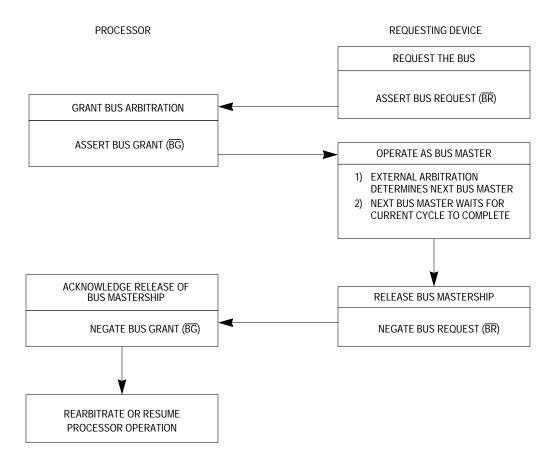

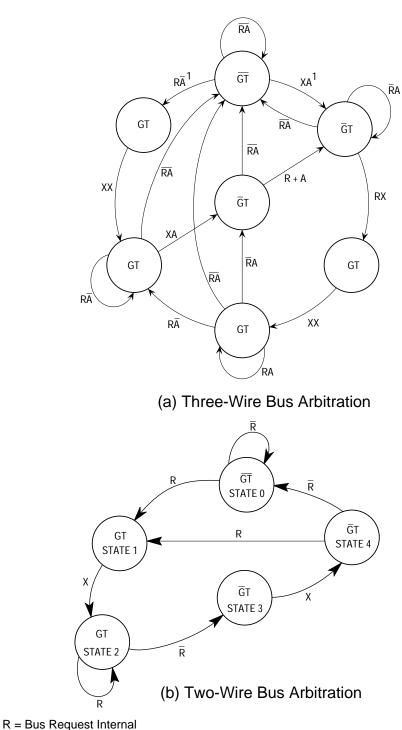

| 3-14 | Three-Wire Bus Arbitration Cycle Flowchart                 | 3-15 |

| 3-15 | Two-Wire Bus Arbitration Cycle Flowchart                   | 3-16 |

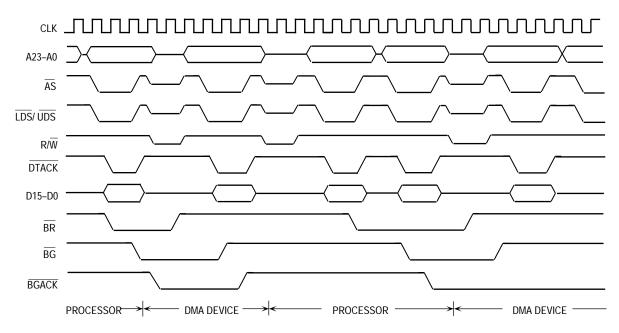

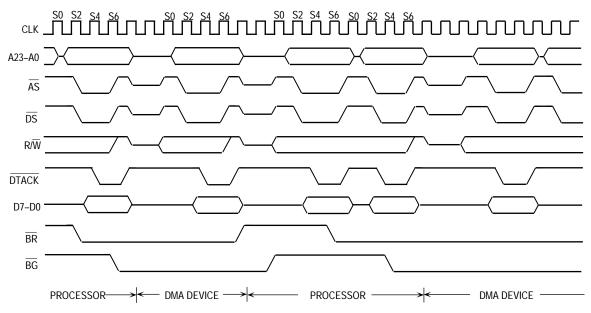

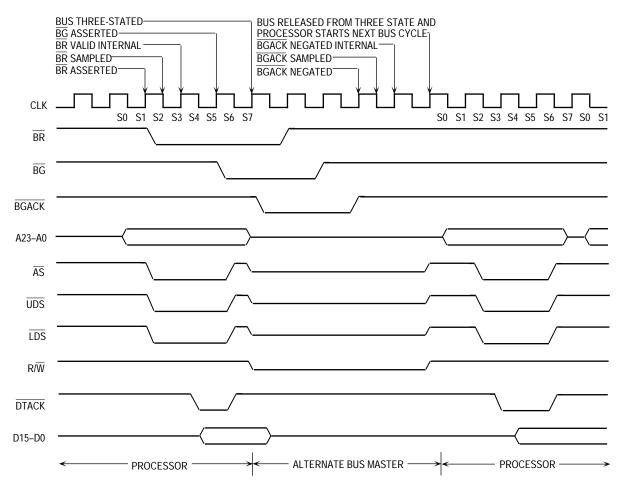

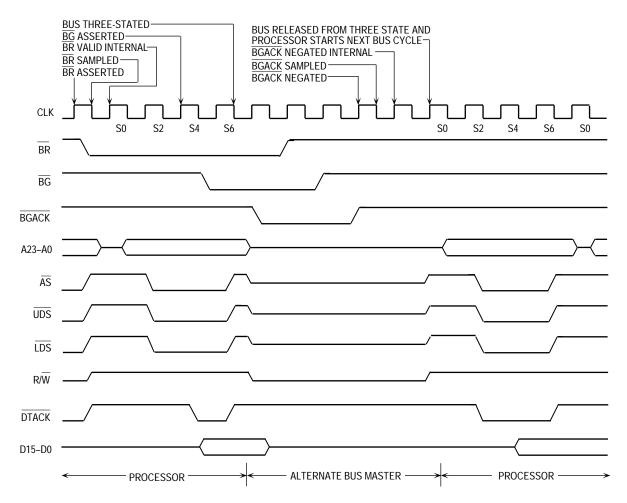

| 3-16 | Three-Wire Bus Arbitration Timing Diagram                  | 3-17 |

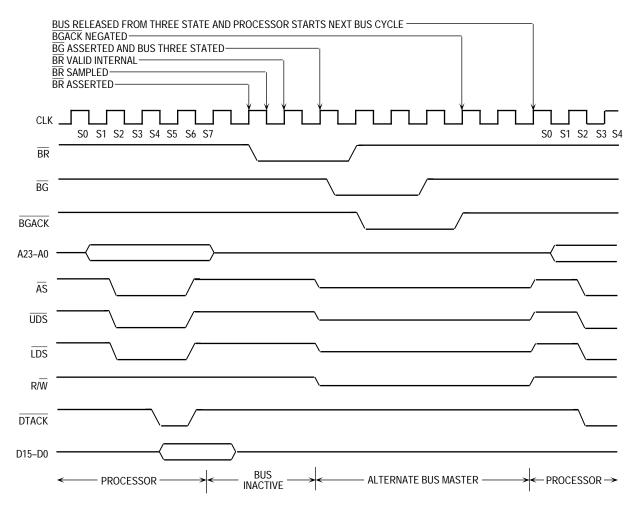

| 3-17 | Two-Wire Bus Arbitration Timing Diagram                    | 3-17 |

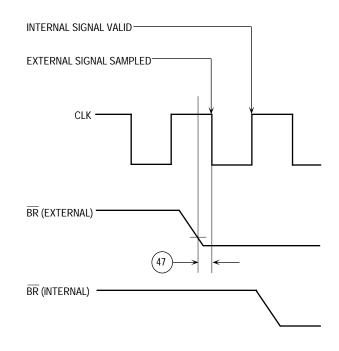

| 3-18 | External Asynchronous Signal Synchronization               | 3-19 |

| 3-19 | Bus Arbitration Unit State Diagrams                        |      |

| 3-20 | Three-Wire Bus Arbitration Timing Diagram—Processor Active | 3-21 |

| 3-21 | Three-Wire Bus Arbitration Timing Diagram—Bus Inactive     |      |

| 3-22 | Three-Wire Bus Arbitration Timing Diagram—Special Case     |      |

| 3-23 | Two-Wire Bus Arbitration Timing Diagram—Processor Active   |      |

| 3-24 | Two-Wire Bus Arbitration Timing Diagram—Bus Inactive       |      |

| 3-25 | Two-Wire Bus Arbitration Timing Diagram—Special Case       |      |

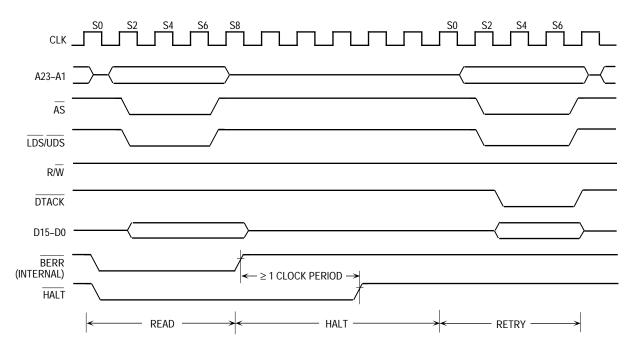

| 3-26 | Bus Error Timing Diagram                                   |      |

| 3-27 | Retry Bus Cycle Timing Diagram                             |      |

| 3-28 | Halt Operation Timing Diagram                              |      |

| 3-29 | Reset Operation Timing Diagram                             |      |

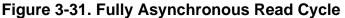

| 3-30 | Fully Asynchronous Read Cycle                              | 3-33 |

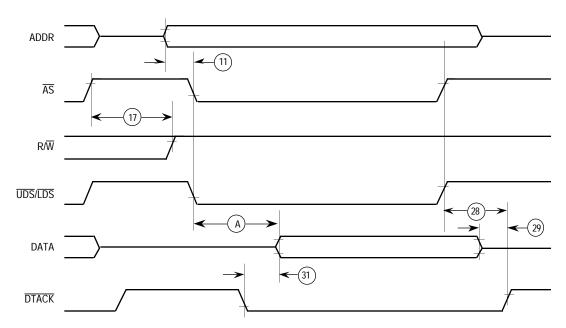

| 3-31 | Fully Asynchronous Write Cycle                             | 3-33 |

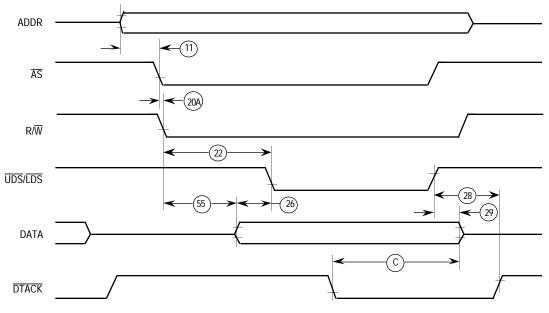

| 3-32 | Pseudo-Asynchronous Write Cycle                            | 3-34 |

| 3-33 | Pseudo-Asynchronous Read Cycle                             | 3-34 |

| 3-34 | Synchronous Read Cycle                                     | 3-37 |

| 3-35 | Synchronous Write Cycle                                    |      |

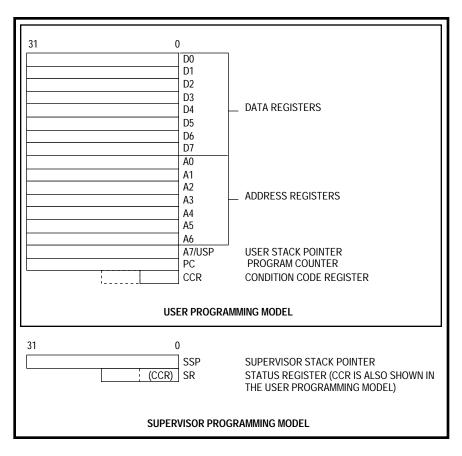

| 4-1  | Programming Model                                          |      |

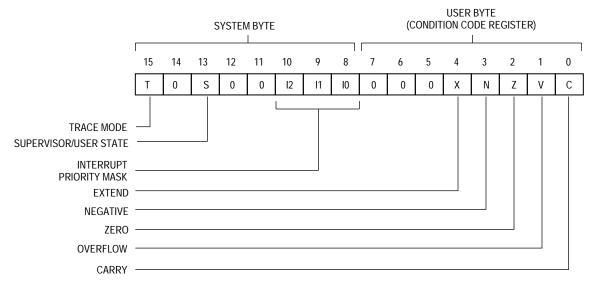

| 4-2  | Status Register                                            |      |

---- -

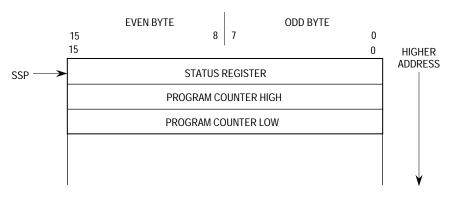

| 4-3  | General Form of Exception Stack Frame                       | 4-10  |

|------|-------------------------------------------------------------|-------|

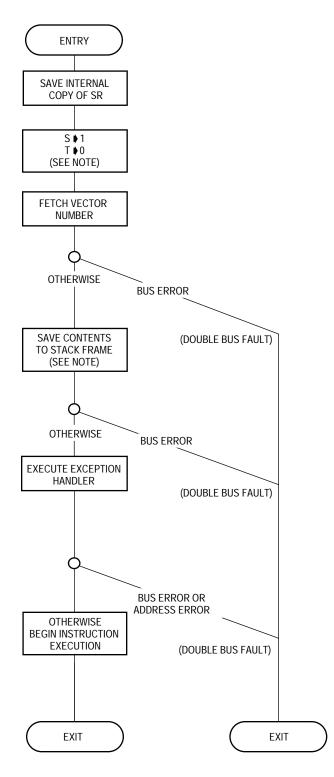

| 4-4  | General Exception Processing Flowchart                      | 4-11  |

| 4-5  | Exception Vector Format                                     |       |

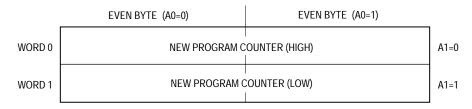

| 4-6  | Address Translated from 8-Bit Vector Number                 | 4-12  |

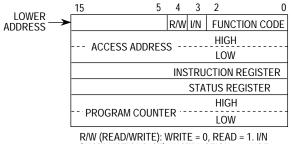

| 4-7  | Supervisor Stack Order for Bus or Address Error Exception   | 4-19  |

| 5-1  | Module Base Address, Decode Logic                           | 5-3   |

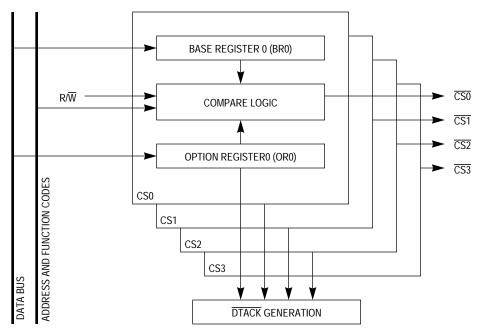

| 5-2  | Chip-Select Block Diagram                                   | 5-6   |

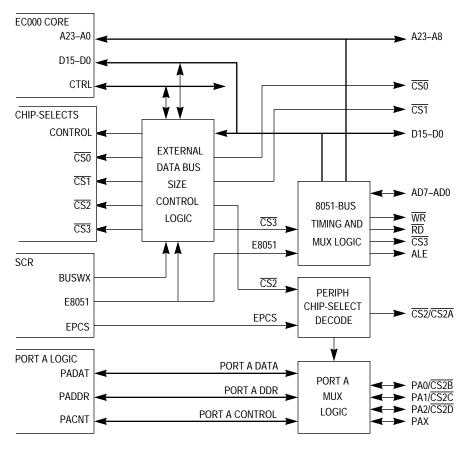

| 5-3  | External Bus Interface Logic                                | 5-9   |

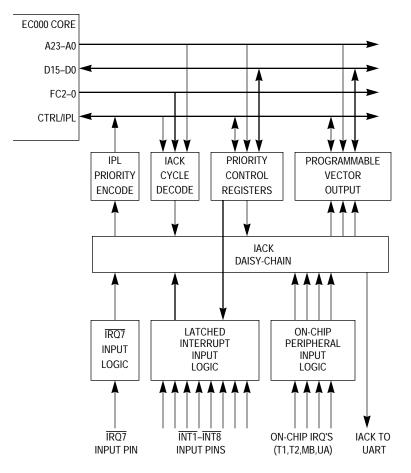

| 5-4  | Interrupt Controller Logic Block Diagram                    | 5-15  |

| 6-1  | Timer Block Diagram                                         |       |

| 7-1  | M-Bus Interface Block Diagram                               | 7-2   |

| 7-2  | M-Bus Transmission Signals                                  |       |

| 7-3  | M-Bus Clock Synchronization                                 | 7-5   |

| 7-4  | Flow-Chart of Typical M-Bus Interrupt Routine               | 7-14  |

| 8-1  | Simplified Block Diagram                                    |       |

| 8-2  | External and Internal Interface Signals                     |       |

| 8-3  | Baud Rate Generator Block Diagram                           |       |

| 8-4  | Transmitter and Receiver Functional Diagram                 |       |

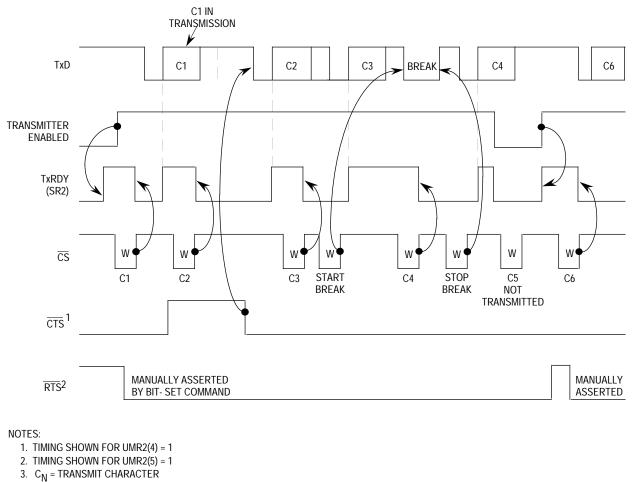

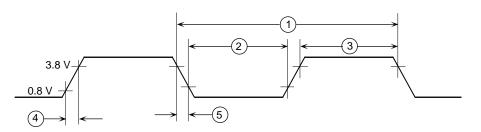

| 8-5  | Transmitter Timing Diagram                                  |       |

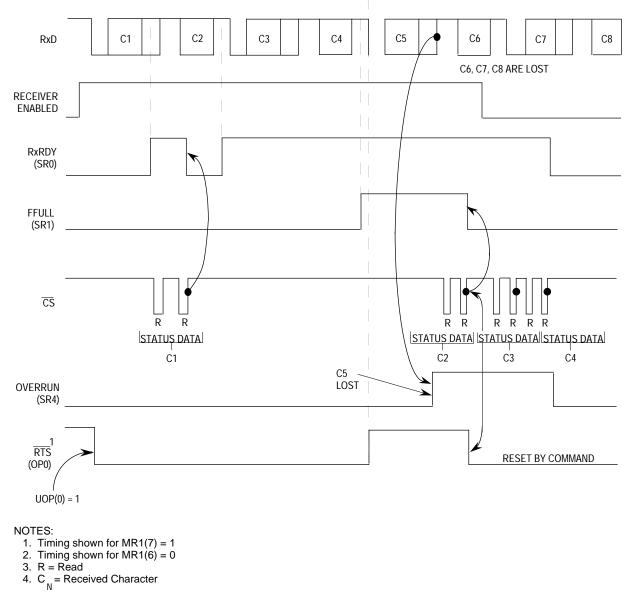

| 8-6  | Receiver Timing Diagram                                     |       |

| 8-7  | Looping Modes Functional Diagram                            |       |

| 8-8  | Multidrop Mode Timing Diagram                               |       |

| 8-9  | Serial Mode Programming Flowchart                           |       |

| 9-1  | Test Access Port Block Diagram                              |       |

| 9-2  | TAP Controller State Machine                                |       |

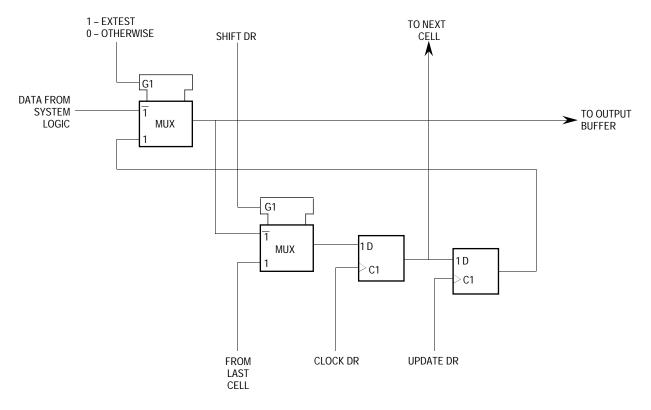

| 9-3  | Output Cell (O.Cell)                                        |       |

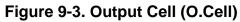

| 9-4  | Input Cell (I.Cell)                                         |       |

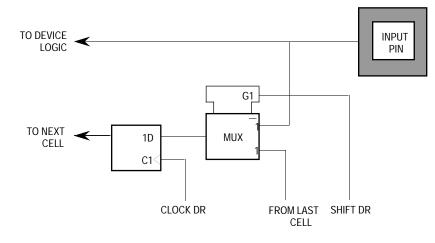

| 9-5  | Output Control Cell (En.Cell)                               |       |

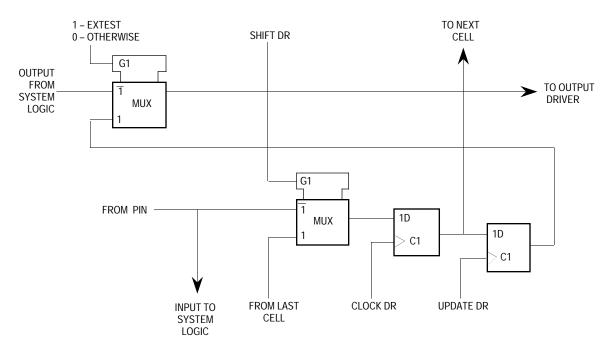

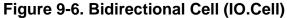

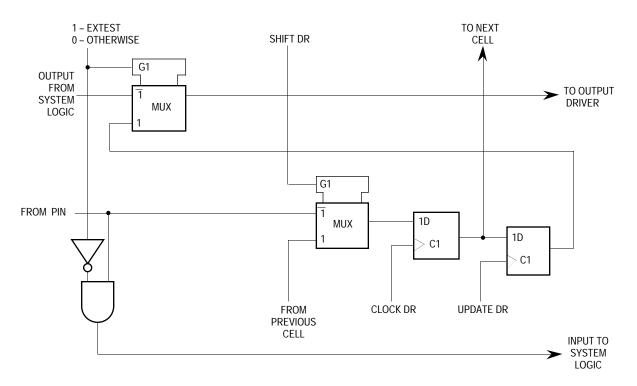

| 9-6  | Bidirectional Cell (IO.Cell)                                |       |

| 9-7  | Bidirectional Cell (IOx0.Cell)                              |       |

| 9-8  | General Arrangement for Bidirectional Pins                  |       |

| 9-9  | Bypass Register                                             |       |

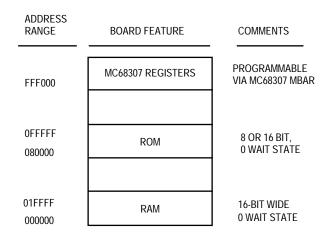

| 10-1 | MC68307 Minimum System Configuration                        | 10-3  |

| 10-2 | Hardware Setup                                              |       |

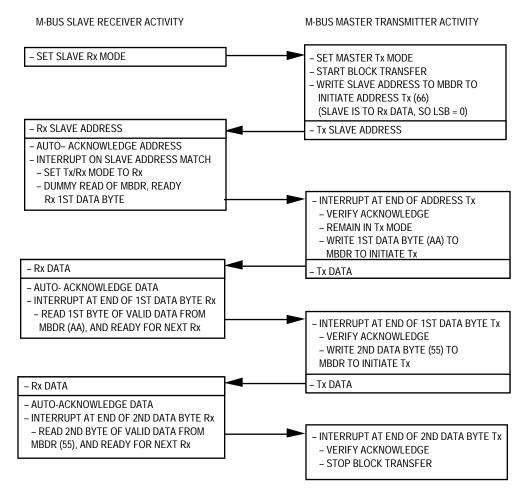

| 10-3 | Master/Slave Responsibilities for the Master Transmit Block | 10-15 |

| 10-4 | Summary of M-Bus Activity for the Master Transmit Block     | 10-15 |

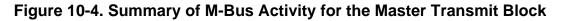

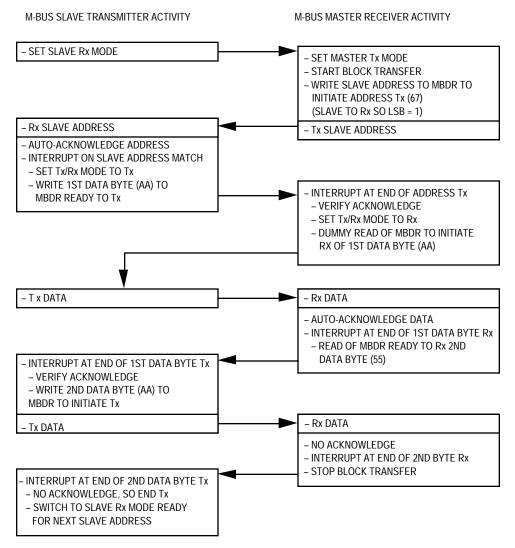

| 10-5 | Master/Slave Responsibilities for the Master Receive Block  |       |

| 10-6 | Summary of M-Bus Activity for the Master Receive Block      | 10-16 |

| 10-7 | Memory Map after Swap Complete                              |       |

| 11-1 | Drive Levels and Test Points for AC Specifications          | 11-3  |

| 11-2 | Clock Timing                                                |       |

| 11-3 | Read Cycle Timing Diagram                                   |       |

| 11-4 | Write Cycle Timing Diagram                                  |       |

| 11-5 | Three-Wire Bus Arbitration Diagram                          |       |

| 11-6 | Two-Wire Bus Arbitration Timing Diagram                     |       |

| External 8051 Bus Read Cycle               |                                 |

|--------------------------------------------|---------------------------------|

|                                            |                                 |

| •                                          |                                 |

|                                            |                                 |

| Receiver Timing                            |                                 |

| M-Bus Interface Input/Output Signal Timing |                                 |

| Port Timing                                |                                 |

| Test Clock Input Timing Diagram            |                                 |

| Boundary Scan Timing Diagram               |                                 |

| Test Access Port Timing Diagram            | 11-18                           |

|                                            | Test Clock Input Timing Diagram |

# **LIST OF TABLES**

| 2-1  | 68000 Bus Signal Summary                               | 2-3  |

|------|--------------------------------------------------------|------|

| 2-2  | 8051 Bus Signal Summary                                | 2-3  |

| 2-3  | Chip Select Signal Summary                             | 2-3  |

| 2-4  | Interrupt Port Signal Summary                          | 2-4  |

| 2-5  | Clock and Mode Control Signal Summary                  | 2-4  |

| 2-6  | Serial Module Signal Summary                           |      |

| 2-7  | JTAG Signal Summary                                    |      |

| 2-8  | Timer Module Signal Summary                            | 2-5  |

| 2-9  | M-Bus Module Signal Summary                            | 2-5  |

| 2-10 | Data Strobe Control of Data Bus                        | 2-8  |

| 2-11 | Signal Index                                           | 2-14 |

| 4-1  | Processor Data Formats                                 |      |

| 4-2  | Effective Addressing Modes                             |      |

| 4-3  | Notation Conventions                                   | 4-4  |

| 4-4  | EC000 Core Instruction Set Summary                     |      |

| 4-5  | Exception Vector Assignments                           |      |

| 4-6  | Exception Grouping and Priority                        |      |

| 5-1  | Address Block Selection in Peripheral Chip Select Mode | 5-7  |

| 5-2  | Port A Pin Functions                                   |      |

| 5-3  | Port B Pin Functions                                   | 5-12 |

| 5-4  | Interrupt Vector Response                              | 5-16 |

| 5-5  | MC68307 Configuration Memory Map                       | 5-20 |

| 5-6  | DTACK Field Encoding                                   | 5-32 |

| 7-1  | M-Bus Prescaler Values                                 | 7-7  |

| 8-1  | Serial Module Programming Model                        | 8-15 |

| 8-2  | PMx and PT Control Bits                                | 8-16 |

| 8-3  | B/Cx Control Bits                                      | 8-17 |

| 8-4  | CMx Control Bits                                       | 8-17 |

| 8-5  | SBx Control Bits                                       | 8-18 |

| 8-6  | RCSx Control Bits                                      | 8-21 |

| 8-7  | TCSx Control Bits                                      | 8-22 |

| 8-8  | MISCx Control Bits                                     | 8-23 |

| 8-9  | TCx Control Bits                                       | 8-24 |

| 8-10 | RCx Control Bits                                       |      |

| 8-11 | Timer Mode and Source Select Bits                      | 8-27 |

| 9-1  | Boundary Scan Control Bits                             | 9-4  |

| 9-2  | Boundary Scan Bit Definitions                          | 9-5  |

| 9-3  | Instructions                                           |      |

| 10-1 | Power Contribution from Modules                        |      |

---- -

# SECTION 1 INTRODUCTION

The MC68307 is an integrated processor combining a static EC000 processor with multiple interchip bus interfaces. The MC68307 is designed to provide optimal integration and performance for applications such as digital cordless telephones, portable measuring equipment, and point-of-sale terminals. By providing 3.3 V, static operation in a small package, the MC68307 delivers cost-effective performance to handheld, battery-powered applications.

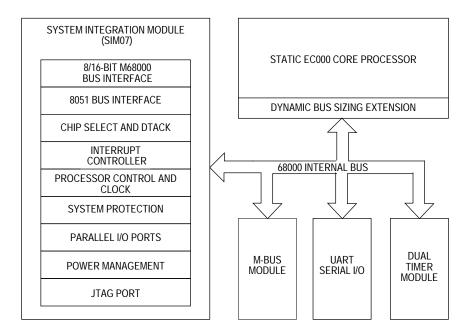

The MC68307 (see Figure 1-1) contains a static EC000 core processor, multiple bus interfaces, a serial channel, two timers, and common system glue logic. The multiple bus interfaces include: dynamic 68000 bus, 8051-compatible bus, and Motorola bus (M-bus) or  $I^2C$  bus<sup>1</sup>.

Figure 1-1. MC68307 Block Diagram

The dynamically-sized 68000 bus allows 16-bit performance using static random access memory (SRAM) while providing a low-cost interface to an 8-bit read-only memory (ROM). The 8051-compatible bus interfaces gluelessly to 8051-type devices and allows the reuse

...

. . .

. . .

<sup>&</sup>lt;sup>1.</sup> I<sup>2</sup>C bus is a proprietary Philips interface bus.

of application-specific integrated circuits (ASICs) designed for this industry standard bus. The M-bus is an industry-standard 2-wire interface that provides efficient communications with peripherals such as EEPROM, analog/digital (A/D) converters, and liquid crystal display (LCD) drivers. Thus, the MC68307 interfaces gluelessly to boot ROM, SRAM, 8051 devices, M-bus devices, and memory-mapped peripherals. The MC68307 also incorporates a slave mode which allows the EC000 core to be disabled, providing a 3.3-V or 5-V static, low-power multifunction peripheral for higher performance M68000 family processors.

The main features of the MC68307 include:

- Static EC000 Core Processor

- Full Compatibility with M68000 and EC000

- -24-Bit Address Bus, for 16-Mbyte Off-Chip Address Space

- 16-Bit On-Chip Data Bus for M68000 Bus Operations

- -2.7 MIPS Performance at 16.67 MHz Processor Clock

- Processor Disable Mmode for Use as a Peripheral to an External Processor

- Emulation Mode for Use with In-Circuit Emulator

- External M68000 Bus Interface with Dynamic Bus Sizing for 8-Bit and 16-Bit Data Ports

- External 8051-Compatible 8-Bit Data Bus Interface

- Power Management

- Fully Static Operation with Processor Shutdown and Wake-Up Modes for Substatial Power Savings

- Very Rapid Response to Interrupts from the Power-Down State

- Operates from DC to 16.67 MHz System Clock

- --- Clock Enable/Disable for Each Peripheral

- M-Bus Module

- Provides Interchip Bus Interface for EEPROMs, LCD Controllers, A/D Converters, etc.

- Compatible with Industry-Standard I<sup>2</sup>C Bus

- Master or Slave Operation Modes, Supports Multiple Masters

- Automatic interrupt Generation with Programmable Level

- Software-Programmable Clock Frequency

- Data Rates from 4–100 Kbit/s above 3.0 MHz System Clock

- Universal Asynchronous Receiver/Transmitter (UART) Module

- Flexible Baud Rate Generator

- Based on MC68681 Dual Universal Asynchronous Receiver/Transmitter (DUART) Programming Model

- 5 Mbits/s Maximum Transfer Rate at 16.67 MHz System Clock

- Automatic Interrupt Generation with Programmable Level

- Modem Control Signals Available (CTS, RTS)

- Timer Module

- Dual Channel 16-Bit General-Purpose Counter/Timer

- Multimode Operation, Independent Capture/Compare Registers

- Automatic Interrupt Generation with Programmable Level

- 60-ns Resolution at 16.67 MHz System Clock

- Separate Input and Output Pins for Each Timer

• System Integration Module (SIM07), Incorporating Many Functions Typically Relegated to External Programmable Array Logic (PALs), Transistor-Transistor Logic (TTL), and ASICs, Such as:

-System Configuration, Programmable Address Mapping

-System Protection by Hardware Watchdog Logic and Software Watchdog Timer

—Power-Down Mode Control, Programmable Processor Clock Driver

- -Four Programmable Chip Selects with Wait State Generation Logic

- —Three Simple Peripheral Chip Selects

-Parallel Input/Output Ports, Some with Interrupt Capability

—Programmed Interrupt Vector Response for On-Chip Peripheral Modules

—IEEE 1149.1 Boundary Scan Test Access Port (JTAG)

- Operating Voltages of  $3.3\,\text{V}\pm0.3\,\text{V}$  and  $5\,\text{V}\pm0.5\,\text{V}$

- 0 to 70°C (Standard part); -40 to +85°C (Extended Temperature Part)

- Compact 100-Lead Quad Flat Pack (QFP) and 100-Lead Thin Quad Flat Pack (TQFP) Packages

#### 1.1 M68300 FAMILY

The MC68307 is one of a series of components in Motorola's M68300 family. Other members of the family include the MC68302, MC68306, MC68322, MC68330, MC68331, MC68332, MC687333, MC68334, MC68340, MC68341, MC68349, MC68356, and MC68360.

#### 1.1.1 Organization

The M68300 family of integrated processors and controllers is built on an M68000 core processor and a selection of intelligent peripherals appropriate for a set of applications. Common system glue logic such as address decoding, wait state insertion, interrupt prioritization, and watchdog timing is also included.

Each member of the M68300 family is distinguished by its selection of on-chip peripherals. Peripherals are chosen to address specific applications, but are often useful in a wide variety of applications. The peripherals may be highly sophisticated timing or protocol engines that have their own processors, or they may be more traditional peripheral functions, such as UARTs and timers.

#### 1.1.2 Advantages

By incorporating so many major features into a single M68300 family chip, a system designer can realize significant savings in design time, power consumption, cost, board space, pin count, and programming. The equivalent functionality can easily require 20 separate components. Each component might have 16–64 pins, totalling over 350 connections. Most of these connections require interconnects or are duplications. Each connection is a candidate for a bad solder joint or misrouted trace. Each component is another part to qualify, purchase, inventory, and maintain. Each component requires a share of the printed circuit board. Each component draws power, which is often used to drive large buffers to get the signal to another chip. The cumulative power consumption of all the components must be available from the power supply. The signals between the central processing unit (CPU)

and a peripheral might not be compatible nor run from the same clock, requiring time delays or other special design considerations.

In an M68300 family component, the major functions and glue logic are all properly connected internally, timed with the same clock, fully tested, and uniformly documented. Only essential signals are brought out to pins. The primary package is the surface-mount plastic QFP for the smallest possible footprint.

#### 1.2 MC68307 ARCHITECTURE

To improve total system throughput and reduce part count, board size and cost of system implementation, the MC68307 integrates a powerful processor, intelligent peripheral modules, and typical system interface logic. These functions include the SIM07, timers, UART, M-bus interface, and 8051-compatible bus interface.

The EC000 core processor communicates with these modules via an internal bus, providing the opportunity for fully synchronized communication between all modules and allowing interrupts to be handled in parallel with data transfers, greatly improving system performance.

#### 1.2.1 EC000 Core Processor

The EC000 is a core implementation of the M68000 32-bit microprocessor architecture. The programmer can use any of the eight 32-bit data registers for fast manipulation of data and any of the eight 32-bit address registers for indexing data in memory. Flexible instructions support data movement, arithmetic functions, logical operations, shifts and rotates, bit set and clear, conditional and unconditional program branches, and overall system control.

The EC000 core can operate on data types of single bits, binary-coded decimal (BCD) digits, and 8, 16, and 32 bits. The integrated chip selects allow peripherals and data in memory to reside anywhere in the 16-Mbyte linear address space. A supervisor operating mode protects system-level resources from the more restricted user mode, allowing a true virtual environment to be developed. Many addressing modes complement these instructions, including predecrement and postincrement, which allow simple stack and queue maintenance and scaled indexing for efficient table accesses. Data types and addressing modes are supported orthogonally by all data operations and with all appropriate addressing modes. Position-independent code is easily written.

Like all M68000 family processors, the EC000 core recognizes interrupts of seven different priority levels and, in conjunction with the integrated interrupt controller, allows a programmed vector to direct the processor to the desired service routine. Internal trap exceptions ensure proper instruction execution with good addresses and data, allow operating system intervention in special situations, and permit instruction tracing. The hardware time-out can terminate bad memory accesses before instructions process data incorrectly. The EC000 core provides 2.7 millions of bits per second (MIPS) at 16.67 MHz.

#### 1.2.2 System Integration Module (SIM07)

The SIM07 provides the external bus interface for the EC000 core. It also eliminates much of the glue logic that typically supports a microprocessor and its interface with the peripheral

and memory system. The SIM07 provides programmable circuits to perform address-decoding and chip selects, wait-state insertion, interrupt handling, clock generation, discrete I/O, and power management features.

**1.2.2.1 EXTERNAL BUS INTERFACE.** The external bus interface (EBI) handles the transfer of information between the internal EC000 core and memory, peripherals, or other processing elements in the external address space. It consists of an M68000 bus interface and an 8051-compatible bus interface. The external M68000 bus provides up to 24 address lines and 16 data lines. Each bus access can appear externally either as an M68000 bus cycle (either 16-bit or 8-bit dynamic data bus width) or an 8-bit wide 8051-compatible bus cycle (multiplexing address and 8-bit data) with the respective sets of control signals. The default bus cycle is an M68000 16-bit-wide one, the 8051-compatible address space being programmable.

**1.2.2.2 CHIP SELECT AND WAIT STATE GENERATION.** Four programmable chip select outputs provide signals to enable external memory and peripheral circuits, providing all handshaking and timing signals for automatic wait-state insertion and data bus sizing.

Base memory address and block size are both programmable, with some restrictions, (e.g. a starting address must be on a boundary which is a multiple of the block size). Each chip-select is general-purpose. However one of the chip-selects can be programmed to select an addressing range which is decoded as an 8051-compatible bus access, and another can be used to enable one of four simple external peripherals. Data bus width (8-bit or 16-bit) is programmable on all four chip-selects and further decoding is available for protection from user mode access or read-only access.

**1.2.2.3 SYSTEM CONFIGURATION AND PROTECTION.** The SIM07 provides configuration registers that allow general system functions to be controlled and monitored. For example, all on-chip registers can be relocated as a block by programming a module base address, power-down modes can be selected, and the source of the most recent RESET or BERR can be checked. The hardware watchdog features can be enabled or disabled and the bus timeout times can be programmed.

The power-down mode allows software to disable the EC000 core during periods of inactivity. This feature works in conjunction with the interrupt control logic to allow any interrupt condition to cause a wake-up, which causes the EC000 core to resume processing without requiring any RESET or re-initialization. All register contents are preserved, and the interrupt which caused wake-up is serviced in the normal manner as soon as the clock restarts. To reduce power consumption further, the internal clocks to the on-chip peripheral modules can be disabled by software.

**1.2.2.4 PARALLEL INPUT/OUTPUT PORTS.** Two general-purpose ports (A and B) are provided for input/output, although the pins for these ports are shared with other functions. Some bits in port A are multiplexed with the peripheral chip-select lines and timer output signals, and port B is multiplexed with various peripheral I/O lines from the UART, M-Bus and Timer modules. Maximum flexibility is therefore available for differing hardware configurations. Eight of the 16 Port B lines are also latched inputs to the interrupt controller, with programmable interrupt priority level.

**1.2.2.5 INTERRUPT CONTROLLER.** The SIM07 coordinates all interrupt sources, both from on-chip peripherals (timer1, timer2, M-bus, and UART) and off-chip inputs (IRQ7, and INT1–INT8). It provides interrupt requests to the EC000 core with programmable priority level, and responds to acknowledge cycles by providing programmed vectors unique to each source.

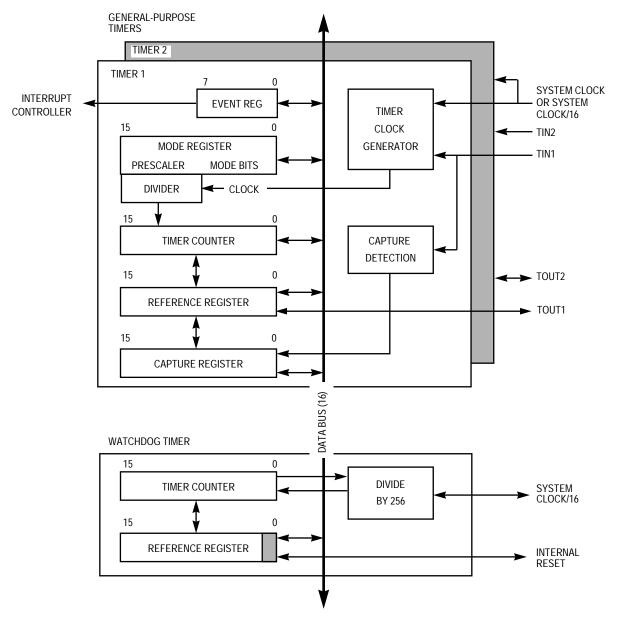

## 1.2.3 Timer Module

The timer module comprises two independent, identical general-purpose timers, and a software watchdog timer. Each general-purpose timer block contains a free-running 16-bit timer that can be used in various modes, to capture the timer value with an external event, to trigger an external event or interrupt when the timer reaches a set value, or to count external events. Each has an 8-bit prescaler to allow a programmable clock input frequency derived from the system clock or external count input. The output pins (one per timer) have a programmable mode.

A software watchdog timer is also provided for system protection. If required, this resets the EC000 core if it is not refreshed periodically by software.

## 1.2.4 UART Module

The MC68307 contains a full-duplex UART module, with an on-chip baud-generator providing both standard and nonstandard baud rates up to 5 Mb/s. The module is functionally equivalent to the MC68681 DUART, although only one serial channel is implemented. Data formats can be 5, 6, 7, or 8 bits with even, odd, or no parity and up to two stop bits in 1/16 increments. Four-byte receive buffers and two-byte transmit buffers minimize CPU service calls. A wide variety of error detection and maskable interrupt capability is provided on each channel. Full-duplex autoecho loopback, local loopback, and remote loopback modes can be selected. Multidrop applications are supported.

Clocking is provided by the MC68307 system clock, via a programmable prescaler allowing various baud rates to be chosen. Modem support is provided with request-to-send ( $\overline{\text{RTS}}$ ) and clear-to-send ( $\overline{\text{CTS}}$ ) lines available. The serial port can sustain data rates of 5 Mbps.

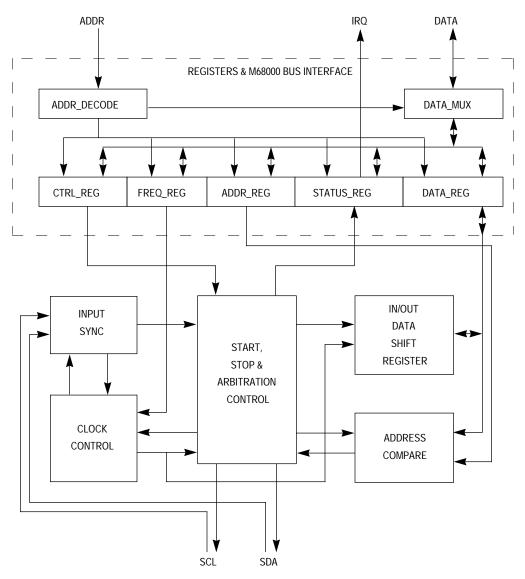

#### 1.2.5 M-Bus Module

The M-bus interface module provides a two-wire, bidirectional serial bus which provides a simple, efficient way for data exchange between devices. It is compatible with the I<sup>2</sup>C-bus standard. M-bus minimizes the interconnection between devices in the end-system. It is best suited for applications which need occasional bursts of fast communication over a short distance, among a number of devices. The maximum data rate is limited to 595 kbps at 16.67 MHz (100 kbps to be compatible with I<sup>2</sup>C), the maximum communication length and number of devices which can be connected are limited physically by the maximum bus capacitance and logically by the number of unique addresses.

The M-bus system is a true multimaster bus including collision detection and arbitration to prevent data corruption if two or more masters intend to control the bus simultaneously. This feature provides the capability for complex applications with multiprocessor control. It may also be used for rapid testing and alignment of end products via external diagnostic connections.

#### **1.2.6 Test Access Port**

To aid in system diagnostics, the MC68307 includes dedicated user-accessible test logic that is compliant with the IEEE 1149.1 standard for boundary scan testability, often referred to as JTAG (Joint Test Action Group). This is described briefly in **Section 9 IEEE 1149.1 Test Access Port**. For further information refer to the IEEE 1149.1 standard.

# SECTION 2 SIGNAL DESCRIPTION

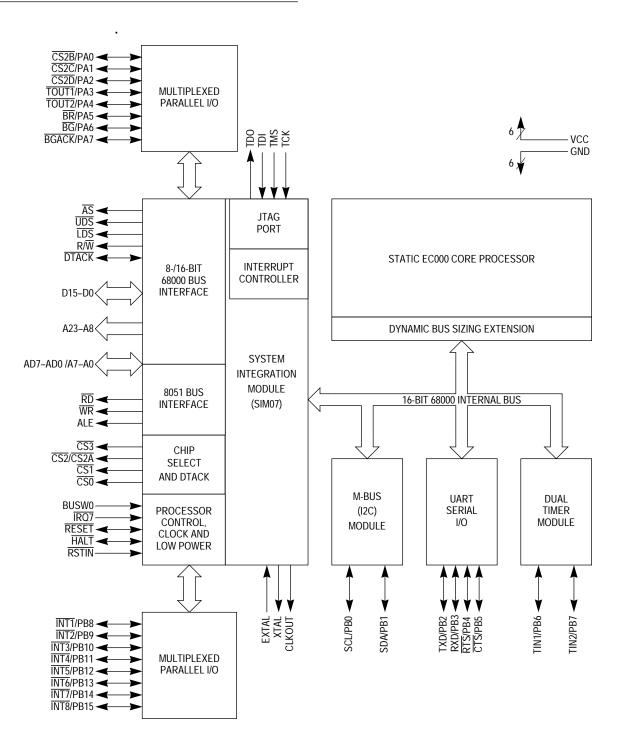

This section contains a brief description of the input and output signals, with reference (if applicable) to other sections which give greater detail on its use. Figure 2-1 provides a detailed diagram showing the integrated peripherals and signals, and Table 2-2 to Table 2-9 provide a quick reference for determining a signal's name, mnemonic, its use as an input or output, active state, and type identification.

#### NOTE

The terms **assertion** and **negation** will be used extensively. This is done to avoid confusion when dealing with a mixture of "active-low" and "active-high" signals. The term assert or assertion is used to indicate that a signal is active or true, independent of whether that level is represented by a high or low voltage. The term negate or negation is used to indicate that a signal is inactive or false.

. .. ..

-----

. . .

. . .

Figure 2-1. MC68307 Detailed Block Diagram

| Signal Name               | Mnemonic  | Input/<br>Output | Three-State During<br>Bus Arbitration | Pullup Resistor<br>Required |

|---------------------------|-----------|------------------|---------------------------------------|-----------------------------|

| Address Signals           | A23–A0    | Output           | Yes                                   | (4)                         |

| Address Strobe            | ĀS        | Output           | Yes                                   | (3)                         |

| Bus Grant                 | BG/PA6    | Output (2)       | No                                    | —                           |

| Bus Grant Acknowledge     | BGACK/PA7 | Input (2)        | —                                     | (1)                         |

| Bus Request               | BR/PA5    | Input (2)        | —                                     | (1)                         |

| Data Bus                  | D15–D0    | I/O              | Yes                                   | —                           |

| Data Transfer Acknowledge | DTACK     | I/O              | Yes                                   | 2.2 KΩ                      |

| Halt                      | HALT      | I/O              | —                                     | 2.2 KΩ                      |

| Lower Data Strobe         | LDS       | Output           | Yes                                   | (3)                         |

| Upper Data Strobe         | UDS       | Output           | Yes                                   | (3)                         |

| Read/Write                | R/W       | Output           | Yes                                   | (3)                         |

| Reset                     | RESET     | I/O              | —                                     | 2.2 KΩ                      |

#### Table 2-1. 68000 Bus Signal Summary