# 8-bit Proprietary Microcontroller cmos

## F<sup>2</sup>MC-8L MB89550A Series

## MB89557A/558A/P558A/PV550A

#### ■ DESCRIPTION

The MB89550A series is a general-purpose, single-chip microcontroller that features a compact instruction set and contains a range of peripheral functions including a dual- clock control system, 5-level operating speed control, LCD controller driver, A/D converter, D/A converter, timer, serial interface, PWM timer, PWC timer, and external interrupts. The LCD controller driver is particularly suited for simultaneous control of LCD duty drive and static drive functions.

### **■ FEATURES**

- Range of package options

- LQFP package (0.5 mm pitch)

- TQFP package (0.4 mm pitch)

- High speed operation at low voltage

- Minimum instruction execution time 0.32 μs (for 12.5 MHz oscillation)

- F2MC-8L CPU core

Instruction set optimized for controller applications

- Multiplication and division instructions

- 16-bit arithmetic operations

- · Bit test branch instructions

- · Bit manipulation instructions, etc.

(Continued)

For the information for microcontroller supports, see the following web site.

http://edevice.fujitsu.com/micom/en-support/

#### (Continued)

### Dual-clock control system

- Main clock 12.5 MHz maximum: (Four speed settings available, oscillation halts in sub-clock mode)

- Sub-clock 32.768 kHz: (Operation clock for sub-clock mode)

### • 11 timer systems

- 8/16-bit timer counter 1 (square wave output, 2-channel output switching available)

- 8/16-bit timer counter 2 (square wave output, 2-channel output switching available)

- 16-bit timer counter (also functions as event counter)

- 8-bit PWM timer (8-bit PWM timer × 2 channels or PPG timer × 1 channel, includes event counter function)

- 8-bit PWC timer (8-bit PWC timer × 1 channel)

- 6-bit PPG timer (6-bit PPG timer × 1 channel)

- 21-bit timebase timer

- Watch prescaler (17-bit)

#### UART/serial interface

· UART/SIO switching

#### UART

Clock synchronous/asynchronous switching available

#### • 10-bit A/D converter

• 10-bit A/D × 8 channels

#### • 8-bit D/A converter

• 8-bit D/A × 2 channels

#### External interrupts

- Eight independent inputs can be used for recovery from low-power consumption modes (selection of rising, falling, or both edge detection functions).

- Eight independent inputs can be used for recovery from low-power consumption modes (L level detection function included).

#### Clock output functions

- High speed clock signal multiplied by 2 available as output from HCLK pin.

- Low speed clock pulse output available from LCLK pin.

### • LCD controller driver

- 32SEG × 4COM (maximum 128 pixels)

- 8 dedicated to segment output only

- 8 for port or segment use

- 16 for port, segment, or static use

- Built-in step-up power supply for driving LCD (optionally available)

### • Low-power consumption modes (standby modes)

- Stop mode (all oscillations halt in sub-clock mode, current consumption falls to almost zero)

- Sleep mode (the CPU stops to reduce current consumption to approximately 1/3 of normal)

- Watch mode (all operations other than the clock prescaler halt, current consumption is very low)

- Sub clock mode (systems operate on sub-clock signals)

#### Maximum 66 I/O ports

- General-purpose I/O ports (N-ch open drain) : 4

- General-purpose I/O ports (N-ch open drain) : 24

- [also function as LCD ports, with restrictions]

- General purpose I/O ports (CMOS): 38

### **■ PRODUCT LINEUP**

| Part no. Parameter                                                                                                     |                          | t no.                                                                                    | MB89P558A-201<br>MB89P558A-202<br>MB89P558A-203                                                                                                                                                                                 | MB89557A               | MB89558A              | MB89PV550A*-201<br>MB89PV550A*-202<br>MB89PV550A*-203 |  |

|------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|-------------------------------------------------------|--|

| ROM size                                                                                                               |                          |                                                                                          | 48 KB                                                                                                                                                                                                                           | 32 KB                  | 48 KB                 | _                                                     |  |

| RAM size                                                                                                               |                          |                                                                                          | 2 KB                                                                                                                                                                                                                            | 1 KB                   | 2 KB                  | 1 KB                                                  |  |

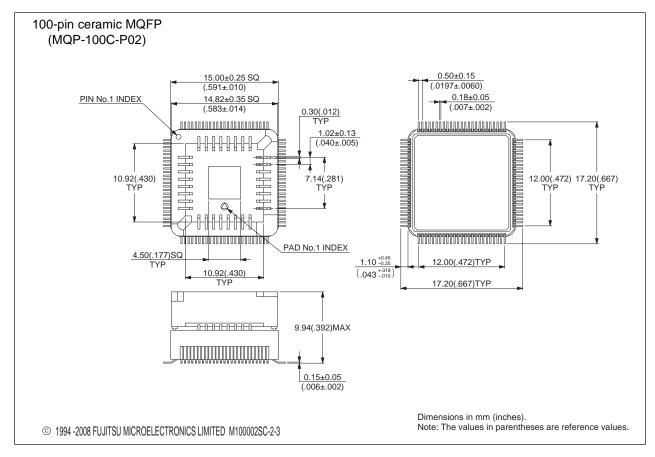

| Packages                                                                                                               |                          |                                                                                          | LQFP100<br>TQFP100                                                                                                                                                                                                              | LQFP100<br>TQFP100     | LQFP100<br>TQFP100    | MQFP100                                               |  |

| Classification                                                                                                         |                          |                                                                                          | One-time product                                                                                                                                                                                                                | Mask ROM product       | Mask ROM product      | Evaluation product                                    |  |

| CPU functions                                                                                                          |                          |                                                                                          | Number of instructions : 136 Instruction bit length : 8-bit Instruction length : 1 to 3bytes Data bit length : 1-, 8-, 16-bits Minimum execution time : 0.32 μs (at 12.5 MHz) Interrupt processing time : 2.88 μs (at 12.5 MHz) |                        |                       |                                                       |  |

| Output-only ports (N-ch open drain) Ports General-purpose I/O ports (N-ch open drain) General-purpose I/O ports (CMOS) |                          |                                                                                          |                                                                                                                                                                                                                                 |                        |                       |                                                       |  |

|                                                                                                                        | 8/16-bit timer counter 1 |                                                                                          | 2-channel 8-bit timer/counter operation (also functions as 1-channel 16-bit timer) with square wave output function                                                                                                             |                        |                       |                                                       |  |

|                                                                                                                        | 8/16-bit timer counter 2 |                                                                                          | 2-channel 8-bit timer/counter operation (also functions as 1-channel 16-bit timer) with square wave output function                                                                                                             |                        |                       |                                                       |  |

| ons                                                                                                                    | 16-bit timer counter     |                                                                                          | 16-bit timer/counter of                                                                                                                                                                                                         | peration, 16-bit event | counter operation     |                                                       |  |

| Peripheral Functions                                                                                                   | PPWM time                | r                                                                                        | 2-channel 8-bit PWM with event counter full                                                                                                                                                                                     |                        | unctions as 1-channel | PPG timer)                                            |  |

| eral                                                                                                                   | PWC timer                |                                                                                          | 1-channel 8-bit PWC                                                                                                                                                                                                             | timer operation        |                       |                                                       |  |

| riph                                                                                                                   | 6-bit PPG tir            | ner                                                                                      | 1-channel 6-bit PWM                                                                                                                                                                                                             | timer operation        |                       |                                                       |  |

| Pe                                                                                                                     | LCD controll driver      | I (some ports provide selection of DLLLY drive/STATIC drive/N-ch open drain I/O port tui |                                                                                                                                                                                                                                 |                        |                       | ppen drain I/O port func-                             |  |

|                                                                                                                        | UART                     | SIO                                                                                      | Switchable between and SIO (simple seria                                                                                                                                                                                        |                        | hronous/asynchronous  | s data transfer function)                             |  |

|                                                                                                                        | UART/SIO                 |                                                                                          | Data transfer function for UART/SIO                                                                                                                                                                                             |                        |                       |                                                       |  |

|                                                                                                                        | A/D converter            |                                                                                          | 8-channel 10-bit resolution                                                                                                                                                                                                     |                        |                       |                                                       |  |

|                                                                                                                        | D/A converter            |                                                                                          | 2-channel, 8-bit resolution                                                                                                                                                                                                     |                        |                       |                                                       |  |

|                                                                                                                        | Clock output             | t                                                                                        | High speed clock multiplied×2, and sub clock output available                                                                                                                                                                   |                        |                       |                                                       |  |

| Sta                                                                                                                    | ndby modes               |                                                                                          | Sub clock mode, slee                                                                                                                                                                                                            | ep mode, watch mode,   | and stop mode         |                                                       |  |

<sup>\*:</sup> The MB89PV550A provides only evaluation functions (functions for use with emulation tools). This model cannot use piggyback functions (functions for use with E²PROM).

### **■ OPTIONS AND CORRESPONDING PRODUCTS**

|                                    |                        | -201 Options                                                                      | -202 Options             | -203 Options                                                                  |

|------------------------------------|------------------------|-----------------------------------------------------------------------------------|--------------------------|-------------------------------------------------------------------------------|

| LCI                                | D step-up circuit      | No step-up circuit                                                                | Step-up circuit included |                                                                               |

| PORT/SEG<br>dual-use pin selection |                        | SEG8 to SEG31 SEG8 to SEG31 SEG/PORT dual use SEG/PORT dual use SEG/PORT dual use |                          | SEG8 to SEG21<br>: SEG/PORT dual use<br>SEG22 to SEG31<br>: N-ch open drain*1 |

|                                    | Evaluation model       | MB89PV550A-201                                                                    | MB89PV550A-202           | MB89PV550A-203                                                                |

| Model                              | One-time model         | MB89P558A-201                                                                     | MB89P558A-202            | MB89P558A-203                                                                 |

| type                               | Mask ROM model*2       | MB89557A                                                                          | MB89557A                 | MB89557A                                                                      |

|                                    | IVIASK ROIVI IIIOGEI - | MB89558A                                                                          | MB89558A                 | MB89558A                                                                      |

<sup>\*1 :</sup> The SEG22-SEG31 pins (N-ch open drain) are not subject to the restriction that input voltage (V<sub>IN</sub>) must be less than the voltage at the V3 pin.

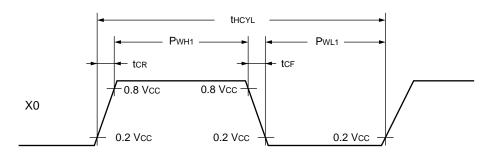

### ■ OSCILLATOR STABILIZATION WAIT TIME SELECTION

The MB89557A/558A allow a selection of default value for oscillator stabilization wait time, to be selected at the time of mask ROM ordering.

| Oscillator stabilization wait time selection | Remarks                    |

|----------------------------------------------|----------------------------|

| 2¹⁴/Fсн                                      | 1.31 ms (at F = 12.5 MHz)  |

| 2 <sup>17</sup> / <b>F</b> сн                | 10.48 ms (at F = 12.5 MHz) |

| 218/Fсн                                      | 20.97 ms (at F = 12.5 MHz) |

<sup>\*2 :</sup> Options may be specified at the time of mask ROM ordering.

### ■ DIFFERENCES AMONG PRODUCTS AND PRECAUTIONS FOR MODEL SELECTION

• Package and Model Combinations

| Models Package                          | MB89PV550A | MB89P558A | MB89557A<br>MB89558A |

|-----------------------------------------|------------|-----------|----------------------|

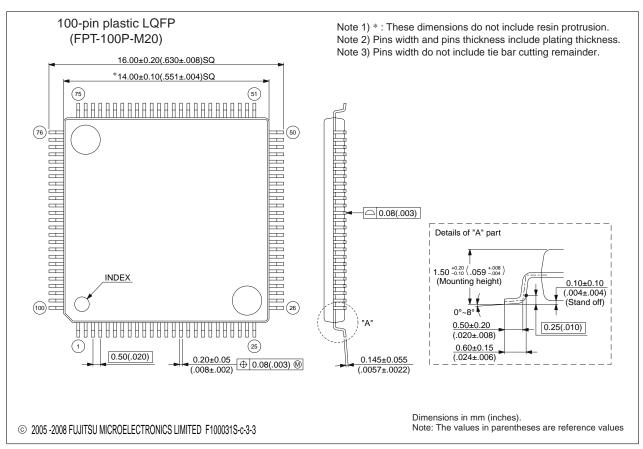

| FPT-100P-M20<br>(LQFP-100 0.5 mm pitch) | ×          | 0         | 0                    |

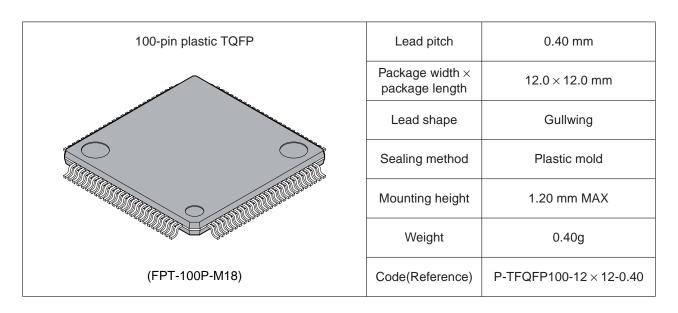

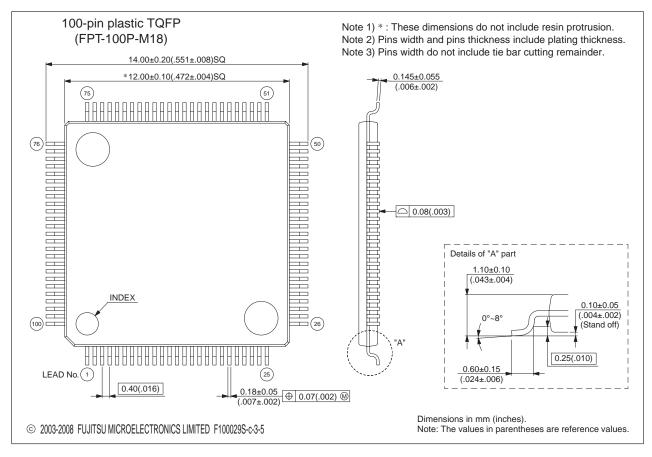

| FPT-100P-M18<br>(TQFP-100 0.4 mm pitch) | ×          | 0         | 0                    |

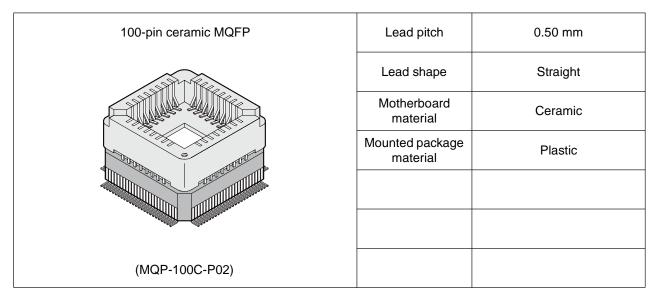

| MQP-100C-P02<br>(MQFP-100 0.5 mm pitch) | 0          | ×         | ×                    |

Note: Compatible with all options (-201/202/203).

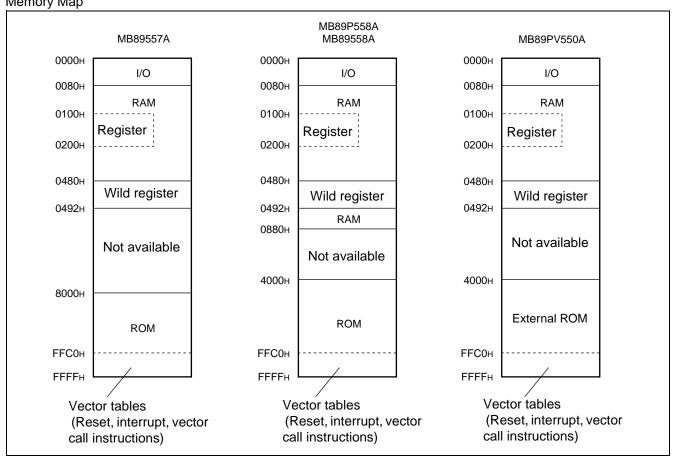

- Memory Space

- When evaluating chips using piggyback evaluators etc., please take note of the differences among products before making the evaluation.

- Current Consumption

- When operating at low speed, one-time PROM and EPROM products will consume more current than mask ROM products. However, the current consumption in sleep/stop modes is the same.

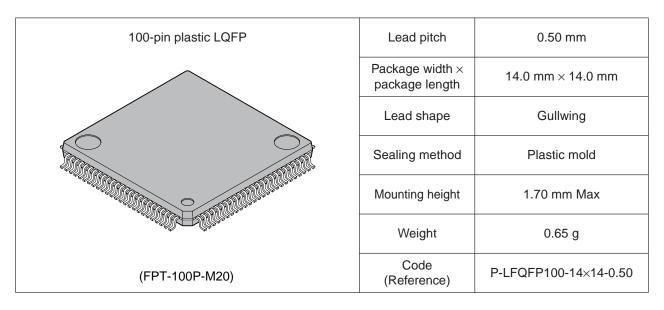

- For specific details about each package, see " PACKAGE DIMENSIONS".

- For details about power consumption, see "■ ELECTRICAL CHARACTERISTICS" .

- Mask Options

- The available options, and methods of using options, differ according to the model. Be sure to confirm the options from the "■ MASK OPTIONS" section.

- LCD Drive Step-up Power Circuit

The MB89550A series is available with or without the step-up circuit option as a mask option.

Power Supply Path

The models in the MB89550A series have two power supply pins,  $V_{CC1}$  and  $V_{CC2}$ , with power supply paths that differ according to the model.

| Models                                                  | Supply pin | Power supply path                                                                                  |

|---------------------------------------------------------|------------|----------------------------------------------------------------------------------------------------|

| MB89557A/                                               | Vcc1       | 3V power supply pin for internal resource operation, including the CPU.                            |

| 558A                                                    | Vcc2       | 5V power supply pin for input/output ports.                                                        |

|                                                         | Vcc1       | V <sub>PP</sub> pin for on-board writing.                                                          |

| MB89P558A V <sub>CC2</sub> V power supply poutput pins. |            | V power supply pin for internal resource operation, including the CPU, and for input/output pins.  |

|                                                         | Vcc1       | Internally shut off, operates as input to Vcc2 only.                                               |

| MB89PV550A                                              | Vcc2       | 5V power supply pin for internal resource operation, including the CPU, and for input/output pins. |

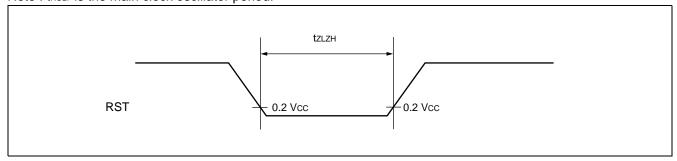

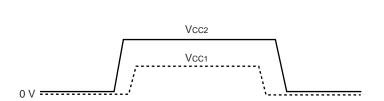

Oscillator Startup and Power-on Reset

On the MB89PV550A and MB89P558A, oscillator startup and power-on reset are applied at the rise of the  $V_{\text{CC2}}$  input. On the MB89558A and MB89557A, oscillator startup and power-on reset are applied at the rise of the  $V_{\text{CC1}}$  input.

### • Wide Register Functions

The space available for use of wide register functions is as follows.

MB89PV550A

2000H to FFFH

MB89P558A

4000H to FFFH

MB89558A

4000H to FFFH

MB89557A

8000H to FFFH

#### • The P40, P41, P84, P85 Pins

On the MB889PV550A, an external oscillator signal equivalent to 64 clock pulses is required to initialize the P40, P41, P84, and P85 pins. Note therefore that at power-on there is an interval in which the values of these ports is undefined.

On the MB89P558A, MB89558A, and MB89557A, these ports are set to "Hi-Z" status at power-on.

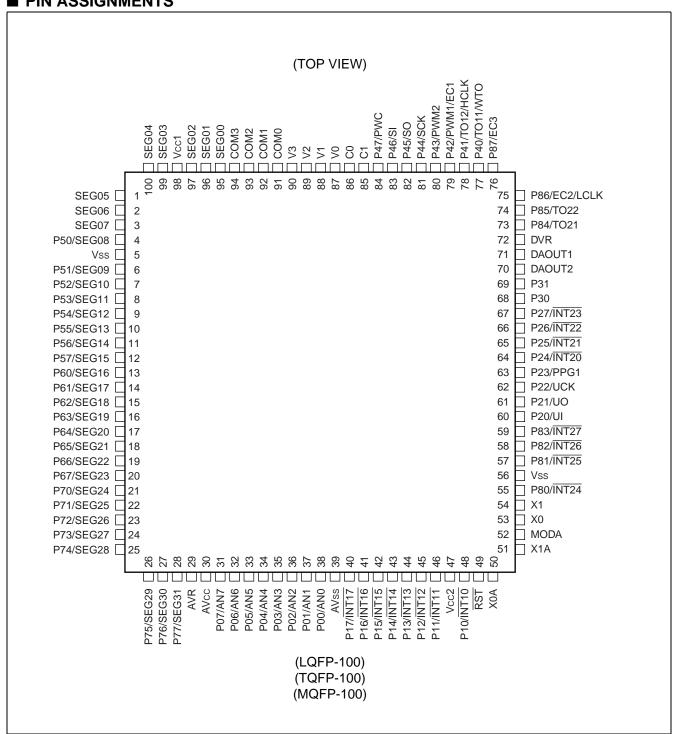

### **■ PIN ASSIGNMENTS**

### **■ PIN DESCRIPTION**

| Pin<br>No. | Pin Name      | Circuit<br>Type | Function                                                                             |  |

|------------|---------------|-----------------|--------------------------------------------------------------------------------------|--|

| 1          | SEG05         | Н               |                                                                                      |  |

| 2          | SEG06         | Н               | Segment output pins for LCDC duty drive.                                             |  |

| 3          | SEG07         | Н               |                                                                                      |  |

| 4          | P50/<br>SEG08 | G               | N-ch open drain I/O pin. Also functions as a segment output pin for LCDC duty drive. |  |

| 5          | Vss           |                 | Power supply (GND) pin.                                                              |  |

| 6          | P51/<br>SEG09 |                 |                                                                                      |  |

| 7          | P52/<br>SEG10 |                 |                                                                                      |  |

| 8          | P53/<br>SEG11 |                 |                                                                                      |  |

| 9          | P54/<br>SEG12 | G               | N-ch open drain I/O pins. Also function as segment output pins for LCDC duty drive.  |  |

| 10         | P55/<br>SEG13 |                 |                                                                                      |  |

| 11         | P56/<br>SEG14 |                 |                                                                                      |  |

| 12         | P57/<br>SEG15 |                 |                                                                                      |  |

| 13         | P60/<br>SEG16 |                 |                                                                                      |  |

| 14         | P61/<br>SEG17 |                 |                                                                                      |  |

| 15         | P62/<br>SEG18 |                 |                                                                                      |  |

| 16         | P63/<br>SEG19 |                 |                                                                                      |  |

| 17         | P64/<br>SEG20 | G               | N-ch open drain I/O pins.                                                            |  |

| 18         | P65/<br>SEG21 | G               | Also function as segment output pins for LCDC duty drive or static drive.            |  |

| 19         | P66/<br>SEG22 |                 |                                                                                      |  |

| 20         | P67/<br>SEG23 |                 |                                                                                      |  |

| 21         | P70/<br>SEG24 |                 |                                                                                      |  |

| 22         | P71/<br>SEG25 |                 |                                                                                      |  |

| Pin<br>No. | Pin Name      | Circuit<br>Type | Function                                                                                                                                                   |

|------------|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23         | P72/<br>SEG26 |                 |                                                                                                                                                            |

| 24         | P73/<br>SEG27 |                 |                                                                                                                                                            |

| 25         | P74/<br>SEG28 | G               | N-ch open drain I/O pins.                                                                                                                                  |

| 26         | P75/<br>SEG29 | G               | Also function as segment output pins for LCDC duty drive or static drive.                                                                                  |

| 27         | P76/<br>SEG30 |                 |                                                                                                                                                            |

| 28         | P77/<br>SEG31 |                 |                                                                                                                                                            |

| 29         | AVR           |                 | A/D converter reference voltage input pin.                                                                                                                 |

| 30         | AVcc          |                 | A/D converter and D/A converter power supply pin.                                                                                                          |

| 31         | P07/AN7       |                 |                                                                                                                                                            |

| 32         | P06/AN6       |                 |                                                                                                                                                            |

| 33         | P05/AN5       |                 |                                                                                                                                                            |

| 34         | P04/AN4       | D               | General purpose I/O ports. Also function as analog input pins.                                                                                             |

| 35         | P03/AN3       | Б               |                                                                                                                                                            |

| 36         | P02/AN2       |                 |                                                                                                                                                            |

| 37         | P01/AN1       |                 |                                                                                                                                                            |

| 38         | P00/AN0       |                 |                                                                                                                                                            |

| 39         | AVss          | _               | A/D converter and D/A converter power supply pin (GND).                                                                                                    |

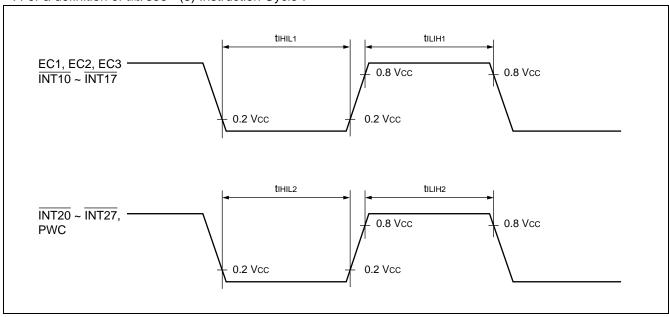

| 40         | P17/INT17     |                 |                                                                                                                                                            |

| 41         | P16/INT16     |                 |                                                                                                                                                            |

| 42         | P15/INT15     |                 | General purpose I/O ports.                                                                                                                                 |

| 43         | P14/INT14     | Е               | Also function as external interrupt 1 input pins.                                                                                                          |

| 44         | P13/INT13     |                 | External interrupt 1 input signals are hysteresis signals (edge detection).                                                                                |

| 45         | P12/INT12     |                 |                                                                                                                                                            |

| 46         | P11/INT11     |                 |                                                                                                                                                            |

| 47         | Vcc2          | _               | Power supply (5V) pin.                                                                                                                                     |

| 48         | P10/INT10     | Е               | General purpose I/O port. Also functions as an external interrupt 1 input pin. External interrupt 1 input signals are hysteresis signals (edge detection). |

| 49         | RST           | ı               | Reset input pin.                                                                                                                                           |

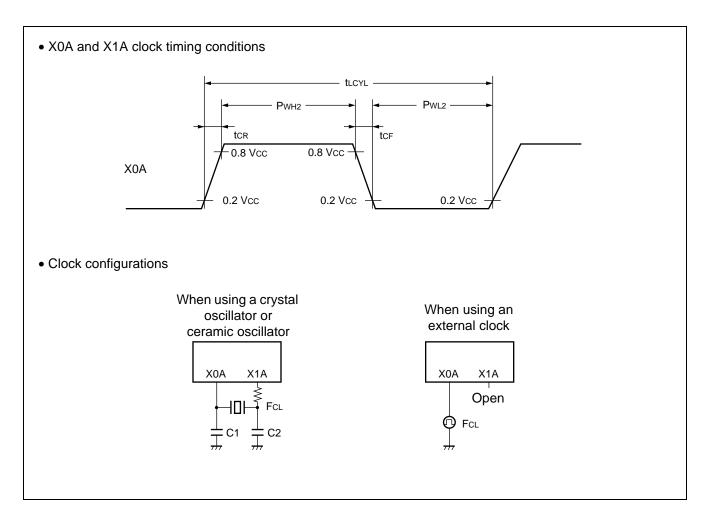

| 50         | X0A           | А               | Crystal oscillator pins (32 KHz) .                                                                                                                         |

| 51         | X1A           |                 | Oryotal Oscillator piris (02 ft 12).                                                                                                                       |

| Pin<br>No. | Pin Name             | Circuit<br>Type | Function                                                                                                                                                     |

|------------|----------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52         | MODA                 | F               | Operating mode setting pin.                                                                                                                                  |

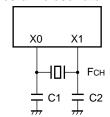

| 53         | X0                   | Α               | Crystal oscillator pins (Max12.5 MHz) .                                                                                                                      |

| 54         | X1                   | Α               | Orystal Oscillator pins (Max 12.3 Mil 12) .                                                                                                                  |

| 55         | P80/INT24            | E               | General purpose I/O port. Also functions as an external interrupt 2 input pin. External interrupt 2 input signals are hysteresis signals (level detection).  |

| 56         | Vss                  | _               | Power supply (GND) pin.                                                                                                                                      |

| 57         | P81/INT25            |                 | General purpose I/O ports.                                                                                                                                   |

| 58         | P82/INT26            | Е               | Also function as external interrupt 2 input pins.                                                                                                            |

| 59         | P83/INT27            |                 | External interrupt 2 input signals are hysteresis signals (level detection).                                                                                 |

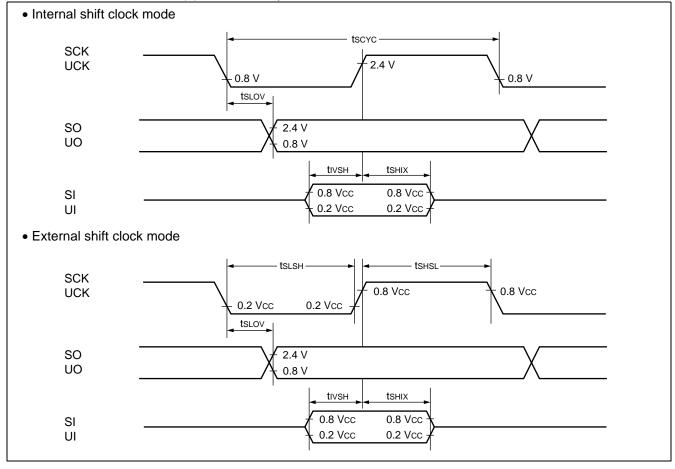

| 60         | P20/UI               | Е               |                                                                                                                                                              |

| 61         | P21/UO               | В               | General purpose I/O ports. Also function as 8-bit serial I/O pins.                                                                                           |

| 62         | P22/UCK              | Е               | This tariotion as a sit serial we pind.                                                                                                                      |

| 63         | P23/PPG1             | В               | General purpose I/O port. Also functions as the 6-bit PPG timer output.                                                                                      |

| 64         | P24/INT20            |                 |                                                                                                                                                              |

| 65         | P25/INT21            | _               | General purpose I/O ports. Also function as external interrupt 2 input pins. External interrupt 2 input signals are hysteresis signals (level detection).    |

| 66         | P26/INT22            | E               |                                                                                                                                                              |

| 67         | P27/INT23            |                 | , , , , , , , , , , , , , , , , , , , ,                                                                                                                      |

| 68         | P30                  | K               | N shapen drain I/O ning                                                                                                                                      |

| 69         | P31                  | K               | N-ch open drain I/O pins.                                                                                                                                    |

| 70         | DAOUT2               | С               | D/A converter output pins.                                                                                                                                   |

| 71         | DAOUT1               | C               | DIA Converter output pins.                                                                                                                                   |

| 72         | DVR                  |                 | D/A converter reference voltage input pin.                                                                                                                   |

| 73         | P84/TO21             | В               | General purpose I/O ports.                                                                                                                                   |

| 74         | P85/TO22             | Ь               | Also function as 8/16-bit timer pins.                                                                                                                        |

| 75         | P86/EC2/<br>LCLK     | E               | <ul> <li>P84 can be used as the output for the main clock×2 pulse.</li> <li>P86 can be used as the event counter input or sub-clock pulse output.</li> </ul> |

| 76         | P87/EC3              | E               | General purpose I/O port. Also functions as a 16-bit timer pin.                                                                                              |

| 77         | P40/TO11/<br>WTO     | D               | General purpose I/O ports.                                                                                                                                   |

| 78         | P41/TO12/<br>HCLK    | D12/ B Also     | Also function as 8/16-bit timer pins.                                                                                                                        |

| 79         | P42/<br>PWM1/<br>EC1 | E               | General purpose I/O ports. Also function as PWM timer pins.                                                                                                  |

| 80         | P43/PWM2             | В               |                                                                                                                                                              |

| Pin<br>No. | Pin Name | Circuit<br>Type | Function                                                       |  |

|------------|----------|-----------------|----------------------------------------------------------------|--|

| 81         | P44/SCK  | E               | General purpose I/O ports. Also function as UART pins.         |  |

| 82         | P45/SO   | В               |                                                                |  |

| 83         | P46/SI   | J               | raise ranousin as Gravit pine.                                 |  |

| 84         | P47/PWC  | J               | General purpose I/O port. Also functions as the PWC timer pin. |  |

| 85         | C1       |                 | Step-up voltage circuit capacitance connection pins.           |  |

| 86         | C0       |                 | Step-up voltage circuit capacitance connection pins.           |  |

| 87         | V0       |                 |                                                                |  |

| 88         | V1       |                 | LCD drive power supply pins                                    |  |

| 89         | V2       |                 | LCD drive power supply pins.                                   |  |

| 90         | V3       |                 |                                                                |  |

| 91         | COM0     |                 |                                                                |  |

| 92         | COM1     | Н               | Dedicated LCDC common output pins.                             |  |

| 93         | COM2     |                 | Dedicated ECDC common output pins.                             |  |

| 94         | COM3     |                 |                                                                |  |

| 95         | SEG00    |                 |                                                                |  |

| 96         | SEG01    | Н               | Dedicated LCDC segment output pins.                            |  |

| 97         | SEG02    |                 |                                                                |  |

| 98         | Vcc1     |                 | Power supply (3V) pin.                                         |  |

| 99         | SEG03    | Н               | Dedicated LCDC agament output ping                             |  |

| 100        | SEG04    |                 | Dedicated LCDC segment output pins.                            |  |

### ■ I/O CIRCUIT TYPES

| Туре | Circuit                                                                             | Remarks                                                                                                          |

|------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

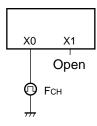

| А    | X1 (X1A)  X0 (X0A)  Main clock control signal (Sub-clock control signal)            | Oscillation feedback resistance • High speed side = approx. 1 $M\Omega$ • Low speed side = approx. 4.5 $M\Omega$ |

| В    | Pull-up control register  Input control signal                                      | • CMOS I/O                                                                                                       |

| С    | Output enable Analog output                                                         | D/A output                                                                                                       |

| D    | Pull-up control register  Pull-up control register  Port input signal  Analog input | A/D input     CMOS I/O                                                                                           |

| Туре | Circuit                                                                               | Remarks                                                              |

|------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| E    | Pull-up control register  Pull-up control register  Port input control Resource input | CMOS I/O     Hysteresis input (for external interrupt 0, 1, 2 input) |

| F    | Input                                                                                 | CMOS input                                                           |

| G    | Input control Port input signal                                                       | LCDC output     N-ch open drain I/O                                  |

| Н    |                                                                                       | LCDC output                                                          |

| I    | R Pch Nch Input                                                                       | Hysteresis input     Pull-up resistance                              |

| J    | Resource input Input control signal Port input                                        | Hysteresis input     N-ch open drain I/O  (Continued)                |

| Туре | Circuit                           | Remarks             |

|------|-----------------------------------|---------------------|

| К    | Input control signal — Port input | N-ch open drain I/O |

### **■ HANDLING DEVICES**

Maximum rated voltage (Prevention of latchup)

Be careful never to exceed maximum rated voltages.

In CMOS IC devices, a condition known as latch-up may occur if voltages higher than Vcc or loser than Vss are applied to input or output pins other than medium- or high-voltage pins, or if the voltage applied between Vcc and Vss exceeds the rated voltage level.

When latch-up occurs, the power supply current increases rapidly resulting in thermal damage to circuit elements. Therefore it is necessary to ensure that maximum ratings are not exceeded in circuit operation. Similarly, when turning the analog power supply on or off, it is necessary to ensure that the analog power supply voltages (AVcc, AVR, and DVR) and analog input voltages do not exceed the digital power supply (Vcc).

Power supply voltages

Power supply voltages should be kept as stable as possible.

Rapid fluctuation of the voltage may cause the device to operate abnormally, even if the voltage remains within the allowed operating range.

As a standard for power supply voltage stability, it is recommended that the peak-to-peak Vcc ripple voltage at commercial supply frequency (50 Hz to 60 Hz) be 10% or less of Vcc. Also when the power supply is turned on or off the transient voltage fluctuation be no more than 0.1V/ms or less.

- Treatment of unused input pins

Leaving unused input pins unconnected can cause abnormal operation. Unused input pins should always be pulled up or down.

- Treatment of N.C. pins

N.C. (not connected) pins should always be left open.

- Treatment of power supply pins on devices with A/D or D/A converters

Even when the A/D or D/A converters are not in use, be sure to make the necessary connections to ensure that AVcc = Vcc, AVss = AVR = DVR = Vss.

- Precautions on using an external clock

An oscillation stabilization delay occurs after a power-on reset or when recovering from sub-clock or stop mode, even if an external clock is used.

- Treatment of unused dedicated LCD pins

Dedicated SEG output pins should be left open when not in use.

- Handling of ports also used as segment pins

When a ports is used as a segment pin, take care to ensure that the voltage applied to the pin does not exceed

V3 (the segment drive voltage). This precaution is particularly necessary in models with step-up voltage circuits.

Note also that after power-on or during a reset, an "L" level default signal is output form the segment/port pin.

- Treatment of unused LCD pins

Connect the V3 pin to Vcc2. The other dedicated LCD pins V0, V1, V2, C0, and C1 should be pulled down.

- Executing programs on RAM

When programs are executed on RAM, debugging cannot be performed even with the use of the MB89PV550A.

- Wild register functions

Wild registers cannot be debugged with the MB89PV550A or tools. To verify operation, use the MB89P558A and perform in-place testing.

### ■ PROGRAMMING SPECIFICATIONS FOR ONE-TIME PROM PRODUCTS

The MB89P558A has a "PROM mode" with functions equivalent to the MBM27C1001, that enables the micro-controller to be programmed by writing from a general-purpose ROM programmer with the use of a special adapter. Note however that electronic signature mode is not available.

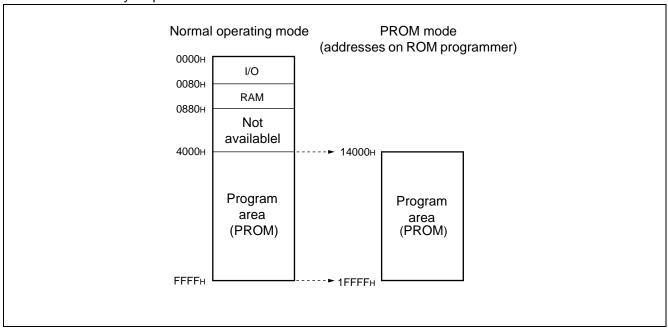

PROM Mode Memory Map

The PROM mode memory map is shown below.

### **PROM Mode Memory Map**

- EPROM Programming Procedure

- 1) Set the EPROM programmer type to MBM27C1001.

- 2) Load the program data into addresses 14000H to 1FFFFH in the EPROM programmer.

- 3) Use the EPROM programmer to program to addresses 14000H to 1FFFFH.

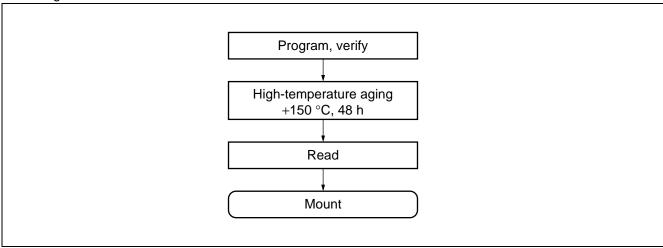

- Recommended Screening Conditions

High-temperature aging is the recommended method of screening unprogrammed one-time PROM microcontrollers before mounting.

The flow of the screening process is shown below.

#### Screening Flow

### • About Writing Yields

The nature of chips before one-time writing of microcontroller programs to PROM prevents the use of all-bit writing tests. Therefore it is not possible to guarantee writing yields of 100% in some cases.

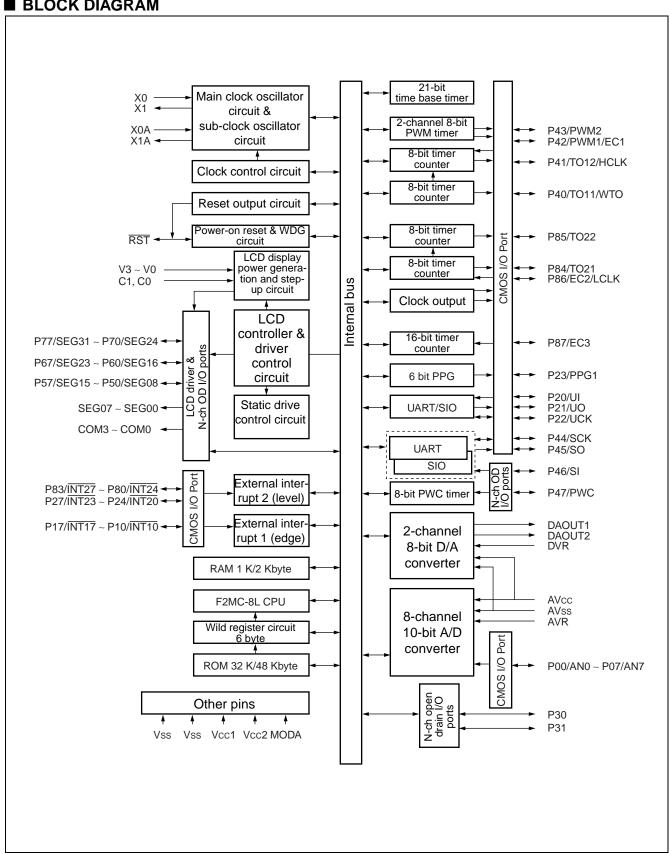

### **■ BLOCK DIAGRAM**

### **■ CPU CORE**

#### Memory space

The MB89550A has 64 Kbytes of memory space, composed of the I/O area, RAM area, ROM area, and external area. The memory space includes general purpose registers, as well as areas used for special purposes such as vector tables.

- I/O Area (address : 0000н to 007Fн)

- This area is allocated to control registers and data registers for internal peripheral functions.

- Because the I/O area is part of memory space, it can be accessed in the same ways. Direct addressing provides faster access.

#### RAM Area

- Static RAM is provided for use as an internal data area.

- The size of internal RAM differs between product models.

- High speed access is available to addresses 80H to FFH using direct addressing (the area available for use is restricted on some models).

- Addresses 100<sub>H</sub> to 1FF<sub>H</sub> are used as the general-purpose register area.

- If a reset is applied during writing to RAM, the value of date at the target addresses is not assured.

#### ROM Area

- ROM is provided for use as the internal program area.

- The size of internal ROM differs between product models.

- Addresses FFC0H to FFFFH are used for special purpose data such as vector tables.

#### Memory Map

### ■ I/O MAP

| Address    | Abbreviation | Resister Name                                           | Read/Write | Initial Value              |  |  |  |  |

|------------|--------------|---------------------------------------------------------|------------|----------------------------|--|--|--|--|

| 00н        | PDR0         | Port 0 data register                                    | R/W        | XXXXXXXX                   |  |  |  |  |

| 01н        | DDR0         | Port 0 direction register                               | W          | 0000000B                   |  |  |  |  |

| 02н        | PDR1         | Port 1 data register                                    | R/W        | XXXXXXXX                   |  |  |  |  |

| 03н        | DDR1         | Port 1 direction register                               | W          | 0000000                    |  |  |  |  |

| 04н to 06н | Unused area  |                                                         |            |                            |  |  |  |  |

| 07н        | SYCC         | System clock control register                           | R/W        | XXX MM1 0 0 <sub>B</sub>   |  |  |  |  |

| 08н        | STBC         | Standby control register                                | R/W        | 00010XXXB                  |  |  |  |  |

| 09н        | WDTC         | Watchdog control register                               | R/W        | 0XXXXXXXB                  |  |  |  |  |

| ОАн        | TBTC         | Time base time control register                         | R/W        | X 0 XXX 0 0 0 <sub>B</sub> |  |  |  |  |

| 0Вн        | WPCR         | Watch prescaler control register                        | R/W        | X0XX0000B                  |  |  |  |  |

| 0Сн        | PDR2         | Port 2 data register                                    | R/W        | XXXXXXXX                   |  |  |  |  |

| 0Дн        | DDR2         | Port 2 direction register                               | R/W        | 0000000B                   |  |  |  |  |

| 0Ен        | PDR3         | Port 3 data register                                    | R/W        | 1 1в                       |  |  |  |  |

| 0Fн        | PDR4         | Port 4 data register                                    | R/W        | 1 1 XXXXXX                 |  |  |  |  |

| 10н        | DDR4         | Port 4 direction register                               | R/W        | 000000в                    |  |  |  |  |

| 11н        | PDR5         | Port 5 data register                                    | R/W        | 00000000                   |  |  |  |  |

| 12н        |              | Unused area                                             |            |                            |  |  |  |  |

| 13н        | PDR6         | Port 6 data register                                    | R/W        | 0000000B                   |  |  |  |  |

| 14н        |              | Unused area                                             |            |                            |  |  |  |  |

| 15н        | PDR7         | Port 7 data register                                    | R/W        | 0000000B                   |  |  |  |  |

| 16н        |              | Unused area                                             |            |                            |  |  |  |  |

| 17н        | PDR8         | Port 8 data register                                    | R/W        | XXXXXXXX                   |  |  |  |  |

| 18н        | DDR8         | Port 8 direction register                               | R/W        | 0000000B                   |  |  |  |  |

| 19н        |              | Unused area                                             |            |                            |  |  |  |  |

| 1Ан        | T2CR#2       | Timer 2 control register # 2(8/16-bit timer/counter -1) | R/W        | X00000X0 <sub>B</sub>      |  |  |  |  |

| 1Вн        | T1CR#1       | Timer 1 control register # 1(8/16-bit timer/counter -1) | R/W        | X00000X0 <sub>B</sub>      |  |  |  |  |

| 1Сн        | T2DR#2       | Timer 2 data register # 2(8/16-bit timer/counter -1)    | R/W        | XXXXXXXXB                  |  |  |  |  |

| 1Dн        | T1DR#1       | Timer 1 data register # 1(8/16-bit timer/counter -1)    | R/W        | XXXXXXXX                   |  |  |  |  |

| 1Ен        | T2CR#4       | Timer 2 control register # 4(8/16-bit timer/counter -2) | R/W        | X00000X0 <sub>B</sub>      |  |  |  |  |

| 1Fн        | T1CR#3       | Timer 1 control register # 3(8/16-bit timer/counter -2) | R/W        | X00000X0 <sub>B</sub>      |  |  |  |  |

| 20н        | T2DR#4       | Timer 2 data register # 4(8/16-bit timer/counter -2)    | R/W        | XXXXXXXXB                  |  |  |  |  |

| 21н        | T1DR#3       | Timer 1 data register # 3(8/16-bit timer/counter -2)    | R/W        | XXXXXXXXB                  |  |  |  |  |

| 22н        | SMC1         | Serial mode control register 1 (UART)                   | R/W        | 00000000                   |  |  |  |  |

| 23н        | SRC1         | Serial rate control register (UART)                     | R/W        | 011000в                    |  |  |  |  |

| Address            | Abbreviation    | Resister Name                                       | Read/Write | Initial Value               |

|--------------------|-----------------|-----------------------------------------------------|------------|-----------------------------|

| 24н                | SSD1            | Serial status and data register (UART)              | R/W        | 00100-1X <sub>B</sub>       |

| 25н                | SIDR1/<br>SODR1 | Serial input/serial output data register (UART)     | R/W        | XXXXXXXXB                   |

| 26н                | SMC2            | Serial mode control register 2 (UART)               | R/W        | 100001в                     |

| 27н                | CNTR1           | PWM control register 1                              | R/W        | 00000000                    |

| 28н                | CNTR2           | PWM control register 2                              | R/W        | 000X0000B                   |

| 29н                | CNTR3           | PWM control register 3                              | R/W        | X 0 0 0 XXXXB               |

| 2Ан                | COMR1           | PWM compare register 1                              | W          | XXXXXXXXB                   |

| 2Вн                | COMR2           | PWM compare register 2                              | W          | XXXXXXXXB                   |

| 2Сн                | PCR1            | PWC pulse width control register 1                  | R/W        | 000 XX 000B                 |

| 2Dн                | PCR2            | PWC pulse width control register 2                  | R/W        | 0000000                     |

| 2Ен                | PLBR            | PWC reload buffer register                          | R/W        | XXXXXXXXB                   |

| 2Fн                | SMC21           | Serial mode control register 1 (UART/SIO)           | R/W        | 00000000                    |

| 30н                | SMC22           | Serial rate control register 2 (UART/SIO)           | R/W        | 00000000                    |

| 31н                | SSD2            | Serial status and data register (UART/SIO)          | R/W        | 00001XXX <sub>B</sub>       |

| 32н                | SIDR2/<br>SODR2 | Serial input/serial output date register (UART/SIO) | R/W        | XXXXXXXXB                   |

| 33н                | SRC2            | Baud rate generator reload register (UART/SIO)      |            | XXXXXXXXB                   |

| 34н                | ADC1            | A/D control register 1                              | R/W        | 00000000                    |

| 35н                | ADC2            | A/D control register 2                              | R/W        | Х 0 0 0 0 0 1в              |

| 36н                | ADDL            | A/D data register low                               | R/W        | XXXXXXXX                    |

| 37н                | ADDH            | A/D data register high                              | R/W        | 000000 XX <sub>B</sub>      |

| 38н to 3Вн         |                 | Unused area                                         |            | •                           |

| 3Сн                | TMCR            | Timer control register (16-bit timer/counter)       | R/W        | XX 0 0 0 0 0 0 <sub>B</sub> |

| 3Dн                | TCHR            | Timer count register high (16-bit timer/counter)    | R/W        | 0000000B                    |

| 3Ен                | TCLR            | Timer count register low (16-bit timer/counter)     | R/W        | 00000000                    |

| 3Fн                | EIC1            | External interrupt register 1                       | R/W        | 00000000                    |

| 40н                | EIC2            | External interrupt register 2                       | R/W        | 00000000                    |

| 41н                | EIC3            | External interrupt register 3                       | R/W        | 0000000                     |

| 42н                | EIC4            | External interrupt register 4                       | R/W        | 0000000                     |

| 43н                | DACR            | D/A control register                                | R/W        | XXXXXX 0 0 <sub>B</sub>     |

| 44н                | DADR1           | D/A data register 1                                 | R/W        | XXXXXXXXB                   |

| 45н                | DADR2           | D/A data register 2                                 | R/W        | XXXXXXXXB                   |

| <b>46</b> н to 55н |                 | Unused area                                         |            | •                           |

| 56н                | EIE2            | External interrupt 2 control register               | R/W        | 00000000B                   |

| Address     | Abbreviation | Resister Name                                    | Read/Write | Initial Value           |

|-------------|--------------|--------------------------------------------------|------------|-------------------------|

| 57н         | EIF2         | External interrupt 2 flag register               | R/W        | XXXXXXX 0 <sub>B</sub>  |

| 58н         | RCR1         | 6-bit PPG control register 1                     | R/W        | 00000000                |

| 59н         | RCR2         | 6-bit PPG control register 2                     | R/W        | 0-00000 <sub>B</sub>    |

| 5Ан         | CKR          | Clock output control register                    | R/W        | XXXXXX 0 0 <sub>B</sub> |

| 5Вн         | LCR1         | LCDC control register 1                          | R/W        | 00010000в               |

| 5Сн         | LCR2         | LCDC control register 2                          | R/W        | 00000000                |

| 5Dн         | LCR3         | LCDC control register 3                          | R/W        | 00000в                  |

| <b>5Е</b> н | LCD1         | LCD static display register 1                    | R/W        | XXXXXXXXB               |

| <b>5</b> Fн | LCD2         | LCD static display register 2                    | R/W        | XXXXXXXXB               |

| 60н to 6Fн  | VRAM         | LCD display RAM                                  | R/W        | XXXXXXXXB               |

| 70н         | SMR          | Serial mode register (8-bit serial I/O)          | R/W        | 00000000                |

| 71н         | SDR          | Serial data register (8-bit serial I/O)          | R/W        | XXXXXXXX                |

| 72н         | PORR0        | Port 0 pull-up option setting register           | R/W        | 11111111                |

| 73н         | PURR1        | Port 1 pull-up option setting register           | R/W        | 11111111                |

| <b>74</b> H | PURR2        | Port 2 pull-up option setting register           | R/W        | 11111111в               |

| 75н         | PURR4        | Port 4 pull-up option setting register           | R/W        | 11111111                |

| 76н         | PURR8        | Port 8 pull-up option setting register           | R/W        | 11111111                |

| <b>77</b> н | WREN         | Wild register/address comparator enable register | R/W        | 000000в                 |

| 78н         |              | Unused area                                      |            |                         |

| 79н         | ADEN         | A/D port input enable register                   | R/W        | 11111111                |

| 7Ан         |              | Unused area                                      | •          | •                       |

| 7Вн         | ILR1         | Interrupt level setting register 1               | W          | 11111111В               |

| 7Сн         | ILR2         | Interrupt level setting register 2               | W          | 11111111В               |

| 7Dн         | ILR3         | Interrupt level setting register 3               | W          | 11111111В               |

| <b>7</b> Ен | ILR4         | Interrupt level setting register 4               | W          | 11111111В               |

| <b>7</b> Fн |              | Unused area                                      | •          | •                       |

### • Extended I/O Area

| Address | Abbreviation | Resister Name                | Read/Write | Initial Value |

|---------|--------------|------------------------------|------------|---------------|

| 480н    | WRARH1       | H address setting register 1 | R/W        | XXXXXXXX      |

| 481н    | WRARL1       | L address setting register 1 | R/W        | XXXXXXXX      |

| 482н    | WRDR1        | Data setting register 1      | W          | XXXXXXXX      |

| 483н    | WRARH2       | H address setting register 2 | R/W        | XXXXXXXX      |

| 484н    | WRARL2       | L address setting register 2 | R/W        | XXXXXXXX      |

| 485н    | WRDR2        | Data setting register 2      | W          | XXXXXXXX      |

| 486н    | WRARH3       | H address setting register 3 | R/W        | XXXXXXXX      |

| 487н    | WRARL3       | L address setting register 3 | R/W        | XXXXXXXX      |

| 488н    | WRDR3        | Data setting register 3      | W          | XXXXXXXX      |

| 489н    | WRARH4       | H address setting register 4 | R/W        | XXXXXXXX      |

| 48Ан    | WRARL4       | L address setting register 4 | R/W        | XXXXXXXX      |

| 48Вн    | WRDR4        | Data setting register 4      | W          | XXXXXXXX      |

| 48Сн    | WRARH5       | H address setting register 5 | R/W        | XXXXXXXX      |

| 48Dн    | WRARL5       | L address setting register 5 | R/W        | XXXXXXXX      |

| 48Ен    | WRDR5        | Data setting register 5      | W          | XXXXXXXX      |

| 48Гн    | WRARH6       | H address setting register 6 | R/W        | XXXXXXXX      |

| 490н    | WRARL6       | L address setting register 6 | R/W        | XXXXXXXX      |

| 491н    | WRDR6        | Data setting register 6      | W          | XXXXXXXX      |

### O Read/write notation

• R/W : Reading and writing enabled

R : Read-onlyW : Write onlyO Initial value notation

0 : Initial value of bit is "0".1 : Initial value of bit is "1".

• X : Initial value of bit is undefined.

Note: Areas indicated as "unused area" are not to be used.

### **■ ELECTRICAL CHARACTERISTICS**

### 1. Absolute Maximum Ratings

(AVss = Vss = 0 V)

| Donomoton                              | O make al       | Ra        | ting       | 11!4     | Bowenter                                                                                        |

|----------------------------------------|-----------------|-----------|------------|----------|-------------------------------------------------------------------------------------------------|

| Parameter                              | Symbol          | Min       | Max        | Unit     | Remarks                                                                                         |

| Dower oupply voltage                   | Vcc1            | Vss - 0.3 | Vss + 4.0  | V        |                                                                                                 |

| Power supply voltage                   | Vcc2            | Vss - 0.3 | Vss + 6.0  | V        |                                                                                                 |

| A/D converter reference input voltage  | AVR             | Vss - 0.3 | Vss + 6.0  | V        | Vcc1 not to exceed Vcc2.*                                                                       |

| D/A converter reference input voltage  | DVR             | Vss - 0.3 | Vss + 6.0  | <b>V</b> |                                                                                                 |

| LCD power supply voltage               | V0-V3           | Vss - 0.3 | Vss + 6.0  | V        | On models without step-up circuits V0-V3 are not to exceed Vcc2.                                |

| Input voltage                          | VI1             | Vss - 0.3 | Vcc2 + 0.3 | V        | Pins other than P50 to P57, P60 to P67, P70 to P77, P46, P47, P30, P31                          |

| 1 1 1 1 1 1 1                          | V <sub>I2</sub> | Vss - 0.3 | V3         | V        | P50 to P57, P60 to P67, P70 to P77                                                              |

|                                        | Vıз             | Vss - 0.3 | Vss + 6.0  | V        | P46, P47, P30, P31                                                                              |

| Output voltage                         | V <sub>O1</sub> | Vss - 0.3 | Vcc2       | V        | Pins other than P50 to P57, P60 to P67, P70 to P77, P46, P47, P30, P31                          |

| o a.p.a. vollage                       | V <sub>O2</sub> | Vss - 0.3 | V3         | V        | P50 to P57, P60 to P67, P70 to P77                                                              |

|                                        | Vоз             | Vss - 0.3 | Vss + 6.0  | V        | P46, P47, P30, P31                                                                              |

| "L" level maximum output current       | lol1            |           | 15         | mA       | Pins other than P22/UCK, P23/<br>PPG1                                                           |

| Current                                | lol2            | _         | 30         | mA       | P22/UCK, P23/PPG1                                                                               |

| "L" level average output               | lolav1          | I         | 4          | mA       | Pins other than P22/UCK, P23/<br>PPG1<br>average value<br>(operating current × operating ratio) |

| Current                                | lolav2          |           | 15         | mA       | P22/UCK, P23/PPG1<br>average value<br>(operating current × operating ratio)                     |

| "L" level total maximum output current | ΣΙοι            | _         | 100        | mA       |                                                                                                 |

| "L" level total average output current | ΣIOLAV          | _         | 60         | mA       | average value (operating current × operating ratio)                                             |

| "H" level maximum output               | Іон1            | _         | -15        | mA       | Pins other than P22/UCK, P23/<br>PPG1                                                           |

| current                                | <b>І</b> он2    | _         | -30        | mA       | P22/UCK, P23/PPG1                                                                               |

|                                        |                 |           |            |          |                                                                                                 |

### (Continued)

| Parameter                              | Symbol   | Rat        | ing  | Unit  | Remarks                                                                                                                    |

|----------------------------------------|----------|------------|------|-------|----------------------------------------------------------------------------------------------------------------------------|

| raiametei                              | Syllibol | Min        | Max  | Oille | Kemarks                                                                                                                    |

| "H" level average output               | Гонач    |            | -4   | mA    | Pins other than P22/UCK, P23/<br>PPG1 and open drain output pins<br>average value<br>(operating current × operating ratio) |

| current                                | Іонач    | _          | -15  | mA    | P22/UCK, P23/PPG1<br>average value<br>(operating current × operating ratio)                                                |

| "H" level total maximum output current | ΣІон     | _          | -50  | mA    |                                                                                                                            |

| "H" level total average output current | ΣΙομαν   | _          | -30  | mA    | average value (operating current × operating ratio)                                                                        |

| Power consumption                      | P□       | _          | 300  | mW    |                                                                                                                            |

| Operating temperature                  | Та       | -40        | +85  | °C    |                                                                                                                            |

| Storage temperature                    | Tstg     | <b>-55</b> | +150 | °C    |                                                                                                                            |

$<sup>^{\</sup>star}$  : Set AVcc to the same potential as Vcc. Also ensure that AVR and DVR do not exceed AVcc + 0.3 V.

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

### 2. Recommended Operating Conditions

(AVss = Vss = 0 V)

| Item                                    | Symbol           | Rat   | ing  | Unit  | Remark                                                                                                                                                         |

|-----------------------------------------|------------------|-------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| item                                    | Зуппоот          | Min   | Max  | Oilit | Kellark                                                                                                                                                        |

|                                         | V <sub>CC1</sub> | 2.2*1 | 3.6  | V     | Guaranteed normal operating range                                                                                                                              |

|                                         | V <sub>CC2</sub> | 2.2*1 | 5.5  | V     | (MB89557A/558A)                                                                                                                                                |

| Power supply voltage*3                  | V <sub>CC1</sub> | _     | _    | V     | Guaranteed normal operating range                                                                                                                              |

|                                         | V <sub>CC2</sub> | 2.7*2 | 5.5  | V     | (MB89P558A)                                                                                                                                                    |

|                                         | Vcc1, Vcc2       | 1.5   | 3.6  | V     | To maintain RAM state in stop mode                                                                                                                             |

| A/D converter reference voltage input*4 | AVR              | Vcc1  | AVcc | V     | Guaranteed normal operating range                                                                                                                              |

| D/A converter reference voltage input*4 | DVR              | Vcc1  | AVcc | V     | Guaranteed normal operating range                                                                                                                              |

| LCD supply voltage                      | V0-V3            | Vss   | Vcc2 | V     | Models without step-up circuit, pins V0 to V3. LCD power supply range and maximum value are determined by the characteristics of the LCD display element used. |

| Operating temperature                   | TA               | -40   | +85  | °C    |                                                                                                                                                                |

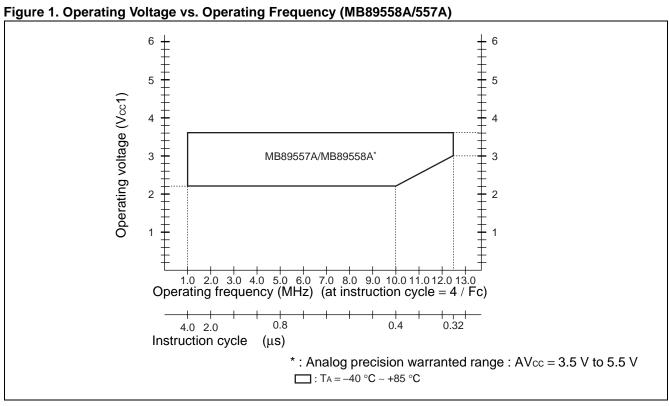

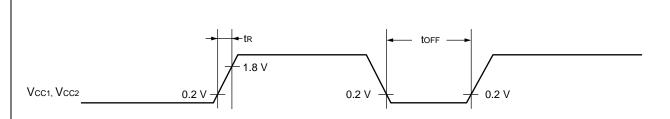

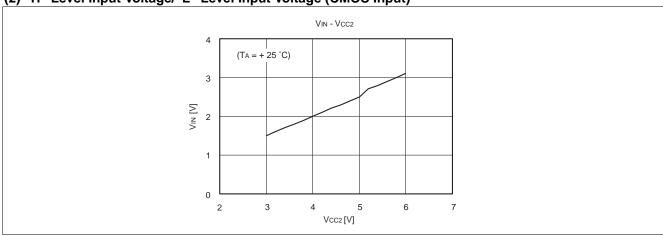

<sup>\*1 :</sup> The operating power supply voltage differs depending on the instruction cycle time of the operating frequency. See Figure 1.

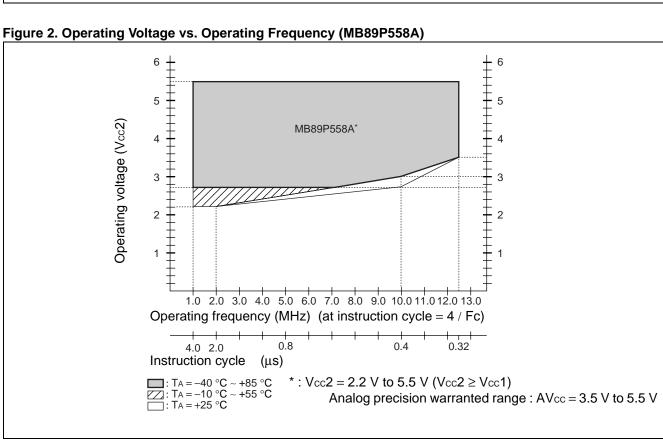

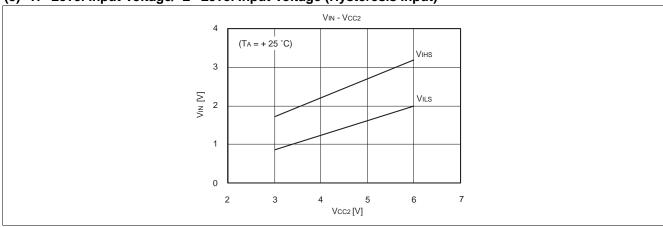

<sup>\*2 :</sup> The operating power supply voltage differs depending on the instruction cycle time of the operating frequency. See Figure 2. Note also that on the MB89PV550A the input to the Vcc1 pin is cut off internally, and on the MB89P558A the Vcc1 pin is used as the VPP pin for on-board writing.

<sup>\*3 :</sup> AVcc and Vcc2 should be set to the same potential. Also, care must be taken to ensure that Vcc1 does not exceed Vcc2

<sup>\*4 :</sup> Care must be taken to ensure that the relation between AVR and DVR is such that " $Vcc1 \le AVR$  (DVR)  $\le AVcc + 0.3 V$ ".

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

> Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their representatives beforehand.

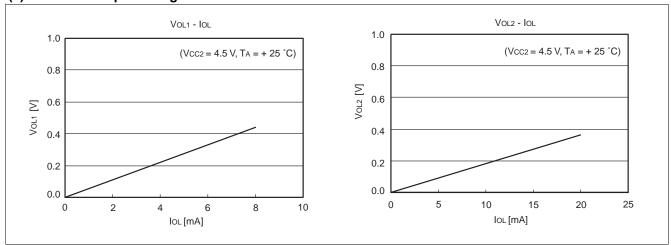

### 3. DC Characteristics

(AVcc = AVR = DVR = Vcc2 = 5.0 V, AVss = Vss = 0 V,  $T_A = -40~^{\circ}C$  to +85  $^{\circ}C$ )

|                                                        | Sym-              |                                                                                                                                |                         |           | Value |            |      | <u> </u>                                 |

|--------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------|-------|------------|------|------------------------------------------|