## 3.3 V Zero Delay Buffer

MPC962304

The MPC962304 is a 3.3 V Zero Delay Buffer designed to distribute high-speed clocks in PC, workstation, datacom, telecom and other high-performance applications. The MPC962304 uses an internal PLL and an external feedback path to lock its low-skew clock output phase to the reference clock phase, providing virtually zero propagation delay. The input-to-output skew is guaranteed to be less than 250 ps and output-to-output skew is guaranteed to be less than 200 ps.

#### Features

- 1:4 outputs LVCMOS zero-delay buffer

- Zero input-output propagation delay, adjustable by the capacitive load on FBK input

- Multiple Configurations, See Table 1. Available MPC962304

Configurations

- Multiple low-skew outputs

- 200 ps max output-output skew

- 500 ps max device-device skew

- Supports a clock I/O frequency range of 10 MHz to 133 MHz

- Low jitter, 200 ps max cycle-cycle

- 8-pin SOIC package

- Single 3.3 V supply

- Ambient temperature range: –40°C to +85°C

- · Compatible with the CY2304

#### **Functional Description**

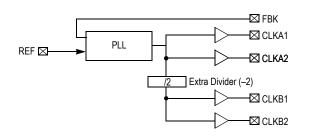

The MPC962304 has two banks of two outputs each. The MPC962304 PLL enters a power down state when there are no rising edges on the REF input. During this state, all of the outputs are in tristate. When the PLL is turned off, there is less than 25  $\mu$ A of current draw.

Multiple MPC962304 devices can accept and distribute the same input clock throughout the system. In this situation, the difference between the output skews of two devices will be less than 500 ps.

The MPC962304 is offered in two configurations. In the -1 version, the reference frequency is reproduced by the PLL and provided to the outputs.

The MPC962304-2 provides 1/2X and 2X the reference frequency at the output banks.

#### **Block Diagram**

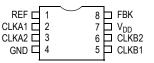

#### **Pin Configuration**

8-pin SOIC Top View

D SUFFIX PLASTIC SOIC PACKAGE CASE 751-06

#### Table 1. Available MPC962304 Configurations

| Device      | Feedback From    | Bank A Frequency | Bank B Frequency |

|-------------|------------------|------------------|------------------|

| MPC962304-1 | Bank A or Bank B | Reference        | Reference        |

| MPC962304-2 | Bank A           | Reference        | Reference/2      |

| MPC962304-2 | Bank B           | 2 X Reference    | Reference        |

#### Table 2. Pin Description

| Pin | Signal             | Description                                   |  |

|-----|--------------------|-----------------------------------------------|--|

| 1   | REF <sup>1</sup>   | Input reference frequency, 5 V tolerant input |  |

| 2   | CLKA1 <sup>2</sup> | Clock output, Bank A                          |  |

| 3   | CLKA2 <sup>2</sup> | Clock output, Bank A                          |  |

| 4   | GND                | Ground                                        |  |

| 5   | CLKB1 <sup>2</sup> | Clock output, Bank B                          |  |

| 6   | CLKB2 <sup>2</sup> | Clock output, Bank B                          |  |

| 7   | V <sub>DD</sub>    | 3.3 V supply                                  |  |

| 8   | FBK                | PLL feedback input                            |  |

1. Weak pull-down.

2. Weak pull-down on all outputs.

#### Table 3. Maximum Ratings

| Characteristics                                         | Value                        | Unit |

|---------------------------------------------------------|------------------------------|------|

| Supply Voltage to Ground Potential                      | -0.5 to +3.9                 | V    |

| DC Input Voltage (Except REF)                           | –0.5 to V <sub>DD</sub> +0.5 | V    |

| DC Input Voltage REF                                    | -0.5 to 5.5                  | V    |

| Storage Temperature                                     | -65 to +150                  | °C   |

| Junction                                                | 150                          | °C   |

| Static Discharge Voltage (per MIL-STD-883, Method 3015) | >2000                        | V    |

| Table 4. Operating | Conditions for MPC9623 | 304-X Industrial Temper | ature Devices |

|--------------------|------------------------|-------------------------|---------------|

|                    |                        |                         |               |

| Parameter       | Description                                        | Min | Мах | Unit |

|-----------------|----------------------------------------------------|-----|-----|------|

| V <sub>DD</sub> | Supply Voltage                                     | 3.0 | 3.6 | V    |

| Τ <sub>Α</sub>  | Operating Temperature (Ambient Temperature) -40 85 |     | °C  |      |

| CL              | Load Capacitance, below 100 MHz                    |     | 30  | pF   |

|                 | Load Capacitance, from 100 MHz to 133 MHz          |     | 15  | pF   |

| C <sub>IN</sub> | Input Capacitance <sup>1</sup>                     |     | 7   | pF   |

1. Applies to both REF clock and FBK.

#### Table 5. Electrical Characteristics for MPC962304-X Industrial Temperature Devices<sup>1</sup>

| Parameter                 | Description                      | Test Conditions                                             | Min | Max.  | Unit |

|---------------------------|----------------------------------|-------------------------------------------------------------|-----|-------|------|

| V <sub>IL</sub>           | Input LOW Voltage                |                                                             |     | 0.8   | V    |

| V <sub>IH</sub>           | Input HIGH Voltage               |                                                             | 2.0 |       | V    |

| Ι <sub>ΙL</sub>           | Input LOW Current                | V <sub>IN</sub> = 0 V                                       |     | 50.0  | μA   |

| Ι <sub>ΙΗ</sub>           | Input HIGH Current               | V <sub>IN</sub> = V <sub>DD</sub>                           |     | 100.0 | μA   |

| V <sub>OL</sub>           | Output LOW Voltage <sup>2</sup>  | I <sub>OL</sub> = 8 mA (-1, -2)                             |     | 0.4   | V    |

| V <sub>OH</sub>           | Output HIGH Voltage <sup>2</sup> | I <sub>OH</sub> = -8 mA (-1, -2)                            | 2.4 |       | V    |

| I <sub>DD</sub> (PD mode) | Power Down Supply Current        | REF = 0 MHz                                                 |     | 25.0  | μA   |

| I <sub>DD</sub>           | Supply Current                   | Unloaded outputs, 100 MHz, Select inputs at $V_{DD}$ or GND |     | 45.0  | mA   |

|                           |                                  | Unloaded outputs, 66-MHz REF<br>(-1, -2)                    |     | 35.0  | mA   |

|                           |                                  | Unloaded outputs, 35-MHz REF<br>(-1, -2)                    |     | 20.0  | mA   |

1. All parameters are specified with loaded outputs.

2. Parameter is guaranteed by design and characterization. Not 100% tested in production.

| Parameter         | Name                                                     | Test Conditions                                                    | Min  | Тур | Max   | Unit |

|-------------------|----------------------------------------------------------|--------------------------------------------------------------------|------|-----|-------|------|

| t <sub>1</sub>    | Output Frequency                                         | 30-pF load, all devices                                            | 10   |     | 100   | MHz  |

|                   | Output Frequency                                         | 15-pF load, all devices                                            | 10   |     | 133.3 | MHz  |

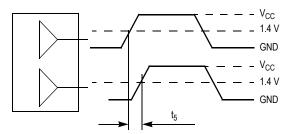

|                   | Duty Cycle <sup>2</sup> = $t_2 \div t_1$<br>(-1, -2)     | Measured at 1.4 V, FOUT = 66.66 MHz<br>30-pF load                  | 40.0 |     | 60.0  | %    |

|                   | Duty Cycle <sup>2</sup> = $t_2 \div t_1$<br>(-1, -2)     | Measured at 1.4 V, FOUT < 50.0 MHz<br>15-pF load                   | 45.0 |     | 55.0  | %    |

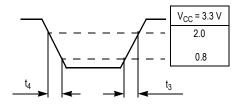

| t <sub>3</sub>    | Rise Time <sup>2</sup><br>(-1, -2)                       | Measured between 0.8 V and 2.0 V,<br>30-pF load                    |      |     | 2.50  | ns   |

|                   | Rise Time <sup>2</sup><br>(-1, -2)                       | Measured between 0.8 V and 2.0 V,<br>15-pF load                    |      |     | 1.50  | ns   |

| t <sub>4</sub>    | Fall Time <sup>2</sup><br>(-1, -2)                       | Measured between 0.8 V and 2.0 V,<br>30-pF load                    |      |     | 2.50  | ns   |

|                   | Fall Time <sup>2</sup><br>(-1, -2)                       | Measured between 0.8 V and 2.0 V,<br>15-pF load                    |      |     | 1.50  | ns   |

| t <sub>5</sub>    | Output to Output Skew on same Bank (-1, -2) <sup>2</sup> | All outputs equally loaded                                         |      |     | 200   | ps   |

|                   | Output Bank A to Output<br>Bank B Skew (-1)              | All outputs equally loaded                                         |      |     | 200   | ps   |

|                   | Output Bank A to Output<br>Bank B Skew (-2)              | All outputs equally loaded                                         |      |     | 400   | ps   |

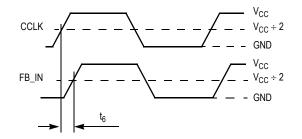

| t <sub>6</sub>    | Delay, REF Rising Edge to FBK Rising Edge <sup>2</sup>   | Measured at $V_{DD}/2$                                             |      | 0   | ±250  | ps   |

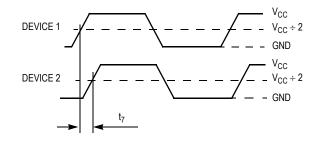

| t <sub>7</sub>    | Device to Device Skew <sup>2</sup>                       | Measured at V <sub>DD</sub> /2 on the FBK pins of devices          |      | 0   | 500   | ps   |

| tj                | Cycle to Cycle Jitter <sup>2</sup><br>(-1)               | Measured at 66.67 MHz, loaded outputs, 15-pF load                  |      |     | 180   | ps   |

|                   |                                                          | Measured at 66.67 MHz, loaded outputs, 30-pF load                  |      |     | 200   | ps   |

|                   |                                                          | Measured at 133.3 MHz, loaded outputs, 15 pF load                  |      |     | 100   | ps   |

| tj                | Cycle to Cycle Jitter <sup>2</sup><br>(-2)               | Measured at 66.67 MHz, loaded outputs 30-pF load                   |      |     | 400   | ps   |

|                   |                                                          | Measured at 66.67 MHz, loaded outputs<br>15-pF load                |      |     | 380   | ps   |

| t <sub>LOCK</sub> | PLL Lock Time <sup>2</sup>                               | Stable power supply, valid clocks presented<br>on REF and FBK pins |      |     | 1.0   | ms   |

#### Table 6. Switching Characteristics for MPC962304-X Industrial Temperature Devices<sup>1</sup>

1. All parameters are specified with loaded outputs.

2. Parameter is guaranteed by design and characterization. Not 100% tested in production.

#### **APPLICATIONS INFORMATION**

The pin-to-pin skew is defined as the worst case difference in propagation delay between any similar delay path within a single device

#### Figure 1. Output-to-Output Skew t<sub>SK(O)</sub>

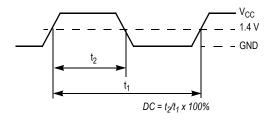

The time from the PLL controlled edge to the non-controlled edge, divided by the time between PLL controlled edges, expressed as a percentage

#### Figure 3. Output Duty Cycle (DC)

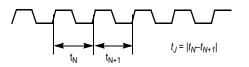

The variation in cycle time of a signal between adjacent cycles, over a random sample of adjacent cycle pairs

#### Figure 5. Cycle-to-Cycle Jitter

#### Figure 2. Static Phase Offset Test Reference

Figure 4. Device-to-Device Skew

#### Figure 6. Output Transition Time Test Reference

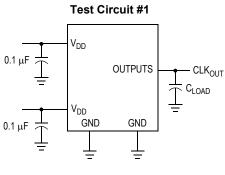

Test Circuit for all parameters

#### **Ordering Information (Available)**

| Ordering Code  | Package Name | Package Type                       |

|----------------|--------------|------------------------------------|

| MPC962304D-1   | D8           | 8-pin 150-mil SOIC                 |

| MPC962304D-1R2 | D8           | 8-pin 150-mil SOIC — Tape and Reel |

| MPC962304D-2   | D8           | 8-pin 150-mil SOIC                 |

| MPC962304D-2R2 | D8           | 8-pin 150-mil SOIC — Tape and Reel |

### Innovate with IDT and accelerate your future networks. Contact:

# www.IDT.com

#### For Sales

800-345-7015 408-284-8200 Fax: 408-284-2775

#### For Tech Support

netcom@idt.com 480-763-2056

#### **Corporate Headquarters**

Integrated Device Technology, Inc. 6024 Silver Creek Valley Road San Jose, CA 95138 United States 800 345 7015 +408 284 8200 (outside U.S.)

#### Asia Pacific and Japan

Integrated Device Technology Singapore (1997) Pte. Ltd. Reg. No. 199707558G 435 Orchard Road #20-03 Wisma Atria Singapore 238877 +65 6 887 5505

#### Europe

IDT Europe, Limited Prime House Barnett Wood Lane Leatherhead, Surrey United Kingdom KT22 7DE +44 1372 363 339

© 2006 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice. IDT and the IDT logo are trademarks of Integrated Device Technology, Inc. Accelerated Thinking is a service mark of Integrated Device Technology, Inc. All other brands, product names and marks are or may be trademarks or registered trademarks used to identify products or services of their respective owners. Printed in USA