November 1989

#### Features

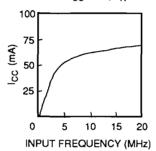

5 mA/MHz

- CMOS EEPLD with Zero Standby Power:

10 µA Typical, 150 µA Maximum

- Operating Power Rises at Less Than

- Propagation Delay: 35, 40 or 45 ns

- Asynchronous Architecture:

- 10 Output Macro Cells with Individually Programmable Clocks, Preset and Reset Signals

- Individually Programmable and Global Output Enable

- Programmable Output Polarity

- Registers Can Be Bypassed Individually

- Preloadable Output Registers Facilitate Testing

- Quickly and Easily Reprogrammable in All Package Types

- 100 Reprogramming Cycles, Minimum

- Silicon Signature Bit for Design Secrecy

- 100 % Field Programming Yield

- 10 Years Data Retention Guaranteed

- Supported By: ABEL™, CUPL™, PALASM2®, PLDesigner™

- Programmed on Standard PAL® Device Programmers

- Space Saving 0.3" Wide 24-Pin Ceramic/Plastic DIP

- 28-Pin LCC and PLCC Packages in Development

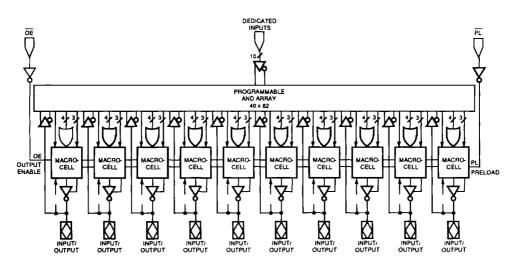

#### **Block Diagram**

ABEL is a trademark of DATA I/O Corporation

PLDesigner is a trademark of Minc Inc.

CUPL is a trademark of Logical Devices Inc.

#### General Description

The 20RA10Z is functionally equivalent to the bipolar PAL20RA10. SEEQ's 20RA10Z consumes significantly less power than its bipolar equivalent: Standby power consumption is typically less than 10 μA; active power rises at less than 5 mA per MHz of operating frequency.

Bipolar devices can not be reprogrammed while UV erasable PLDs can be reprogrammed only in windowed, ceramic packages. Electrically erasable device offer reprogrammability without constraints in all package types.

Reprogrammability reduces development costs and eliminates the risks involved in preprogramming production quantities. Systems can be updated quickly by reconfiguring the EEPLDs. Reprogrammability helps SEEQ to extensively test the entire device and offer 100% field programming yield.

The asynchronous 20RA10Z adds a new dimension to PAL device flexibility. Its unique architecture allows the designer to individually clock, set or reset each of the 10 output macro cells, and to enable/disable each output buffer individually.

#### Functional Description

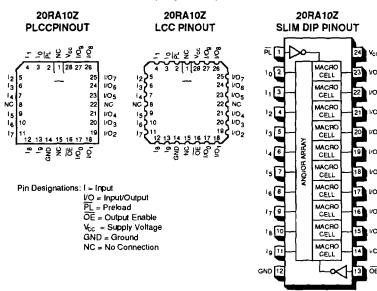

The 20RA10Z has ten dedicated input lines and 10 programmable I/O macrocells. The Registered Asychronous (RA) macrocell is shown on page 3. Pin 1 of the EEPLD serves as global register perload, pin 13 (DIP) or pin 16 (LCC/PLCC) serves as global output enable. The exclusive-OR in every macro cell allows choosing between active high and active low output polarity, and ensures highest possibility utilization of the AND-OR array.

Thrid party software packages allow users to enter PLD designs on personal computers or engineering workstations. Common input formats are: Boolean Algebra, Truth-Tables, State Diagrams, Wave Forms or schematics. The software automatically converts such specifications into fuse patterns. These files, once downloaded to PAL programmers, configure PLDs according to the user's specifications.

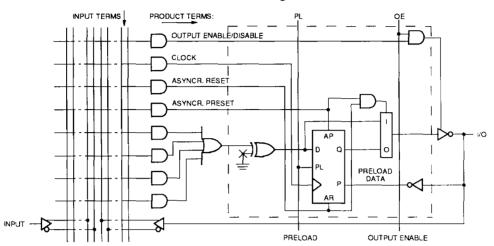

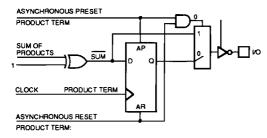

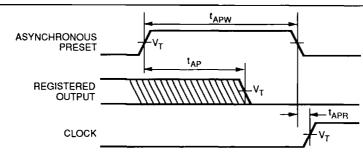

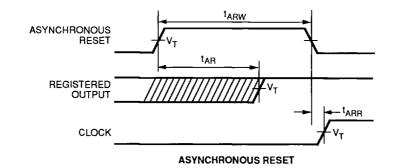

#### Programmability Preset and Reset

In each macrocell, two product lines are dedicated to asynchronous preset and asynchronous reset. If the preset product term is HIGH, the Q output of the register

## Pin Configuration (Top View)

#### RA Macrocell Configuration

becomes logic 1. If the reset product term is HIGH, the Q output of the register becomes a logic 0. The operation of the programmable preset and reset overrides the clock.

#### Programmable Clock

The clock input to each flip-flop comes from the programmable array, Allowing any flip-flop to be clocked independently if desired.

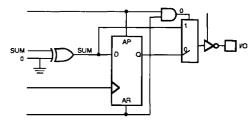

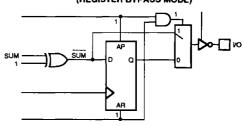

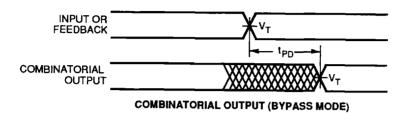

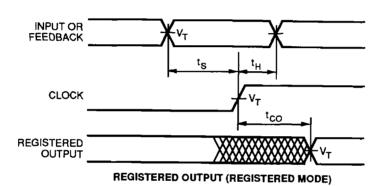

### Bypass Mode/Registered Mode

If both the preset and reset product terms are HIGH, the flip-flop is bypassed (Bypass Mode) and the output becomes combinatorial. Otherwise, the output is from the register (Registered Mode). Each output can be configured to be combinatorial or registered.

### Programmable Polarity

The outputs can be programmed either active-LOW or active-HIGH. This is represented by the Exclusive-OR gate shown in the 20RA10Z logic diagram. When the output polarity bit is programmed, the lower input to the Exclusive-OR gate is HIGH, so the output is active-HIGH. Similarly when the output polarity bit is unprogrammed, the output is active-LOW. The programmable output polarity feature allows the user a higher degree of flexibility when writing equations.

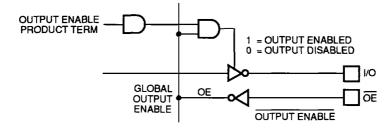

The device provides a product term dedicated to local output control. There is a global output control pin. The

output is enabled if both the global output oin is LOW ans the local output control product is HIGH, all outputs will be disabled. if the local output control product term is LOW, then that output will be disabled.

Remark: The output buffer inverts the sum of products signal.

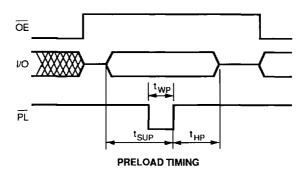

#### Register Preload

Register preload allows any arbitrary state to be loaded into the PAL device output registers. This allows complete logic verification, including states that are impossible or impractical to reach otherwise. To use the preload feature, first disable the outputs by bringing  $\overline{OE}$  HIGH, and present the data at the output pins. A LOW level on the preload pin ( $\overline{PL}$ ) will then load the data into registers. (See Register Preload Waveform on the bottom of page 11.)

| OE Product Term | ŌE Pin | 1/0                     |

|-----------------|--------|-------------------------|

| 1               | 0      | Indiv. output enabled   |

| 0               | Х      | Indiv. output disabled* |

| X               | 1      | All outputs disabled*   |

Output pin(s) floating or used as input(s)

Note: Floaating outputs, as well as unused or floating inputs should be pulled HIGH or Low. Otherwise noise, amplified through the feedback paths or input buffers, may constantly trigger the edge defection circuitry within the 20RA10Z and inhibit standby mode.

#### Security Bit

A security bit prevents copying of your proprietary design. When this bit is set, the verify data path in the PLD is disabled, making it impossible to copy your pattern. Since EEPLDs store patterns as electrical charges on floating polysilicon gates (and not in blown fuses, like other PLD technologies) it is not possible to determine the pattern by simply examining the die. A copy protected EEPLD can be reused after a block erase, which clears both the previously programmed pattern and the security bit at the same

#### **Output Macrocell Configurations**

#### REGISTER OUTPUT/ACTIVE HIGH

#### REGISTERED OUTPUT/ACTIVE LOW

#### COMBINATIONAL OUTPUT/ACTIVE LOW (REGISTER BYPASS MODE)

## COMBINATORIAL OUTPUT/ACTIVE HIGH (REGISTER BYPASS MODE)

### Output Buffer with Individually Programmable and Global Output Enable

## **EEPLD** 20RA10Z EEPLD 20RA10Z Logic Diagram - 23 (27) I/O g 10 5 (3) -- 22 (26) I/O<sub>8</sub> 11 3 (4) 21 (25) 1/07 12 4 (5) 20 (24) 1/0 6 13 5 (6) 19 (23) I/O<sub>5</sub> 14 6 (7) - 18 (21) 1/04 15 7 (9) 17 (20) 1/03 I6 8 (10) - 16 (19) 1/O<sub>2</sub> 17 9 (11) 15 (18) 1/0 1 18 10 (12) 14 (17) 1/00 - 13 (16) OE PIN NUMBERS REFER TO DIP (PLCC PINOUT)

MD 400065/B

SEEQ Technology, Incorporated

#### Absolute Maximum Ratings

| Supply voltage, V <sub>cc</sub> 0.5 V to 7 V                                      |

|-----------------------------------------------------------------------------------|

| DC input voltage, V0.5 V to VCC + 0.5V                                            |

| DC output voltage V <sub>o</sub> 0.5 V to VCC + 0.5 V                             |

| DC output source/sink                                                             |

| current per output pin, Io±35 mA                                                  |

| DC V <sub>cc</sub> or ground current, I <sub>cc</sub> or I <sub>gnp</sub> ≠100 mA |

| Input diode current, I,,                                                          |

| V, < 020 mA                                                                       |

| V, > V <sub>cc</sub> +20 mA                                                       |

| Output diode current, I <sub>ox</sub>                                             |

| V <sub>O</sub> < 020 mA                                                           |

| $V_{o} > V_{cc}$ +20 mA                                                           |

| Storage temperature65°C to 150°C                                                  |

| Static discharge voltage > 2001 V                                                 |

| Latchup current > 100 mA                                                          |

| Ambient Temperature under bias55°C to +125°C                                      |

Stresses above those listed under ABSOLUTE MAXI-MUM RATING may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### **Operating Ranges**

| Commercial (Q) Devices          |                |

|---------------------------------|----------------|

| Temperature (T <sub>A</sub> )   |                |

| Operating Free Air              | 0°C to +75°C   |

| Supply voltage, V <sub>CC</sub> |                |

| Industrial (E) Devices          |                |

| Temperature (T,)                |                |

| Case                            | 40°C to +85°C  |

| Supply voltage, V <sub>cc</sub> | 4.5 V to 5.5 V |

|                                 |                |

Operating ranges define those limits between which the functionality of the device is guaranteed.

#### DC Characteristics (over operating conditions unless otherwise specified)

| Symbol           | Parameter                               | Test Con                                                              | Min.                                            | Max. | Unit            |    |

|------------------|-----------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------|------|-----------------|----|

| V <sub>IL</sub>  | Low-level Input Voltage                 | Guaranteed In<br>Voltage for all                                      | 0                                               | 0.8  | V               |    |

| V <sub>IH</sub>  | High-level Input Voltage                | Guaranteed Input Logical High<br>Voltage for all Inputs <sup>1)</sup> |                                                 | 2    | V <sub>cc</sub> | V  |

| l <sub>n</sub>   | Low-level Input Current                 | V <sub>cc</sub> = Max.                                                | V, =GND                                         | ~ 1  |                 | μА |

| I <sub>IH</sub>  | High-level Input Current                | $V_{cc} = Max.$ $V_1 = V_{cc}$                                        |                                                 |      | 1               | μА |

| Vor              | Low-level Output Voltage                | V <sub>cc</sub> = Min. I <sub>oL</sub> = 8 mA                         |                                                 |      | 0.5             | V  |

|                  |                                         | V <sub>cc</sub> = 5V                                                  | l <sub>oL</sub> = 1 μA                          |      | 0.05            |    |

| V <sub>oн</sub>  | High-level Output Voltage               | V <sub>cc</sub> = Min.                                                | I <sub>OH</sub> = -4.0 mA                       | 3.80 |                 |    |

|                  |                                         | V <sub>cc</sub> = 5V                                                  | I <sub>OL</sub> = -1 μ <b>A</b>                 | 4.95 |                 |    |

| lozL             | Off-state Output Current                | VCC =Max. V <sub>o</sub> = GND <sup>(4)</sup>                         |                                                 | -10  |                 | μΑ |

| I <sub>ozh</sub> |                                         |                                                                       | V <sub>o</sub> = V <sub>cc</sub> <sup>[4]</sup> |      | 10              | μА |

| Icc              | Standby Supply Current[2]               | I <sub>o</sub> = 0 mA, V <sub>i</sub> = GND or V <sub>cc</sub>        |                                                 |      | 150             | μА |

|                  | Operating Supply Current <sup>(3)</sup> | f = 1 MHz, l <sub>o</sub> =                                           |                                                 | 25   | mA              |    |

Notes: 1. These are absolute voltages with respect to the ground pin on the device and include all overshoots due to system and/or tester noise. Do not attempt to test these values without suitable equipment.

Disabled output pins = V<sub>cc</sub> or GND.

Frequency of any input. See gragh page 12 for I<sub>cc</sub> versus frequency

I/O pin leakage is worst case of I<sub>IL</sub> and I<sub>oz</sub> (or I<sub>IH</sub> and I<sub>OH2</sub>).

#### Capacitance

| Parameter<br>Symbol | Parameter Description | Test conditions                                                                        | Тур. | Unit |

|---------------------|-----------------------|----------------------------------------------------------------------------------------|------|------|

| C <sub>IN</sub>     | Input capacitance[1]  | V <sub>IN</sub> = 2.0 V at f = 1.0 MHz<br>V <sub>CC</sub> = 5 V T <sub>A</sub> = 25°C  | 7    | pF   |

| Соит                | Output capacitance[1] | V <sub>OUT</sub> = 2.0 V at f = 1.0 MHz<br>V <sub>CC</sub> = 5 V T <sub>A</sub> = 25°C | 8    |      |

Note: 1. Sampled but not 100% tested.

#### Switching Characteristics (over commercial operating range[1])

|                  | mbol Parameter <sup>[2]</sup>                           |                                                       | - 35 <sup>[5]</sup> |      | - 40     |      | - 45 <sup>[6]</sup> |      |      |

|------------------|---------------------------------------------------------|-------------------------------------------------------|---------------------|------|----------|------|---------------------|------|------|

| Symbol           |                                                         |                                                       | Min.                | Max. | Min.     | Max. | Min.                | Max. | Unit |

| t <sub>PD</sub>  | Input or Feedba                                         | ck to Output                                          |                     | 35   |          | 40   |                     | 45   | ns   |

| t <sub>s</sub>   | Setup Time for                                          | Input or Feednack to Clock                            | 15                  |      | 20       |      | 20                  |      | ns   |

| t <sub>H</sub>   | Hold Time                                               |                                                       | 10                  | -    | 15       |      | 15                  |      | ns   |

| tco              | Clock to Output                                         | or Feedback <sup>[3]</sup>                            |                     | 30   |          | 40   |                     | 45   | ns   |

| twp              | PreloadPulse W                                          | lidth                                                 | 25                  |      | 30       |      | 30                  | -    | ns   |

| t <sub>sup</sub> | Preload Setup 1                                         | lime .                                                | 20                  |      | 25       |      | 25                  |      | ns   |

| t <sub>hP</sub>  | Preload Hold Time                                       |                                                       | 20                  |      | 25       |      | 25                  |      | ns   |

| t <sub>AP</sub>  | Asynchronous Preset to Registered Output <sup>[3]</sup> |                                                       |                     | 35   | <u> </u> | 45   |                     | 45   | ns   |

| tAPW             | Asynchronous Preset Pulse Width                         |                                                       | 25                  |      | 25       |      | 30                  |      | ns   |

| t <sub>APR</sub> | Asynchronous Preset Recovery Time                       |                                                       | 10                  |      | 15       | -    | 15                  |      | ns   |

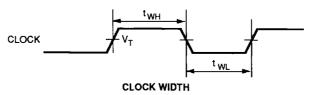

| twL              | Width of Clock LOW                                      |                                                       | 15                  |      | 20       |      | 20                  | 1    | ns   |

| t <sub>wh</sub>  |                                                         | HIGH                                                  | 15                  | •    | 20       |      | 20                  |      | ns   |

| f <sub>MAX</sub> | Maximum                                                 | Extenal Feedback 1/t <sub>s</sub> = t <sub>co</sub> ) | 22.2                |      | 16.6     |      | 15.3                |      | MHz  |

|                  | Frequency                                               | No Feedback 1/(t <sub>wL</sub> = t <sub>wH</sub> )    | 33.3                |      | 25       |      | 25                  |      | MHz  |

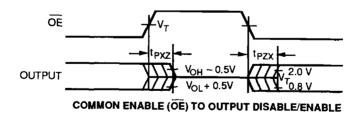

| t <sub>PZX</sub> | Common Enable to Output Buffer Enabled                  |                                                       |                     | 20   |          | 25   |                     | 30   | ns   |

| t <sub>PXZ</sub> | Common Enable to Output Buffer Disabled                 |                                                       |                     | 20   |          | 25   |                     | 30   | ns   |

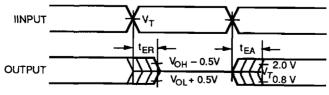

| t <sub>EA</sub>  | Input to Output Buffer Enabled <sup>[4]</sup>           |                                                       |                     | 30   |          | 40   |                     | 45   | ns   |

| t <sub>ER</sub>  | Input to Output Buffer Disabled[4]                      |                                                       |                     | 30   |          | 40   |                     | 45   | ns   |

#### Note:

- The 20RA10Z is designed for the full military operating range. Contact your nearest SEEQ representative for availability information and for specifications of industrial and military devices.

- 2. Test conditions are specified in table on page 12.

- 3. Minimum values of these parameters are guaranteed to be larger than the hold time t<sub>ir</sub>.

- Equivalent functions to t<sub>PZX</sub>/t<sub>PXZ</sub> but using product term control.

- 5. Preliminary specification.

- 6. The 20RA10Z-45 is available and specified for commercial and industrial operating conditions.

Remarks: All specified input-to-output delays include the time it takes the input edge detection circuitry to activate the device (from standby mode into operating mode).

#### Data Retention and Endurance

| Symbol          | Parameter                   | Value | Unit   | Conditions                                               |

|-----------------|-----------------------------|-------|--------|----------------------------------------------------------|

| t <sub>DR</sub> | Pattern data retention time | > 10  | years  | Max. storage temperature<br>Mil-STD 883 Test Method 1008 |

| N               | Min. reprogramming cycles   | 100   | cycles | Operating conditions                                     |

## Switching Waveforms

INPUT TO OUTPUT DISABLE/ENABLE

**EEPLD**

**ASYNCHRONOUS PRESET**

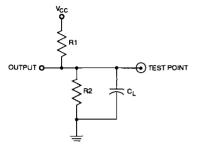

### Switching Test Laod

| Specification                      | C <sub>L</sub> | R <sub>1</sub> | R,   | Measured<br>Output Value                                       |

|------------------------------------|----------------|----------------|------|----------------------------------------------------------------|

| t <sub>IL</sub> ,t <sub>CO</sub>   | 50 pF          | 440Ω           | 190Ω | 1.5V                                                           |

| t <sub>PZX</sub> , t <sub>EA</sub> | 50 pF          | 440Ω           | 190Ω | Z-H: 2.0V<br>Z-L: 0.8V                                         |

| t <sub>PXZ</sub> , t <sub>ER</sub> | 5pF            | 440Ω           | 190Ω | H – Z: V <sub>OH</sub> –0.5 V<br>L – Z: V <sub>OL</sub> + 0.5V |

## Icc Versus Frequency

TYPICAL: VCC = 5V, TA = 25°C

## Key to Timing Diagrams

WAVEFORM

**INPUTS**

**OUTPUTS**

DON'T CARE: CHANGE PERMITTED

CHANGING: STATE UNKNOWN

NOT APPLICABLE

CENTER LINE IS HIGH IMPEDANCE STATE

MUST BE STEADY

WILL BE STEADY

MAY CHANGE FROM

WILL BE CHANGING FROM H TO L

MAY CHANGE FROM L TO H

WILL BE CHANGING FROM L TO H

Notes: 1.  $V_{\tau} = 1.5 \text{ V}$

2. Input pulse amplitude 0 V to 3.0 V

3. Input rise and fall times 2 - 5 ns typical

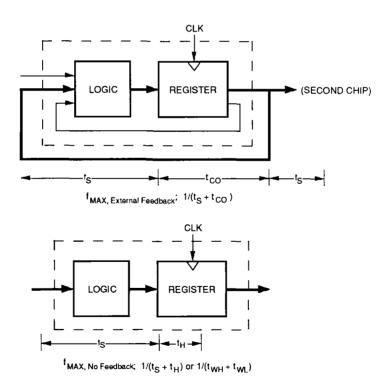

#### f Parameters

The parameters  $f_{\text{MAX}}$  is the maximum clock rate at which the device is guaranteed to operate. Because flexibility inherent in programmable logic devices offers a choice of clocked flip-flop designs,  $f_{MAX}$  is specified in this case for two types of synchronous designs.

The first type of design is a state machine with feedback signals sent off-chip. This external feedback could go back to the device inputs, or to a second device in a multichip state machine. The slowest path defining the period is the sum of the clock-to-output time and input setup time for the external signals ( $t_s + t_{co}$ ). The reciprocal,  $f_{MAX'}$  is the maximum frequency with external feedback or in conjunction with an equivalent speed device. This f<sub>MAX</sub> is designated "f<sub>MAX</sub>, External Feedback."

The second type of design is a simple data path application. In this case, input data is presented to the flip-flop and clocked through; no feedback is employed. Under these conditions, the period is limited by the sum of the data setup time and the data hold time  $(t_s + t_H)$ . However, a lower limit for the period of each  $f_{MAX}$  type is the minimum clock period ( $t_{w_H} + t_{w_L}$ ). Usually, this minimum clock period determines the period for the second  $f_{\text{MAX}}$  designated "MAX, No leedback

#### PLD Development

Development software assists the user in implementing a design in one or several PLDs. The software converts the user's input into a device dependent fuse map in JEDEC format. The software packages listed below support the 20RA10Z EEPLD. For more information about PLD development software contact SEEQ Technology or the software vendor directly:

#### DATA I/O Corp.

10525 Willows Road, NE, P.O. Box 97046, Redmont, WA 98073-9746 (800) 247-5700 Software offered: ABEL, PLD Test

#### Minc. Incorporated

1575 York Road, Colorado Springs, CO 80918 (719) 590-1155 Software offered: PLDesigner

#### Logical Devices, Inc.

1021 N.W. 65th Place, Fort Lauderdale, FL 33309 (305) 974-0967 Software offered: CUPL

#### PLD Programming

The 20RA10Z can be programmed on standard logic programmers. Previously programmed devices can be reprogrammed easily, using exactly the same procedure as required for blank EEPLDs. If the user wants to erase a 20RA10Z, but not program it to a new pattern, an empty JEDEC file should be loaded into the device programmer.

#### PLD Programmer Vendors

#### Adams MacDonald

800 Airport Road, Monterey, CA 93940 (408) 373-3607

#### DATA I/O Corp.

10525 Willows Road NE, P.O. Box 97046

Redmont, WA 98073-9746

(800) 247-5700

PLD Programming equipment:

System 29A or 29B

Logic Pal™ 303A-V04

Adaptor 303-011A for 24 pin DIP

303-011B for 28 pin PLCC

Family Pinout Code for 20RA10Z: 9E/45

#### Digilec Inc.

22736 Vanowen, Canoga Park, CA 91307 (800) 367-8750; CA: (818) 887-3755

#### Logical Devices Inc.

1201 N.W. 65th Place, Fort Lauderdale, FL 33309 (305) 974-0967

#### PROMOC

see Adams MacDonald

#### Stag Microsystems Inc.

1600 Wyatt Dr., Santa Clara CA 95054 (408) 988-1118

For more information about PLD programmers contact SEEQ Technology or the programmer vendor directly.

Logic Pak is a trademark of DATA I/O Corporation.

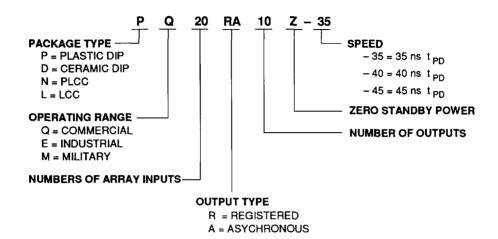

## Ordering Information