# **PEX 8111BB**

# ExpressLane PCI Express-to-PCI Bridge

# Data Book

Version 1.2

June 2006

Websitewww.plxtech.comTechnical Supportwww.plxtech.com/supportPhone408 774-9060800 759-3735808 774-2169

Copyright © 2006 by PLX Technology Inc. All Rights Reserved – Version 1.2 June, 2006

#### **Copyright Information**

Copyright @ 2005 – 2006 PLX Technology, Inc. All rights reserved. The information in this document is proprietary to PLX Technology. No part of this document may be reproduced in any form or by any means or used to make any derivative work (such as translation, transformation, or adaptation) without written permission from PLX Technology.

PLX Technology provides this documentation without warranty, term or condition of any kind, either express or implied, including, but not limited to, express and implied warranties of merchantability, fitness for a particular purpose, and non-infringement. While the information contained herein is believed to be accurate, such information is preliminary, and no representations or warranties of accuracy or completeness are made. In no event will PLX Technology be liable for damages arising directly or indirectly from any use of or reliance upon the information contained in this document. PLX Technology may make improvements or changes in the product(s) and/or the program(s) described in this documentation at any time.

PLX Technology retains the right to make changes to this product at any time, without notice. Products may have minor variations to this publication, known as errata. PLX Technology assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of PLX Technology products.

PLX Technology and the PLX logo are registered trademarks and ExpressLane is a trademark of PLX Technology, Inc.

PCI Express is a trademark of the PCI Special Interest Group.

All product names are trademarks, registered trademarks, or servicemarks of their respective owners. Order Number: 8111BB-SIL-DB-P1-1.2

### **Revision History**

|     | Date           | Description of Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0 | November, 2005 | Initial Production release Silicon Revision BB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 1.1 | December, 2005 | <ul> <li>Table 16-2 – Corrected JTAG IDCODE values in Version column.</li> <li>Table 17-1 – Removed "Ambient Temperature" row.</li> <li>Table 18-2 – Corrected 161-Ball FBGA Package ball pitch dimension.</li> <li>Global (2 places) – Changed "PCI Express host" to "PCI Express Root Complex."</li> <li>Section 5.1.1.2 – Added note regarding <i>No Snoop</i> and <i>Relaxed Ordering</i> bits.</li> <li>Register 14-56, (Offset 68h; DEVCTL) PCI Express Device Control, Bits [3:0] – Added "Valid only in Forward Bridge mode" to bit descriptions.</li> <li>Register 14-82, (Offset 101Ch; POWER) Power – Added "(Forward Bridge Mode Only" to register title.</li> <li>Figure 18-3 – Corrected title.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.2 | June, 2006     | <ul> <li>Reorganized Chapter 2, "Ball Descriptions." Other changes include:</li> <li>Clarified reset for GPIO[3:2] in Forward and Reverse modes.</li> <li>WAKEIN# definition, added "In Forward Bridge mode, pull WAKEIN# high."</li> <li>IDSEL definitions, replaced "In Forward Bridge mode, IDSEL is grounded or pulled up to 3.3V" with "It is recommended to ground IDSEL in Forward Bridge mode to prevent it from floating."</li> <li>PCIRST# definitions, changed "OD" to "TP".</li> <li>PCLKO definitions, added "PCLKO can be connected to PCLKI to drive PCLKI."</li> <li>Global – Corrected PME# references to PMEIN# and PMEOUT#.</li> <li>Global – Corrected PEX_PERST# references to PERST#.</li> <li>Section 4.1.1.1, replaced last two sentences of second paragraph with "PCIRST# is asserted for at least 2 ms after the power levels are valid."</li> <li>Added new Chapter 9, "Bridge Operation," and renumbered all subsequent chapters.</li> <li>Corrected Table 18-2 (formerly Table 16-2) Version column values to reflect BB silicon revision.</li> <li>Register split into two chapters – one for Forward Bridge mode (Chapter 15), the other for Reverse Bridge mode (Chapter 16).</li> <li>Register chapters, PCI Control register, bit 26, changed first sentence describing action when cleared.</li> <li>Chapter 19, "Electrical Specifications," changes (formerly Chapter 17):</li> <li>Replaced Sections 19.1 and 19.2 with Section 19.1, "Power Sequence," and Section 19.1.1, "VIO."</li> <li>Added new Table 19-2, "Package Thermal Resistance," and renumbered all subsequent tables.</li> <li>Added section 19.4.2, "SerDes Interface DC Characteristics."</li> <li>Corrected VDD3.3 signal reference in Table 19-4 for V<sub>IH</sub>.</li> <li>Changed "TLB" references to "TLP".</li> </ul> |

#### Preface

This document contains material that is proprietary to PLX. Reproduction without the express written consent of PLX is prohibited. All reasonable attempts are made to ensure the contents of this document are accurate; however no liability, expressed or implied is guaranteed. PLX reserves the right to modify this document, without notification, at any time. This PLX document is periodically updated as new information is made available.

#### Scope

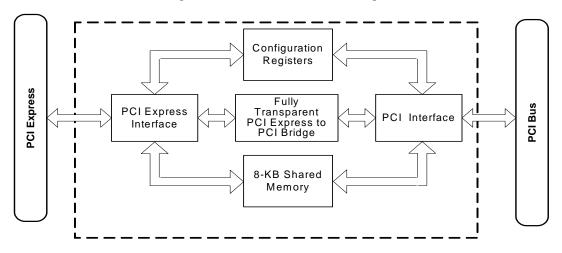

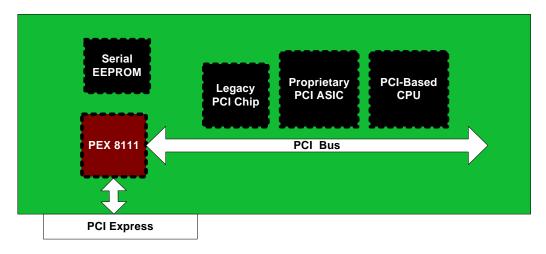

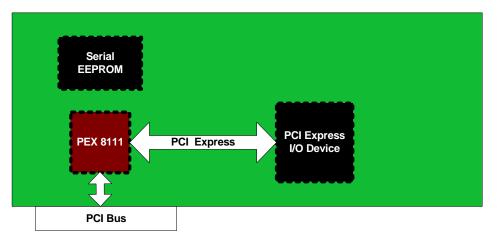

This document describes the PEX 8111 bridge operation and provides operational data for customer use.

#### Audience

This data book provides the functional details of PLX Technology ExpressLane<sup>TM</sup> PEX 8111 PCI Express-to-PCI Bridge, for hardware designers and software/firmware engineers.

#### Supplemental Documentation

This data book assumes that the reader is familiar with the documents referenced below.

• PLX Technology, Inc.

870 Maude Ave., Sunnyvale, CA 94085 USA

Tel: 408 774-9060 or 800 759-3735, Fax: 408 774-2169, http://www.plxtech.com

<u>– PEX 8111 Quick Start Design Note</u>

- PCI Special Interest Group (PCI-SIG) 3855 SW 153rd Drive, Beaverton, OR 97006 USA Tel: 503 619-0569, Fax: 503 644-6708, http://www.pcisig.com

- PCI Local Bus Specification, Revision 3.0

- PCI Local Bus Specification, Revision 2.2

- PCI to PCI Bridge Architecture Specification, Revision 1.1

- PCI Bus Power Management Interface Specification, Revision 1.1

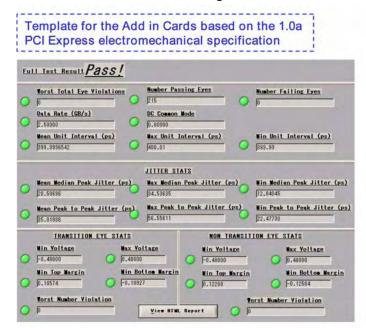

- PCI Express Base Specification, Revision 1.0a

- PCI Express to PCI/PCI-X Bridge Specification, Revision 1.0

- PCI Express Card Electromechanical (CEM) Specification, Revision 1.0a

- The Institute of Electrical and Electronics Engineers, Inc.

445 Hoes Lane, PO Box 1331, Piscataway, NJ 08855-1331, USA

Tel: 800 678-4333 (domestic only) or 732 981-0060, Fax: 732 981-1721, http://www.ieee.org

- IEEE Standard 1149.1-1990, IEEE Standard Test Access Port and Boundary-Scan Architecture, 1990

- IEEE 1149.1a-1993, IEEE Standard Test Access Port and Boundary-Scan Architecture

- IEEE Standard 1149.1b-1994, Specifications for Vendor-Specific Extensions

### **Supplemental Documentation Abbreviations**

*Note:* In this data book, shortened titles are provided to the previously listed documents. The following table lists these abbreviations.

| Abbreviation                             | Document                                                       |

|------------------------------------------|----------------------------------------------------------------|

| PCI r3.0                                 | PCI Local Bus Specification, Revision 3.0                      |

| PCI r2.2                                 | PCI Local Bus Specification, Revision 2.2                      |

| PCI-to-PCI Bridge r1.1                   | PCI to PCI Bridge Architecture Specification, Revision 1.1     |

| PCI Power Mgmt. r1.1                     | PCI Bus Power Management Interface Specification, Revision 1.1 |

| PCI Express r1.0a                        | PCI Express Base Specification, Revision 1.0a                  |

| PCI Express-to-PCI/<br>PCI-X Bridge r1.0 | PCI Express to PCI/PCI-X Bridge Specification, Revision 1.0    |

| IEEE Standard 1149.1-1990                | IEEE Standard Test Access Port and Boundary-Scan Architecture  |

### **Data Assignment Conventions**

| Data Width        | PEX 8111 Convention |

|-------------------|---------------------|

| 1 byte (8 bits)   | Byte                |

| 2 bytes (16 bits) | Word                |

| 4 bytes (32 bits) | DWORD/DWord/Dword   |

#### **Terms and Abbreviations**

The following table lists common terms and abbreviations used in this document. Terms and abbreviations defined in the *PCI Express r1.0a* are not included in this table.

| Terms and<br>Abbreviations | Definition                                                                                                                                                                                                          |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| #                          | Indicates an Active-Low signal.                                                                                                                                                                                     |

| АСК                        | Acknowledge Control Packet. A control packet used by a destination to acknowledge data packet receipt. A signal that acknowledges the signal receipt.                                                               |

| ADB                        | Allowable Disconnect Boundary.                                                                                                                                                                                      |

| ADQ                        | Allowable Disconnect Quantity. In PCI Express, the ADQ is a buffer size.<br>Used to indicate memory requirements or reserves.                                                                                       |

| BAR                        | Base Address Register.                                                                                                                                                                                              |

| Byte                       | 8-bit quantity of data.                                                                                                                                                                                             |

| CA                         | Completion with Completer Abort status.                                                                                                                                                                             |

| CFG                        | Access initiated by PCI Configuration transactions on the primary bus.                                                                                                                                              |

| Clock cycle                | One period of the PCI Bus clock.                                                                                                                                                                                    |

| Completer                  | Device addressed by a <i>requester</i> .                                                                                                                                                                            |

| CRS                        | Configuration Retry Status.                                                                                                                                                                                         |

| CSR                        | Configuration Status register; Control and Status register; Command and Status register                                                                                                                             |

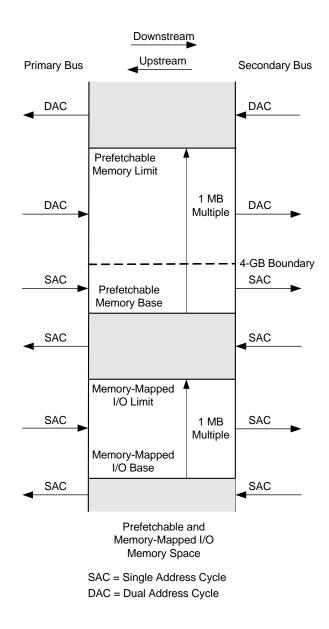

| DAC                        | Dual Address cycle. A PCI transaction wherein a 64-bit address is transferred across a 32-bit data path in two Clock cycles.                                                                                        |

| Destination Bus            | Target of a transaction that crosses a bridge is said to reside on the destination bus.                                                                                                                             |

| DLLP                       | Data Link Layer Packet (originates at the Data Link Layer); can contain<br>Flow Control (FCx DLLPs) acknowledge packets (ACK and NAK DLLPs);<br>and power management (PMx DLLPs).                                   |

| Downstream                 | Transactions that are forwarded from the primary bus to the secondary bus of a bridge are said to be flowing downstream.                                                                                            |

| DWORD                      | 32-bit quantity of data.                                                                                                                                                                                            |

| ECRC                       | End-to-end Cyclic Redundancy Check (CRC)                                                                                                                                                                            |

| EE                         | Access initiated by the Serial EEPROM Controller during initialization.                                                                                                                                             |

| Endpoints                  | <ul> <li>Devices, other than the Root Complex and switches, that are requesters or completers of PCI Express transactions.</li> <li>Endpoints can be PCI Express endpoints or <i>legacy</i> endpoints.</li> </ul>   |

|                            | <ul> <li>Legacy endpoints can support I/O and Locked transaction semantics.</li> <li>PCI Express endpoints do not support I/O and Locked transaction semantics.</li> </ul>                                          |

| FCP                        | Flow Control Packet devices on each link exchange FCPs, which carry <i>header</i> and <i>data payload</i> credit information for one of three packet types – Posted Requests, Non-Posted Requests, and Completions. |

| Forward Bridge mode        | The primary bus is closest to the PCI Express Root Complex.                                                                                                                                                         |

| host                       | Computer that provides services to computers that connect to it on a network.<br>Considered to be in charge of the other devices connected to the bus.                                                              |

#### Terms and Abbreviations

### Terms and Abbreviations (Cont.)

| Terms and<br>Abbreviations | Definition                                                                                                                                                                                                                                                                                                                          |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HwInit                     | Hardware initialized register or register bit. The register bits are initialized by a PEX 8111 hardware initialization mechanism or PEX 8111 Serial EEPROM register initialization feature. Register bits are Read-Only after initialization and are reset only with a Cold or Warm Reset.                                          |

| Ι                          | CMOS Input.                                                                                                                                                                                                                                                                                                                         |

| I/O                        | CMOS Bi-Directional Input Output.                                                                                                                                                                                                                                                                                                   |

| Lane                       | Differential signal pair in each direction.                                                                                                                                                                                                                                                                                         |

| Layers                     | <ul> <li>PCI Express defines three layers:</li> <li><i>Transaction Layer</i> – The primary function of the Transaction Layer is assembly and disassembly of TLPs. The major components of a transaction layer packet (TLP) are Header, Data Payload, and an optional Digest Field.</li> </ul>                                       |

|                            | <ul> <li><i>Data Link Layer</i> – The primary task of the Data Link Layer is to provide link management and data integrity, including error detection and correction. This layer defines the data control for PCI Express.</li> <li><i>Physical Layer</i> – The primary value to users is that this layer appears to the</li> </ul> |

|                            | • <b>Physical Layer</b> – The primary value to users is that this rayer appears to the upper layers to be PCI. It connects the lower protocols to the upper layers.                                                                                                                                                                 |

| MM                         | Access initiated by PCI Memory transactions on the primary or secondary bus, using the address range defined by <b>PCI Base Address 0</b> .                                                                                                                                                                                         |

| MSI                        | Message Signaled Interrupt.                                                                                                                                                                                                                                                                                                         |

| NAK                        | Negative Acknowledge.                                                                                                                                                                                                                                                                                                               |

| Non-Posted Transaction     | A Memory Read, I/O Read or Write, or Configuration Read or Write that returns a completion to the master.                                                                                                                                                                                                                           |

| NS                         | No Snoop.                                                                                                                                                                                                                                                                                                                           |

| 0                          | CMOS Output.                                                                                                                                                                                                                                                                                                                        |

| OD                         | Open Drain Output.                                                                                                                                                                                                                                                                                                                  |

| Originating Bus            | Master of a transaction that crosses a bridge is said to reside on the originating bus.                                                                                                                                                                                                                                             |

| Packet Types               | There are three packet types:                                                                                                                                                                                                                                                                                                       |

|                            | • <i>TLP</i> , Transaction Layer Packet                                                                                                                                                                                                                                                                                             |

|                            | • <i>DLLP</i> , Data Link Layer Packet                                                                                                                                                                                                                                                                                              |

|                            | PLP, Physical Layer Packet                                                                                                                                                                                                                                                                                                          |

| PCI                        | PCI Compliant                                                                                                                                                                                                                                                                                                                       |

| PCI                        | Peripheral Component Interconnect. A PCI Bus is a high-performance bus that<br>is 32 bits or 64 bits wide. It is designed to be used with devices that contain<br>high-bandwidth requirements ( <i>such as</i> , the display subsystem). It is an I/O bus<br>that has the ability to be dynamically configured.                     |

| PCI Master (Initiator)     | Drives the Address phase and transaction boundary (FRAME#).<br>Initiates a transaction and drives data handshaking (IRDY#) with the target.                                                                                                                                                                                         |

| PCI Target                 | Claims the transaction by asserting DEVSEL# and handshakes the transaction (TRDY#) with the initiator.                                                                                                                                                                                                                              |

| PCI Transaction            | Read, Write, Read Burst, or Write Burst operation on the PCI Bus.<br>Includes an Address phase, followed by one or more Data phases.                                                                                                                                                                                                |

| PCI Transfer               | During a transfer, data is moved from the source to the destination on the PCI Bus.<br>TRDY# and IRDY# assertion indicates a Data transfer.                                                                                                                                                                                         |

| PCIE                       | PCI Express.                                                                                                                                                                                                                                                                                                                        |

| Terms and<br>Abbreviations | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Port                       | Interface between a PCI Express component and the <i>link</i> . Consists of transmitters<br>and receivers.<br>• An <i>ingress</i> port receives a packet.<br>• An <i>egress</i> port transmits a packet.<br>• A <i>link</i> is a physical connection between two devices that consists of xN <i>lanes</i> .<br>• An x1 link consists of one Transmit and one Receive signal, where each<br>signal is a differential pair. This is one lane. There are four lines or signals<br>in an x1 link.<br>• $V_1 \circ \downarrow \downarrow I_1 \qquad I_2 \downarrow \downarrow \downarrow \lor V_2$<br>A Differential Pair<br>$I_b$<br>This is an x1 Link<br>This is an x1 Link<br>There are four signals<br>• A Differential Pair<br>in each direction<br>= one Lane |

| Posted Transaction         | Memory write that does not return a completion to the master.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Primary Bus                | Bus closest to the PCI Express Root Complex (Forward Bridge mode) or the PCI host CPU (Reverse Bridge mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PU                         | Signal is internally pulled up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| QoS                        | Quality of Service.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| RC                         | Root Complex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RCB                        | Read Boundary Completion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Request packet             | A <i>non-posted request packet</i> transmitted by a requester has a completion packet returned by the associated completer.<br>A <i>posted request packet</i> transmitted by a requester has no completion packet returned by the completer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Requester                  | Device that originates a transaction or puts a transaction sequence into the PCI Express fabric.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Reverse Bridge Mode        | The primary bus is closest to the PCI host CPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RO                         | Read-Only register or register bit. Register bits are Read-Only and cannot be altered by software. Register bits are initialized by a PEX 8111 hardware initialization mechanism or PEX 8111 Serial EEPROM register initialization feature.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RO                         | Relaxed Ordering.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RsvdP                      | <i>Reserved</i> and Preserved. <i>Reserved</i> for future RW implementations. Registers are Read-Only and must return 0 when read. Software must preserve value read for writes to bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RsvdZ                      | <i>Reserved</i> and Zero. <i>Reserved</i> for future RW1C implementations. Registers are Read-Only and must return 0 when read. Software must use 0 for writes to bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Terms and Ab | breviations | (Cont.) |

|--------------|-------------|---------|

|--------------|-------------|---------|

| Terms and<br>Abbreviations | Definition                                                                                                                                                                                      |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RW                         | Read-Write register. Register bits are Read-Write and set or cleared by software to the needed state.                                                                                           |

| RW1C                       | Read-Only Status. Write 1 to clear status register. Register bits indicate status when read; a set bit indicating a status event is cleared by writing 1. Writing 0 to RW1C bits has no effect. |

| RX                         | Received Packet.                                                                                                                                                                                |

| SC                         | Successful Completion.                                                                                                                                                                          |

| Secondary Bus              | The bus farthest from the PCI Express Root Complex (Forward Bridge mode) or the PCI host CPU (Reverse Bridge mode).                                                                             |

| STRAP                      | Strapping pads ( <i>such as</i> , BAR0ENB#, FORWARD, and EXTARB) must be connected to H or L on the board.                                                                                      |

| STS                        | Sustained Three-State Output, Driven High for One CLK before Float.                                                                                                                             |

| TC                         | Traffic Class.                                                                                                                                                                                  |

| TLP                        | Translation Layer Packet.                                                                                                                                                                       |

| ТР                         | Totem Pole.                                                                                                                                                                                     |

| TS                         | Three-State Bi-Directional.                                                                                                                                                                     |

| TX                         | Transmitted Packet.                                                                                                                                                                             |

| Upstream                   | Transactions that are forwarded from the secondary bus to the primary bus of a bridge are said to be flowing upstream.                                                                          |

| UR                         | Unsupported Request.                                                                                                                                                                            |

| VC                         | Virtual Channel.                                                                                                                                                                                |

| WO                         | Write-Only register. Used to indicate that a register is written by the Serial EEPROM Controller.                                                                                               |

| Word                       | 16-bit quantity of data.                                                                                                                                                                        |

Data Book

## Contents

| Chapter 1 | <b>Intr</b><br>1.1<br>1.2<br>1.3 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1<br>1<br>2<br>2<br>2                                                                                              |

|-----------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| Chapter 2 | <b>Bal</b><br>2.1<br>2.2<br>2.3  | <b>Descriptions.</b> Ball Description Abbreviations         PCI Signal Pull-Up Resistors (Forward Bridge Mode Only)         Ball Description – 144-Ball PBGA Package         2.3.1 PCI Express Signals         2.3.2 PCI Signals         2.3.3 Clock, Reset, and Miscellaneous Signals         2.3.4 JTAG Interface Signals         2.3.5 Test Signals         2.3.6 No Connect Signal         2.3.7 Power and Ground Signals         2.3.8 Ball Tables – 144-Ball PBGA Package         2.3.9 Physical Ball Assignment – 144-Ball PBGA Package         Ball Description – 161-Ball FBGA Package         2.4.1 PCI Express Signals         2.4.2 PCI Signals         2.4.3 Clock, Reset, and Miscellaneous Signals         2.4.4 JTAG Interface Signals         2.4.5 Test Signals         2.4.4 JTAG Interface Signals         2.4.5 Test Signals         2.4.6 No Connect Signals         2.4.7 Power and Ground Signals         2.4.7 Power and Ground Signals         2.4.7 Power and Ground Signals         2.4.8 Ball Tables – 161-Ball FBGA Package | 5.5<br>5.6<br>5.6<br>5.7<br>10<br>11<br>12<br>12<br>13<br>14<br>16<br>17<br>18<br>21<br>23<br>24<br>24<br>25<br>26 |

| Chapter 3 | <b>Res</b><br>3.1<br>3.2<br>3.3  | 2.4.9 Physical Ball Assignment – 161-Ball FBGA Package         Set Summary         Forward Bridge Mode         Reverse Bridge Mode         Initialization Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>. 31</b><br>. 31<br>. 31                                                                                        |

| Chapter 4 | 4.1                              | alization         Forward Bridge Initialization         4.1.1       Forward Bridge Reset Behavior         4.1.1       Fundamental Reset (Cold/Warm Reset)         4.1.1.2       Primary Reset Due to Physical Layer Mechanism (Hot Reset)         4.1.1.3       Primary Reset Due to Data Link Down         4.1.1.4       Secondary Bus Reset by way of Bridge Control Register         4.1.1.5       Bus Parking during Reset         Reverse Bridge Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 33<br>. 33<br>. 33<br>. 33<br>. 34<br>. 34<br>. 34<br>. 34                                                       |

| Chapter 5 | Interrupts |                                                      |  |  |  |

|-----------|------------|------------------------------------------------------|--|--|--|

| -         | 5.1        | Forward Bridge PCI Interrupts                        |  |  |  |

|           |            | 5.1.1 Forward Bridge Internally Generated Interrupts |  |  |  |

|           |            | 5.1.1.1 Virtual Wire Interrupts 38                   |  |  |  |

|           |            | 5.1.1.2 Message Signaled Interrupts                  |  |  |  |

|           | 5.2        | Reverse Bridge PCI Interrupts                        |  |  |  |

|           |            | 5.2.1 Reverse Bridge Internally Generated Interrupts |  |  |  |

|           |            | 5.2.1.1 INTx# Signals                                |  |  |  |

|           |            | 5.2.1.2 Message Signaled Interrupts                  |  |  |  |

| Chapter 6 | Ser        | al EEPROM Controller                                 |  |  |  |

| enapter e | 6.1        | Overview                                             |  |  |  |

|           | 6.2        | Serial EEPROM Data Format                            |  |  |  |

|           | 6.3        | Initialization                                       |  |  |  |

|           | 6.4        | Serial EEPROM Random Read/Write Access               |  |  |  |

|           | 0.4        | 6.4.1 Serial EEPROM Opcodes                          |  |  |  |

|           |            | 6.4.2 Serial EEPROM Low-Level Access Routines        |  |  |  |

|           |            | 6.4.3 Serial EEPROM Read Status Routine              |  |  |  |

|           |            | 6.4.4 Serial EEPROM Write Data Routine               |  |  |  |

|           |            | 6.4.5 Serial EEPROM Read Data Routine                |  |  |  |

|           |            |                                                      |  |  |  |

| Chapter 7 | ۸da        | ress Spaces                                          |  |  |  |

| Chapter 7 |            | -                                                    |  |  |  |

|           | 7.1        | Introduction                                         |  |  |  |

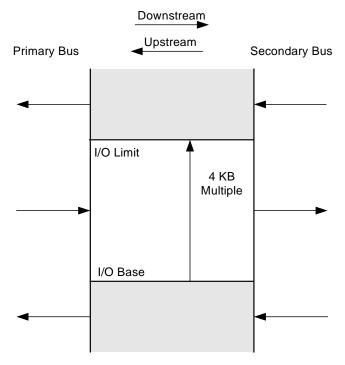

|           | 7.2        | I/O Space                                            |  |  |  |

|           |            | 7.2.1 Enable Bits                                    |  |  |  |

|           |            | 7.2.2 I/O Base and Limit Registers                   |  |  |  |

|           |            | 7.2.3 ISA Mode                                       |  |  |  |

|           |            | 7.2.4 VGA Mode                                       |  |  |  |

|           |            | 7.2.4.1 VGA Palette Snooping                         |  |  |  |

|           | 7.3        | Memory-Mapped I/O Space                              |  |  |  |

|           |            | 7.3.1 Enable Bits                                    |  |  |  |

|           |            | 7.3.2 Memory Base and Limit Registers                |  |  |  |

|           |            | 7.3.3 VGA Mode                                       |  |  |  |

|           | 7.4        | Prefetchable Space                                   |  |  |  |

|           |            | 7.4.1 Enable Bits                                    |  |  |  |

|           |            | 7.4.2 Prefetchable Base and Limit Registers          |  |  |  |

|           |            | 7.4.3 64-Bit Addressing                              |  |  |  |

|           |            | 7.4.3.1 Forward Bridge Mode 54                       |  |  |  |

|           |            | 7.4.3.2 Reverse Bridge Mode                          |  |  |  |

|           |            | 7.4.4 VGA Mode                                       |  |  |  |

| Chapter 8 | Cor        | figuration Transactions                              |  |  |  |

| -         | 8.1        | Introduction                                         |  |  |  |

|           | 8.2        | Type 0 Configuration Transactions                    |  |  |  |

|           | 8.3        | Type 1 Configuration Transactions                    |  |  |  |

|           | 8.4        | Type 1-to-Type 0 Conversion                          |  |  |  |

|           |            | 8.4.1 Forward Bridge Mode                            |  |  |  |

|           |            | 8.4.2 Reverse Bridge Mode                            |  |  |  |

|           | 8.5        | Type 1-to-Type 1 Forwarding                          |  |  |  |

|           |            | 8.5.1 Forward Bridge Mode                            |  |  |  |

|           |            | 8.5.2 Reverse Bridge Mode                            |  |  |  |

|           | 8.6        | Type 1-to-Special Cycle Forwarding                   |  |  |  |

| 8            | 3.7  | PCI Ex | press En | hanced Configuration Mechanisms                                     | 63 |

|--------------|------|--------|----------|---------------------------------------------------------------------|----|

|              |      | 8.7.1  | Memory   | Mapped Indirect (Reverse Bridge Mode Only)                          | 63 |

| 8            | 8.8  |        |          | etry Mechanism                                                      |    |

|              |      |        |          | Bridge Mode                                                         |    |

|              |      | 8.8.2  | Reverse  | Bridge Mode                                                         | 64 |

|              |      |        |          | •                                                                   |    |

| Chapter 9 E  | Brid | ge Op  | eration. |                                                                     | 65 |

|              |      |        |          | Operation                                                           |    |

|              |      |        |          | Bridge Flow Control                                                 |    |

|              |      | 9.1.2  | Forward  | Bridge Buffer Size and Management                                   | 66 |

|              |      |        |          | Bridge Requester ID and Tag Assignment                              |    |

|              |      |        |          | Bridge PCI Express-to-PCI Forwarding (Downstream)                   |    |

|              |      |        | 9.1.4.1  | Transaction Types                                                   |    |

|              |      |        | 9.1.4.2  | Write Transactions                                                  |    |

|              |      |        | 9.1.4.3  | Read Transactions                                                   | 70 |

|              |      | 9.1.5  | Forward  | Bridge PCI-to-PCI Express Forwarding (Upstream)                     | 73 |

|              |      |        | 9.1.5.1  | Transaction Types                                                   |    |

|              |      |        | 9.1.5.2  | Write Decomposition                                                 |    |

|              |      |        | 9.1.5.3  | Read Decomposition                                                  |    |

|              |      |        | 9.1.5.4  | PCI Express Header Field Formation Rules                            |    |

|              |      |        | 9.1.5.5  | Requester ID and Tag                                                |    |

|              |      |        | 9.1.5.6  | Memory Write or Memory Write and Invalidate                         |    |

|              |      |        | 9.1.5.7  | Delayed Transactions                                                |    |

|              |      |        | 9.1.5.8  | Memory Read, Memory Read Line, or Memory Read Line Multiple .       |    |

|              |      |        | 9.1.5.9  | I/O Write                                                           | 78 |

|              |      |        | 9.1.5.10 | I/O Read                                                            | 78 |

|              |      | 9.1.6  | Forward  | Bridge PCI Transaction Terminations                                 | 79 |

|              |      |        | 9.1.6.1  | PCI Master Termination Initiated by PEX 8111                        | 80 |

|              |      |        | 9.1.6.2  | PCI Master Abort Received by PEX 8111                               |    |

|              |      |        | 9.1.6.3  | Delayed Write Target Termination Response                           |    |

|              |      |        | 9.1.6.4  | Posted Write Target Termination Response                            |    |

|              |      |        | 9.1.6.5  | Delayed Read Target Termination Response                            | 82 |

|              |      |        | 9.1.6.6  | Target Retry Initiated by PEX 8111                                  |    |

|              |      |        | 9.1.6.7  | Target Disconnect Initiated by PEX 8111                             | 83 |

|              |      |        | 9.1.6.8  | Target Abort Initiated by PEX 8111                                  | 83 |

| 9            | 9.2  | Revers | e Bridge | Operation                                                           | 84 |

|              |      | 9.2.1  | Reverse  | Bridge PCI-to-PCI Express Forwarding (Downstream)                   | 85 |

|              |      |        | 9.2.1.1  | Transaction Types                                                   | 85 |

|              |      |        |          |                                                                     |    |

| Chapter 10 E | Erro |        |          |                                                                     |    |

| 1            | 0.1  |        |          | e Error Handling                                                    |    |

|              |      | 10.1.1 | Forwar   | d Bridge PCI Express Originating Interface (Primary to Secondary) . |    |

|              |      |        | 10.1.1.1 | Received Poisoned TLP                                               |    |

|              |      |        | 10.1.1.2 | PCI Uncorrectable Data Errors                                       | 88 |

|              |      |        | 10.1.1.3 |                                                                     |    |

|              |      |        | 10.1.1.4 | PCI Master Abort on Posted Transaction                              | 89 |

|              |      |        | 10.1.1.5 | PCI Master Abort on Non-Posted Transaction                          | 89 |

|              |      |        | 10.1.1.6 | PCI Target Abort on Posted Transaction                              | 90 |

|              |      |        | 10.1.1.7 | 0                                                                   |    |

|              |      |        | 10.1.1.8 | PCI Retry Abort on Posted Transaction                               | 90 |

|              |      |        | 10.1.1.9 | PCI Retry Abort on Non-Posted Transaction                           | 90 |

|            | 10.1.2     |            | Bridge PCI Originating Interface (Secondary to Primary)         |      |

|------------|------------|------------|-----------------------------------------------------------------|------|

|            |            |            | Received PCI Errors                                             |      |

|            |            | 10.1.2.2   | Unsupported Request (UR) Completion Status                      | . 93 |

|            |            | 10.1.2.3   | Completer Abort (CA) Completion Status                          | . 93 |

|            | 10.1.3     | Forward    | Bridge Timeout Errors                                           | . 94 |

|            |            | 10.1.3.1   | PCI Express Completion Timeout Errors                           | . 94 |

|            |            | 10.1.3.2   | PCI Delayed Transaction Timeout Errors                          | . 94 |

|            | 10.1.4     |            | Bridge "Other" Errors                                           |      |

|            |            |            | Error Handling                                                  |      |

|            |            | -          | Bridge PCI Express Originating Interface (Secondary to Primary) |      |

|            |            |            | Received Poisoned TLP                                           |      |

|            |            |            | PCI Uncorrectable Data Errors                                   |      |

|            |            |            | PCI Address Errors                                              |      |

|            |            |            | PCI Master Abort on Posted Transaction                          |      |

|            |            |            | PCI Master Abort on Non-Posted Transaction                      |      |

|            |            |            | PCI Target Abort on Posted Transaction                          |      |

|            |            |            | PCI Target Abort on Non-Posted Transaction                      |      |

|            |            |            | PCI Retry Abort on Posted Transaction                           |      |

|            |            |            | PCI Retry Abort on Non-Posted Transaction                       |      |

|            | 1022       |            | Bridge PCI Originating Interface (Primary to Secondary)         |      |

|            | 10.2.2     |            | Received PCI Errors                                             |      |

|            |            |            | Unsupported Request (UR) Completion Status                      |      |

|            |            |            | Completer Abort (CA) Completion Status                          |      |

|            | 1023       |            | Bridge Timeout Errors                                           |      |

|            |            |            | PCI Express Completion Timeout Errors                           |      |

|            |            |            | PCI Delayed Transaction Timeout Errors                          |      |

|            | 1024       |            | Bridge PCI Express Error Messages                               |      |

|            |            |            | Bridge "Other" Errors                                           |      |

|            |            |            | U U U U U U U U U U U U U U U U U U U                           |      |

| Chapter 11 | Exclusive  | (Locked)   | Access                                                          | .103 |

|            | 11.1 Forwa | ard Bridge | Exclusive Accesses                                              | 103  |

|            | 11.1.1     | Forward    | Bridge Lock Sequence across PEX 8111                            | 103  |

|            | 11.1.2     | Forward    | Bridge PCI Master Rules for Supporting LOCK#                    | 104  |

|            | 11.1.3     | Forward    | Bridge Acquiring Exclusive Access across PEX 8111               | 104  |

|            | 11.1.4     | Forward    | Bridge Non-Posted Transactions and Lock                         | 104  |

|            | 11.1.5     | Forward    | Bridge Continuing Exclusive Access                              | 104  |

|            | 11.1.6     | Forward    | Bridge Completing Exclusive Access                              | 104  |

|            | 11.1.7     | Forward    | Bridge Invalid PCI Express Requests while Locked                | 105  |

|            | 11.1.8     |            | Bridge Locked Transaction Originating on PCI Bus                |      |

|            | 11.1.9     |            | Bridge PCI Bus Errors while Locked                              |      |

|            |            | 11.1.9.1   | PCI Master Abort during Posted Transaction                      | 105  |

|            |            |            | PCI Master Abort during Non-Posted Transaction                  |      |

|            |            |            | PCI Target Abort during Posted Transaction                      |      |

|            |            |            | PCI Target Abort during Non-Posted Transaction                  |      |

|            | 11.2 Reve  |            | Exclusive Accesses                                              |      |

|            | 11.2.1     |            | Bridge PCI Target Rules for Supporting LOCK#                    |      |

|            | 11.2.2     |            | Bridge Acquiring Exclusive Access across PEX 8111               |      |

|            | 11.2.3     |            | Bridge Completing Exclusive Access                              |      |

|            | 11.2.4     |            | Bridge PCI Express Locked Read Request                          |      |

|            | 11.2.5     |            | Bridge Limitations                                              |      |

| Chapter 12 | Power Management                                                              | 107   |

|------------|-------------------------------------------------------------------------------|-------|

|            | 12.1 Forward Bridge Power Management                                          | . 107 |

|            | 12.1.1 Forward Bridge Link State Power Management                             | . 107 |

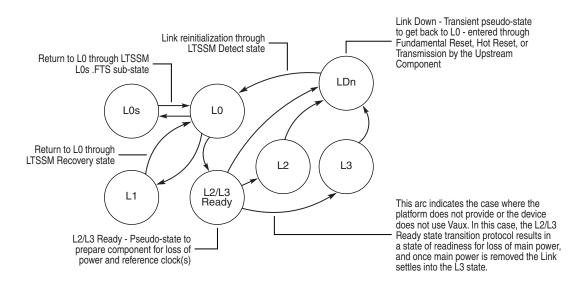

|            | 12.1.1.1 Link Power States                                                    | . 107 |

|            | 12.1.1.2 Link State Transitions                                               |       |

|            | 12.1.2 Forward Bridge Power Management States                                 | . 109 |

|            | 12.1.2.1 Power States                                                         |       |

|            | 12.1.3 Forward Bridge Power Management Signaling                              | . 110 |

|            | 12.1.4 Set Slot Power                                                         | . 110 |

|            | 12.2 Reverse Bridge Power Management                                          | . 111 |

|            | 12.2.1 Reverse Bridge Active State Power Management (ASPM)                    | . 111 |

|            | 12.2.1.1 ASPM States                                                          | . 111 |

|            | 12.2.2 Reverse Bridge Power Management States                                 | . 112 |

|            | 12.2.2.1 Power States                                                         | . 112 |

|            | 12.2.3 Reverse Bridge Power Down Sequence                                     | . 113 |

|            | 12.2.4 Reverse Bridge PMEOUT# Signal                                          | . 113 |

|            | 12.2.5 Reverse Bridge Set Slot Power                                          | . 113 |

|            | , , , , , , , , , , , , , , , , , , ,                                         |       |

| Chapter 13 | PCI Express Messages                                                          | 115   |

| •          | 13.1 Forward Bridge PCI Express Messages                                      |       |

|            | 13.1.1 Forward Bridge INTx# Interrupt Signaling                               |       |

|            | 13.1.2 Forward Bridge Power Management Messages                               |       |

|            | 13.1.3 Forward Bridge Error Signaling Messages                                |       |

|            | 13.1.4 Forward Bridge Locked Transactions Support                             |       |

|            | 13.1.5 Forward Bridge Slot Power Limit Support                                |       |

|            | 13.1.6 Forward Bridge Hot Plug Signaling Messages                             |       |

|            | 13.2 Reverse Bridge PCI Express Messages                                      |       |

|            | 13.2.1 Reverse Bridge INTx# Interrupt Message Support                         |       |

|            | 13.2.2 Reverse Bridge Power Management Message Support                        |       |

|            | 13.2.2.1 PME Handling Requirements                                            |       |

|            | 13.2.3 Reverse Bridge Error Signaling Message Support                         |       |

|            | 13.2.4 Reverse Bridge Locked Transaction Support                              |       |

|            | 13.2.5 Reverse Bridge Slot Power Limit Support                                |       |

|            |                                                                               |       |

| Chapter 14 | PCI Arbiter                                                                   | 119   |

| •          | 14.1 Overview                                                                 |       |

|            | 14.2 Internal Arbiter Mode                                                    |       |

|            | 14.2.1 Single-Level Mode                                                      |       |

|            | 14.2.2 Multi-Level Mode                                                       |       |

|            | 14.3 External Arbiter Mode                                                    |       |

|            | 14.4 Arbitration Parking                                                      |       |

|            |                                                                               | 0     |

| Chapter 15 | Forward Bridge Mode Configuration Registers                                   | 121   |

| Unapter 10 | 15.1 Register Description                                                     |       |

|            | 15.1.1 Indexed Addressing                                                     |       |

|            | 15.2 Configuration Access Types                                               |       |

|            | 15.3 Register Attributes                                                      |       |

|            | 15.4 Register Summary                                                         |       |

|            | 15.5 Register Maps                                                            |       |

|            | 15.5.1 PCI-Compatible Configuration Registers (Type 1)                        |       |

|            | 15.5.2 PCI-Compatible Extended Capability Registers for PCI Express Interface |       |

|            | 15.5.3 PCI Express Extended Capability Registers                              |       |

|            | 15.5.4 Main Control Registers                                                 |       |

|            |                                                                               | . 121 |

|                          | 15.6 PCI-Compatible Configuration Registers (Type 1) 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 120                                                                                                                                                                                                                                                                                                                                   |