# Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

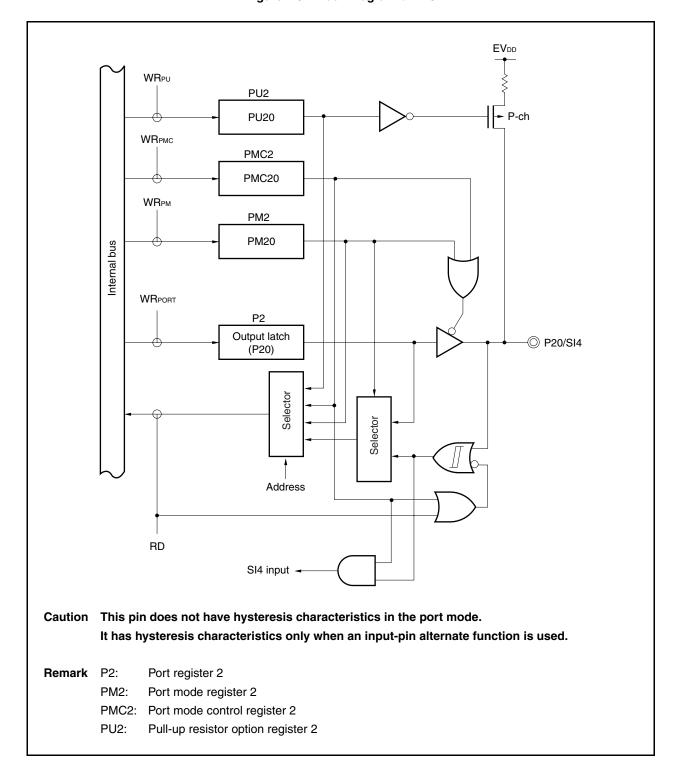

Renesas Electronics website: http://www.renesas.com

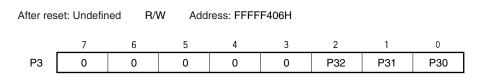

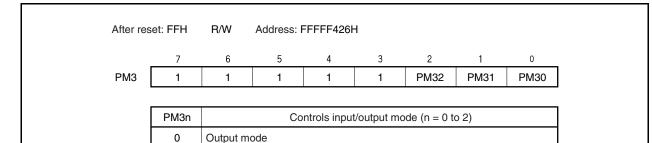

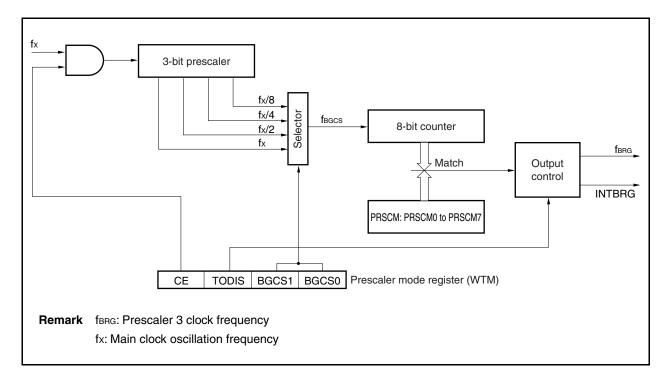

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

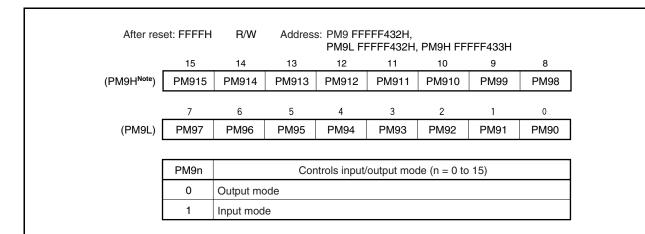

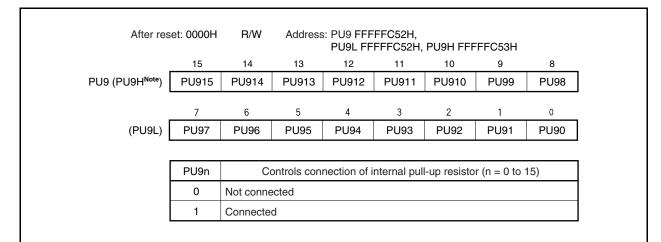

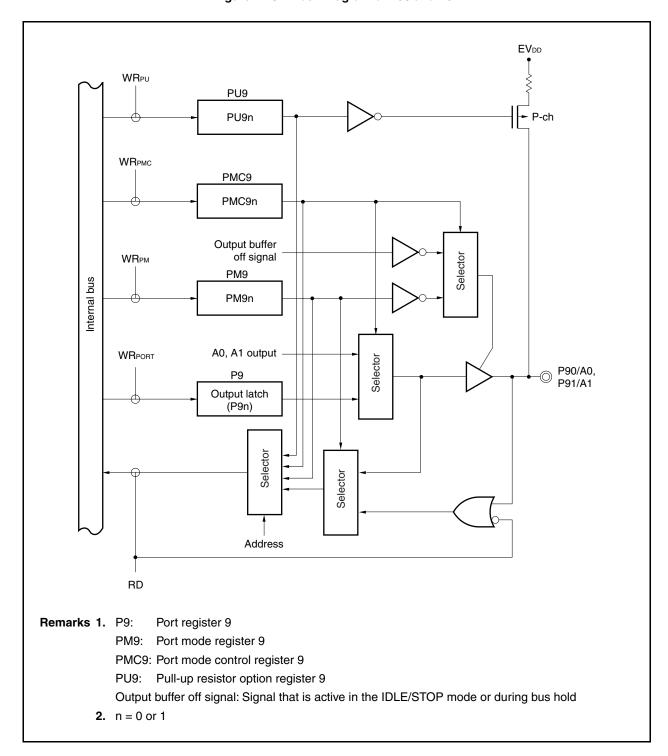

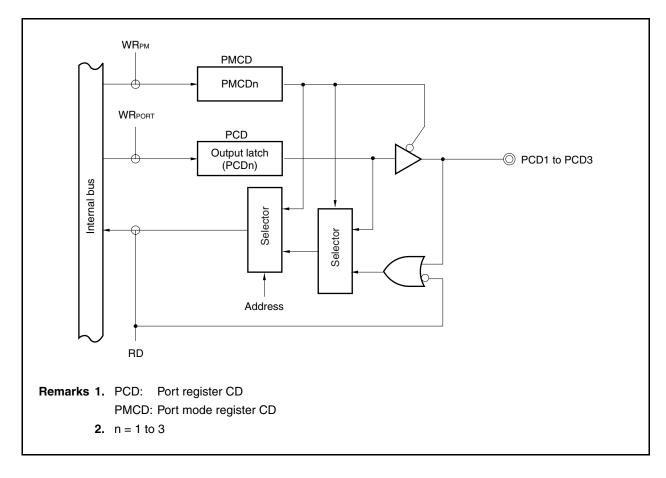

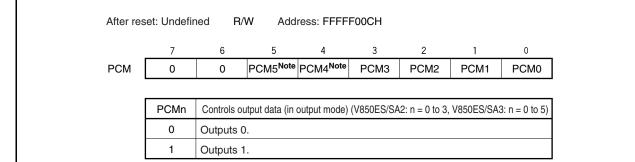

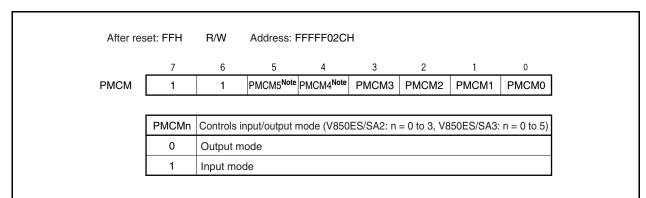

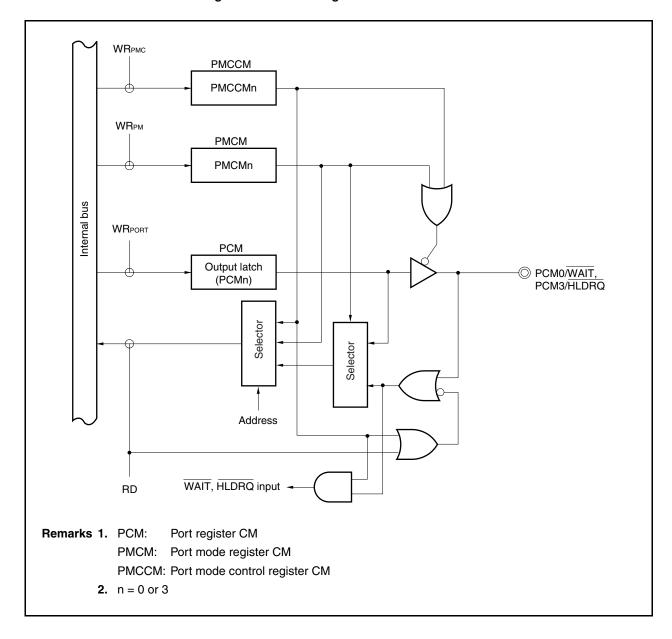

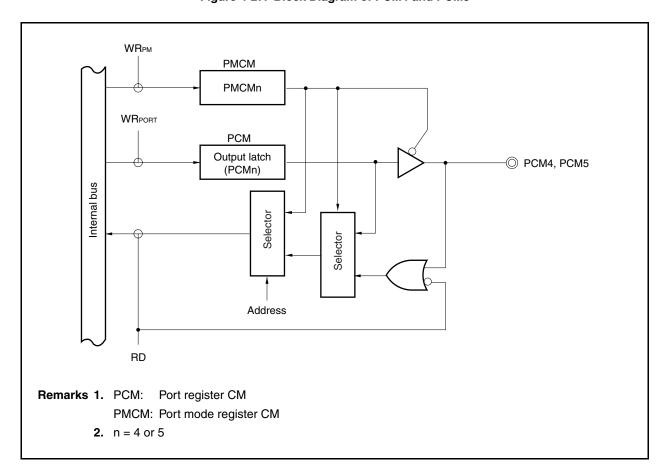

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

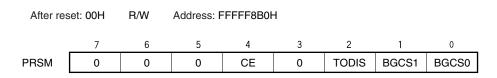

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

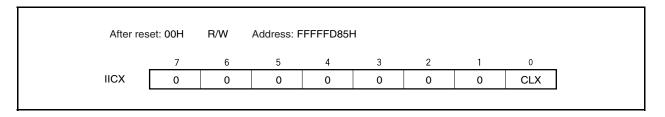

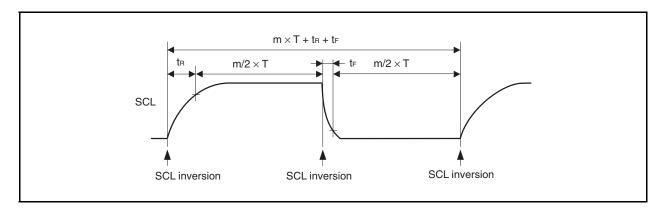

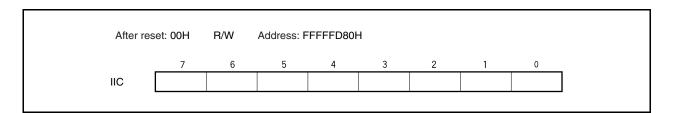

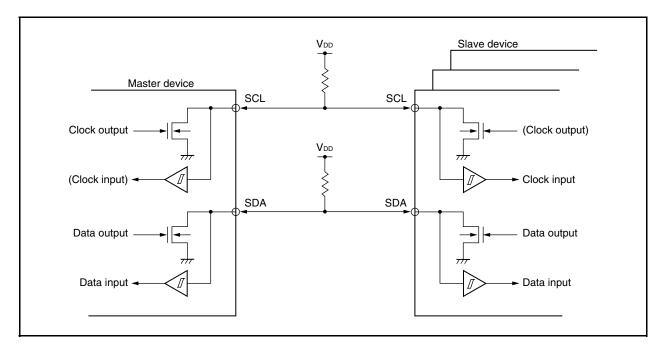

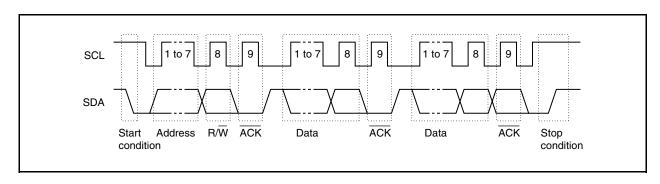

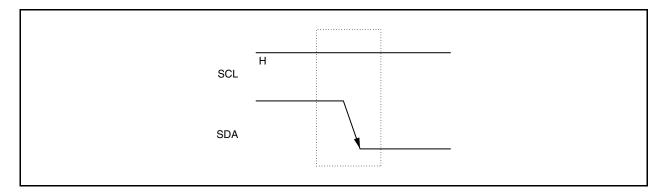

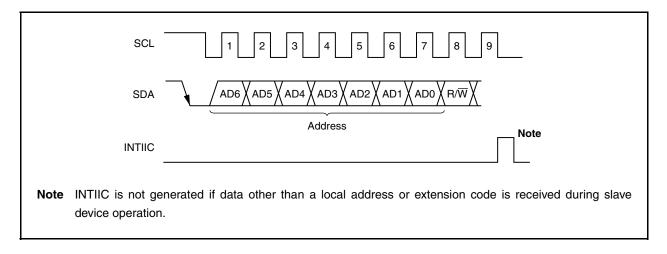

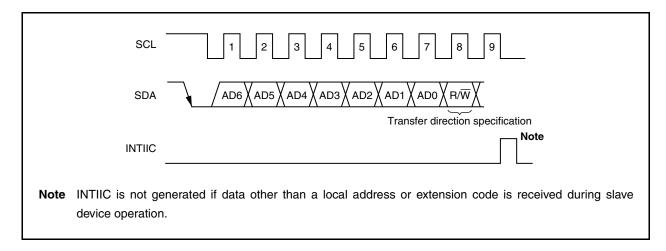

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

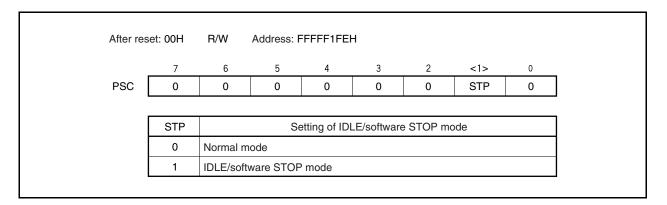

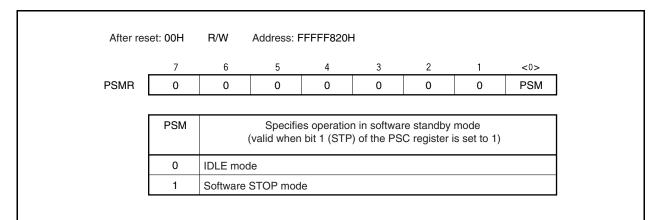

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

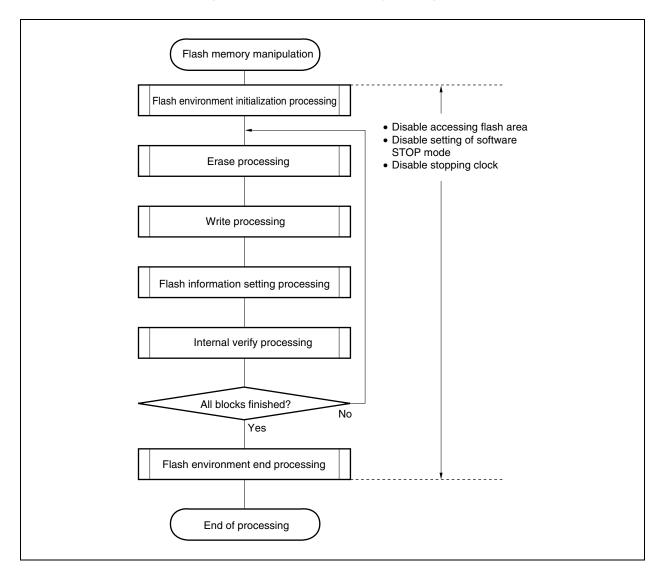

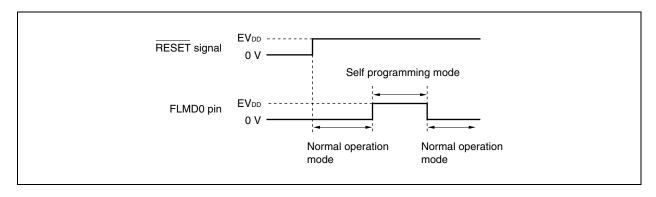

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# **User's Manual**

# V850ES/SA2, V850ES/SA3

# 32-Bit Single-Chip Microcontrollers

# **Hardware**

V850ES/SA2: V850ES/SA3:

$\mu$ PD703200  $\mu$ PD703204

$\mu$ PD703200Y  $\mu$ PD703204Y

$\mu$ PD703201  $\mu$ PD70F3204

μPD703201Y μPD70F3204Y

**μPD70F3201**

$\mu$ PD70F3201Y

Document No. U15905EJ2V1UD00 (2nd edition) Date Published August 2005 N CP(K)

# [MEMO]

#### NOTES FOR CMOS DEVICES —

#### (1) VOLTAGE APPLICATION WAVEFORM AT INPUT PIN

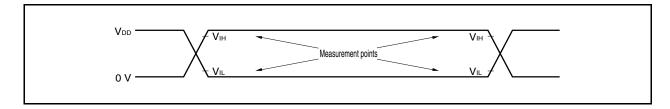

Waveform distortion due to input noise or a reflected wave may cause malfunction. If the input of the CMOS device stays in the area between  $V_{\rm IL}$  (MAX) and  $V_{\rm IH}$  (MIN) due to noise, etc., the device may malfunction. Take care to prevent chattering noise from entering the device when the input level is fixed, and also in the transition period when the input level passes through the area between  $V_{\rm IL}$  (MAX) and  $V_{\rm IH}$  (MIN).

### (2) HANDLING OF UNUSED INPUT PINS

Unconnected CMOS device inputs can be cause of malfunction. If an input pin is unconnected, it is possible that an internal input level may be generated due to noise, etc., causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND via a resistor if there is a possibility that it will be an output pin. All handling related to unused pins must be judged separately for each device and according to related specifications governing the device.

#### ③ PRECAUTION AGAINST ESD

A strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it when it has occurred. Environmental control must be adequate. When it is dry, a humidifier should be used. It is recommended to avoid using insulators that easily build up static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work benches and floors should be grounded. The operator should be grounded using a wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with mounted semiconductor devices.

#### (4) STATUS BEFORE INITIALIZATION

Power-on does not necessarily define the initial status of a MOS device. Immediately after the power source is turned ON, devices with reset functions have not yet been initialized. Hence, power-on does not guarantee output pin levels, I/O settings or contents of registers. A device is not initialized until the reset signal is received. A reset operation must be executed immediately after power-on for devices with reset functions.

#### (5) POWER ON/OFF SEQUENCE

In the case of a device that uses different power supplies for the internal operation and external interface, as a rule, switch on the external power supply after switching on the internal power supply. When switching the power supply off, as a rule, switch off the external power supply and then the internal power supply. Use of the reverse power on/off sequences may result in the application of an overvoltage to the internal elements of the device, causing malfunction and degradation of internal elements due to the passage of an abnormal current.

The correct power on/off sequence must be judged separately for each device and according to related specifications governing the device.

#### **6** INPUT OF SIGNAL DURING POWER OFF STATE

Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up power supply may cause malfunction and the abnormal current that passes in the device at this time may cause degradation of internal elements. Input of signals during the power off state must be judged separately for each device and according to related specifications governing the device.

These commodities, technology or software, must be exported in accordance with the export administration regulations of the exporting country. Diversion contrary to the law of that country is prohibited.

- The information in this document is current as of July, 2005. The information is subject to change

without notice. For actual design-in, refer to the latest publications of NEC Electronics data sheets or

data books, etc., for the most up-to-date specifications of NEC Electronics products. Not all

products and/or types are available in every country. Please check with an NEC Electronics sales

representative for availability and additional information.

- No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics. NEC Electronics assumes no responsibility for any errors that may appear in this document.

- NEC Electronics does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC Electronics products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Electronics or others.

- Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of a customer's equipment shall be done under the full responsibility of the customer. NEC Electronics assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.

- While NEC Electronics endeavors to enhance the quality, reliability and safety of NEC Electronics products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC Electronics products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment and anti-failure features.

- NEC Electronics products are classified into the following three quality grades: "Standard", "Special" and "Specific".

- The "Specific" quality grade applies only to NEC Electronics products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of an NEC Electronics product depend on its quality grade, as indicated below. Customers must check the quality grade of each NEC Electronics product before using it in a particular application.

- "Standard": Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots.

- "Special": Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support).

- "Specific": Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems and medical equipment for life support, etc.

The quality grade of NEC Electronics products is "Standard" unless otherwise expressly specified in NEC Electronics data sheets or data books, etc. If customers wish to use NEC Electronics products in applications not intended by NEC Electronics, they must contact an NEC Electronics sales representative in advance to determine NEC Electronics' willingness to support a given application.

(Note)

- (1) "NEC Electronics" as used in this statement means NEC Electronics Corporation and also includes its majority-owned subsidiaries.

- (2) "NEC Electronics products" means any product developed or manufactured by or for NEC Electronics (as defined above).

M8E 02.11-1

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC Electronics product in your application, please contact the NEC Electronics office in your country to obtain a list of authorized representatives and distributors. They will verify:

- · Device availability

- · Ordering information

- · Product release schedule

- · Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- · Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### [GLOBAL SUPPORT]

http://www.necel.com/en/support/support.html

# NEC Electronics America, Inc. (U.S.) NEC Electronics (Europe) GmbH NEC Electronics Hong Kong Ltd.

Santa Clara, California Tel: 408-588-6000 800-366-9782

Duesseldorf, Germany Tel: 0211-65030

#### • Sucursal en España Madrid, Spain

Tel: 091-504 27 87

### • Succursale Française

Vélizy-Villacoublay, France Tel: 01-30-675800

### Filiale Italiana

Milano, Italy Tel: 02-66 75 41

#### Branch The Netherlands

Eindhoven. The Netherlands Tel: 040-2654010

#### Tyskland Filial

Taeby, Sweden Tel: 08-63 87 200

#### United Kingdom Branch

Milton Keynes, UK Tel: 01908-691-133

Hong Kong Tel: 2886-9318

#### **NEC Electronics Hong Kong Ltd.**

Seoul Branch Seoul, Korea Tel: 02-558-3737

#### **NEC Electronics Shanghai Ltd.**

Shanghai, P.R. China Tel: 021-5888-5400

#### **NEC Electronics Taiwan Ltd.**

Taipei, Taiwan Tel: 02-2719-2377

#### **NEC Electronics Singapore Pte. Ltd.**

Novena Square, Singapore Tel: 6253-8311

J05.6

#### **PREFACE**

Readers

This manual is intended for users who wish to understand the functions of the V850ES/SA2 ( $\mu$ PD703200, 703200Y, 703201, 703201Y, 70F3201, 70F3201Y) and V850ES/SA3 ( $\mu$ PD703204, 703204Y, 70F3204, 70F3204Y) and design application systems using these products.

**Purpose**

This manual is intended to give users an understanding of the hardware functions of the V850ES/SA2 and V850ES/SA3 shown in the Organization below.

Organization

This manual is divided into two parts: Hardware (this manual) and Architecture (V850ES Architecture User's Manual).

#### Hardware

- Pin functions

- CPU function

- On-chip peripheral functions

- Flash memory programming

- Electrical specifications

#### Architecture

- Data types

- Register set

- Instruction format and instruction set

- · Interrupts and exceptions

- Pipeline operation

#### **How to Read This Manual**

It is assumed that the readers of this manual have general knowledge in the fields of electrical engineering, logic circuits, and microcontrollers.

To learn the detailed functions of a register whose register name is known

→ Refer to APPENDIX A REGISTER INDEX.

To understand the details of an instruction function

→ Refer to the **V850ES Architecture User's Manual** available separately.

#### Register format

→The name of the bit whose number is in angle brackets (<>) in the figure of the register format of each register is defined as a reserved word in the device file.

To understand the overall functions of the V850ES/SA2 and V850ES/SA3

→ Read this manual according to the **CONTENTS**.

To know the electrical specifications of the V850ES/SA2 and V850ES/SA3

→ Refer to CHAPTER 22 ELECTRICAL SPECIFICATIONS.

The mask ★ shows the major revised points.

#### **Conventions** Data significance:

Higher digits on the left and lower digits on the right

Active low representation:  $\overline{xxx}$  (overscore over pin or signal name)

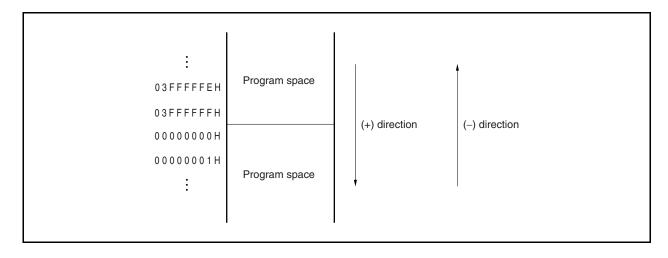

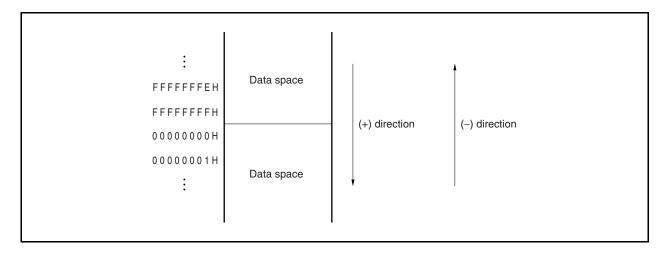

Memory map address: Higher addresses on the top and lower addresses on

the bottom

**Note:** Footnote for item marked with **Note** in the text

Caution: Information requiring particular attention

**Remark:** Supplementary information Numeric representation: Binary ... xxxx or xxxxB

Decimal ... xxxx

Hexadecimal ... xxxxH

Prefix indicating power of 2 (address space, memory

capacity):  $K \text{ (kilo): } 2^{10} = 1,024$

M (mega):  $2^{20} = 1,024^2$ G (giga):  $2^{30} = 1,024^3$

#### **Related Documents**

The related documents indicated in this publication may include preliminary versions. However, preliminary versions are not marked as such.

#### Documents related to V850ES/SA2 and V850ES/SA3

| Document Name                                 | Document No. |

|-----------------------------------------------|--------------|

| V850ES Architecture User's Manual             | U15943E      |

| V850ES/SA2, V850ES/SA3 Hardware User's Manual | This manual  |

| V850ES/SA2, V850ES/SA3 Application Note       | U16764E      |

#### Documents related to development tools

| Document Name                                | Document No.      |         |

|----------------------------------------------|-------------------|---------|

| IE-V850ES-G1 (In-Circuit Emulator)           |                   | U16313E |

| IE-703204-G1-EM1 (In-Circuit Emulator Option | on Board)         | U16622E |

| CA850 C Compiler Package Ver. 2.50           | Operation         | U16053E |

|                                              | C Language        | U16054E |

|                                              | Assembly Language | U16042E |

| PM plus Ver. 5.10                            |                   | U16569E |

| ID850 Integrated Debugger Ver. 2.50          | Operation         | U16217E |

| RX850 Real-Time OS Ver. 3.13 or Later        | Basics            | U13430E |

|                                              | Installation      | U13410E |

|                                              | Technical         | U13431E |

| RX850 Pro Real-Time OS Ver. 3.15             | Basics            | U13773E |

|                                              | Installation      | U13774E |

|                                              | Technical         | U13772E |

| RD850 Task Debugger Ver. 3.01                | U13737E           |         |

| RD850 Pro Task Debugger Ver. 3.01            |                   | U13916E |

| AZ850 System Performance Analyzer Ver. 3.20  |                   | U14410E |

| PG-FP4 Flash Memory Programmer               |                   | U15260E |

# **CONTENTS**

| 1617191920242426293637 ed Pins49 |

|----------------------------------|

| 1819202426293637                 |

| 192024262929                     |

| 192024262936                     |

| 192426292936                     |

| 202426292936                     |

| 2426292936                       |

| 24292936                         |

| 262936                           |

| 29<br>29<br>36                   |

| 29<br>36                         |

| 36<br>37                         |

| 37                               |

|                                  |

| ed Pins49                        |

|                                  |

| 53                               |

| 53                               |

| 54                               |

| 55                               |

| 56                               |

| 62                               |

| 63                               |

| 63                               |

| 64                               |

| 65                               |

| 66                               |

| 68                               |

| 73                               |

| 75                               |

| 83                               |

| 87                               |

| 88                               |

| 88                               |

| 88                               |

| 88                               |

|                                  |

|                                  |

|            | 4.2.1               | V850ES/SA2                                                                                   | 89  |

|------------|---------------------|----------------------------------------------------------------------------------------------|-----|

|            | 4.2.2               | V850ES/SA3                                                                                   | 90  |

| 4.3        | Port C              | onfiguration                                                                                 | 91  |

|            | 4.3.1               | Port 0                                                                                       |     |

|            | 4.3.2               | Port 2                                                                                       |     |

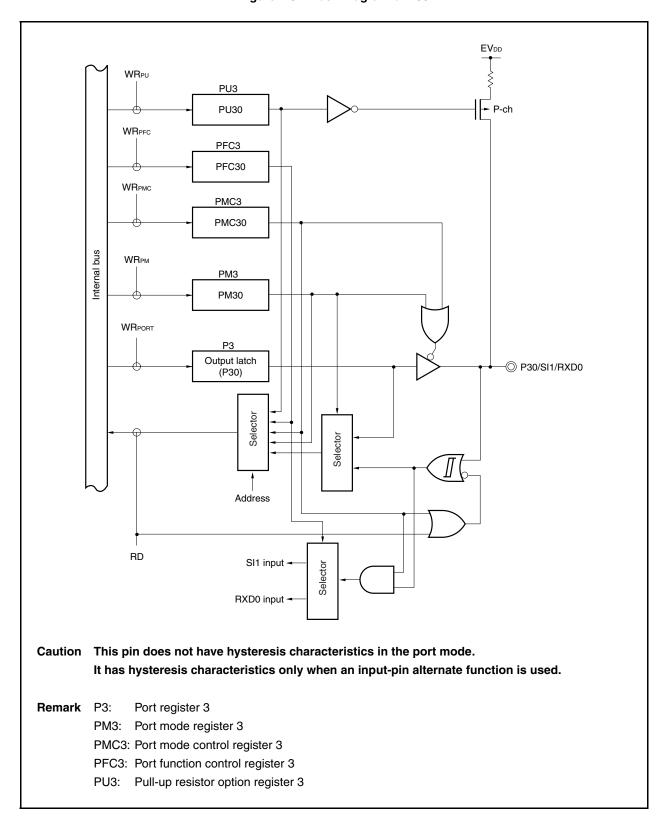

|            | 4.3.3               | Port 3                                                                                       | 106 |

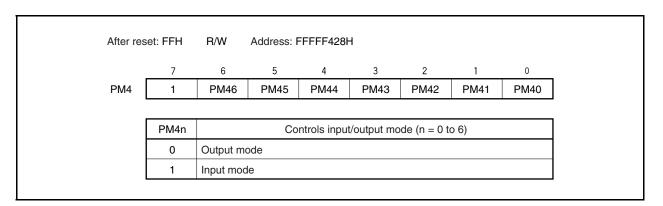

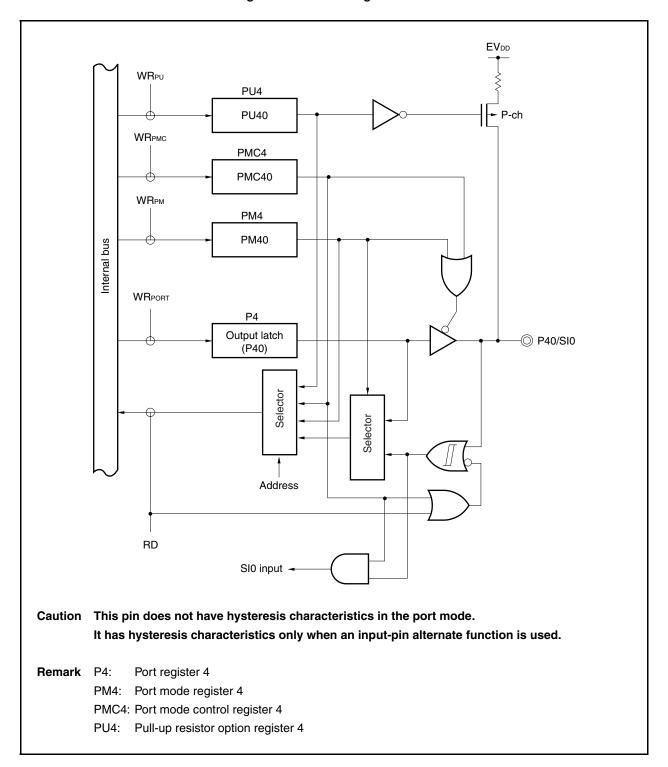

|            | 4.3.4               | Port 4                                                                                       | 113 |

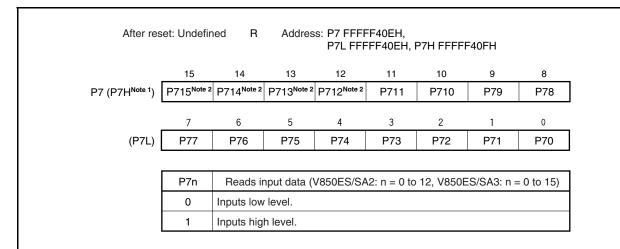

|            | 4.3.5               | Port 7                                                                                       | 123 |

|            | 4.3.6               | Port 8                                                                                       | 125 |

|            | 4.3.7               | Port 9                                                                                       | 127 |

|            | 4.3.8               | Port CD                                                                                      | 143 |

|            | 4.3.9               | Port CM                                                                                      | 146 |

|            | 4.3.10              | Port CS                                                                                      | 152 |

|            | 4.3.11              | Port CT                                                                                      | 157 |

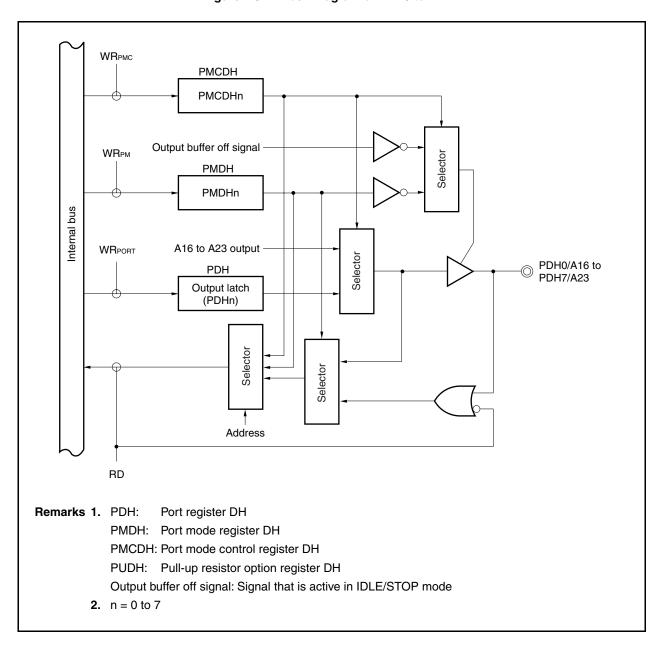

|            | 4.3.12              | Port DH                                                                                      | 162 |

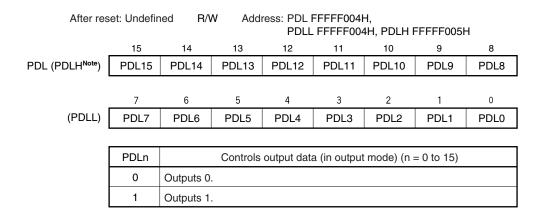

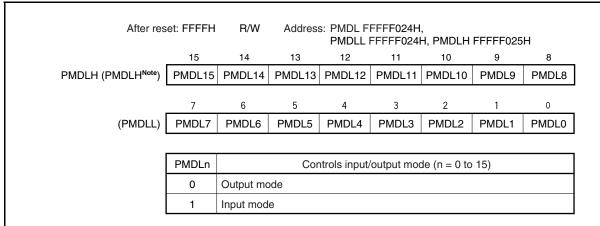

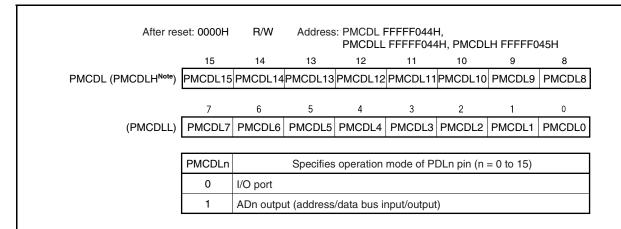

|            | 4.3.13              | Port DL                                                                                      | 166 |

| 4.4        | Cautio              | ons                                                                                          | 176 |

|            | 4.4.1               | Writing data to I/O port                                                                     | 176 |

|            | 4.4.2               | Reading data from I/O port                                                                   | 176 |

| 5.1<br>5.2 |                     | resontrol Pinsontrol                                                                         |     |

| 5.2        | Bus C               | ontrol Pins                                                                                  | 177 |

|            | 5.2.1               | Pin status when internal ROM, internal RAM, or internal peripheral I/O is accessed           |     |

|            | 5.2.2               | Pin status in each operation mode                                                            |     |

| 5.3        |                     | ry Block Function                                                                            |     |

|            | 5.3.1<br><b>-</b> . | Chip select control function                                                                 |     |

| 5.4        |                     | nal Bus Interface Mode Control Function                                                      |     |

| 5.5        |                     | ccess                                                                                        |     |

|            | 5.5.1               | Number of clocks for access                                                                  |     |

|            | 5.5.2               | Bus size setting function                                                                    |     |

| F. C       | 5.5.3               | Access by bus size                                                                           |     |

| 5.6        |                     | unction                                                                                      |     |

|            | 5.6.1<br>5.6.2      | Programmable wait function                                                                   |     |

|            | 5.6.2<br>5.6.3      | External wait function                                                                       |     |

|            |                     | Relationship between programmable wait and external wait  Programmable address wait function |     |

| 5.7        | 5.6.4               | rogrammable address wait function                                                            |     |

| 5.7<br>5.8 |                     | old Function                                                                                 |     |

| 5.0        | 5.8.1               | Functional outline                                                                           |     |

|            | 5.8.2               | Bus hold procedure                                                                           |     |

|            | 5.8.3               | Operation in power save mode                                                                 |     |

| 5.9        |                     | riority                                                                                      |     |

|            |                     | Jary Operation Conditions                                                                    |     |

|        | 5.10.1  | Program space                                    | 195 |

|--------|---------|--------------------------------------------------|-----|

|        | 5.10.2  | Data space                                       | 195 |

| 5.11   | 1 Bus T | iming                                            | 196 |

| CHAPTE | ER 6 CI | LOCK GENERATION FUNCTION                         | 202 |

| 6.1    | Overv   | riew                                             | 202 |

| 6.2    | Config  | guration                                         | 203 |

| 6.3    | Contro  | ol Registers                                     | 205 |

| 6.4    | Opera   | ation                                            | 208 |

|        | 6.4.1   | Operation of each clock                          | 208 |

|        | 6.4.2   | Clock output function                            | 208 |

| 6.5    | Presca  | aler 3                                           | 209 |

|        | 6.5.1   | Control register                                 | 210 |

|        | 6.5.2   | Generation of clock                              | 211 |

| CHAPTE | ER 7 16 | 6-BIT TIMER/EVENT COUNTERS 0 AND 1               | 212 |

| 7.1    | Featu   | res                                              | 212 |

| 7.2    |         | ional Overview                                   |     |

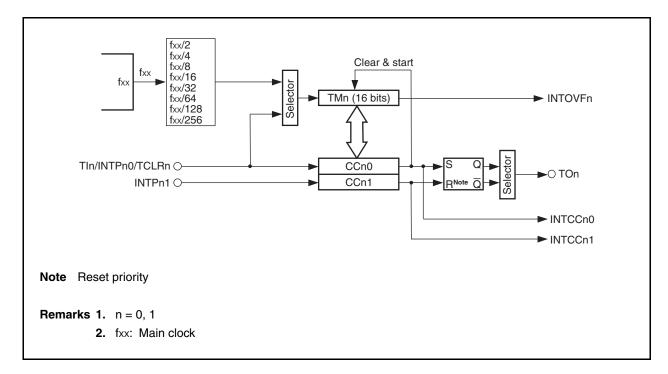

| 7.3    | Config  | guration                                         | 213 |

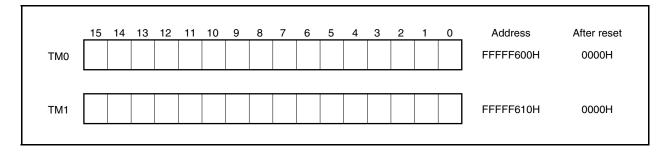

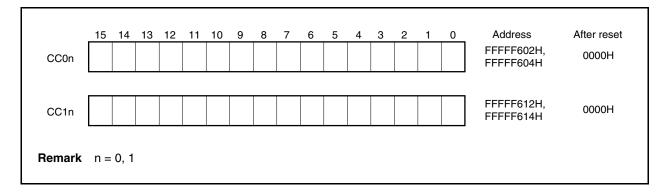

| 7.4    | Contro  | ol Registers                                     | 217 |

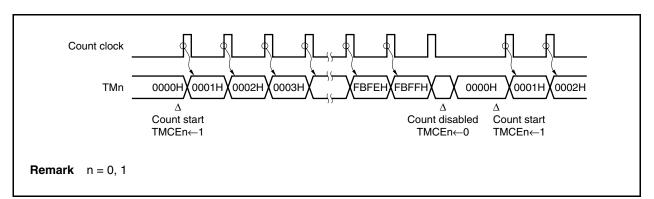

| 7.5    | Opera   | ation                                            | 222 |

| 7.6    | Applic  | cation Examples                                  | 229 |

| 7.7    | Cautio  | ons                                              | 238 |

| CHAPTE | ER 8 8- | BIT TIMER/EVENT COUNTERS 2 TO 5                  | 239 |

| 8.1    | Functi  | ional Overview                                   | 239 |

| 8.2    |         | guration                                         |     |

| 8.3    | _       | ol Registers                                     |     |

| 8.4    |         | ation                                            |     |

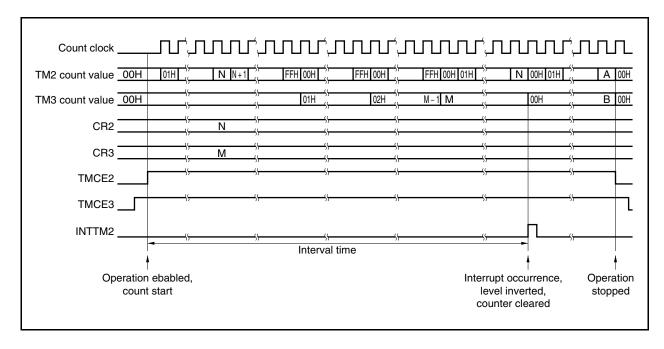

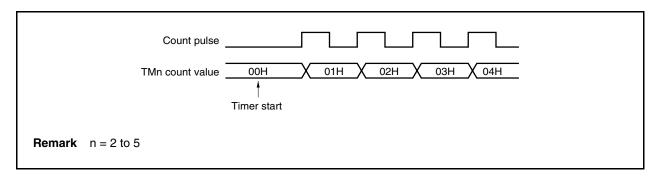

|        | 8.4.1   | Operation as interval timer (8 bits)             |     |

|        | 8.4.2   | Operation as external event counter (8 bits)     |     |

|        | 8.4.3   | Square-wave output operation (8-bit resolution)  |     |

|        | 8.4.4   | 8-bit PWM output operation                       |     |

|        | 8.4.5   | Operation as interval timer (16 bits)            |     |

|        | 8.4.6   | Operation as external event counter (16 bits)    |     |

|        | 8.4.7   | Square-wave output operation (16-bit resolution) |     |

|        | 8.4.8   | Cautions                                         |     |

| CHAPTE | ER 9 RE | EAL-TIME COUNTER FUNCTION                        | 259 |

| 9.1    | Functi  | ion                                              | 259 |

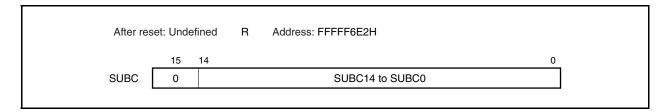

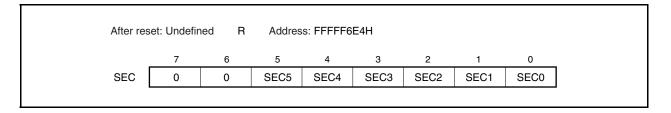

| 9.2    | Contro  | ol Registers                                     | 260 |

| 9.3    | Opera   | ation                                            | 266 |

|        | 9.3.1   | Initializing counter and count-up                | 266 |

|        | 9.3.2   | Rewriting counter                                | 266 |

|                         | 9.3.3 Controlling interrupt request signal output            | 267      |

|-------------------------|--------------------------------------------------------------|----------|

|                         | 9.3.4 Notes                                                  | 267      |

| CHAPTEI                 | R 10 WATCHDOG TIMER FUNCTIONS                                | 269      |

| 10.1                    | Functions                                                    | 269      |

|                         | Configuration                                                |          |

|                         | Control Registers                                            |          |

|                         | Operation                                                    |          |

|                         | 10.4.1 Operation as watchdog timer                           | 274      |

|                         | 10.4.2 Operation as interval timer                           |          |

|                         | 10.4.3 Oscillation stabilization time selection function     |          |

| CHAPTE                  | R 11 A/D CONVERTER                                           | 277      |

| 11.1                    | Function                                                     | 277      |

| 11.2                    | Configuration                                                | 279      |

| 11.3                    | Control Registers                                            | 281      |

| 11.4                    | Operation                                                    | 288      |

|                         | 11.4.1 Conversion operation                                  | 288      |

|                         | 11.4.2 Conversion operation (power fail monitoring function) | 288      |

| 11.5                    | Notes on Use                                                 | 289      |

| 11.6                    | How to Read A/D Converter Characteristics Table              | 290      |

| HAPTEI                  | R 12 D/A CONVERTER                                           | 29       |

| 12.1                    | Functions                                                    | 294      |

|                         | Configuration                                                |          |

|                         | Control Registers                                            |          |

|                         | Operation                                                    |          |

|                         | 12.4.1 Operation in normal mode                              |          |

|                         | 12.4.2 Operation in real-time output mode                    |          |

|                         | 12.4.3 Cautions                                              |          |

| CHAPTEI                 | R 13 ASYNCHRONOUS SERIAL INTERFACE n (UARTn)                 | 299      |

| 13.1                    | Features                                                     | 299      |

|                         | 13.1.1 Switching modes between UART0 and CSI1                | 300      |

| 13.2                    | Configuration                                                | 301      |

| 13.3                    | Control Registers                                            | 303      |

| 13.4                    | Interrupt Requests                                           | 310      |

| 40 =                    | Operation                                                    | 211      |

| 13.5                    | Operation                                                    |          |

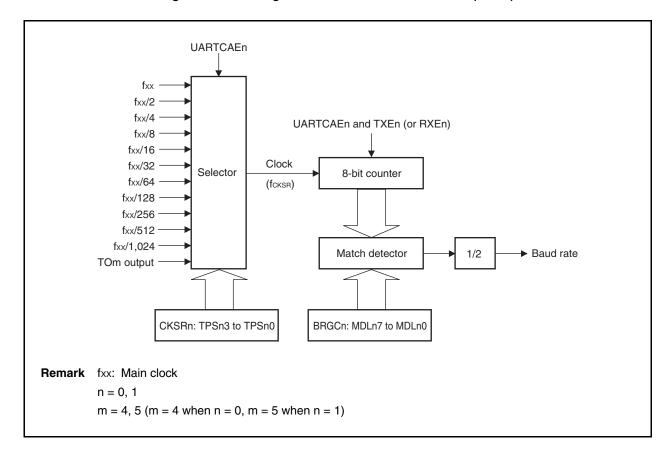

| 13.5<br>13.6            | Dedicated Baud Rate Generator n (BRGn)                       |          |

| 13.6                    | •                                                            | 323      |

| 13.6<br>13.7            | Dedicated Baud Rate Generator n (BRGn)                       | 323      |

| 13.6<br>13.7<br>CHAPTEI | Dedicated Baud Rate Generator n (BRGn)                       | 32<br>33 |

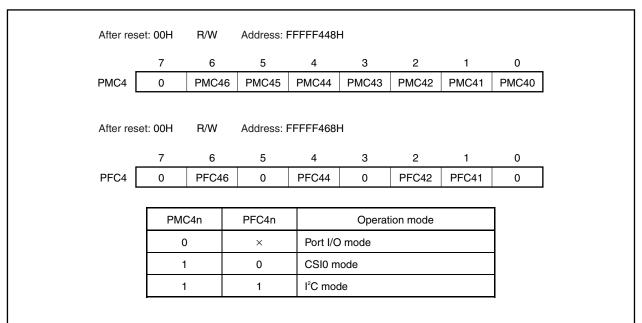

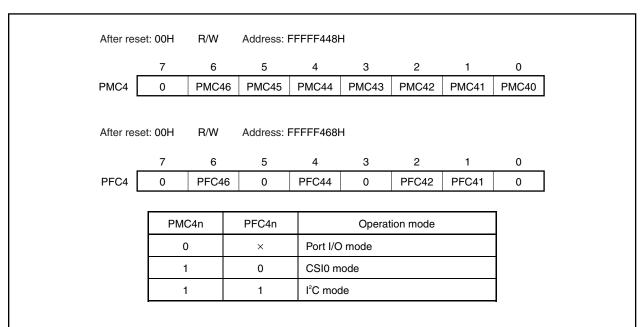

|        | 14.1.1 Switching modes between CSI0 and I <sup>2</sup> C        | 333 |

|--------|-----------------------------------------------------------------|-----|

|        | 14.1.2 Switching modes between CSI1 and UART0                   | 334 |

| 14.2   | Configuration                                                   | 334 |

| 14.3   | Control Registers                                               | 336 |

| 14.4   | Operation                                                       | 342 |

| 14.5   | Output Pins                                                     | 345 |

| 14.6   | System Configuration Example                                    | 346 |

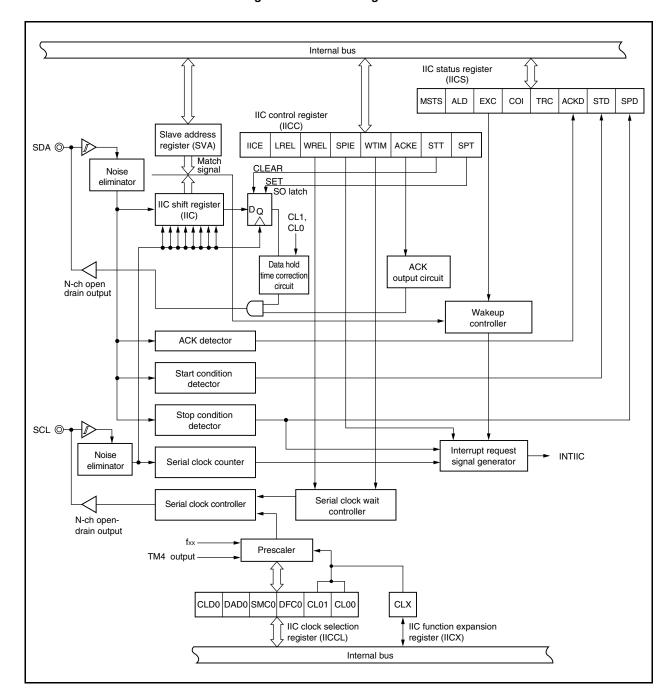

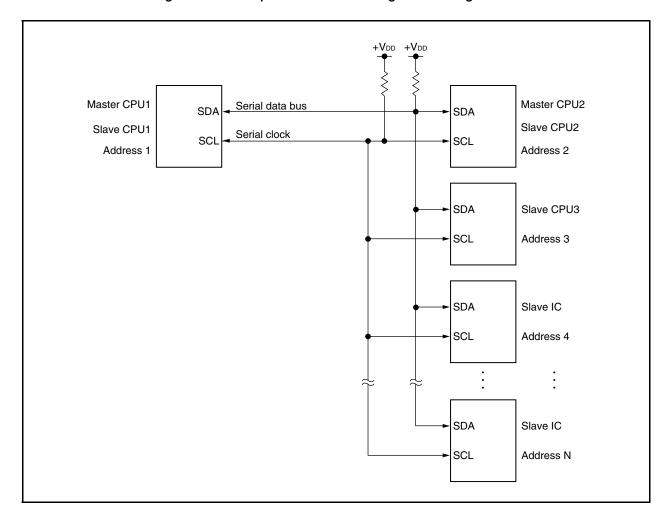

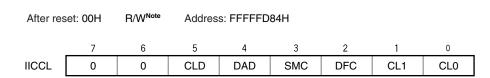

| CHAPTE | R 15 I <sup>2</sup> C BUS                                       | 347 |

| 15.1   | Features                                                        | 347 |

|        | 15.1.1 Switching modes between I <sup>2</sup> C and CSI0        | 348 |

| 15.2   | Configuration                                                   | 351 |

| 15.3   | Control Registers                                               | 353 |

| 15.4   | I <sup>2</sup> C Bus Mode Functions                             | 364 |

| 15.5   | I <sup>2</sup> C Bus Definitions and Control Methods            | 365 |

| 15.6   | I <sup>2</sup> C Interrupt Request (INTIIC)                     |     |

| 15.7   | Interrupt Request (INTIIC) Generation Timing and Wait Control   | 390 |

| 15.8   | 7.44.000                                                        |     |

|        | Error Detection                                                 |     |

|        | 0 Extension Code                                                |     |

|        | 1 Arbitration                                                   |     |

|        | 2 Wakeup Function                                               |     |

|        | 3 Communication Reservation                                     |     |

|        | 4 Cautions                                                      |     |

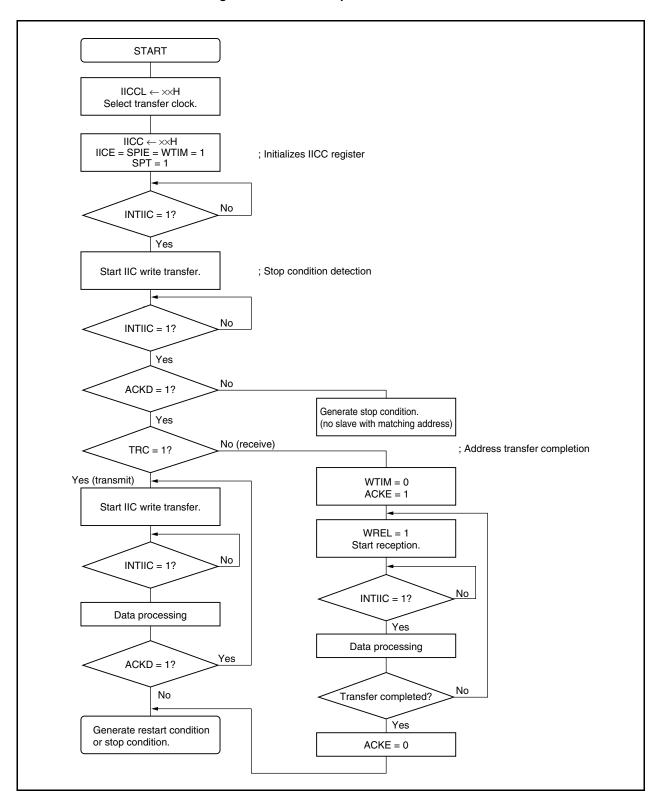

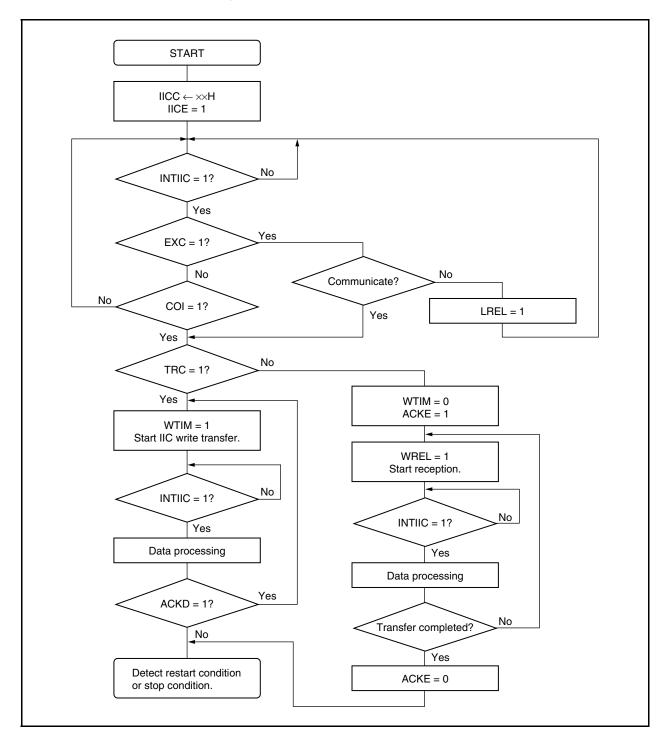

|        | 5 Communication Operations                                      |     |

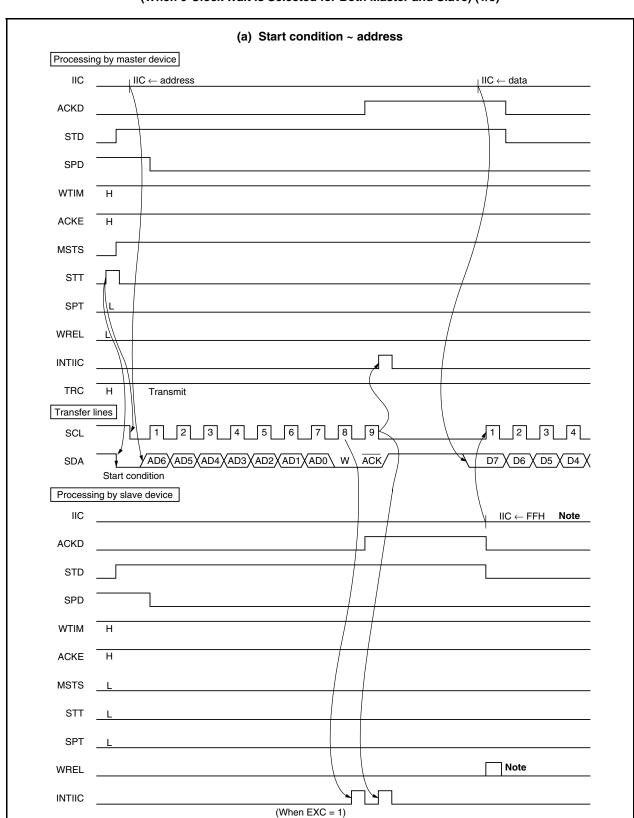

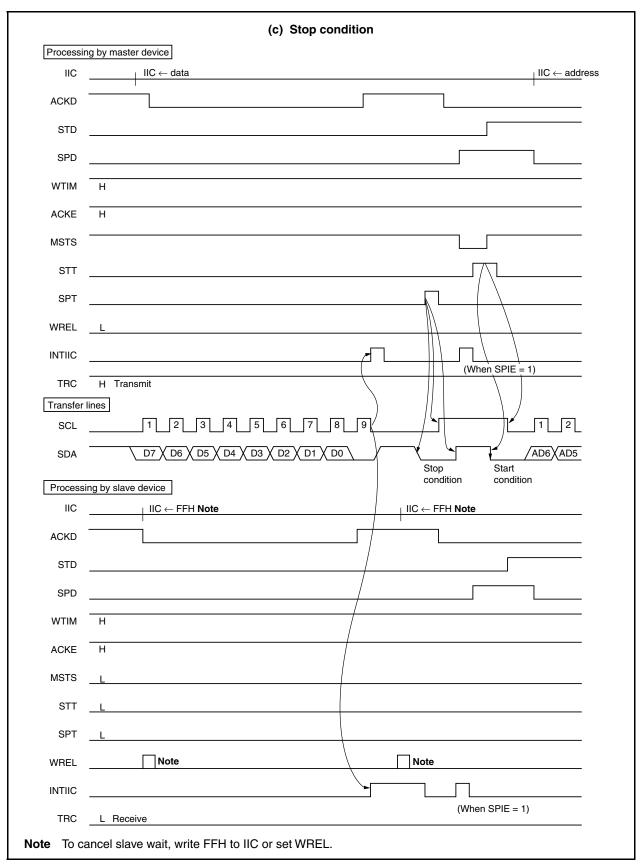

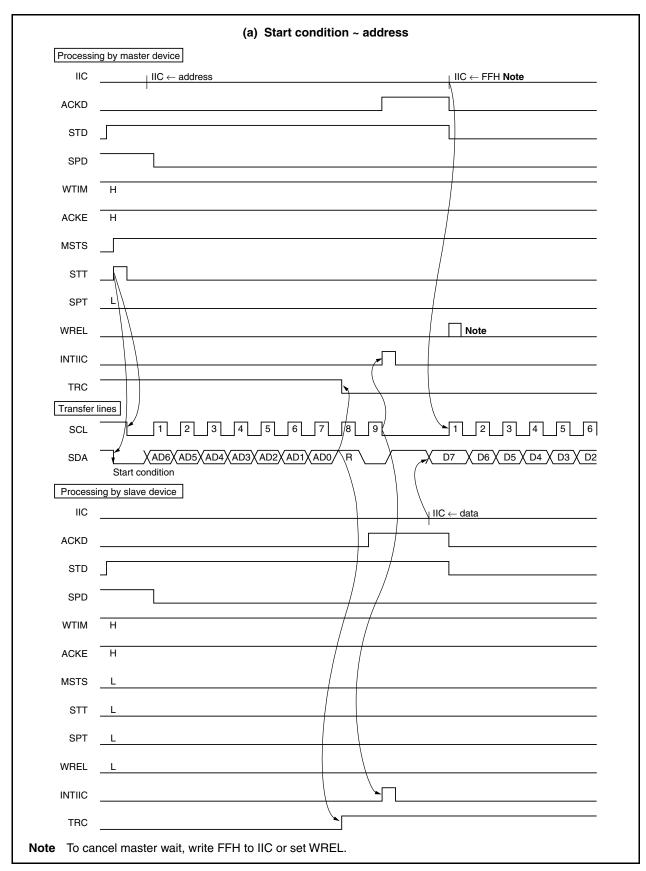

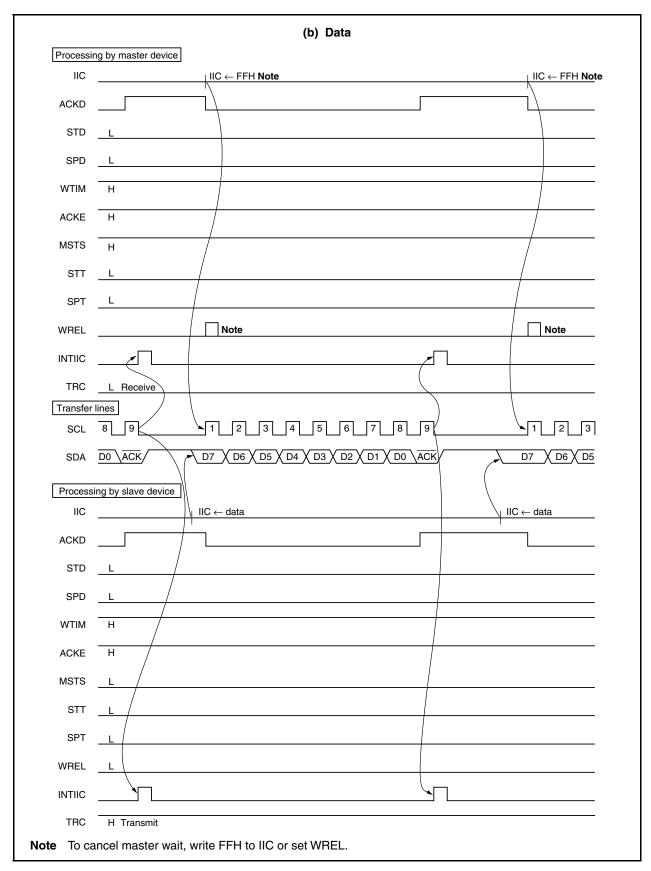

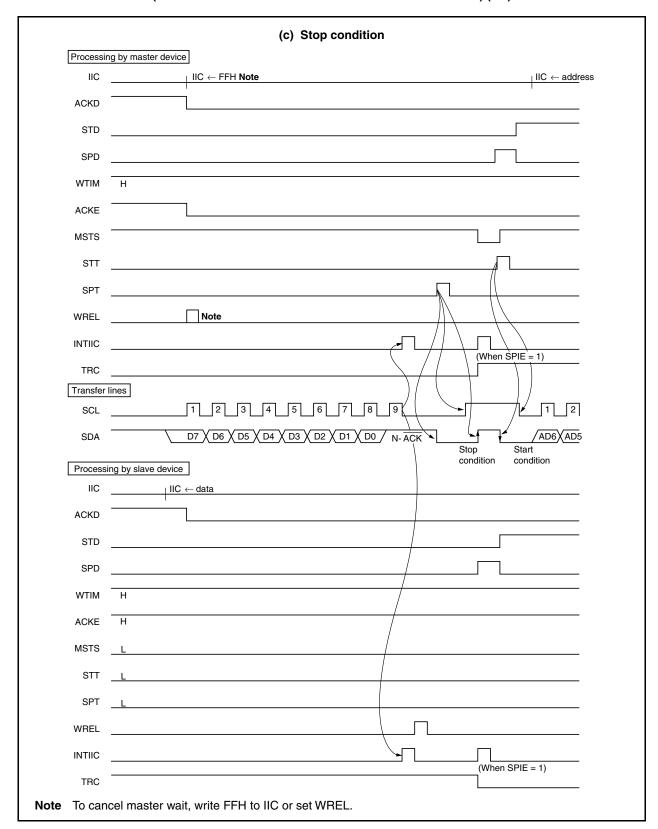

| 15.1   | 6 Timing of Data Communication                                  | 401 |

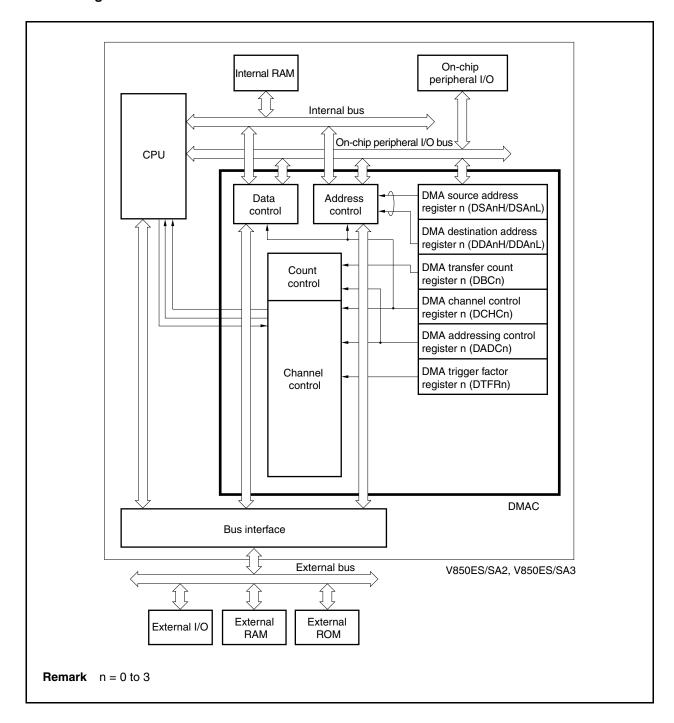

| CHAPTE | R 16 DMA FUNCTIONS (DMA CONTROLLER)                             | 408 |

| 16.1   | Features                                                        | 408 |

| 16.2   | Configuration                                                   | 409 |

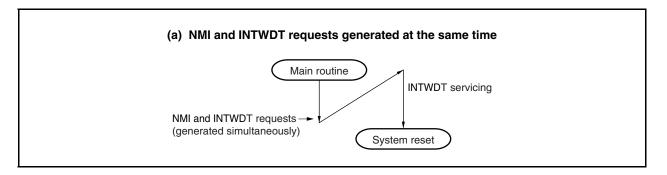

| 16.3   | Control Registers                                               | 410 |

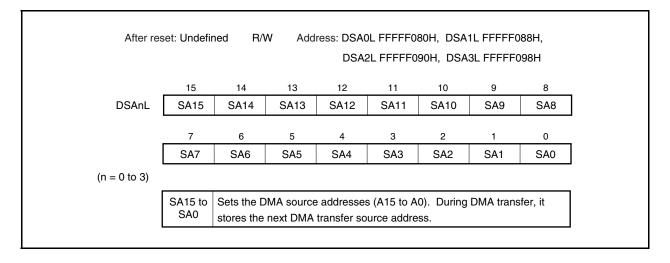

|        | 16.3.1 DMA source address registers 0 to 3 (DSA0 to DSA3)       | 410 |

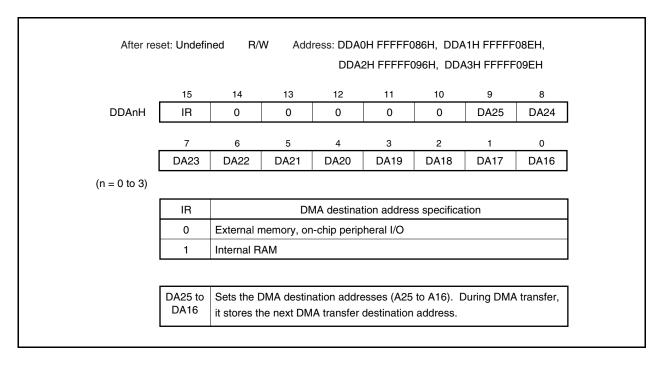

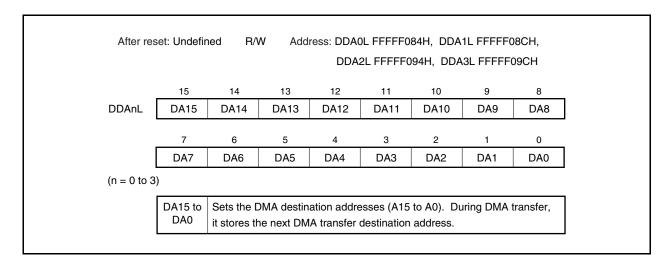

|        | 16.3.2 DMA destination address registers 0 to 3 (DDA0 to DDA3)  | 411 |

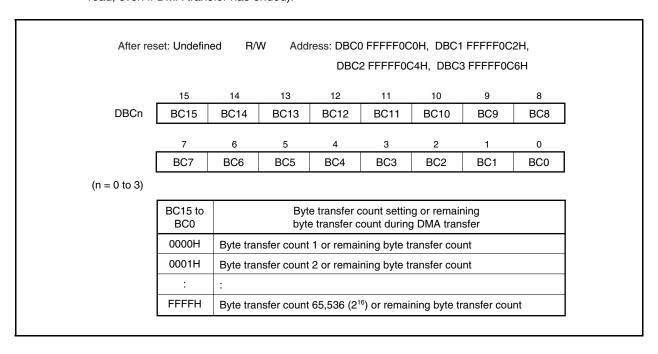

|        | 16.3.3 DMA byte count registers 0 to 3 (DBC0 to DBC3)           | 412 |

|        | 16.3.4 DMA addressing control registers 0 to 3 (DADC0 to DADC3) | 413 |

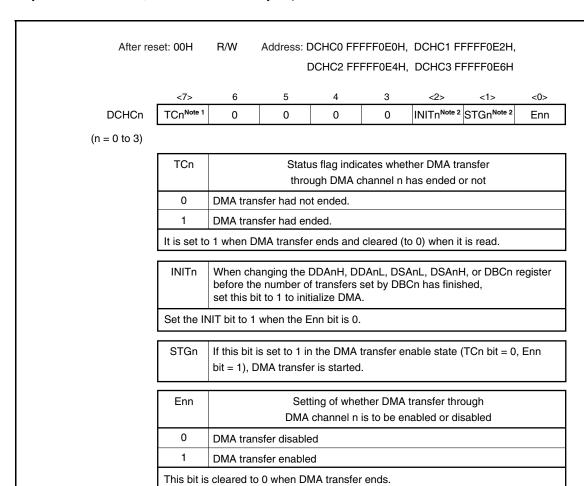

|        | 16.3.5 DMA channel control registers 0 to 3 (DCHC0 to DCHC3)    | 414 |

|        | 16.3.6 DMA trigger factor registers 0 to 3 (DTFR0 to DTFR3)     | 415 |

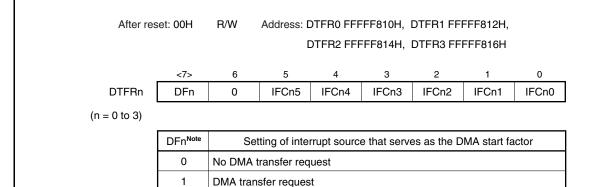

| 16.4   | DMA Bus States                                                  | 417 |

|        | 16.4.1 Types of bus states                                      | 417 |

|        | 16.4.2 DMAC bus cycle state transition                          | 418 |

| 16.5   | Transfer Mode                                                   | 419 |

|        | 16.5.1 Single transfer mode                                     |     |

| 16.6   | Transfer Types                                                  | 419 |

|        | 16.6.1 Two-cycle transfer                                       | 419 |

| 16.7   | Transfer Object                                                         | 420 |

|--------|-------------------------------------------------------------------------|-----|

|        | 16.7.1 Transfer type and transfer object                                | 420 |

|        | 16.7.2 External bus cycles during DMA transfer (two-cycle transfer)     | 420 |

| 16.8   | DMA Channel Priorities                                                  | 421 |

| 16.9   | DMA Transfer Start Factors                                              | 421 |

| 16.1   | 0 DMA Transfer End                                                      | 421 |

|        | 16.10.1 DMA transfer end interrupt                                      | 421 |

|        | 16.10.2 Terminal count output upon DMA transfer end                     | 421 |

| 16.1   | 1 Precautions                                                           | 422 |

|        | 16.11.1 Interrupt factors                                               | 424 |

| CHAPTE | R 17 INTERRUPT/EXCEPTION PROCESSING FUNCTION                            | 425 |

| 17.1   | Features                                                                | 425 |

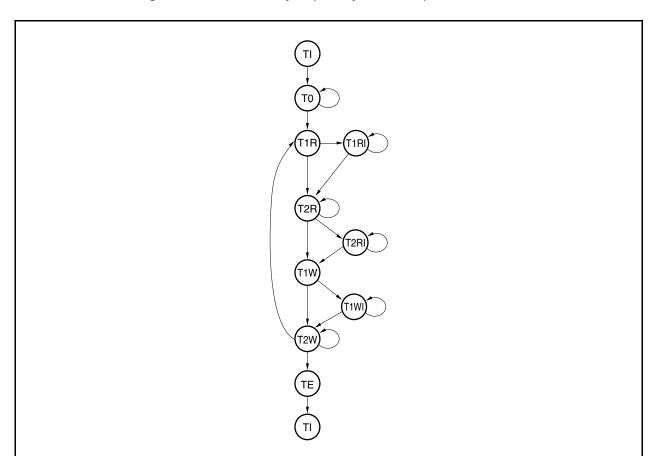

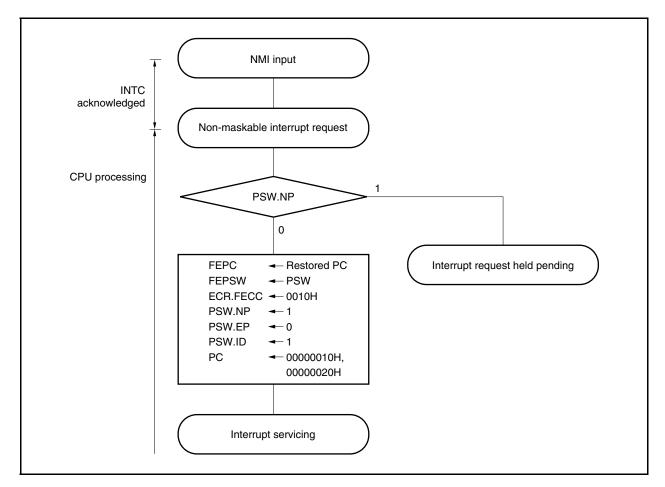

| 17.2   | Non-Maskable Interrupts                                                 | 428 |

|        | 17.2.1 Operation                                                        | 430 |

|        | 17.2.2 Restore                                                          | 431 |

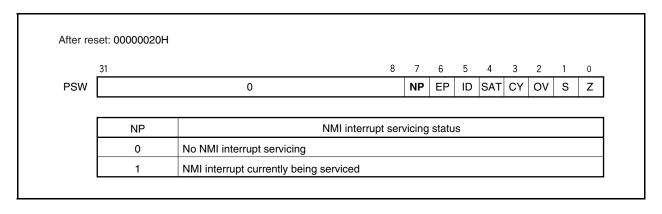

|        | 17.2.3 NP flag                                                          | 432 |

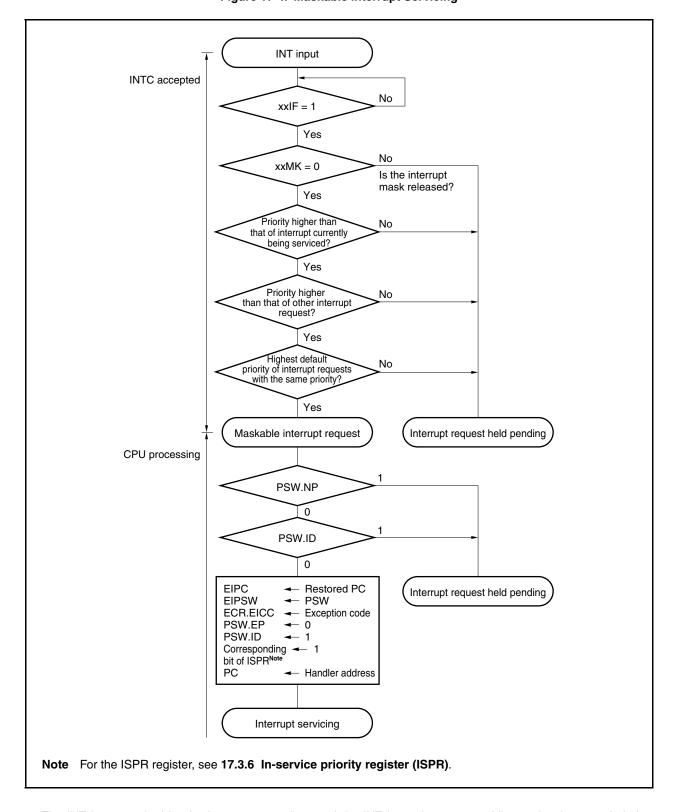

| 17.3   | Maskable Interrupts                                                     | 433 |

|        | 17.3.1 Operation                                                        | 433 |

|        | 17.3.2 Restore                                                          | 435 |

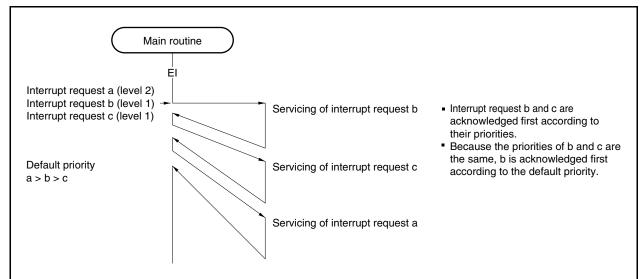

|        | 17.3.3 Priorities of maskable interrupts                                | 436 |

|        | 17.3.4 Interrupt control register (xxICn)                               | 440 |

|        | 17.3.5 Interrupt mask registers 0 to 2 (IMR0 to IMR2)                   | 442 |

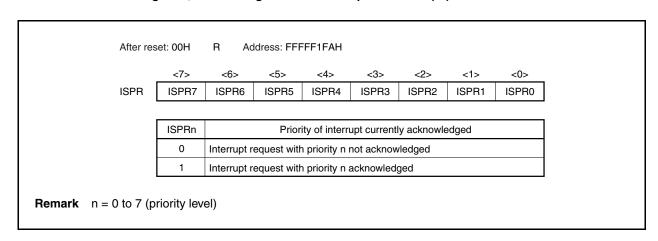

|        | 17.3.6 In-service priority register (ISPR)                              | 443 |

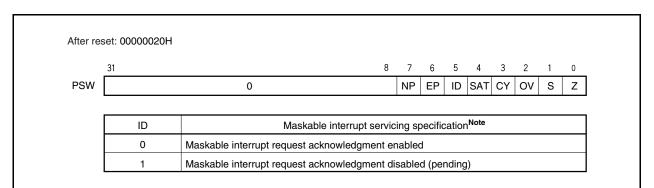

|        | 17.3.7 ID flag                                                          | 443 |

|        | 17.3.8 Watchdog timer mode register (WDTM)                              | 444 |

| 17.4   | Noise Elimination at External Interrupt Request Input Pins              | 445 |

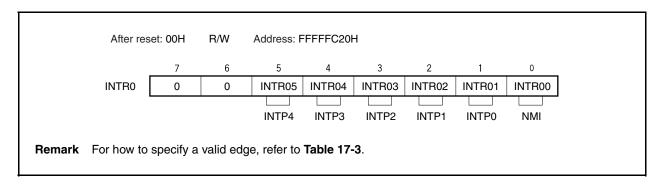

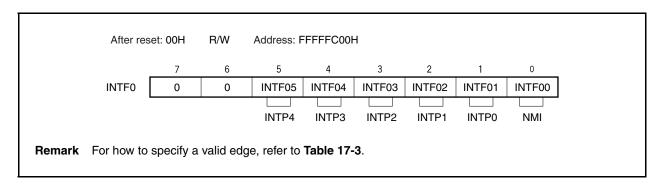

|        | 17.4.1 Edge detection function of external interrupt request input pins | 445 |

| 17.5   | Software Exception                                                      | 448 |

|        | 17.5.1 Operation                                                        | 448 |

|        | 17.5.2 Restore                                                          | 449 |

|        | 17.5.3 EP flag                                                          | 450 |

| 17.6   | Exception Trap                                                          |     |

|        | 17.6.1 Illegal opcode definition                                        | 451 |

|        | 17.6.2 Debug trap                                                       | 453 |

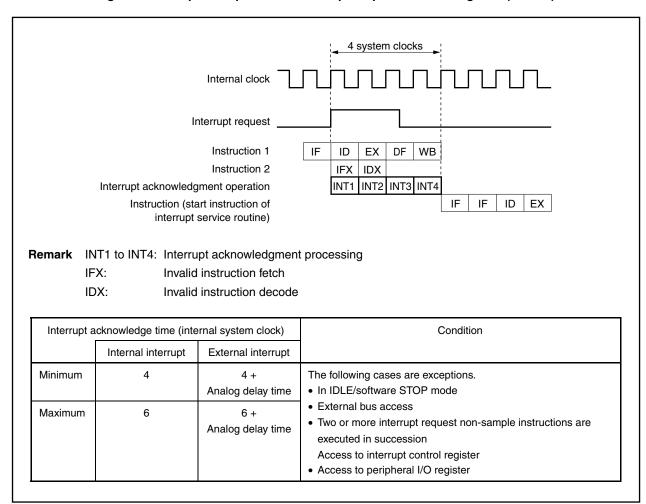

| 17.7   | Interrupt Acknowledge Time of CPU                                       | 455 |

| 17.8   | Periods in Which Interrupts Are Not Acknowledged by CPU                 | 456 |

|        |                                                                         |     |

| CHAPTE | R 18 STANDBY FUNCTION                                                   | 457 |

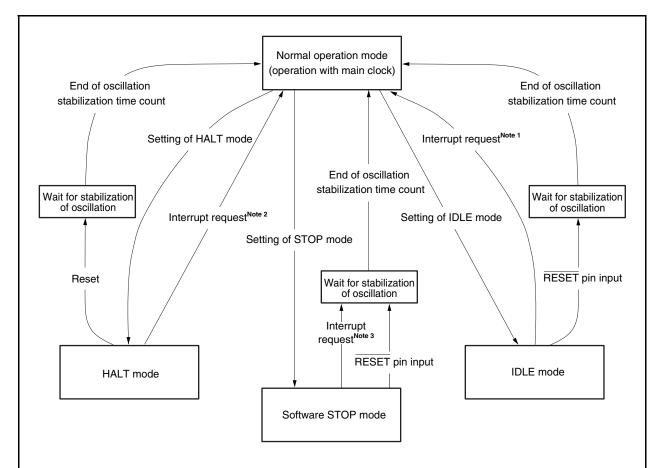

| 18.1   | Overview                                                                | 457 |

| 18.2   | HALT Mode                                                               | 460 |

|        | 18.2.1 Setting and operation status                                     | 460 |

|        | 18.2.2 Releasing HALT mode                                              | 460 |

| 10 2   | IDI F Mode                                                              | 462 |

|     |      | 18.3.1 | Setting and operation status                           | 462 |

|-----|------|--------|--------------------------------------------------------|-----|

|     |      | 18.3.2 | Releasing IDLE mode                                    | 462 |

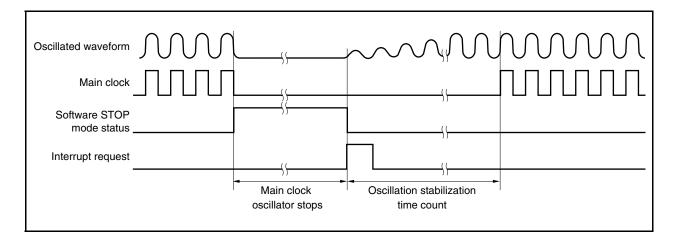

|     | 18.4 | Softwa | are STOP Mode                                          | 464 |

|     |      | 18.4.1 | Setting and operation status                           | 464 |

|     |      | 18.4.2 | Releasing software STOP mode                           | 464 |

|     | 18.5 | Securi | ing Oscillation Stabilization Time                     | 466 |

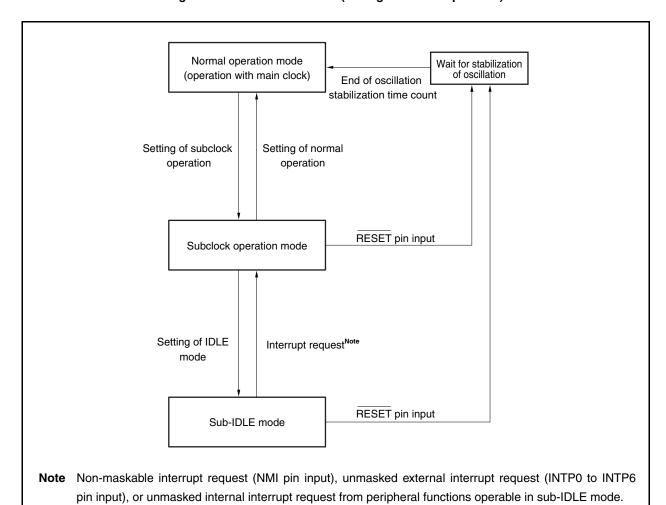

|     | 18.6 | Subclo | ock Operation Mode                                     | 467 |

|     |      | 18.6.1 | Setting and operation status                           | 467 |

|     |      | 18.6.2 | Releasing subclock operation mode                      |     |

|     | 18.7 | Sub-ID | DLE Mode                                               | 469 |

|     |      | 18.7.1 | Setting and operation status                           | 469 |

|     |      | 18.7.2 | Releasing sub-IDLE mode                                |     |

|     | 18.8 | Contro | ol Registers                                           | 471 |

| СНА | PTFF | 2 19 R | RESET FUNCTION                                         | 472 |

|     |      |        |                                                        |     |

|     |      |        | iew                                                    |     |

|     | 19.2 | _      | guration                                               |     |

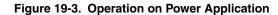

|     | 19.3 | Opera  | tion                                                   | 4/3 |

| СНА | PTEF | R 20 R | OM CORRECTION FUNCTION                                 | 476 |

|     | 20.1 | Overvi | iew                                                    | 476 |

|     |      |        | ol Registers                                           |     |

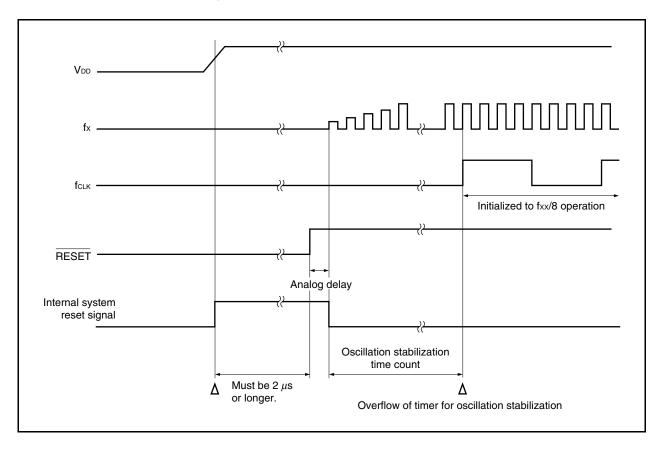

|     | 20.2 | 20.2.1 | Correction address registers 0 to 3 (CORAD0 to CORAD3) |     |

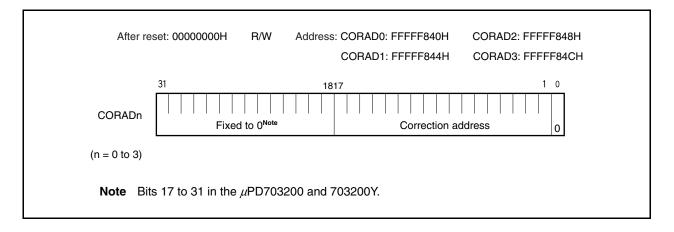

|     |      | 20.2.1 | Correction control register (CORCN)                    |     |

|     | 20.3 |        | Correction Operation and Program Flow                  |     |

|     | 20.0 | TIOW C |                                                        | 470 |

| СНА | PTEF | R 21 F | LASH MEMORY                                            | 480 |

|     | 21.1 | Featur | res                                                    | 481 |

|     |      | 21.1.1 |                                                        |     |

|     | 21.2 | Functi | onal Overview                                          |     |

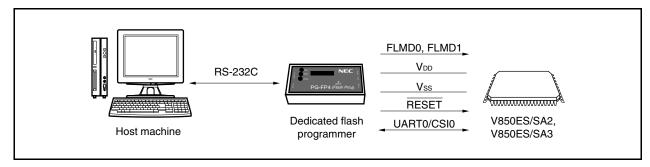

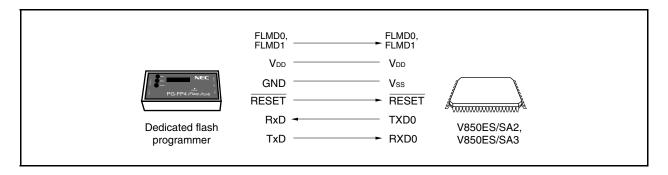

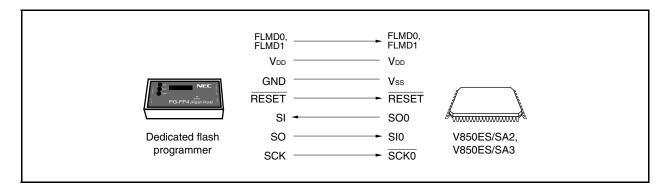

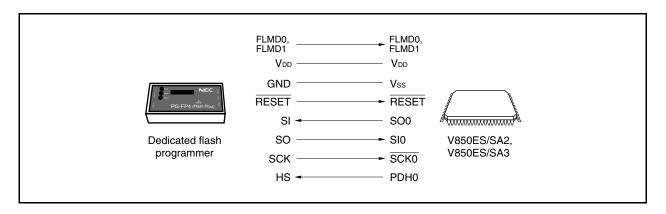

|     | 21.3 |        | amming Environment                                     |     |

|     | 21.4 | •      | nunication Mode                                        |     |

|     |      |        | onnection                                              |     |

|     |      | 21.5.1 | FLMD0 pin                                              | 490 |

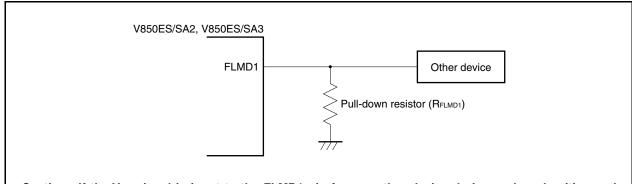

|     |      | 21.5.2 | FLMD1 pin                                              | 491 |

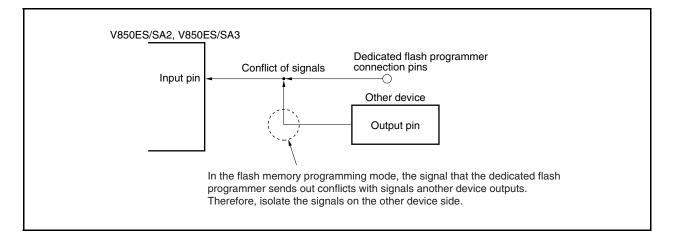

|     |      | 21.5.3 | Serial interface pin                                   | 491 |

|     |      | 21.5.4 | RESET pin                                              | 494 |

|     |      | 21.5.5 | Port pins (including NMI)                              | 494 |

|     |      | 21.5.6 | Other signal pins                                      | 494 |

|     |      | 21.5.7 | Power supply                                           | 494 |

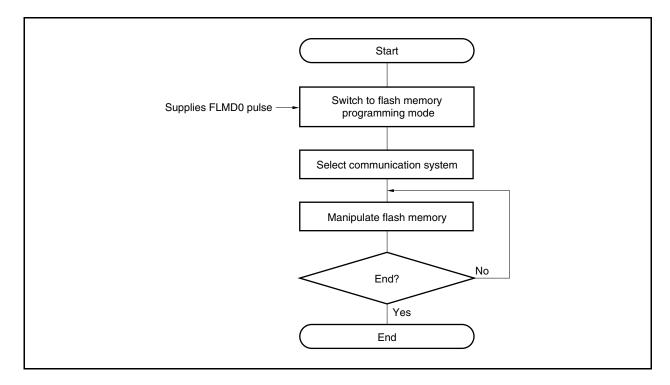

|     | 21.6 | Progra | amming Method                                          | 495 |

|     |      | 21.6.1 | Flash memory control                                   | 495 |

|     |      | 21.6.2 | Flash memory programming mode                          | 496 |

|     |      | 2163   | Selection of communication mode                        | 497 |

|   | 21.6.4 Communication command                | 497 |

|---|---------------------------------------------|-----|

| * | 21.7 Rewriting by Self Programming          | 499 |

|   | 21.7.1 Overview                             | 499 |

|   | 21.7.2 Features                             | 500 |

|   | CHAPTER 22 ELECTRICAL SPECIFICATIONS        | 503 |

|   | CHAPTER 23 PACKAGE DRAWINGS                 | 532 |

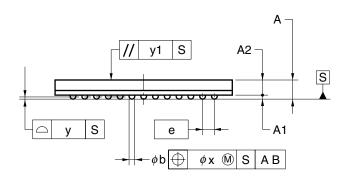

| * | CHAPTER 24 RECOMMENDED SOLDERING CONDITIONS | 534 |

| * | APPENDIX A REGISTER INDEX                   | 536 |

| * | APPENDIX B INSTRUCTION SET LIST             | 543 |

|   | B.1 Conventions                             | 543 |

|   | B.2 Instruction Set (In Alphabetical Order) |     |

| * | APPENDIX C REVISION HISTORY                 | 553 |

|   | C 1 Major Revisions in This Edition         | 553 |

#### **CHAPTER 1 INTRODUCTION**

The V850ES/SA2 and V850ES/SA3 are low-power models of the NEC Electronics V850 Series of single-chip microcontrollers for real-time control.

#### 1.1 Overview

The V850ES/SA2 and V850ES/SA3 are 32-bit single-chip microcontrollers that employ the V850ES CPU core and integrate peripheral functions such as ROM/RAM, timers/counters, serial interfaces, an A/D converter, a D/A converter, and a DMA controller.

These products are part of the V850/SA1 line of low-power microcontrollers, but employ the V850ES as the CPU and have additional peripheral functions such as a D/A converter and ROM correction. They also realized lower voltage and power consumption.

The V850ES/SA2 and V850ES/SA3 feature instructions ideal for digital servo control applications, such as multiplication instructions using a hardware multiplier, saturated operation instructions, and bit manipulation instructions, as well as basic instructions with a short real-time response speed and a 1-clock pitch. These microcontrollers can be used in real-time control systems requiring low power consumption, such as DVC and portable audio systems, with a high cost effectiveness.

Table 1-1 shows the products in the V850ES/SA2 and V850ES/SA3 lineup.

Provided

μPD70F3204Y

**Product Name** I<sup>2</sup>C ROM **RAM Size** Package Commercial Name Part Number Size Type  $\mu$ PD703200 100-pin TQFP ( $14 \times 14$ ) V850ES/SA2 None Mask ROM 128 KB 8 KB μPD703200Y Provided μPD703201 256 KB 16 KB None μPD703201Y Provided μPD70F3201 None Flash memory μPD70F3201Y Provided V850ES/SA3 μPD703204 121-pin FBGA (12 × 12) None Mask ROM 256 KB 16 KB μPD703204Y Provided μPD70F3204 None Flash memory

Table 1-1. V850ES/SA2 and V850ES/SA3 Product Lineup

#### 1.2 Features

O Number of instructions 83 Minimum instruction execution time 50 ns: Main clock = 20 MHz (µPD703200, 703201, 703204, 70F3201, 70F3204) 59 ns: Main clock = 17 MHz (μPD703200Y, 703201Y, 703204Y, 70F3201Y, 70F3204Y)  $30.5 \ \mu s$ : Subclock =  $32.768 \ kHz$ O General-purpose registers 32 bits × 32 registers Instruction set Signed multiplication (16  $\times$  16  $\rightarrow$  32): 1 to 2 clocks Signed multiplication (32  $\times$  32  $\rightarrow$  64): 1 to 5 clocks Saturated operation (with overflow/underflow detection function) 32-bit shift instruction: 1 clock Bit manipulation instruction Load/store instruction with long/short format O Memory space 64 MB linear address space (for program/data) External expansion: Up to 4 MB for V850ES/SA2 and 16 MB for V850ES/SA3 (of which 1 MB is used as internal ROM/RAM space) Memory block division function: 2, 2, 4, 8 MB (total: 4 blocks) Programmable wait function Idle state insertion function O External bus interface Multiplexed bus/separate bus output selectable 8/16-bit data bus sizing function 4-space chip select function Wait functions • Programmable wait function • External wait function Idle state function Bus hold function O Internal memory RAM: 16 KB (μPD703201, 703201Y, 70F3201, 70F3201Y, 703204, 703204Y, 70F3204, 70F3204Y) 8 KB (µPD703200, 703200Y) Mask ROM: 256 KB (µPD703201, 703201Y, 703204, 703204Y) 128 KB (μPD703200, 703200Y)

Flash memory: 256 KB (µPD70F3201, 70F3201Y, 70F3204, 70F3204Y)

#### **CHAPTER 1 INTRODUCTION**

| ○ Interrupts/exceptions           | External interrupts: 8 sources Internal interrupts: 30 sources (μPD703200, 703201, 70F3201) 31 sources (μPD703200Y, 703201Y, 70F3201Y) 31 sources (μPD703204, 70F3204) |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                   | 32 sources (μPD703204Y, 70F3204Y) Software exception: 32 sources                                                                                                       |

|                                   | Exception trap: 1 source                                                                                                                                               |

| ○ I/O lines                       | Total: 82 (input ports: 14, I/O ports: 68) (V850ES/SA2)                                                                                                                |

|                                   | 102 (input ports: 18, I/O ports: 84) (V850ES/SA3)                                                                                                                      |

| ○ Timer/counter                   | 16-bit timer/event counter: 2 ch (PWM output)                                                                                                                          |

|                                   | 8-bit timer/event counter: 4 ch (connectable in cascade)                                                                                                               |

| ○ Real-time counter (for watch)   | Subclock/main clock operation: 1 ch                                                                                                                                    |

|                                   | Dedicated on-chip hardware counter for weeks, days, hours, minutes, and seconds                                                                                        |

|                                   | Up to 4,095 weeks can be counted                                                                                                                                       |

| O Watchdog timer:                 | 1 ch                                                                                                                                                                   |

| ○ Serial interface                | Asynchronous serial interface (UART)                                                                                                                                   |

|                                   | Clocked serial interface (CSI)                                                                                                                                         |

|                                   | I <sup>2</sup> C bus interface (I <sup>2</sup> C)                                                                                                                      |

|                                   | (μPD703200Y, 703201Y, 703204Y, 70F3201Y, and 70F3204Y only)                                                                                                            |

|                                   | CSI/UART: 1 ch                                                                                                                                                         |

|                                   | UART: 1 ch                                                                                                                                                             |

|                                   | CSI/I <sup>2</sup> C: 1 ch                                                                                                                                             |

|                                   | CSI: 2 ch (V850ES/SA2), 3 ch (V850ES/SA3)                                                                                                                              |

| <ul><li>○ A/D converter</li></ul> | 10-bit resolution: 12 ch (V850ES/SA2)                                                                                                                                  |

|                                   | 16 ch (V850ES/SA3)                                                                                                                                                     |

| ○ D/A converter                   | 8-bit resolution: 2 ch                                                                                                                                                 |

| O DMA controller:                 | 4 ch (transfer object: Internal memory, on-chip peripheral I/O, and external memory)                                                                                   |

| ROM correction:                   | 4 places specifiable                                                                                                                                                   |

| ○ Clock generator                 | Main clock/subclock operation                                                                                                                                          |

|                                   | CPU clock: 7 steps (fx, fx/2, fx/4, fx/8, fx/16, fx/32, fxT)                                                                                                           |

| O Power save function             | HALT/IDLE/STOP mode                                                                                                                                                    |

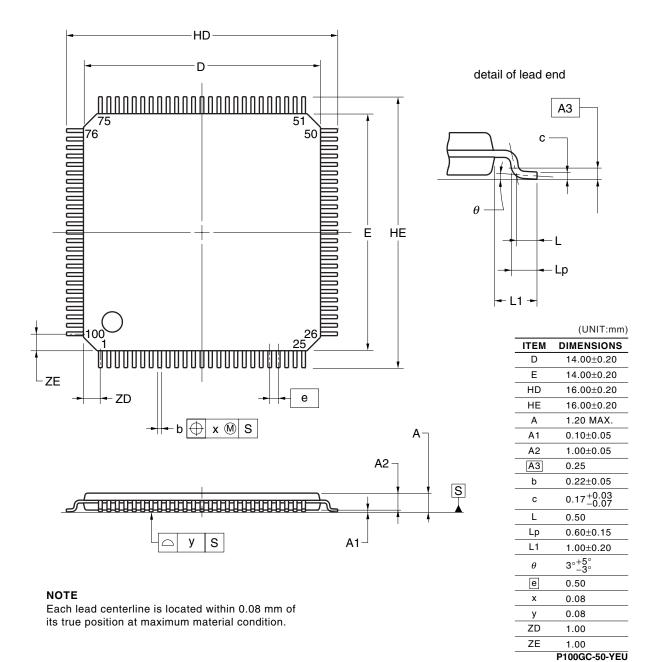

| ○ Package                         | 100-pin plastic TQFP (fine pitch) (14 $\times$ 14) (V850ES/SA2)                                                                                                        |

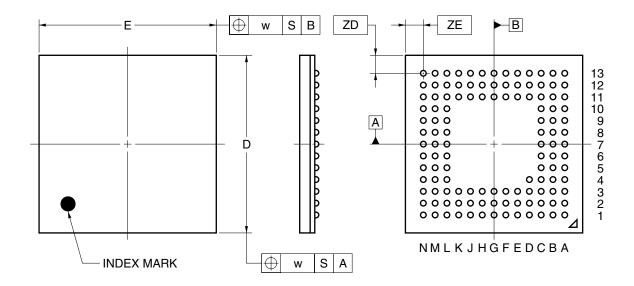

|                                   | 121-pin plastic FBGA (12 × 12) (V850ES/SA3)                                                                                                                            |

# 1.3 Application Fields

Mobile devices requiring low power consumption

**Example** DVC and portable audio systems

# 1.4 Ordering Information

#### 1.4.1 V850ES/SA2

|   | Part Number                 | Package                                            | Internal ROM          |

|---|-----------------------------|----------------------------------------------------|-----------------------|

| * | $\mu$ PD703200GC-xxx-YEU-A  | 100-pin plastic TQFP (fine pitch) (14 $\times$ 14) | Mask ROM (128 KB)     |

| * | $\mu$ PD703200YGC-×××-YEU-A | 100-pin plastic TQFP (fine pitch) (14 $\times$ 14) | Mask ROM (128 KB)     |

| * | $\mu$ PD703201GC-xxx-YEU-A  | 100-pin plastic TQFP (fine pitch) (14 $\times$ 14) | Mask ROM (256 KB)     |

| * | $\mu$ PD703201YGC-××-YEU-A  | 100-pin plastic TQFP (fine pitch) (14 $\times$ 14) | Mask ROM (256 KB)     |

| * | $\mu$ PD70F3201GC-YEU-A     | 100-pin plastic TQFP (fine pitch) (14 $\times$ 14) | Flash memory (256 KB) |

| * | $\mu$ PD70F3201YGC-YEU-A    | 100-pin plastic TQFP (fine pitch) (14 $\times$ 14) | Flash memory (256 KB) |

- **Remarks 1.** ××× indicates ROM code suffix.

- 2. No ROMless model is available.

- **3.** Products with -A at the end of the part number are lead-free products.

#### 1.4.2 V850ES/SA3

|   | Part Number                                 | Package                               | Internal ROM          |

|---|---------------------------------------------|---------------------------------------|-----------------------|

| * | $\mu$ PD703204F1- $\times$ $\times$ -EA6-A  | 121-pin plastic FBGA (12 $\times$ 12) | Mask ROM (256 KB)     |

| * | $\mu$ PD703204YF1- $\times$ $\times$ -EA6-A | 121-pin plastic FBGA (12 $\times$ 12) | Mask ROM (256 KB)     |

| * | μPD70F3204F1-EA6-A                          | 121-pin plastic FBGA (12 $\times$ 12) | Flash memory (256 KB) |

| * | μPD70F3204YF1-EA6-A                         | 121-pin plastic FBGA (12 $\times$ 12) | Flash memory (256 KB) |

- Remarks 1. xxx indicates ROM code suffix.

- 2. No ROMIess model is available.

- 3. Products with -A at the end of the part number are lead-free products.

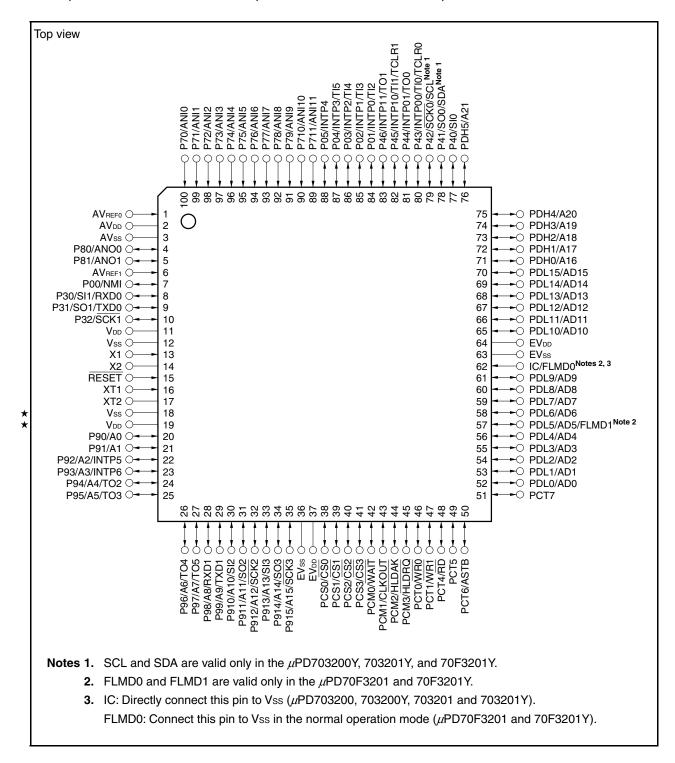

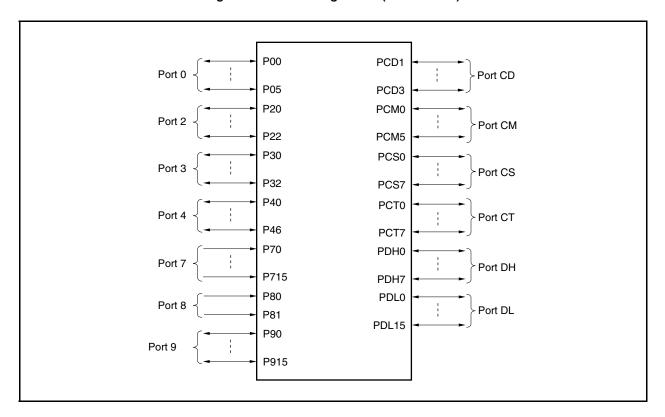

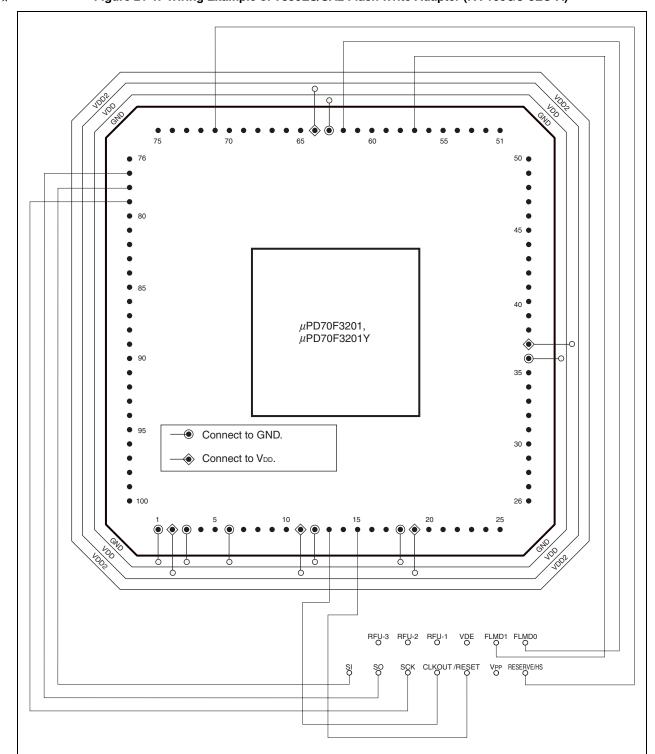

#### 1.5 Pin Configuration

#### ○ V850ES/SA2

100-pin plastic TQFP (fine pitch) (14  $\times$  14)

- μPD703200GC-×××-YEU-A

- μPD703201GC-×××-YEU-A

- μPD70F3201GC-YEU-A

- μPD703200YGC-xxx-YEU-A

- μPD703201YGC-××-YEU-A

- μPD70F3201YGC-YEU-A

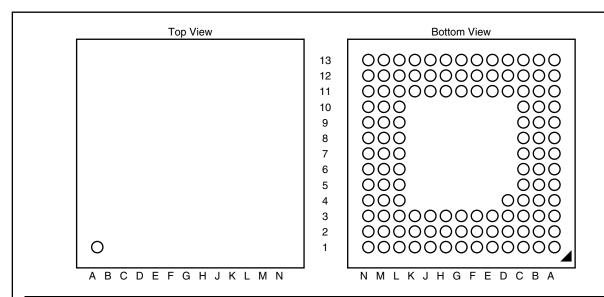

#### ○ V850ES/SA3

121-pin plastic FGBA ( $12 \times 12$ )

μPD703204F1-xxx-EA6-A μPD70F3204F1-EA6-A μPD703204YF1-xxx-EA6-A μPD70F3204YF1-EA6-A

| Pin No. | Name                        | Pin No. | Name                         | Pin No. | Name               |

|---------|-----------------------------|---------|------------------------------|---------|--------------------|

| A1      | P70/ANI0                    | B8      | PCD3                         | D2      | AV <sub>REF1</sub> |

| A2      | P71/ANI1                    | В9      | P02/INTP1/TI3                | D3      | P00/NMI            |

| А3      | P73/ANI3                    | B10     | P46/INTP11/TO1               | D11     | PDH0/A16           |

| A4      | P713/ANI13                  | B11     | P42/SCK0/SCL <sup>Note</sup> | D12     | PDH2/A18           |

| A5      | P76/ANI6                    | B12     | P40/SI0                      | D13     | PDH1/A17           |

| A6      | P78/ANI8                    | B13     | PDH4/A20                     | E1      | P30/SI1/RXD0       |

| A7      | P711/ANI11                  | C1      | P80/ANO0                     | E2      | P31/SO1/TXD0       |

| A8      | P04/INTP3/TI5               | C2      | AVss                         | E3      | P32/SCK1           |

| A9      | PCD2                        | C3      | P74/ANI4                     | E11     | PDL14/AD14         |

| A10     | P45/INTP10/TI1/TCLR1        | C4      | P714/ANI14                   | E12     | PDH6/A22           |

| A11     | P43/INTP00/TI0/TCLR0        | C5      | P715/ANI15                   | E13     | PDL15/AD15         |

| A12     | P41/SO0/SDA <sup>Note</sup> | C6      | P79/ANI9                     | F1      | Vss                |

| A13     | PDH5/A21                    | C7      | P05/INTP4                    | F2      | X1                 |

| B1      | AV <sub>DD</sub>            | C8      | P03/INTP2/TI4                | F3      | V <sub>DD</sub>    |

| B2      | AV <sub>REF0</sub>          | C9      | PCD1                         | F11     | PDL11/AD11         |

| В3      | P72/ANI2                    | C10     | P01/INTP0/TI2                | F12     | PDL13/AD13         |

| B4      | P712/ANI12                  | C11     | P44/INTP01/TO0               | F13     | PDL12/AD12         |

| B5      | P75/ANI5                    | C12     | PDH3/A19                     | G1      | RESET              |

| B6      | P77/ANI7                    | C13     | PDH7/A23                     | G2      | XT1                |

| B7      | P710/ANI10                  | D1      | P81/ANO1                     | G3      | X2                 |

**Note** SCL and SDA are valid only in the  $\mu$ PD703204Y and 70F3204Y.

Remark Leave the D4 pin open.

(2/2)

| Pin No. | Name                             | Pin No. | Name             | Pin No. | Name          |

|---------|----------------------------------|---------|------------------|---------|---------------|

| G11     | EVss                             | K13     | PDL3/AD3         | M7      | PCS4          |

| G12     | PDL10/AD10                       | L1      | P93/A3/INTP6     | M8      | PCM0/WAIT     |

| G13     | EV <sub>DD</sub>                 | L2      | P94/A4/TO2       | M9      | PCM2/HLDAK    |

| H1      | Vss                              | L3      | P911/A11/SO2     | M10     | PCT3          |

| H2      | V <sub>DD</sub>                  | L4      | P914/A14/SO3     | M11     | PCT4/RD       |

| НЗ      | XT2                              | L5      | P915/A15/SCK3    | M12     | PCT7          |

| H11     | PDL8/AD8                         | L6      | EV <sub>DD</sub> | M13     | PDL0/AD0      |

| H12     | IC/FLMD0 <sup>Notes 1, 2</sup>   | L7      | PCS0/CS0         | N1      | P96/A6/TO4    |

| H13     | PDL9/AD9                         | L8      | PCS2/CS2         | N2      | P98/A8/RXD1   |

| J1      | P20/SI4                          | L9      | PCM4             | N3      | P910/A10/SI2  |

| J2      | P91/A1                           | L10     | PCT2             | N4      | P912/A12/SCK2 |

| J3      | P90/A0                           | L11     | PCT0/WR0         | N5      | PCS7          |

| J11     | PDL5/AD5/FLMD1 <sup>Note 1</sup> | L12     | PDL1/AD1         | N6      | PCS6          |

| J12     | PDL7/AD7                         | L13     | PDL2/AD2         | N7      | PCS1/CS1      |

| J13     | PDL6/AD6                         | M1      | P95/A5/TO3       | N8      | PCS3/CS3      |

| K1      | P22/SCK4                         | M2      | P97/A7/TO5       | N9      | PCM5          |

| K2      | P92/A2/INTP5                     | М3      | P99/A9/TXD1      | N10     | PCM3/HLDRQ    |

| K3      | P21/SO4                          | M4      | P913/A13/SI3     | N11     | PCT1/WR1      |

| K11     | PCM1/CLKOUT                      | M5      | EVss             | N12     | PCT5          |

| K12     | PDL4/AD4                         | M6      | PCS5             | N13     | PCT6/ASTB     |

**Notes 1.** FLMD0 and FLMD1 are valid only in the  $\mu$ PD70F3204 and 70F3204Y.

**2.** IC: Directly connect this pin to Vss ( $\mu$ PD703204 and 703204Y). FLMD0: Connect this pin to Vss in the normal operation mode ( $\mu$ PD70F3204 and 70F3204Y).

#### Pin Identification

A0 to A23: Address bus P90 to P915: Port 9 AD0 to AD15: Address/data bus PCD1 to PCD3: Port CD ANI0 to ANI15: Analog input PCM0 to PCM5: Port CM ANO0, ANO1: Analog output PCS0 to PCS7: Port CS ASTB: Address strobe PCT0 to PCT7: Port CT AVDD: Analog VDD PDH0 to PDH7: Port DH AVREFO, AVREF1: PDL0 to PDL15: Port DL Analog reference voltage AVss: Analog Vss RD: Read strobe RESET: CLKOUT: Reset Clock output  $\overline{\text{CS0}}$  to  $\overline{\text{CS3}}$ : Chip select RXD0, RXD1: Receive data SCK0 to SCK4: EV<sub>DD</sub>: Power supply for port Serial clock EVss: Ground for port SCL: Serial clock FLMD0, FLMD1: Flash programming mode SDA: Serial data HLDAK: SI0 to SI4: Hold acknowledge Serial input HLDRQ: SO0 to SO4: Hold request Serial output IC: Internally connected TCLR0, TCLR1: Timer clear input INTP0 to INTP6: External interrupt input TI0 to TI5: Timer input INTP00, INTP01: TO0 to TO5: Interrupt request to timer Timer output INTP10, INTP11 TXD0, TXD1: Transmit data NMI: Non-maskable interrupt request V<sub>DD</sub>: Power supply P00 to P05: Port 0 Vss: Ground WAIT: Wait P20 to P22: Port 2 P30 to P32: Port 3 WR0: Lower byte write strobe P40 to P46: WR1: Port 4 Higher byte write strobe P70 to P715: X1, X2: Port 7 Crystal for main clock XT1, XT2: P80, P81: Port 8 Crystal for subclock

#### 1.6 Function Block Configuration

#### 1.6.1 Internal block diagram

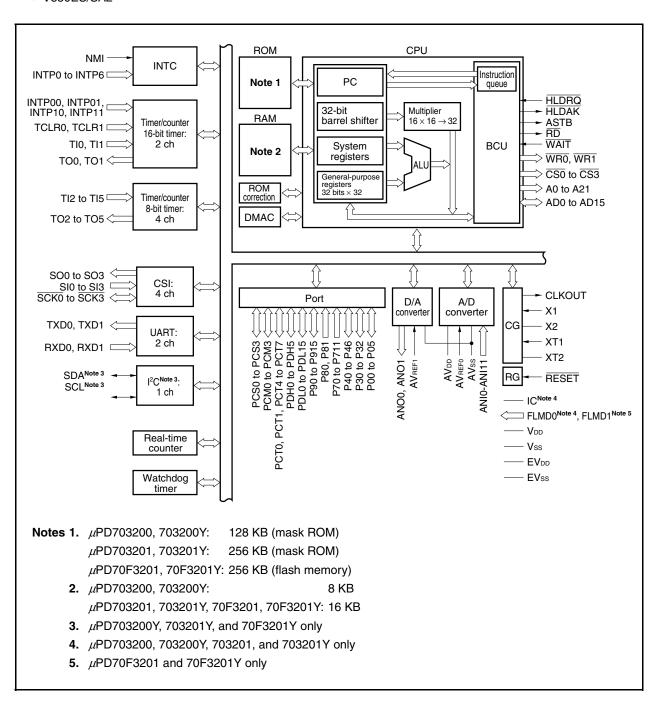

V850ES/SA2

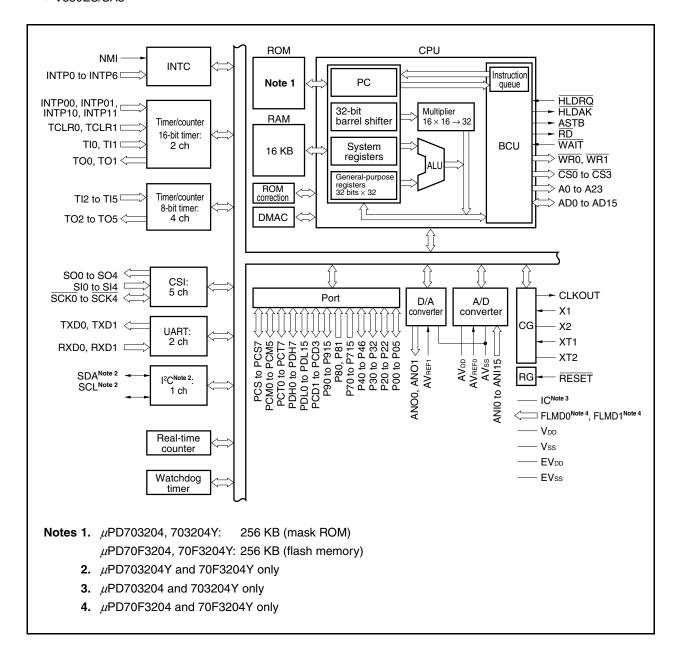

#### • V850ES/SA3

#### 1.6.2 Internal units

# (1) CPU

The CPU can execute almost all instruction processing, such as address calculation, arithmetic logic operations, and data transfer, with 1 clock, using a 5-stage pipeline.

The CPU has dedicated hardware units such as a multiplier (16 bits  $\times$  16 bits  $\rightarrow$  32 bits) and a barrel shifter (32 bits) to speed up complicated instruction processing.

#### (2) Bus control unit (BCU)

The BCU starts the required external bus cycles in accordance with the physical address obtained by the CPU. If the CPU does not request the start of a bus cycle when an instruction is fetched from the external memory area, the BCU generates a prefetch address and prefetches an instruction code. The prefetched instruction code is loaded to the internal instruction queue.

#### (3) ROM

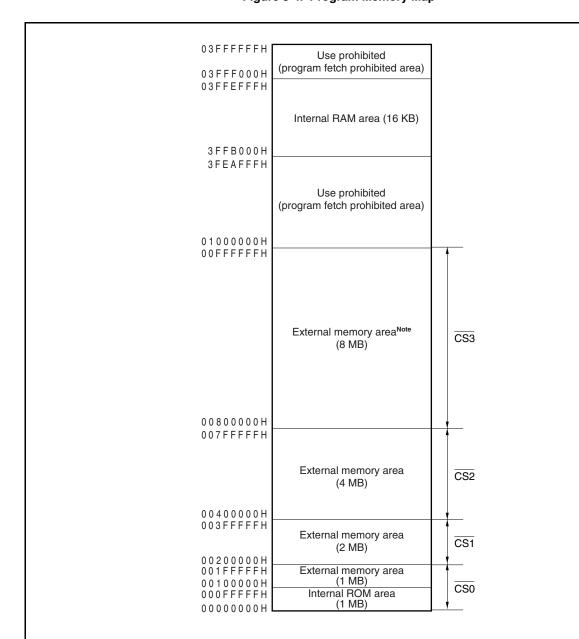

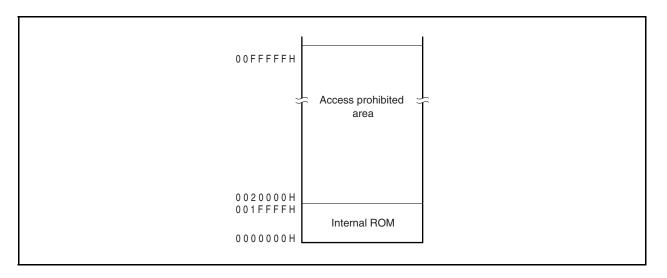

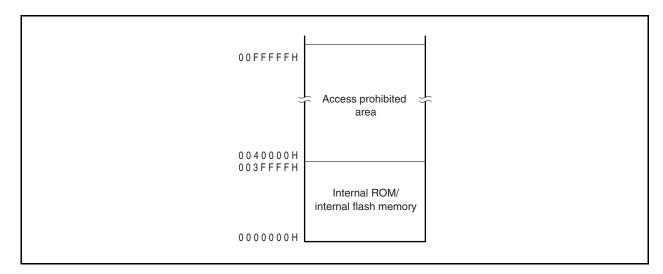

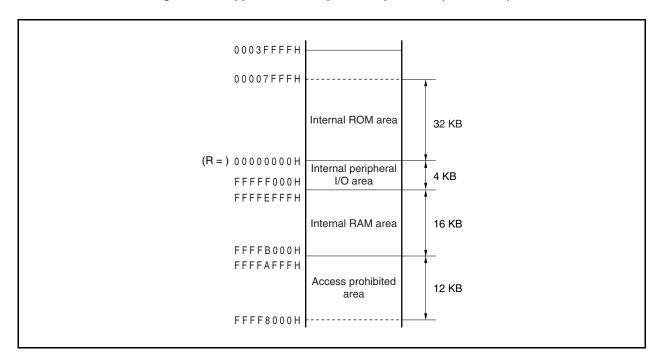

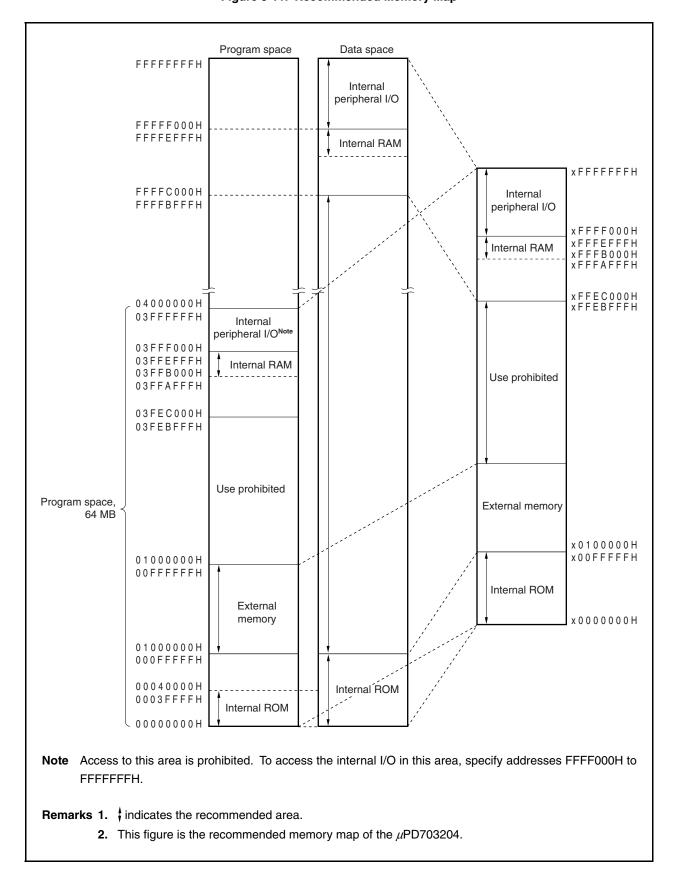

This is a 256 KB or 128 KB mask ROM or flash memory mapped to addresses 0000000H to 003FFFFH or 0000000H to 001FFFFH. The CPU can access the ROM with 1 clock when an instruction is fetched.

#### (4) RAM

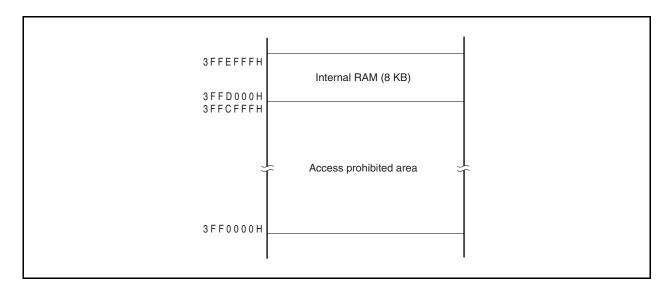

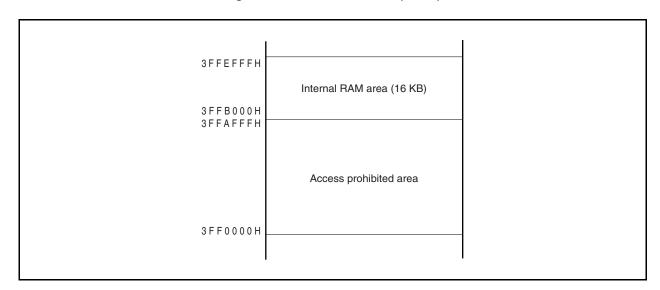

This is a 16 KB or 8 KB RAM mapped to addresses 3FFB000H to 3FFEFFFH or 3FFD000H to 3FFEFFFH. It can be accessed by the CPU with 1 clock when data is accessed.

#### (5) Interrupt controller (INTC)

The INTC processes hardware interrupt requests (NMI, INTP0 to INTP6) from the internal peripheral hardware and external sources. Eight levels of priority can be specified for these interrupt requests. Multiple interrupts can also be processed.

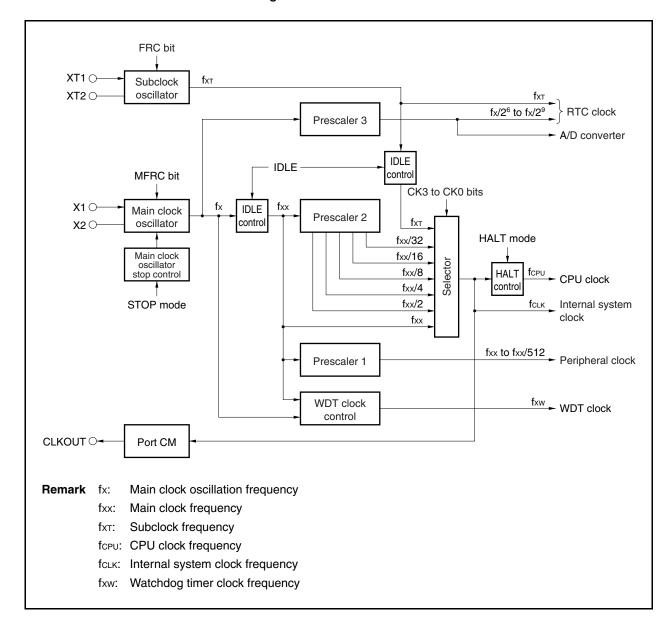

#### (6) Clock generator (CG)

Two oscillators, one for the main clock (fx) and the other for the subclock (fx $\tau$ ), are provided. Seven types of clocks (fx, fx/2, fx/4, fx/8, fx/16, fx/32, and fx $\tau$ ) can be generated, of which one is supplied to the CPU as the operation clock (fcPU). The subclock can be selected only as the operation clock for the real-time counter.

#### (7) Timer/counter

A two-channel 16-bit timer/event counter and four-channel 8-bit timer/event counter are available, enabling pulse interval and frequency measurement and programmable pulse output.

Two 8-bit timer/event counter channels can be connected in cascade and used as a 16-bit timer.

#### (8) Real-time counter (for watch)

This counter counts the reference time (1 second) for the watch count from the subclock (32.768 kHz) or main clock. It can also be used as an interval timer that operates with the main clock. Dedicated hardware counters for counting weeks, days, hours, minutes, and seconds, are provided, and up to 4095 weeks can be counted.

#### (9) Watchdog timer

A watchdog timer that detects program hang-up and system errors is provided.

This watchdog timer can also be used as an interval timer.

When used as a watchdog timer, a non-maskable interrupt request (INTWDT) is generated if the watchdog timer overflows. When used as an interval timer, a maskable interrupt request is generated when the timer overflows.

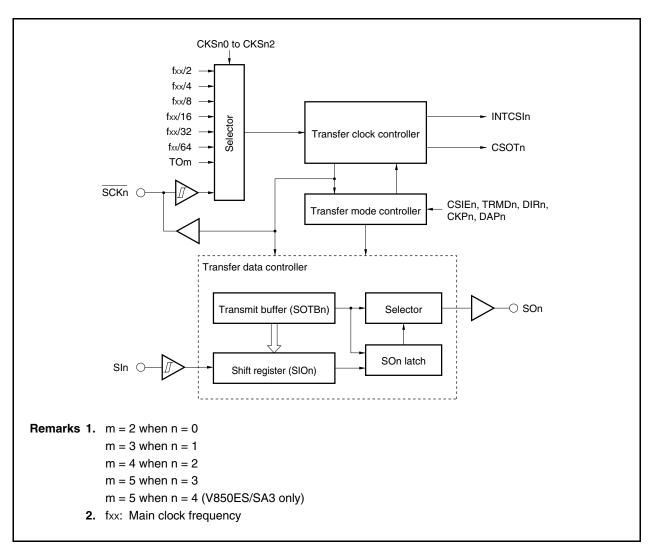

#### (10) Serial interface (SIO)

The V850ES/SA2 and V850ES/SA3 have asynchronous serial interfaces (UART0 and UART1), clocked serial interfaces (V850ES/SA2: CSI0 to CSI3, V850ES/SA3: CSI0 to CSI4), and an I<sup>2</sup>C bus interface (I<sup>2</sup>C) as the serial interfaces. The V850ES/SA2 can use up to four channels, and the V850ES/SA3 can use up to five channels at the same time. Of these channels, one can be switched between UART and CSI, and another can be switched between CSI and I<sup>2</sup>C.

UART0 and UART1 transfer data using the TXD0, TXD1, RXD0, and RXD1 pins.

CSI0 to CSI3 transfer data using the SO0 to SO3, SI0 to SI3, and SCK0 to SCK3 pins.

CSI4 transfers data using the SO4, SI4, and SCK4 pins (V850ES/SA3 only).

I<sup>2</sup>C transfers data using the SDA and SCL pins.

$I^2C$  is provided only in the  $\mu$ PD703200Y, 703201Y, 703204Y, 70F3201Y, and 70F3204Y.

UART includes a dedicated baud rate generator.

#### (11) A/D converter

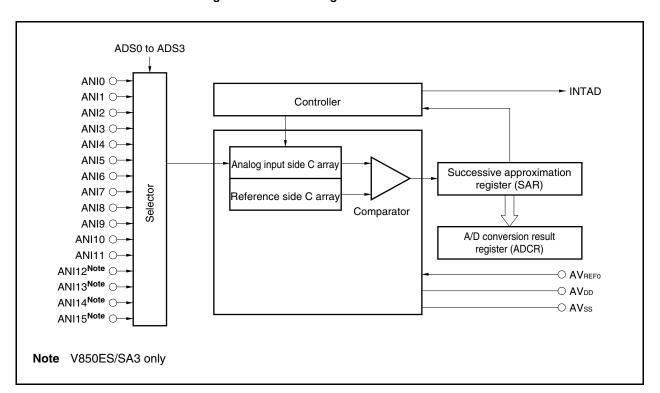

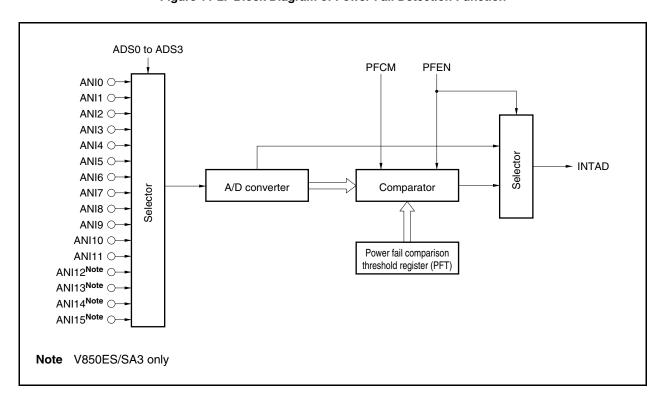

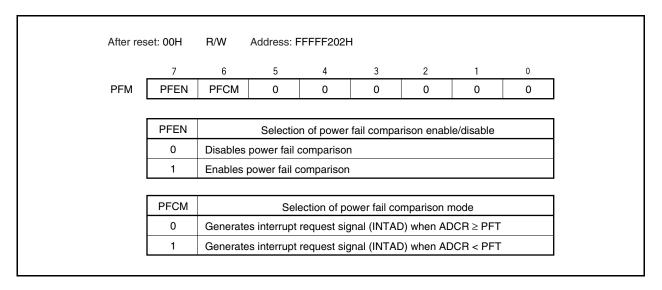

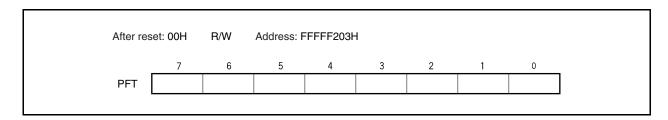

The V850ES/SA2 and V850ES/SA3 have a high-speed high-resolution, 10-bit A/D converter with 12 and 16 analog input pins, respectively. The A/D converter in both products is a successive approximation type.

#### (12) D/A converter

A two-channel 8-bit resolution R-string D/A converter is provided.

#### (13) DMA controller

A DMA controller with four channels is provided. This DMA controller transfers data between the internal RAM, on-chip peripheral I/O, and external memory, in response to interrupt requests from the on-chip peripheral I/O.

#### (14) ROM correction

This is a function to replace part of the program in the mask ROM with program in the internal RAM for execution. The program can be corrected at up to four places.

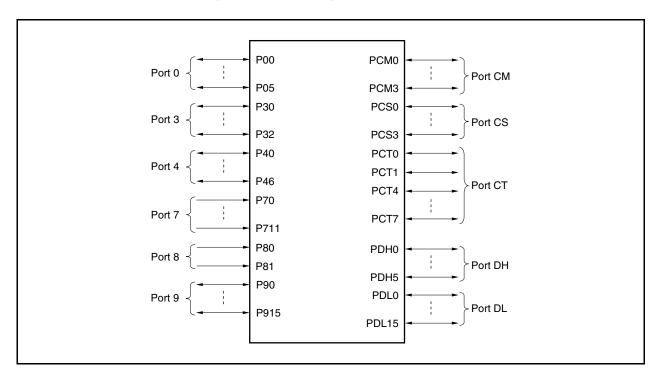

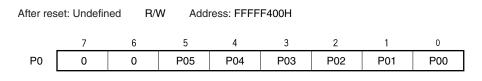

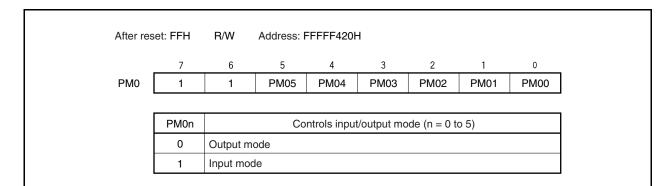

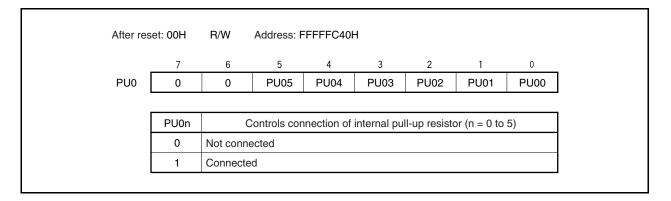

# (15) Ports

Some port pins have a control function as well as a general-purpose port function, as shown below.

| Port                | I/O                                                    | Port Function        | Control Function                                                         |

|---------------------|--------------------------------------------------------|----------------------|--------------------------------------------------------------------------|

| P0                  | 6-bit I/O                                              | General-purpose port | NMI, external interrupt, timer input                                     |

| P2 <sup>Note</sup>  | 3-bit I/O                                              |                      | Serial interface                                                         |

| P3                  | 3-bit I/O                                              |                      | Serial interface                                                         |

| P4                  | 7-bit I/O                                              |                      | Serial interface, timer I/O, timer trigger                               |

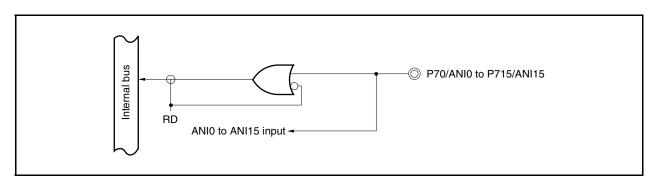

| P7                  | 12-bit input (V850ES/SA2)<br>16-bit input (V850ES/SA3) |                      | A/D converter analog input                                               |

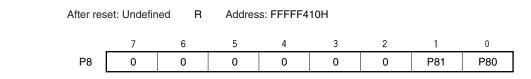

| P8                  | 2-bit input                                            |                      | D/A converter analog output                                              |

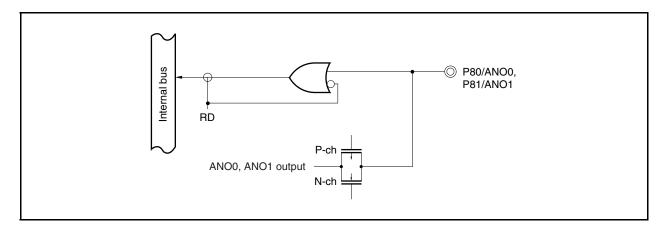

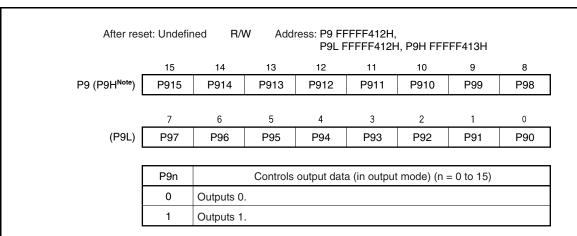

| P9                  | 16-bit I/O                                             |                      | External address bus, serial interface, timer output, external interrupt |

| PCD <sup>Note</sup> | 3-bit I/O                                              |                      | -                                                                        |

| PCM                 | 4-bit I/O (V850ES/SA2)<br>6-bit I/O (V850ES/SA3)       | _                    | External bus interface                                                   |

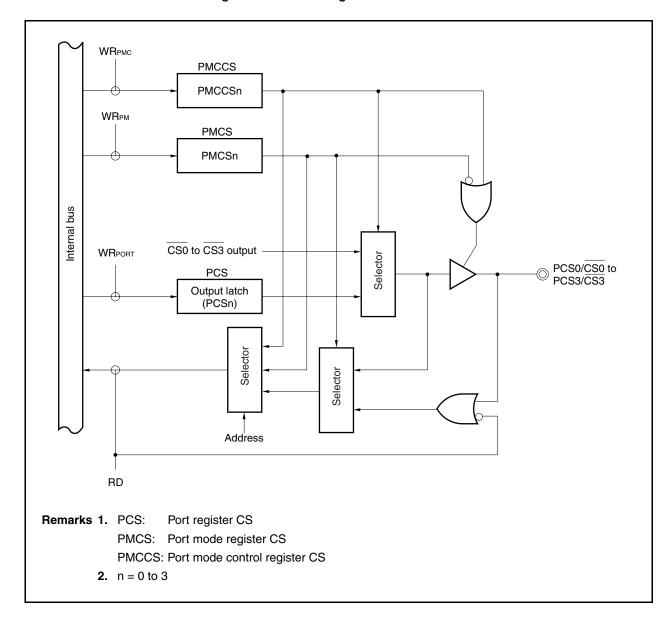

| PCS                 | 4-bit I/O (V850ES/SA2)<br>8-bit I/O (V850ES/SA3)       | _                    | Chip select output                                                       |

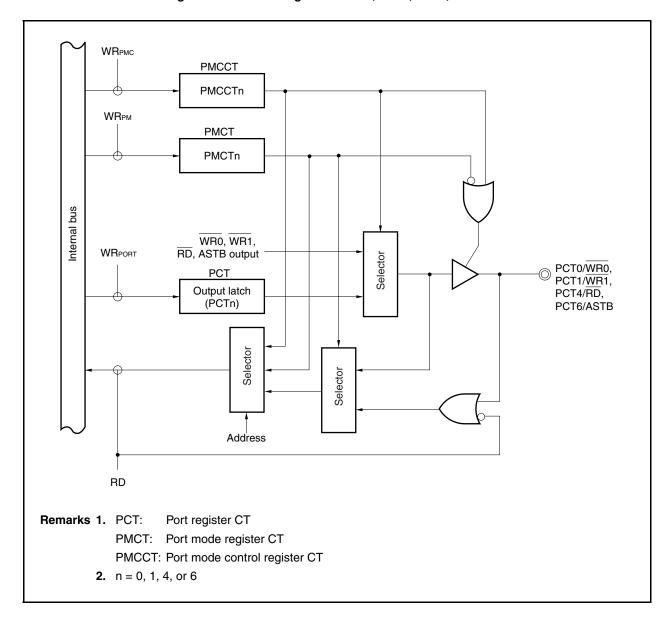

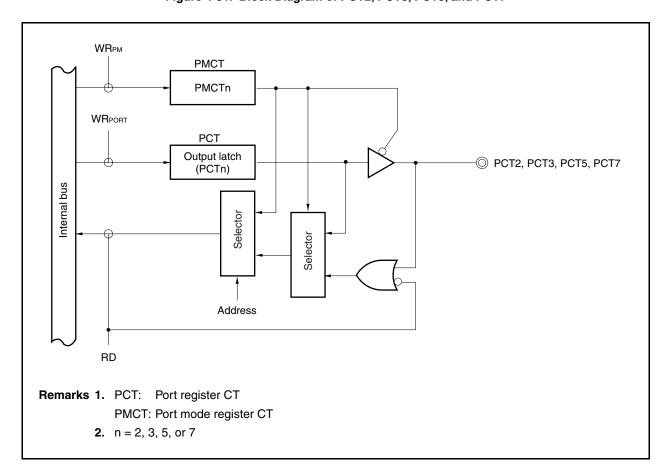

| PCT                 | 6-bit I/O (V850ES/SA2)<br>8-bit I/O (V850ES/SA3)       |                      | External bus interface                                                   |

| PDH                 | 6-bit I/O (V850ES/SA2)<br>8-bit I/O (V850ES/SA3)       |                      | External address bus                                                     |

| PDL                 | 16-bit I/O                                             |                      | External address/data bus                                                |

Note V850ES/SA3 only

#### **CHAPTER 2 PIN FUNCTIONS**

#### 2.1 Pin Function List

This chapter explains the names and functions of the pins in the V850ES/SA2 and V850ES/SA3, classified into port pins and non-port pins.

Two power supplies are available for the pin I/O buffers:  $AV_{DD}$  and  $EV_{DD}$ . The relationship between the power supplies and pins is shown below.

Table 2-1. I/O Buffer Power Supply for Each Pin

| Power Supply     | Corresponding Pin                                                                                   |

|------------------|-----------------------------------------------------------------------------------------------------|

| AV <sub>DD</sub> | Port 7, port 8                                                                                      |

| EV <sub>DD</sub> | Port 0, port 2, port 3, port 4, port 9, port CD, port CM, port CS, port CT, port DH, port DL, RESET |

The differences in the pins of the V850ES/SA2 and V850ES/SA3 are shown below.

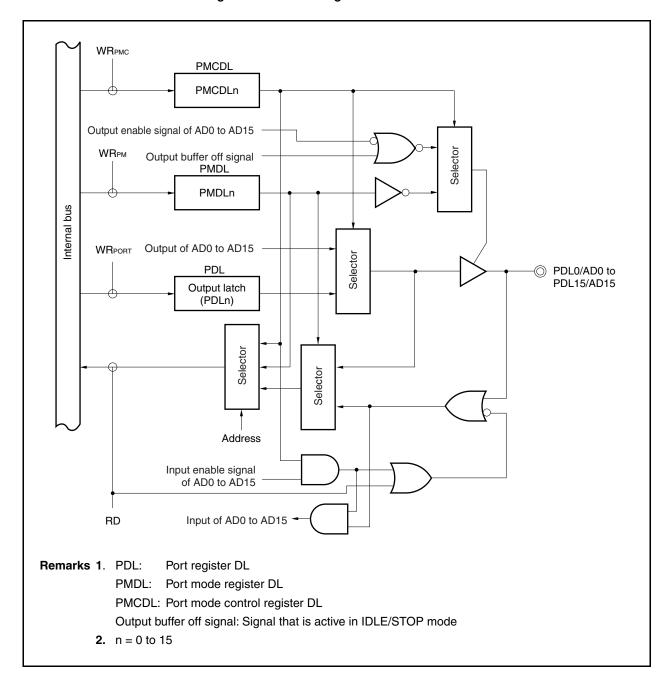

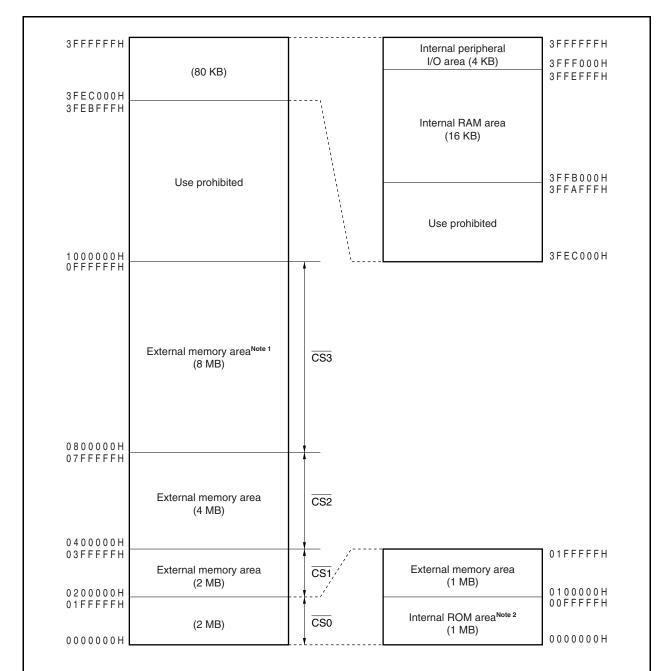

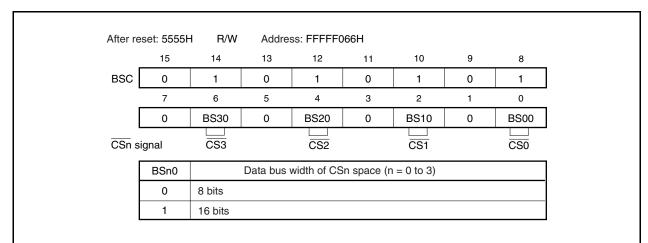

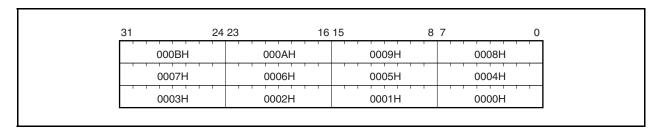

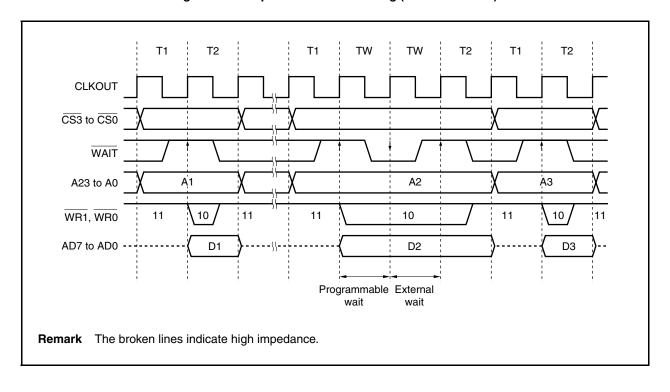

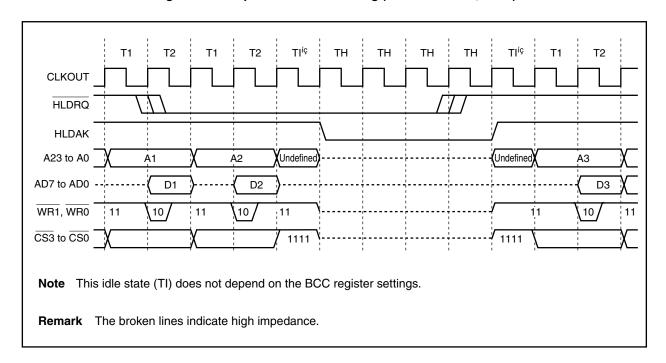

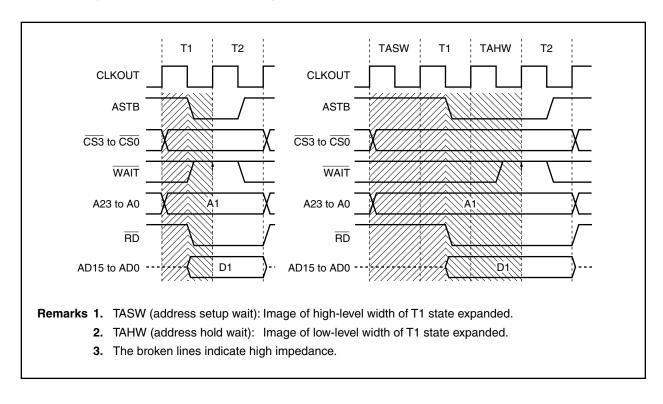

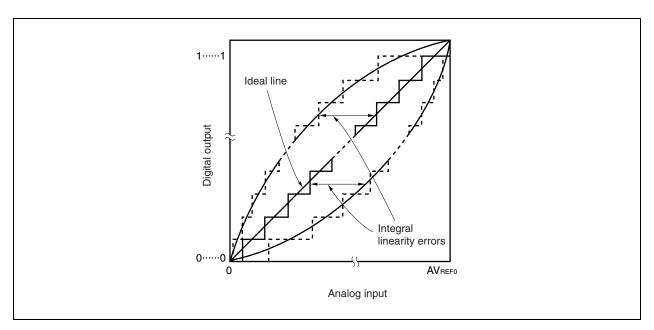

Table 2-2. Differences in Pins of V850ES/SA2 and V850ES/SA3