## **FEATURES**

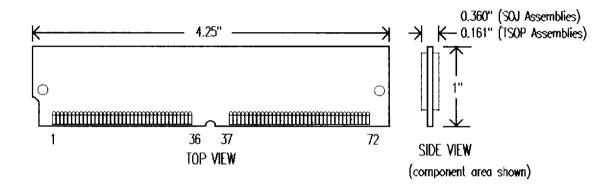

- 72-pin industry standard 4-byte single-in-line memory module

- JEDEC compliant: 21-C, Fig. 4-18 A,B, Fig 4-6 (Release 6);

No.95 MO-116

- Supports 90°, 40° and 22.5° connectors

- · High performance, CMOS

- Single 5V ± 10% power supply

- TTL-compatible inputs and outputs

- FAST PAGE MODE access cycle

- Refresh modes: RAS-ONLY, CAS-BEFORE-RAS, HIDDEN

- Refresh: 2048 refresh cycles every 32 ms

- Dimensions: 4.25" (length) x 1.00" (height) x 0.360" (max thickness)

# **PERFORMANCE RANGE**

| t <sub>CAC</sub> t <sub>AA</sub> t <sub>RC</sub> | DADAMETER                       | Rating       |              |  |  |

|--------------------------------------------------|---------------------------------|--------------|--------------|--|--|

|                                                  | PARAMETER                       | 60 ns        | 7'0 ns       |  |  |

| t <sub>RAC</sub>                                 | RAS Access Time                 | 60 ns (max)  | 70 ris (max) |  |  |

| t <sub>CAC</sub>                                 | CAS Access Time                 | 15 ns (max)  | 20 ris (max) |  |  |

| t <sub>AA</sub>                                  | Access Time from Column Address | 30 ns (max)  | 35 ris (max) |  |  |

| t <sub>RC</sub>                                  | Random Read or Write Cycle Time | 110 ns (min) | 130 ns (min) |  |  |

| t <sub>PC</sub>                                  | Fast Page Mode Cycle Time       | 40 ns (min)  | 45 ns (min)  |  |  |

## **ORDERING INFORMATION**

| DESCRIPTION                         | PART<br>NUMBER | ENGINEERING DESCRIPTOR |  |  |

|-------------------------------------|----------------|------------------------|--|--|

| 8M x 32, 60 ns, Gold Tabs, SOJ      | 20022C         | CL001E08320B0DJ-60     |  |  |

| 8M x 32, 60 ns, Gold Tabs, TSOP     | 20603C         | CL001E08320B0DT-60     |  |  |

| 8M x 32, 60 ns, Tin/Lead Tabs, SOJ  | 14864C         | CL001D08320B0DJ-60     |  |  |

| 8M x 32, 60 ns, Tin/Lead Tabs, TSOP | 20604C         | CL001D08320B0DT-60     |  |  |

| 8M x 32, 70 ns, Gold Tabs, SOJ      | 20004C         | CL001E08320B0DJ-70     |  |  |

| 8M x 32, 70 ns, Gold Tabs, TSOP     | 20605C         | CL001E08320B0DT-70     |  |  |

| 8M x 32, 70 ns, Tin/Lead Tabs, SOJ  | 4779C          | CL001D08320B0DJ-70     |  |  |

| 8M x 32, 70 ns, Tin/Lead Tabs, TSOP | 20606C         | CL001D08320B0DT-70     |  |  |

| 8M x 32, 60 ns, Gold Tabs, SOJ      | 20092C         | CL001E08320B0EJ-60     |  |  |

| 8M x 32, 60 ns, Tin/Lead Tabs, SOJ  | 20093C         | CL001D08320B0EJ-60     |  |  |

| 8M x 32, 70 ns, Gold Tabs, SOJ      | 20094C         | CL001E08320B0EJ-70     |  |  |

| 8M x 32, 70 ns, Tin/Lead Tabs, SOJ  | 20095C         | CL001D08320B0EJ-70     |  |  |

Page: 1 of 14

#### **CARD OUTLINE**

#### **GENERAL DESCRIPTION**

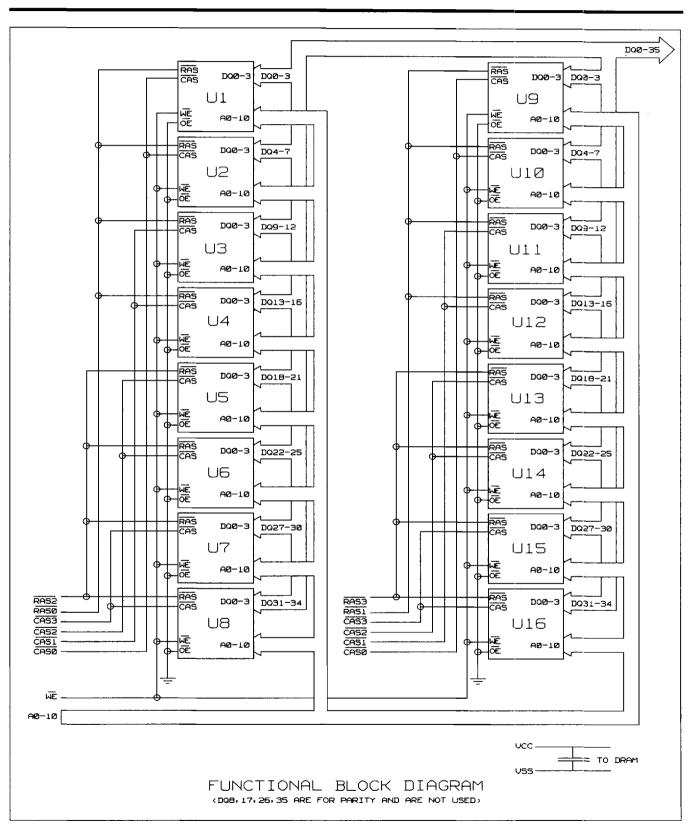

The 8M x 32 SIMM uses dynamic RAM devices and is designed for use as a general-purpose 4-byte wide memory assembly with 8 data bits per byte. The SIMM is populated with sixteen 4M x 4 DRAMs.

Presence Detect (PD) bits provide information about SIMM density, addressing, performance and features.

During Read or Write Cycles, each byte may be uniquely addressed via 22 address bits, with the first eleven bits (A0~A10) latched on RAS and the latter eleven bits (A0~A10) latched on CAS. READ or WRITE cycles are selected with the WE input, with a logic low indicating a WRITE cycle and a logic HIGH indicating a READ cycle. During a WRITE cycle, data-in is latched by the falling edge of WE or CAS, whichever occurs last.

FAST PAGE MODE operation allows for faster READs or WRITEs within a row-address-defined page boundary. A FAST PAGE MODE cycle is initiated with RAS followed by CAS, then strobing CAS to latch different column addresses while holding RAS LOW.

Returning RAS and CAS high terminates a memory cycle and returns the DRAMs to a reduced-current STANDBY state.

Memory cell data is retained in its correct state by maintaining power and executing any RAS cycle (READ, WRITE) or RAS refresh cycle (RAS-ONLY, CBR, or HIDDEN) so that all 2048 combinations of RAS addresses (A0~A10) are executed at least every 32 ms. The CBR refresh and HIDDEN refresh cycles will invoke the on-chip refresh address counters for automatic RAS addressing.

# **PIN DESCRIPTION**

| RAS0~RAS3                        | Row Address Strobe    |

|----------------------------------|-----------------------|

| CAS0~CAS3                        | Column Address Strobe |

| WE                               | Write Enable          |

| A0~A10                           | Address Inputs        |

| DQ0~7,DQ9~16,<br>DQ18~25,DQ27~34 | Data In/Out           |

| VCC                              | Power (+5.0V)         |

| VSS                              | Ground                |

| NC                               | No Connection         |

| PD1~4                            | Presence Detects      |

# PRESENCE DETECT

| PIN SYMBOL | CONFIGU | JRATION |

|------------|---------|---------|

| PIN STMBOL | 60 ns   | 70 ns   |

| PD1        | NC      | NC      |

| PD2        | VSS     | VSS     |

| PD3        | NC      | VSS     |

| PD4        | NC      | NC      |

#### **PIN CONFIGURATION**

| #  | Name |

|----|------|----|------|----|------|----|------|----|------|----|------|

| 1  | VSS  | 13 | A1   | 25 | DQ24 | 37 | NC   | 49 | DQ9  | 61 | DQ14 |

| 2  | DQ0  | 14 | A2   | 26 | DQ7  | 38 | NC   | 50 | DQ27 | 62 | DQ33 |

| 3  | DQ18 | 15 | A3   | 27 | DQ25 | 39 | vss  | 51 | DQ10 | 63 | DQ15 |

| 4  | DQ1  | 16 | A4   | 28 | A7   | 40 | CAS0 | 52 | DQ28 | 64 | DQ34 |

| 5  | DQ19 | 17 | A5   | 29 | NC   | 41 | CAS2 | 53 | DQ11 | 65 | DQ16 |

| 6  | DQ2  | 18 | A6   | 30 | VCC  | 42 | CAS3 | 54 | DQ29 | 66 | NC   |

| 7  | DQ20 | 19 | A10  | 31 | A8   | 43 | CAS1 | 55 | DQ12 | 67 | PD1  |

| 8  | DQ3  | 20 | DQ4  | 32 | A9   | 44 | RAS0 | 56 | DQ30 | 68 | PD2  |

| 9  | DQ21 | 21 | DQ22 | 33 | RAS3 | 45 | RAS1 | 57 | DQ13 | 69 | PD3  |

| 10 | vcc  | 22 | DQ5  | 34 | RAS2 | 46 | NC   | 58 | DQ31 | 70 | PD4  |

| 11 | NC   | 23 | DQ23 | 35 | NC   | 47 | WE   | 59 | VCC  | 71 | NC   |

| 12 | A0   | 24 | DQ6  | 36 | NC   | 48 | NC   | 60 | DQ32 | 72 | vss  |

## **TRUTH TABLE**

| FUNCTION               |           | RAS   | CAS | WE | ROW<br>ADDR | COL<br>ADDR | DATA IN/OUT            |

|------------------------|-----------|-------|-----|----|-------------|-------------|------------------------|

| Standby                |           | Н     | H→X | Х  | Х           | Х           | Hi-Z                   |

| Read                   |           | L     | L   | Н  | ROW         | COL         | Valid D <sub>oJT</sub> |

| Early-Write            |           | L     | L   | L  | ROW         | COL         | Valid D <sub>IN</sub>  |

| Fast Page Mode-Read    | 1st Cycle | L     | H-L | Н  | ROW         | COL         | Valid D <sub>o∪T</sub> |

| rast rage Mode-nead    | 2nd Cycle | L     | H→L | Н  | N/A         | COL         | Valid D <sub>out</sub> |

| Fast Page Mode-Write   | 1st Cycle | L     | H⊸L | L  | ROW         | COL         | Valid D <sub>IN</sub>  |

| rasi rage Mode-wille   | 2nd Cycle | L     | H→L | L  | N/A         | COL         | Valid D <sub>IN</sub>  |

| RAS-Only Refresh       |           | L     | Н   | Х  | ROW         | N/A         | Hi-Z                   |

| Hidden Refresh         | Read      | L→H→L | L   | Н  | ROW         | COL         | Valid D <sub>олт</sub> |

| Hidden heitesti        | Write     | L→H→L | L   | L  | ROW         | COL         | Valid D <sub>IN</sub>  |

| CAS-Before-RAS Refresh |           | H→L   | L   | Н  | Х           | Х           | Hi-Z                   |

X:"H" or "L" D<sub>IN</sub>:Data In D<sub>OUT</sub>:Data Out Hi-Z:High Impedance N/A:Not Applicable

## **ABSOLUTE MAXIMUM RATINGS** (Note 1,22)

| SYMBOL           | PARAMETER                                      | RATING      | UNITS | NOTES |  |

|------------------|------------------------------------------------|-------------|-------|-------|--|

| V <sub>cc</sub>  | Power Supply Voltage                           | -1.0 to 7.0 | V     | 2     |  |

| V <sub>IN</sub>  | Voltage on any Bin Bolotive to V               | -1.0 to 7.0 | V     | 2     |  |

| V <sub>out</sub> | Voltage on any Pin Relative to V <sub>ss</sub> | -1.0 to 7.0 | V     | 2     |  |

| T <sub>opr</sub> | Operating Temperature                          | 0 to 70     | °C    |       |  |

| T <sub>stg</sub> | Storage Temperature                            | -55 to 125  | °C    |       |  |

| P <sub>D</sub>   | Power Dissipation                              | 16.0        | W     | 17,31 |  |

| os               | Short Circuit Output Current                   | 50          | mA    | 17    |  |

**RECOMMENDED OPERATING CONDITIONS** (T<sub>A</sub>= 0 to 70 °C) (Note 2)

| SYMBOL          | PARAMETER          | MIN. | TYP. | MAX.                 | UNITS | NOTES |

|-----------------|--------------------|------|------|----------------------|-------|-------|

| V <sub>cc</sub> | Supply Voltage     | 4.5  | 5.0  | 5.5                  | V     |       |

| V <sub>ss</sub> | Ground             | 0    | 0    | 0                    | V     |       |

| V <sub>iH</sub> | Input High Voltage | 2.4  | -    | V <sub>cc</sub> +1.0 | V     | 22    |

| V <sub>IL</sub> | Input Low Voltage  | -1.0 | -    | 0.8                  | V     | 22    |

T<sub>A</sub>: Ambient temperature

# **CAPACITANCE** (f = 1 MHz; $T_A = 25$ °C) (Note 22)

| SYMBOL          | PARAMETER                        | MAX. | UNITS | NOTES |

|-----------------|----------------------------------|------|-------|-------|

| C <sub>i1</sub> | Input Capacitance (A0-A10)       | 96   | pF    |       |

| C <sub>12</sub> | Input Capacitance (RAS0~RAS3)    | 28   | pF    |       |

| C <sub>13</sub> | Input Capacitance (CAS0~CAS3)    | 28   | pF    |       |

| C <sub>14</sub> | Input Capacitance (WE)           | 112  | pF    |       |

| C <sub>O1</sub> | Output Capacitance (Data In/Out) | 14   | pF    |       |

T<sub>A</sub>: Ambient temperature

## DC CHARACTERISTICS

(Recommended operating conditions unless otherwise noted.) (Note 18,22)

| SYMBOL           | PARAMETER                                                                                                                                                     |                                                             | SPEED         | MIN. | MAX. | NOTES             |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------|------|------|-------------------|

| I <sub>CC1</sub> | OPERATING CURRENT: Ave<br>Operating Current (RAS,CAS                                                                                                          |                                                             | 60 ns         | -    | 896  | 3,4,5,6,16        |

|                  | $t_{RC(min)}, V_{CC} = V_{CC (max)} (mA)$                                                                                                                     |                                                             | 70 ns         | -    | 816  |                   |

| I <sub>CC2</sub> | STANDBY CURRENT (TTL):<br>Current (RAS=CAS=Vcc, Dat<br>all other inputs =Vcc, V <sub>cc</sub> =V <sub>cc</sub>                                                | a out is disabled (Hi-Z),                                   | Don't<br>Care | -    | 32   |                   |

| I <sub>CC3</sub> | RAS-ONLY REFRESH CURRENT: Average Power Supply Current, RAS-Only Mode (RAS, Address                                                                           |                                                             | 60 ns         |      | 1760 | 3,4,5,6,16,<br>31 |

|                  | Cycling, CAS=V <sub>IH</sub> @t <sub>RC</sub> =t <sub>RC(min)</sub> ,                                                                                         | $V_{CC} = V_{CC(max)}$ ) (mA)                               | 70 ns         | -    | 1600 |                   |

| I <sub>CC4</sub> | FAST PAGE MODE CURRENT: Average Power Supply Current, FPM (RAS=V <sub>IL</sub> ,CAS, Address                                                                  |                                                             | 60 ns         |      | 656  | 3,4,5,7,16        |

|                  | Cycling@ t <sub>PC</sub> =t <sub>PC(min)</sub> ,V <sub>CC</sub> =V <sub>CC(m</sub>                                                                            | $_{\max})$ (mA)                                             | 70 ns         | -    | 576  |                   |

| I <sub>CC5</sub> | STANDBY CURRENT (CMOS): Power Supply Standby Current ( $\overline{RAS}=\overline{CAS}=V_{CC}-0.2V$ , Data Out is disabled (Hi-Z), $V_{CC}=V_{CC(max)}$ ) (mA) |                                                             | Don't<br>Care | -    | 16   |                   |

| I <sub>CC6</sub> | CAS-BEFORE-RAS, REFRES                                                                                                                                        |                                                             | 60 ns         | -    | 1760 | 3,4,5,6,16,       |

|                  | (RAS,CAS Cycling@t <sub>RC</sub> =t <sub>RC(mir</sub>                                                                                                         |                                                             | 70 ns         | -    | 1600 |                   |

| I <sub>LI</sub>  | INPUT LEAKAGE<br>CURRENT: Input Leakage                                                                                                                       | A0~A10, WE                                                  |               | -160 | 160  |                   |

|                  | Current, any input $(0 \le V_{IN} \le V_{cc}, \text{ all other pins not })$                                                                                   | RASO~RAS3                                                   |               | -40  | 40   |                   |

|                  | under test=0V, $V_{CC=}V_{CC(max)}$ ) ( $\mu A$ )                                                                                                             | CASO~CAS3                                                   |               | -40  | 40   |                   |

| I <sub>LO</sub>  | OUTPUT LEAKAGE CURREN                                                                                                                                         | NT: (Data Out is disabled (Hi-Z),                           |               | -20  | 20   |                   |

| $V_{OH}$         | OUTPUT HIGH LEVEL: Outpu                                                                                                                                      | EVEL: Output "H" Level Voltage (I <sub>OUT</sub> =-5mA) (V) |               | 2.4  | -    | 2                 |

| V <sub>OL</sub>  | OUTPUT LOW LEVEL: Output(V)                                                                                                                                   | ıt "L" Level Voltage (Ι <sub>ουτ</sub> =+                   | 4.2mA)        | -    | 0.4  | 2                 |

## **AC CHARACTERISTICS**

# READ, WRITE, AND REFRESH CYCLES (COMMON PARAMETERS)

(Recommended operating conditions unless otherwise noted.) (Note 8,18)

| CVMPOL           | PARAMETER                                       | 60   | ns    | 70   | ns    | NOTEC |

|------------------|-------------------------------------------------|------|-------|------|-------|-------|

| . <u> </u>       |                                                 | MIN. | MAX.  | MIN. | MAX.  | NOTES |

| t <sub>RC</sub>  | Random READ or WRITE Cycle Time (ns)            | 110  | -     | 130  | -     |       |

| t <sub>RP</sub>  | RAS Precharge Time (ns)                         | 40   | -     | 50   | -     |       |

| t <sub>CP</sub>  | CAS Precharge Time (ns)                         | 10   | -     | 10   | -     |       |

| t <sub>ras</sub> | RAS Pulse Width (ns)                            | 60   | 10000 | 70   | 10000 | 23    |

| t <sub>cas</sub> | CAS Pulse Width (ns)                            | 15   | 10000 | 20   | 10000 | 23    |

| t <sub>asr</sub> | Row Address Setup Time (ns)                     | 0    | -     | 0    | -     | 22    |

| t <sub>rah</sub> | Row Address Hold Time (ns)                      | 10   | -     | 10   | -     |       |

| t <sub>asc</sub> | Column Address Setup Time (ns)                  | 0    | -     | 0    | -     | 22    |

| t <sub>cah</sub> | Column Address Hold Time (ns)                   | 10   | -     | 15   | -     | 22    |

| t <sub>RCD</sub> | RAS to CAS Delay Time (ns)                      | 20   | 45    | 20   | 50    | 10    |

| t <sub>RAD</sub> | RAS to Col. Address Delay Time (ns)             | 15   | 30    | 15   | 35    | 15,23 |

| t <sub>RSH</sub> | RAS Hold Time (ns)                              | 15   | -     | 20   | -     | 22    |

| t <sub>csн</sub> | CAS Hold Time (ns)                              | 60   | -     | 70   | ***   |       |

| t <sub>CRP</sub> | CAS to RAS Precharge Time (ns)                  | 5    | _     | 5    | -     | 22    |

| t <sub>RPC</sub> | RAS Precharge to CAS hold Time (ns)             | 5    | -     | 5    | -     | 22    |

| t <sub>T</sub>   | Transition Time (Rise and Fall) (ns)            | 3    | 30    | 3    | 30    | 22    |

| t <sub>AR</sub>  | Column Address Hold Time Referenced to RAS (ns) | -    | -     | -    | -     |       |

**READ CYCLES** (Note 8.18)

| CVMDOL           | PARAMETER                           | 60   | ns   | 70   | ns   | NOTEO      |

|------------------|-------------------------------------|------|------|------|------|------------|

| STWBOL           |                                     | MIN. | MAX. | MIN. | MAX. | NOTES      |

| t <sub>RAC</sub> | Access Time from RAS (ns)           | -    | 60   | -    | 70   | 9,10,15,30 |

| t <sub>CAC</sub> | Access Time from CAS (ns)           | -    | 15   |      | 20   | 9,10,30    |

| t <sub>AA</sub>  | Access Time from Address (ns)       | -    | 30   | -    | 35   | 9,15,30    |

| t <sub>RCS</sub> | Read Command Setup Time (ns)        | 0    | -    | 0    | -    | 22         |

| t <sub>ACH</sub> | Read Command Hold Time to CAS (ns)  | 0    | -    | 0    | -    | 14,22      |

| t <sub>RRH</sub> | Read Command Hold Time to RAS (ns)  | 0    | -    | 0    | -    | 14,22      |

| t <sub>RAL</sub> | Column Address to RAS Lead Time(ns) | 30   | -    | 35   | -    | 22         |

| t <sub>CLZ</sub> | CAS to Output in Low-Z (ns)         | 0    | -    | 0    | -    | 9,22       |

| t <sub>DZC</sub> | Data to CAS Low Delay Time (ns)     | -    | -    | -    | -    |            |

| t <sub>CDD</sub> | CAS High to Data Delay Time (ns)    | 15   | -    | 18   | -    | 27         |

| t <sub>OFF</sub> | Output Buffer Turn-Off Delay (ns)   | 0    | 15   | 0    | 20   | 12,24      |

WRITE CYCLES (Note 8,18)

| SYMBOL           | PARAMETER                                      | 60 ns |      | 70 ns |      | NOTES |

|------------------|------------------------------------------------|-------|------|-------|------|-------|

|                  |                                                | MIN.  | MAX. | MIN.  | MAX. | NOTES |

| t <sub>wcs</sub> | Write Command Set Up Time (ns)                 | 0     | -    | 0     | -    | 13    |

| t <sub>wch</sub> | Write Command Hold Time (ns)                   | 10    | -    | 15    | -    |       |

| t <sub>wp</sub>  | Write Command Pulse Width (ns)                 | 10    | -    | 15    | -    | 22    |

| t <sub>RWL</sub> | Write Command to RAS Lead Time (ns)            | 15    | -    | 20    | -    | 22    |

| t <sub>cwL</sub> | Write Command to CAS Lead Time (ns)            | 15    | -    | 20    | -    | 22    |

| t <sub>os</sub>  | D <sub>IN</sub> Setup Time (ns)                | 0     | -    | 0     | -    | 25    |

| t <sub>on</sub>  | D <sub>IN</sub> Hold Time (ns)                 | 10    | -    | 15    | -    | 22,25 |

| t <sub>wcn</sub> | Write Command Hold Time Referenced to RAS (ns) | -     | -    | -     | -    |       |

| t <sub>DHR</sub> | Data in Hold Time Referenced to RAS (ns)       | -     | -    | -     | -    |       |

FAST PAGE MODE CYCLES (Note 8,18)

| SYMBOL            | PARAMETER                             | 60 ns |        | 70 ns |        | NOTEO |

|-------------------|---------------------------------------|-------|--------|-------|--------|-------|

|                   |                                       | MIN.  | MAX.   | MIN.  | MAX.   | NOTES |

| t <sub>PC</sub>   | Fast Page Mode Cycle Time (ns)        | 40    | -      | 45    | -      |       |

| t <sub>rasp</sub> | Fast Page Mode RAS Pulse Width (ns)   | 60    | 100000 | 70    | 100000 | 22    |

| t <sub>CPRH</sub> | RAS Hold Time from CAS Precharge (ns) | 35    | -      | 40    | -      | 22    |

| t <sub>cpa</sub>  | Access Time from CAS Precharge (ns)   | -     | 35     | -     | 40     | 21,22 |

| t <sub>CPW</sub>  | WE Delay Time From CAS Precharge (ns) | 60    | _      | 70    | -      |       |

REFRESH CYCLE (Note 8,18)

| SYMBOL           | PARAMETER                                          | 60 ns |      | 70 ns |      | NOTES |

|------------------|----------------------------------------------------|-------|------|-------|------|-------|

|                  |                                                    | MIN.  | MAX. | MIN.  | MAX. | NOTES |

| t <sub>CHR</sub> | CAS Hold Time (CAS-before-RAS Refresh Cycle) (ns)  | 10    | -    | 15    | -    | 22    |

| t <sub>CSR</sub> | CAS Setup Time (CAS-before-RAS Refresh Cycle) (ns) | 5     | -    | 5     | -    |       |

| t <sub>wrp</sub> | WE Setup Time (CAS-before-RAS Refresh Cycle) (ns)  | 10    | -    | 10    | -    | 22    |

| t <sub>wrt</sub> | WE Hold Time (CAS-before-RAS Refresh Cycle) (ns)   | 10    | -    | 10    | -    | 22    |

| t <sub>REF</sub> | Refresh Period (2048 cycles) (ms)                  | -     | 32   | -     | 32   |       |

#### **NOTES**

- 1. Permanent damage to the device may occur if "ABSOLUTE MAXIMUM RATINGS" are exceeded. Functional operation should be restricted to the conditions as detailed in this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. All voltages referenced to V<sub>ss</sub>.

- I<sub>cc</sub> is specified as an average current.

- This parameter depends on output loading and/or cycle rates.

- Specified values are obtained with the output open.

- 6. Address can be changed a maximum of once while RAS=V<sub>11</sub>.

- 7. Address can be changed a maximum of once while CAS=V<sub>IH</sub>.

- $V_{IH(min)}$  and  $V_{IL(max)}$  are reference levels for measuring timing of input signals. Transition time  $(t_{\tau})$  is measured between  $V_{IH(min)}$  and  $V_{IL(max)}$ , and is assumed to be 5ns for all inputs. All input signals must transit between  $V_{IH}$ and  $V_{IL}$  (or  $V_{IL}$  and  $V_{IH}$ ) without slope reversal.

- 9. Measured with a load equivalent to 2 TTL loads and 100pF.

- 10. Operation within the  $t_{RCD(max)}$  limit ensures that  $t_{RAC(max)}$  can be met.  $t_{RCD(max)}$  is specified as a reference point only. If t<sub>RCD</sub> is greater than the specified t<sub>RCD(max)</sub> limit, then access time is controlled exclusively by t<sub>CAC</sub>.

- 11. Assumes that  $t_{RCD} \ge t_{RCD(max)}$ ,  $t_{RAD} \le t_{RAD(max)}$ .

- 12. This parameter defines the time at which the output achieves the open circuit condition and is not referenced to  $V_{OH}$  or  $V_{OL}$ .

- 13. This is a non-restrictive operating parameter. It is included in the data sheet as an electrical characteristic only. If  $t_{wcs} \ge t_{wcs(min)}$  the cycle is an early write cycle and the data out pins will remain high impedance (open circuit) for the duration of the cycle. If the above condition is not satisfied, the condition of the data out (at access time) is indeterminate.

- 14. Either t<sub>RCH</sub> or t<sub>RRH</sub> must be satisfied for a read cycle.

- 15. Operation within the  $t_{RAD(max)}$  limit ensures that  $t_{RAC(max)}$  can be met.  $t_{RAD(max)}$  is specified as a reference point only. If t<sub>RAD</sub> is greater than the specified t<sub>RAD(max)</sub> limit, then access time is controlled exclusively by t<sub>AA</sub>.

- **16.** Specified values are obtained with minimum cycle time.

- 17. Specified values are obtained with  $T_A = 25$  °C.

- 18. An initial pause of 200μs is required after power-up followed by a minimum of eight initialization cycles (any 8 CAS-before-RAS or RAS-only Refresh cycles with WE high) before proper device operation is assured. Also, any 8 CAS-before-RAS or RAS-only Refresh cycles with WE high are required after prolonged periods (greater than t<sub>REF</sub>) of RAS inactivity before proper device operation is assured.

- 19. Measured with a load equivalent to 50pF and 500 ohms.

- 20. Write cycle is applicable instead of read cycle. Timing requirements for RAS, CAS and Address are the same for Hidden Refresh Write Cycle as that shown for Hidden Refresh Read Cycle. WE, D<sub>IN</sub> and D<sub>DUT</sub> for Hidden Refresh Write Cycle are the same as for Write Cycle.

- 21.  $t_{CPA}$  is access time from  $\overline{CAS}$  precharge (that is caused by changing  $\overline{CAS}$  from "L" to "H"). Therefore, if  $t_{CP}$  is long, then  $t_{CPA}$  is longer than  $t_{CPA(max)}$ .

- 22. Calculated based on data supplied by the DRAM manufacturer(s).

- 23. Maximum value is calculated based on data supplied by the DRAM manufacturer(s).

- 24. Minimum value is calculated based on data supplied by the DRAM manufacturer(s).

- 25. This parameter is referenced to the CAS leading edge in Early Write cycles and to the WE leading edge in Read-Modify-Write cycles.

- **26.**  $V_{IN} = 0$  Volt.

- 27. Either t<sub>CDD</sub> or t<sub>ODD</sub> must be satisfied.

- 28. Either t<sub>DZC</sub> or t<sub>DZO</sub> must be satisfied.

- 29. t<sub>RASP(MIN)</sub> is specified as two cycles of CAS input are performed.

- 30. The access time is limited by all four parameters  $t_{RAC}$ ,  $t_{CAC}$ ,  $t_{AA}$ ,  $t_{CPA}$ .

- 31. This assumes all RAS (and all CAS for CBR refresh) are active.

For Timing Diagrams see "FPM Timing Diagrams" (Document No. 20432C).

Available from fax-on-demand and Website: http://www.celestica.com/memory/

Celestica Inc. 1996 Contact Information For further information on this product, please call:

Celestica 1-888-889-9998

The information provided is believed to be accurate and reliable. Celestica reserves the right to make changes to this document and to the product described without notice. No liability is assumed as a result of its use nor for any infringement on the rights of others.

TM Celestica is a trademark of Celestica, Inc.

August 13, 1996