# MP1208/9/10

Microprocessor Compatible Double-Buffered, 12-Bit Digital-to-Analog Converter

#### **FEATURES**

- Lower Data Bus Feedthrough @ CS = 1

- Stable, More Accurate Segmented DAC Approach

- Ultra Stable

- 0.2 ppm/°C Linearity Tempco

- 2 ppm/°C Max Gain Error Tempco

- · Low Sensitivity to Amplifier VOS

- · Low Output Capacitance

- C<sub>OUT1</sub> = 80 pF at Full Scale, Gives Fastest Settling Times, and Larger Stable Bandwidth capability

- Lower Glitch Emergy

- Four Quadrant Municipalication

- Guaranteed Mor otonic

- Low Feedthrough Land

- Low Power Consumption

- TTL/5 V CM 2S Compatible

- Latch-U Free

- -40 C 11 +63 C Operation

- 8-BinBus Version: MP123€A/7231A/1232A

#### **GENERAL DESCRIPTION**

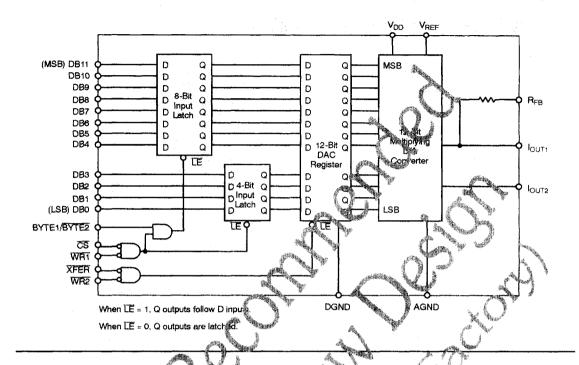

The MP1208/09/10 series are 12-bit Digital-to-Anana Converters with an 8/4 bit latched input interface and provide maximum flexibility in interfacing to LD data bits. All data loading and data transfer operations are identical to the WRITE cycle of a static RAM.

The MP1208 series use unique circuit which significantly reduces transients in massurplies during DATA bus transitions at  $\overline{CS} = 1$ .

The MP1208 series are ma ufactured using advanced thin film resistors on a double metal CMOS process. The MP1208 series is corporates a unique bit deducting technique yielding laws glisch, higher speed and excellent accorder to the proper and time. 2-bit linearity is achieved with minimal trimining. Obstantling features include:

Stability: Both integral and differential line and are rated at 0.2 ppm/°C typical, and monotonicity is guaranteed over the entire temperature range (-40 to +85°C). Scale factor is a low 2 ppm/°C maximum.

Low Output Capacitance: Due to smaller MOSFET switch geometries allowed by decoding, the output capacitance at  $l_0$  and  $l_{OUT2}$  are slow 80pF / 40pF and 25pF / 65 pF for the conditions of full/zero scale. This is over two times less than the Neutonal DAC 1208 Series. Lower apacitance allows the MP1208 series to achieve fester CMOS DAC settling times; less than 1 µsec for a 10 V or to 0.01% when utilizing a high speed output amplifier. Larger output amplifier bandwidths are available, for a given amplifier loop gain, because a smaller feedback "zero" compensating capacitor is required to onset the smaller  $l_{OUT}$  capacitance.

Low Senaitivity to Output Amplifier Offset: 4 quadrant multiplying CMOS DACs provide an output current into the virtual ground of an op amp. The additional linearity error incurred by amplifier offset is reduced by a factor of 2 in the MP1208 series over conventional R-2R DACs, to 330µV per millivolt of offset.

### SIMPLIFIED BLOCK DIAGRAM

## ORDERING INFORMATION

| Pickagi<br>Type | emperature<br>Range | Pal No.  | INL<br>(LSB) | PNL<br>(LSB) | Gain Error<br>(% FSR) |

|-----------------|---------------------|----------|--------------|--------------|-----------------------|

| Plastic Dip     | -40 to +85          | MP12 DHN | ±2           | ±2           | ±0.4                  |

| Plastic Dip     | 40 to €15°C         | W51393N  | ±            | ±1           | ±0.4                  |

| Plastic Dip     | -40 to +85          | MP1208KN | ±1/2         | ±3/4         | ±0.4                  |

<sup>\*</sup>Contact factory for non-compliant military processing

**TATANAN**