# AMDA

# Am79C874

# Quad Fast Ethernet Transceiver Plus (QFEX+™) for 100BASE-X

#### DISTINCTIVE CHARACTERISTICS

- Compatible with IEEE 802.3u standard for 100BASE-TX and 100BASE-FX

- Fully integrated MLT-3 function with Baseline Wander Restoration

- Low latency to meet Class 2 Repeater applications

- Fully integrated Quad Media Independent Interface (MII)

- Quad Integrated Digital CMOS 100 Mbps clock recovery circuits

- Full Duplex capability

- Programmable loopback modes

- **■** Programmable LED support

- Capable of bypassing transmit and receive state machine to support 5-bit symbol interface

- IEEE 1149.1-compatible JTAG support

- Scramble and descramble feature supported for 100BASE-TX

- Link Monitor and Far End Fault Indication (FEFI)

- Optimized for 100BASE-X repeater or switch applications

- Configurable repeater modes supporting port switching

- Carrier Integrity Monitor (CIM) support with dedicated CIM\_ISOLATE counter available in repeater mode

- Direct interface to TX (MLT-3) or FX Physical Medium Dependent (PMD) devices

- Individual False Carrier Indication signal for repeater applications

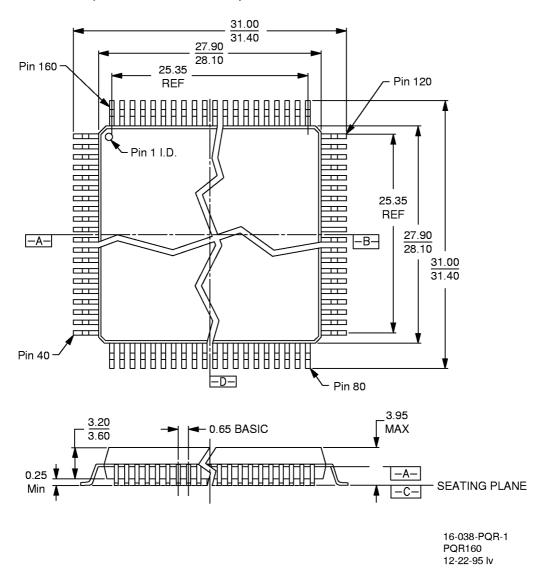

- CMOS device features high integration and low power with a single +5 V supply in 160-pin PQFP

# **GENERAL DESCRIPTION**

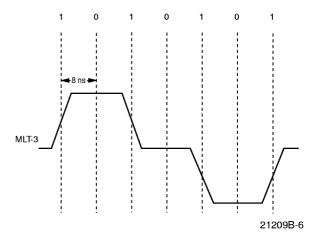

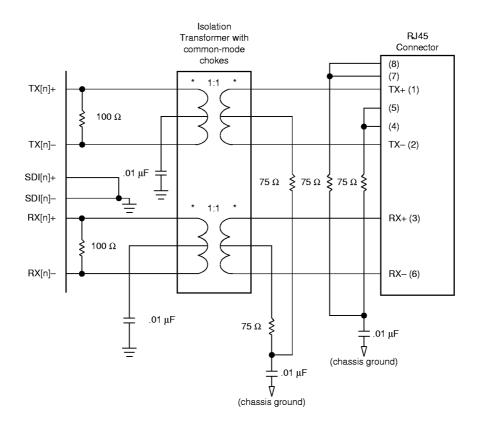

The Am79C874 Quad Fast Ethernet Transceiver Plus (QFEX+) is a CMOS device that implements the MII, Physical Coding Sublayer (PCS), Physical Medium Attachment (PMA), and Physical Medium Dependent (PMD) sublayers, including the MLT-3 functions, for four 100BASE-TX ports. Therefore, the QFEX+ device interfaces directly to magnetics to support operation over two pairs of shielded twisted pair (STP) or two pairs of Category 5 unshielded twisted pair (UTP) cables. The MLT-3 functions can be disabled to support 100BASE-FX applications over two multi-mode fibers.

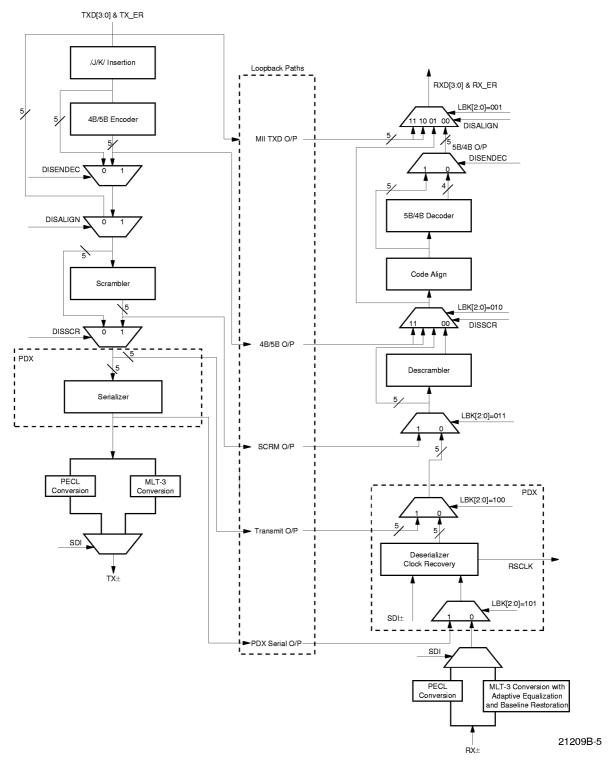

The QFEX+ device performs all the functions of the QFEX (Am79C870) device which include encoding the MII 4-bit data (4B/5B), decoding the received code groups (5B/4B), generating carrier sense and collision detect indications, serializing code groups for transmission, de-serializing received serial data, mapping transmit, receive, carrier sense, and collision at the MII interface, and recovering clock from the incoming data stream. In addition, the QFEX+ device includes an MLT-3 encoder/decoder, baseline wander restoration circuitry, and an adaptive equalizer per port. The QFEX+ chip offers stream cipher scrambling and descrambling capability for 100BASE-TX applications.

When transmitting, the QFEX+ chip receives 4-bit (nibble) wide data across the MII at 25 million nibbles per second. It then encodes the data, optionally scrambles the data, serializes the data, and converts the NRZI data stream to a three-level code for transmission to the network.

When receiving, the QFEX+ chip receives the three-level code and converts it back to an NRZI data stream. It then recovers the clock from the NRZI data stream, de-serializes the data stream, optionally descrambles the data stream, and decodes the code groups (5B/4B).

The QFEX+ chip has an independent MII for each of the four ports. Therefore, all four ports can simultaneously receive data from the network and output data to individual MII ports. The device can also be configured in such a way (referred to as "Shared MII mode" in this document) that the four network ports are independently mapped to either one of the MIIs (MII[0] and MII[1]). In this mode, more than one port can share a single MII.

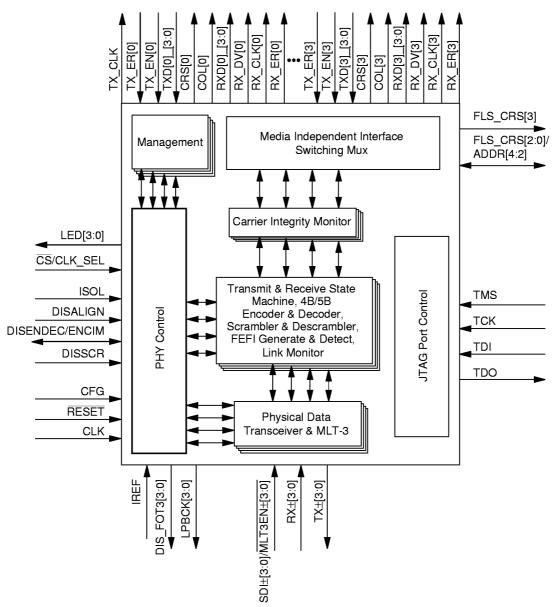

# **BLOCK DIAGRAM (INDEPENDENT MII MODE)**

21209B-1

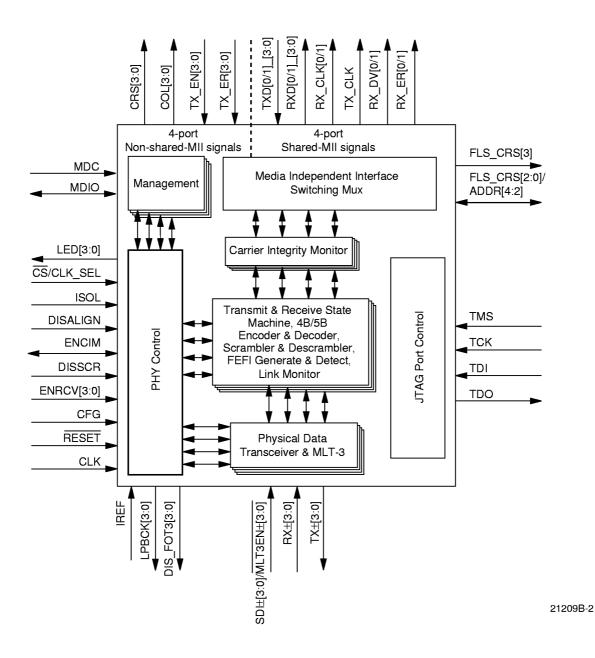

# **BLOCK DIAGRAM (SHARED MII MODE)**

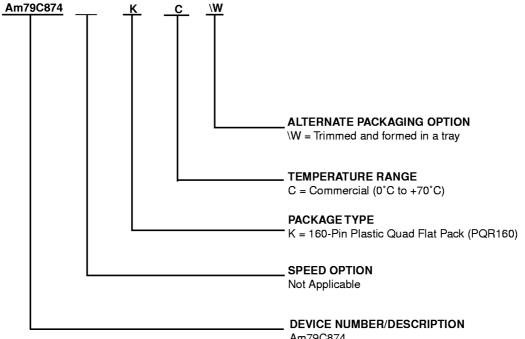

# **ORDERING INFORMATION**

## **Standard Products**

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the elements below.

Am79C874

Quad Fast Ethernet Transceiver Plus (QFEX+) for 100BASE-X

| Valid Combinations |      |  |  |

|--------------------|------|--|--|

| Am79C874           | KC\W |  |  |

# **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

# **RELATED PRODUCTS**

| Part No.  | Description                                                                                 |

|-----------|---------------------------------------------------------------------------------------------|

| Am7990    | Local Area Network Controller for Ethernet (LANCE)                                          |

| Am7992B   | Serial Interface Adapter (SIA)                                                              |

| Am7996    | IEEE 802.3/Ethernet/Cheapernet Transceiver                                                  |

| Am79C90   | CMOS Local Area Network Controller for Ethernet (C-LANCE)                                   |

| Am79C98   | Twisted Pair Ethernet Transceiver (TPEX)                                                    |

| Am79C100  | Twisted Pair Ethernet Transceiver Plus (TPEX+)                                              |

| Am79C730  | Integrated Multiport Repeater 100 (IMR100™)                                                 |

| Am79C870  | Quad Fast Ethernet Transceiver for 100BASE-X (QFEX™)                                        |

| Am79C871  | Quad Fast Ethernet Transceiver for 100BASE-X Repeaters (QFEXr™)                             |

| Am79C875  | Quad Fast Ethernet Transceiver Plus for 100BASE-X Repeaters (QFEXr+™)                       |

| Am79C981  | Integrated Multiport Repeater Plus (IMR+™)                                                  |

| Am79C982  | basic Integrated Multiport Repeater (bIMR™)                                                 |

| Am79C983  | Integrated Multiport Repeater 2 (IMR2™)                                                     |

| Am79C984A | enhanced Integrated Multiport Repeater (elMR™)                                              |

| Am79C985  | enhanced Integrated Multiport Repeater Plus (eIMR+™)                                        |

| Am79C987  | Hardware Implemented Management Information Base (HIMIB™)                                   |

| Am79C988  | Quad Integrated Ethernet Transceiver (QuIET™)                                               |

| Am79C900  | Integrated Local Area Communications Controller (ILACC™)                                    |

| Am79C940  | Media Access Controller for Ethernet (MACE™)                                                |

| Am79C960  | PCnet™-ISA Single-Chip Ethernet Controller (for ISA bus)                                    |

| Am79C961  | PCnet™-ISA+ Single-Chip Ethernet Controller for ISA (with Microsoft® Plug n' Play® Support) |

| Am79C961A | PCnet™-ISA II Full Duplex Single-Chip Ethernet Controller for ISA                           |

| Am79C965  | PCnet™-32 Single-Chip 32-Bit Ethernet Controller                                            |

| Am79C970  | PCnet™-PCl Single-Chip Ethernet Controller (for PCl bus)                                    |

| Am79C970A | PCnet™-PCI II Full Duplex Single-Chip Ethernet Controller (for PCI bus)                     |

| Am79C971B | PCnet™-FAST Single-Chip Full-Duplex 10/100 Mbps Ethernet Controller for PCI Local Bus       |

| Am79C974  | PCnet™-SCSI Combination Ethernet and SCSI Controller for PCI Systems                        |

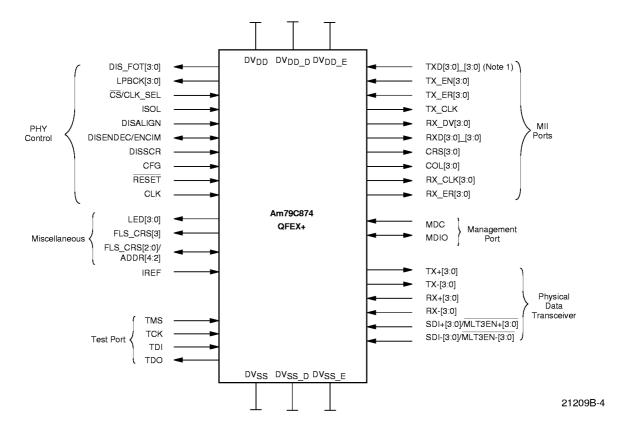

#### **CONNECTION DIAGRAM**

21209B-3

# **LOGIC SYMBOL**

#### Note:

$TXD[2]_[x] = ENRCV[x]$  when CFG = 1.

# **TABLE OF CONTENTS**

| DISTINCTIVE CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| BLOCK DIAGRAM (INDEPENDENT MII MODE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| BLOCK DIAGRAM (SHARED MII MODE)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3    |

| ORDERING INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| Standard Products                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4    |

| RELATED PRODUCTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5    |

| CONNECTION DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6    |

| LOGIC SYMBOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7    |

| PIN DESIGNATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 10 |

| Listed by Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 10 |

| PIN DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 12 |

| Network Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 12 |

| Media Independent Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 12 |

| Configuration, Status, and Control Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| Test Access Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| LED Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| Clock Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |      |

| Media Independent Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| Independent MII Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

| Shared MII Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| False Carrier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| Carrier Integrity Monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| CIM Isolation Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

| 100BASE-X MAU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

| Transmit Process.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |

| Receive Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| Internal Loopback Paths                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| Encoder Encode |      |

| Decoder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

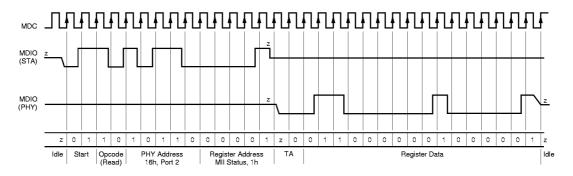

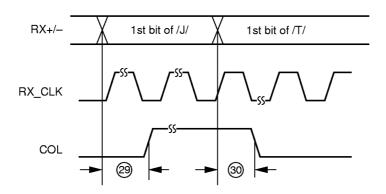

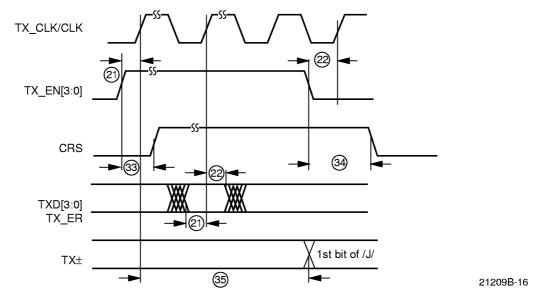

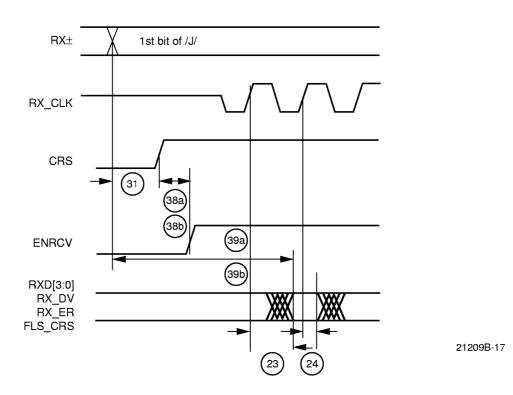

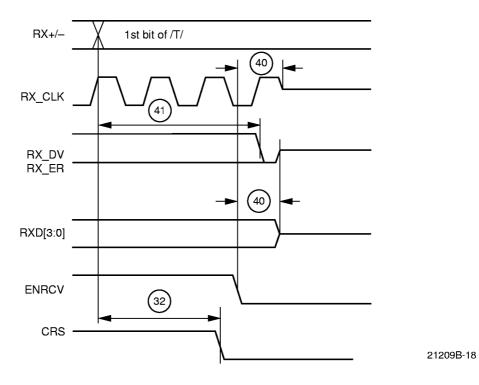

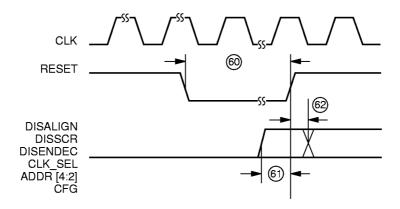

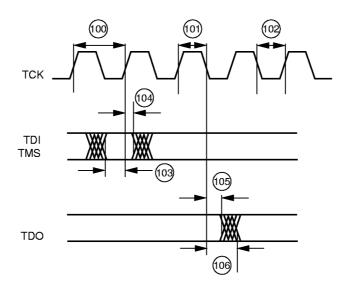

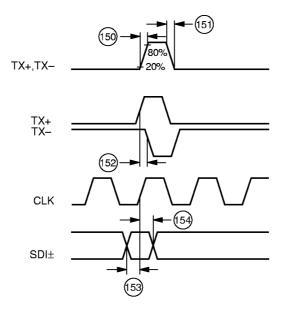

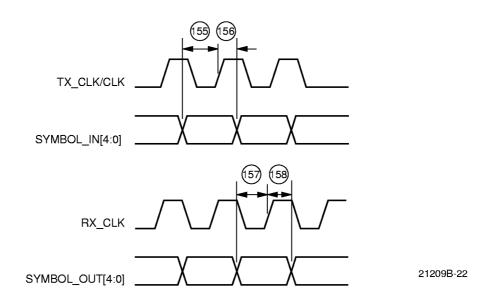

| Scrambler/Descrambler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |