# TRI-STATE 1024-Bit Read Only Memories

### General Description

The DM76L97/DM86L97 is a custom-programmed Read Only Memory organized as 256 four-bit words. Selection of the proper word is accomplished through the eight select inputs.

Two overriding memory enable inputs are provided which when mask-programmed in one of the three options described will cause all four outputs to read either the normal memory contents or go to the high impedance state.

### **Features**

- Full tenth-power technology

- Pin compatible with SN54187/SN74187

- Typical power dissipation

75 mW

Typical access time

70 ns

- Custom-programmed memory enable inputs

- TRI-STATE outputs

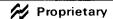

## Connection Diagram

# 76L97/86L97(J), (N), (W)

# Truth Table

| OPTION | M£1 | ME2 | OUTPUTS        |

|--------|-----|-----|----------------|

| 1      | L   | L   | Normal         |

|        | н   | ×   | High Impedance |

|        | ×   | н   | High Impedance |

| 2      | H   | Н   | Normal         |

|        | L   | ×   | High Impedance |

|        | ×   | L   | High Impedance |

| 3      | Н   | L   | Normal         |

|        | ×   | н   | High Impedance |

|        | L   | X   | High Impedance |

X = Don't Care

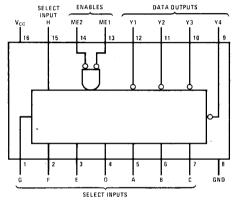

# Logic Diagram

3-144

Electrical Characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER           |                                                    | CONDITIONS                                       |                       |     | UNITS  |      |    |

|---------------------|----------------------------------------------------|--------------------------------------------------|-----------------------|-----|--------|------|----|

|                     |                                                    |                                                  |                       | •   |        |      |    |

|                     |                                                    |                                                  |                       | MIN | TYP(1) | MAX  |    |

| V <sub>IH</sub>     | High Level Input Voltage                           | V <sub>CC</sub> = Min                            |                       | 2   |        |      | V  |

| V <sub>IL</sub>     | Low Level Input Voltage                            | V <sub>CC</sub> = Min                            |                       |     |        | 0.7  | V  |

| V <sub>I</sub>      | Input Clamp Voltage                                | V <sub>CC</sub> = Min, I <sub>1</sub> = -12 mA   |                       |     |        | -1.5 | V  |

| Гон                 | High Level Output Current                          |                                                  |                       |     |        | -1.0 | mA |

| V <sub>OH</sub>     | High Level Output Voltage                          | V <sub>CC</sub> = Min, I <sub>OH</sub> = -1.0 mA |                       | 2.4 |        |      | V  |

| I <sub>OL</sub>     | Low Level Output Current                           |                                                  | DM76                  |     |        | 2.0  | mA |

|                     |                                                    |                                                  | DM86                  |     |        | 3.6  |    |

| V <sub>OL</sub>     | Low Level Output Voltage                           | V <sub>CC</sub> = Min<br>I <sub>OL</sub> = Max   | DM76                  |     |        | 0.3  | V  |

|                     |                                                    |                                                  | DM86                  |     |        | 0.4  |    |

| I <sub>O(OFF)</sub> | Off State (High Impedance<br>State) Output Current | V <sub>CC</sub> = Max                            | V <sub>O</sub> = 0.4V | -   |        | -40  | μΑ |

|                     |                                                    |                                                  | V <sub>O</sub> = 2.4V |     |        | 40   |    |

| 11                  | Input Current at Maximum Input Voltage             | V <sub>CC</sub> = Max, V <sub>i</sub> = 5.5V     |                       |     |        | 100  | μΑ |

| I <sub>IH</sub>     | High Level Input Current                           | $V_{CC} = Max, V_1 = 2.4V$                       |                       |     |        | 10   | μΑ |

| IIL                 | Low Level Input Current                            | V <sub>CC</sub> = Max, V <sub>1</sub> = 0.3V     |                       |     |        | -180 | μА |

| Ios                 | Short Circuit Output Current                       | V <sub>CC</sub> = Max(2)                         |                       | -6  |        | -30  | mA |

| Icc                 | Supply Current                                     | V <sub>CC</sub> = Max                            |                       |     | 15     | 20   | mA |

#### Notes

- (1) All typical values are at  $V_{CC} = 5V$  and  $T_A = 25^{\circ}C$ .

- (2) Not more than one output should be shorted at a time.

Switching Characteristics  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$

| PARAMETER        |                                                     | FROM    | то     |                                           | DM76L/86L<br>L97 |     |     | UNITS |

|------------------|-----------------------------------------------------|---------|--------|-------------------------------------------|------------------|-----|-----|-------|

|                  |                                                     |         |        | CONDITIONS                                |                  |     |     |       |

|                  |                                                     |         |        |                                           | MIN              | TYP | MAX |       |

| t <sub>PLH</sub> | Propagation Delay Time,<br>Low-to-High Level Output | Address | Output | $C_{L} = 50 \text{ pF}, R_{L} = 4k\Omega$ |                  | 86  | 130 | ns    |

| tpHL             | Propagation Delay Time,<br>High-to-Low Level Output | Address | Output |                                           |                  | 55  | 85  | ns    |

| t <sub>ZH</sub>  | Output Enable Time<br>to High Level                 | Enable  | Any    |                                           |                  | 34  | 51  | ns    |

| tzL              | Output Enable Time<br>to Low Level                  | Enable  | Any    | ·                                         |                  | 47  | 70  | ns    |

| t <sub>HZ</sub>  | Output Disable Time<br>from High Level              | Enable  | Any    | $C_1 = 5.0 \text{ pF}, R_L = 4k\Omega$    | , .              | 15  | 23  | ns    |

| t <sub>LZ</sub>  | Output Disable Time<br>from Low Level               | Enable  | Any    |                                           |                  | 57  | 86  | ns    |

### Ordering Instructions

Programming instructions for the DM76L97 or DM86L97 are solicited in the form of a sequenced deck of 32 standard 80-column data cards providing the information requested under data card format, accompanied by a properly sequenced listing of these cards, and the supplementary ordering data. Upon receipt of these items, a computer run will be made from the deck of cards which will produce a complete truth table of the requested part. This truth table, showing output conditions for each of the 256 words, will be forwarded to the purchaser as verification of the input data as interpreted by the computer-automated design (CAD) program. This single run also generates mask and test program data; therefore, verification of the truth table should be completed promptly.

Each card in the data deck prepared by the purchaser identifies the eight words specified and describes the conditions at the four outputs for each of the eight words. All addresses must have all outputs defined and columns designated as "blank" must not be punched. Cards should be punched according to the data card format shown.

# Supplementary Ordering Data

Submit the following information with the data cards:

- a) Customer's name and address

- b) Customer's purchase order number

- c) Customer's drawing number.

## **Data Card Format**

# Column

- 1- 3 Punch a right-justified integer representing the binary input address (000-248) for the first set of outputs described on the card.

- 4 Punch a "-" (Minus sign)

- 5- 7 Punch a right-justified integer representing the binary input address (007-255) for the last set of outputs described on the card.

- 8-9 Blank

- 10-13 Punch "H," "L," or "X" for bits four, three, two, and one (outputs Y4, Y3, Y2, and Y1 in that order) for the first set of outputs specified on the card. (H = high level output, L = low level output, X = don't care.)

- 14 Blank

- 15-18 Punch "H," "L," or "X" for the second set of outputs.

- 19 Blank

- 20-23 Punch "H," "L," or "X" for the third set of outputs.

- 24 Blank

- 25-28 Punch "H," "L," or "X" for the fourth set of outputs.

- 29 Blank

- 30-33 Punch "H," "L," or "X" for the fifth set of outputs.

- 34 Blank

- 35-38 Punch "H," "L," or "X" for the sixth set of outputs.

- 39 Blank

- 40-43 Punch "H," "L," or "X" for the seventh set of outputs.

- 44 Blank

- 45-48 Punch "H," "L," or "X" for the eighth set of outputs.

- 49 Blank

- 50-51 Punch a right-justified integer representing the current calendar day of the month.

- 52 Blank

- 53-55 Punch an alphabetic abbreviation representing the current month.

- 56 Blank

- 57-58 Punch the last two digits of the current year.

- 59 Blank

- 60-61 Punch "DM"

- 62-67 Punch the National Semiconductor part number DM76L97 or DM86L97.

- 68-70 Blank

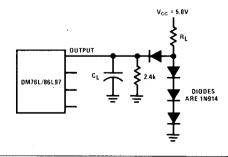

### **AC Test Circuit**