|                                                                                                 |                                                                                                              |                           |            |                          |                                     |                                                  |                  |                       |                                                  | ONS               |                               |                  |                   |                     |                          |              |                   |            |      |    |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------|------------|--------------------------|-------------------------------------|--------------------------------------------------|------------------|-----------------------|--------------------------------------------------|-------------------|-------------------------------|------------------|-------------------|---------------------|--------------------------|--------------|-------------------|------------|------|----|

| LTR                                                                                             | DESCRIPTION DATE (YR-MO-DA) APPROVED  Add device type 02. Technical changes in table 94-09-21 M. L. Poelking |                           |            |                          |                                     |                                                  |                  |                       |                                                  | )                 |                               |                  |                   |                     |                          |              |                   |            |      |    |

| A                                                                                               | Add device type 02. Technical changes in table I. Editorial changes throughout.                              |                           |            |                          |                                     |                                                  |                  | le                    |                                                  | 94-0              | 9-21                          | -                | M.                | L.                  | Poel                     | cing         |                   |            |      |    |

|                                                                                                 |                                                                                                              |                           |            |                          |                                     |                                                  |                  |                       |                                                  |                   |                               |                  |                   |                     |                          |              |                   |            |      |    |

|                                                                                                 |                                                                                                              |                           |            |                          |                                     |                                                  |                  |                       |                                                  |                   |                               |                  |                   |                     |                          |              |                   |            |      |    |

| REV<br>SHEET                                                                                    |                                                                                                              |                           |            |                          |                                     |                                                  |                  |                       |                                                  |                   |                               |                  |                   |                     |                          |              |                   |            |      |    |

| · · · · · · · · · · · · · · · · · · ·                                                           |                                                                                                              |                           |            |                          | A                                   | A                                                | A                | A                     |                                                  |                   |                               |                  |                   |                     |                          |              |                   |            |      |    |

| SHEET                                                                                           | 15<br>US                                                                                                     | 16                        | 17         | 18 RE                    | 19                                  | A 20                                             | A 21 A           | A 22                  | A                                                | A                 | A                             | A                | A                 | A                   | A                        | A            | A                 | A          |      |    |

| SHEET REV SHEET                                                                                 | US                                                                                                           | 16                        | 17         | RE                       | 19                                  | <del>                                     </del> | 21               | 22                    | A 3                                              | A 4               | A 5                           | A 6              | A 7               | A 8                 | A 9                      | A 10         | A 111             | A 12       |      | 14 |

| SHEET REV SHEET REV STAT                                                                        | US<br>S                                                                                                      | 16                        | 17         | RE                       | 19 EV EET                           | 20                                               | 21<br>A<br>1     | 22<br>A<br>2          | <del>                                     </del> | 4                 | 5                             | 6<br>SE EI       | 7<br>ECIR         | 8                   | 9<br>S SU                | 10<br>PPLY   | 11<br>CEN         | 12         | 2 13 | 14 |

| SHEET REV SHEET REV STATOF SHEET PMIC N/A STA                                                   | US<br>S<br>NDAR                                                                                              | RD                        |            | RE<br>SH<br>PREP         | 19  VETT  PARED B Chri              | 20<br>SY<br>stophe                               | 21<br>A<br>1     | A 2                   | <del>                                     </del> | 4                 | 5                             | 6<br>SE EI       | 7<br>ECIR         | 8                   | 9                        | 10<br>PPLY   | 11<br>CEN         | 12         | 2 13 | 14 |

| SHEET REV SHEET REV STATOF SHEET PMIC N/A STA                                                   | US<br>S<br>NDAR<br>CIRC<br>AWING                                                                             | RD<br>CUIT<br>G<br>VAILAE | BLE        | RE<br>SH<br>PREP         | 19 EV PARED B Chri CKED BY Will     | 20<br>3Y<br>stophe                               | 21 A 1 C. Heck   | 22<br>A<br>2<br>Rauch | <del>                                     </del> | MIC 16-           | 5<br>EFENS                    | GE EL            | 7<br>ECIR<br>AYTO | 8<br>SONIC<br>SN, C | 9<br>S SU<br>HIO<br>GITA | PPLY 454     | CEN<br>44         | TER        | 2 13 |    |

| SHEET  REV SHEET  REV STATE OF SHEET  PMIC N/A  STA MICRO DRAWIN FOR USE BY                     | US<br>S<br>NDAR<br>CIRC<br>AWING                                                                             | RD<br>CUIT<br>G<br>VAILAB | SLE<br>NTS | SH<br>PREP<br>CHEC       | 19 EV PARED B Chri CKED BY Will     | 20  SY stophe  (liam k                           | 21 A 1 C. Heck   | 22<br>A<br>2<br>Rauch | <del>                                     </del> | MIC<br>16-<br>SII | EFENS<br>CROC<br>-BIT<br>LICO | 6 SE EI CIRCUMIC | 7 ECIR AYTO       | 8 SONICE ONT        | 9<br>S SU<br>HIO<br>GITA | PPLY<br>454. | CEN<br>44<br>CHMC | TER<br>OS, | 2 13 | I  |

| SHEET  REV SHEET  REV STAT  OF SHEET  PMIC N/A  STA  MICRO DRA  THIS DRAWIN FOR USE BY AND AGEN | US<br>S<br>NDAR<br>CIRC<br>AWING<br>IG IS A<br>ALL DEF                                                       | RD<br>CUIT<br>G<br>VAILAB | SLE<br>NTS | RE<br>SH<br>PREP<br>CHEC | 19 EV HEET CARED B Chri KED BY Will | 20<br>Stophe<br>(liam k                          | 21 A 1 A C. Heck | 22<br>A<br>2<br>Rauch | <del>                                     </del> | MIC 16-           | EFENS<br>CROC<br>-BIT<br>LICO | 6 SE EI CIRCUMIC | 7<br>ECIR<br>AYTO | B SONICE ONT        | 9<br>S SU<br>HIO<br>GITA | PPLY<br>454. | CEN<br>44         | TER<br>OS, | 2 13 | I  |

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

5962-E288-94

**■** 9004708 0003903 120 **■**

## 1. SCOPE

- 1.1 <u>Scope</u>. This drawing describes device requirements for class B microcircuits in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices".

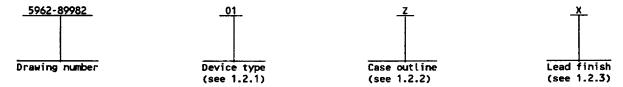

- 1.2 Part or Identifying Number (PIN). The complete PIN shall be as shown in the following example:

1.2.1 <u>Device type(s)</u>. The device type(s) shall identify the circuit function as follows:

| Device type | Generic number | <u>Circuit function</u>             |  |  |

|-------------|----------------|-------------------------------------|--|--|

| 01          | 80C196KB       | 12 MHz CHMOS 16-bit microcontroller |  |  |

| 02          | 80C196KB-12    | 12 MHz CHMOS 16-bit microcontroller |  |  |

1.2.2 <u>Case outline(s)</u>. The case outline(s) shall be as designated in MIL-STD-1835 and as follows:

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style               |

|----------------|------------------------|------------------|-----------------------------|

| Z              | CMGA3~P68              | 68               | pin grid array package      |

| Y              | see figure 1           | 68               | leaded chip carrier package |

1.2.3 <u>Lead finish</u>. The lead finish shall be as specified in MIL-STD-883 (see 3.1 herein). Finish letter "X" shall not be marked on the microcircuit or its packaging. The "X" designation is for use in specifications when lead finishes A, B, and C are considered acceptable and interchangeable without preference.

1.3 Absolute maximum ratings.

| Supply voltage range (V <sub>CC</sub> )                                | 4.5 V dc to 5.5 V dc |

|------------------------------------------------------------------------|----------------------|

| Voltage on any pin with respect to ground                              | -0.5 V to +7.0 V     |

| Storage temperature range                                              | -65°C to +150°C      |

| Case operating temperature range (T <sub>C</sub> )                     | -55°C to +125°C      |

| Case operating temperature range ( $T_C$ ) Power dissipation ( $P_D$ ) | 1.5 W <u>1</u> /     |

| Lead temperature (soldering 10 seconds)                                | 265°C                |

| Junction temperature (T <sub>j</sub> )                                 | 150°C                |

| Thermal resistance, junction-to-case (0 <sub>10</sub> ):               | See MIL-STD-1835     |

1.4 Recommended operating conditions.

| Case operating temperature range ( $I_c$ ) | -55°C to +125°C <u>2</u> / |

|--------------------------------------------|----------------------------|

| Supply voltage range (V <sub>CC</sub> )    | 4.5 V dc to 5.5 V dc       |

| Digital circuit ground (V <sub>CC</sub> )  | 0.0 V dc                   |

| Analog supply voltage (Vpc)                | 4.5 V dc to 5.5 V dc       |

| Analog supply voltage (V <sub>REF</sub> )  | 3.5 to 12 MHz              |

| High level input voltage:                  |                            |

| Excluding XTAL1, RESET (V,u)               | 1.9 V dc to 6.0 V dc       |

| XTAL1 (V <sub>141</sub> ) <sup>10</sup>    | 3.15 V dc to 6.0 V dc      |

| RESET (V <sub>102</sub> )                  | 2.2 V dc to 6.0 V dc       |

| Excluding XTAL1, RESET (V <sub>IH</sub> )  | -0.5 V dc to 0.8 V dc      |

- 1/ Must withstand the added PD due to short circuit test; e.g., IOS.

- 2/ Case temperatures are "instant on".

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-89982 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444            |           | REVISION LEVEL<br>A | SHEET 2    |

DESC FORM 193A JUL 94

■ 9004708 0003904 067 **■**

### 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and bulletin</u>. Unless otherwise specified, the following specification, standards, and bulletin of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

### **SPECIFICATION**

MILITARY

MIL-I-38535 - Integrated Circuits (Microcircuits) Manufacturing, General Specification for.

#### **STANDARDS**

MILITARY

MIL-STD-883 - Test Methods and Procedures for Nicroelectronics.

MIL-STD-1835 - Microcircuit Case Outlines.

### BULLETIN

MILITARY

MIL-BUL-103 - List of Standard Microcircuit Drawings (SMD's).

(Copies of the specification, standards, and bulletin required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

2.2 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

#### 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein. Product built to this drawing that is produced by a Qualified Manufacturer Listing (QML) certified and qualified manufacturer or a manufacturer who has been granted transitional certification to MIL-I-38535 may be processed as QML product in accordance with the manufacturers approved program plan and qualifying activity approval in accordance with MIL-I-38535. This QML flow as documented in the Quality Management (QM) plan may make modifications to the requirements herein. These modifications shall not affect form, fit, or function of the device. These modifications shall not affect the PIN as described herein. A "Q" or "QML" certification mark in accordance with MIL-I-38535 is required to identify when the QML flow option is used.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-STD-883 (see 3.1 herein) and herein.

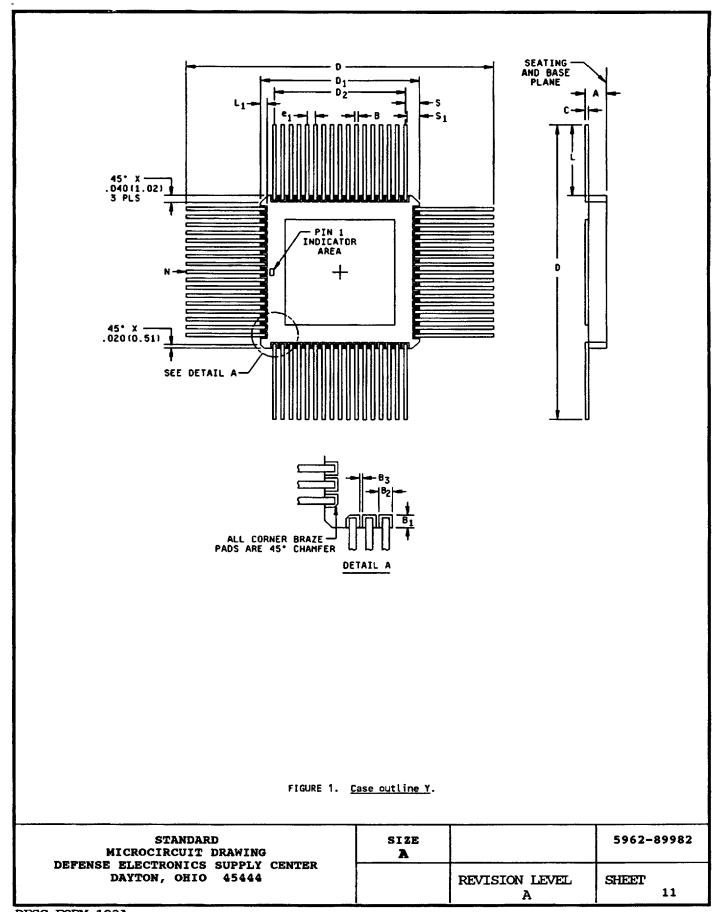

- 3.2.1 Case outline(s). The case outline(s) shall be in accordance with 1.2.2 herein and figure 1 herein.

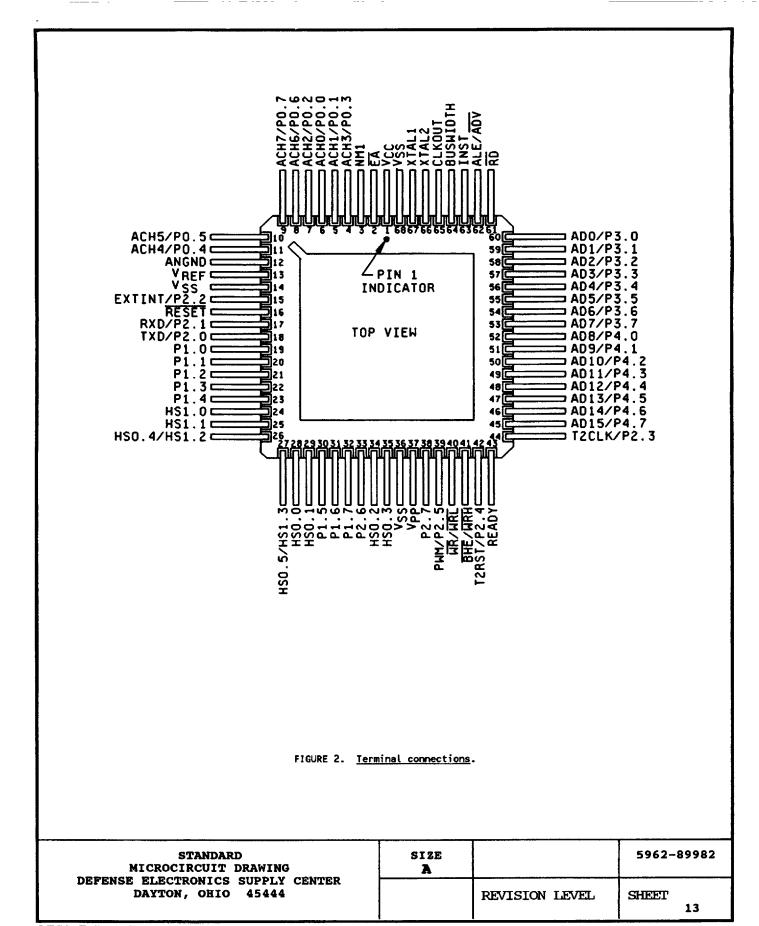

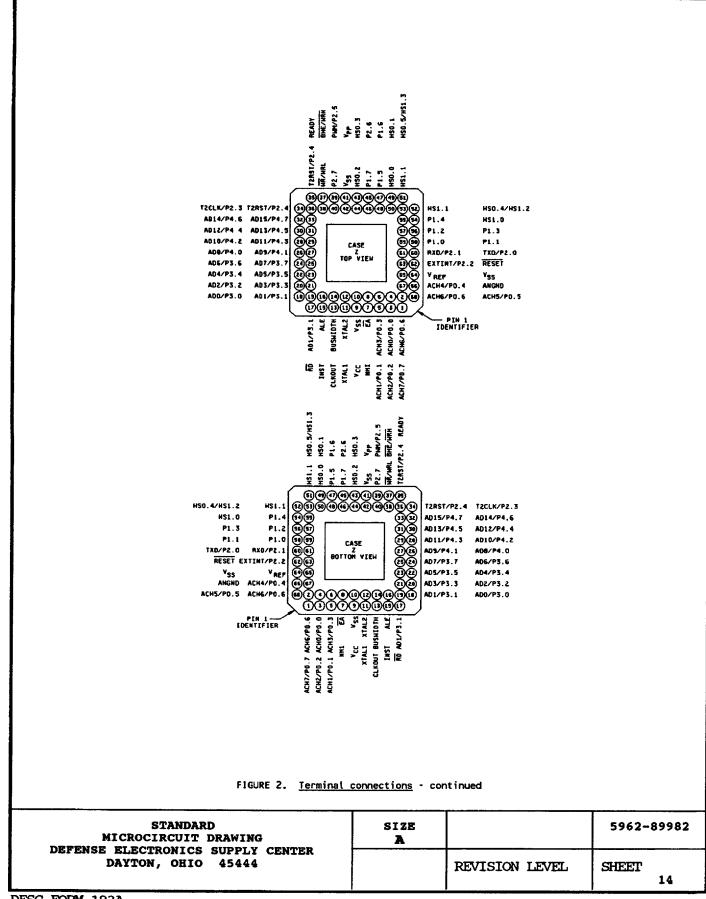

- 3.2.2 <u>Terminal connections</u>. The terminal connections shall be as specified on figure 2.

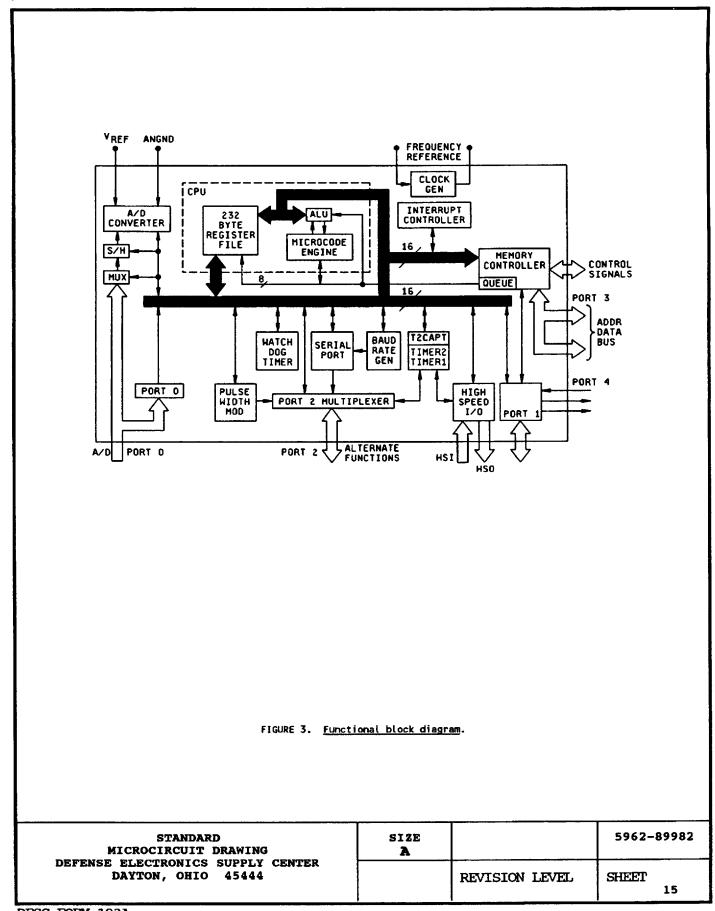

- 3.2.3 Functional block diagram. The functional block diagram shall be as specified on figure 3.

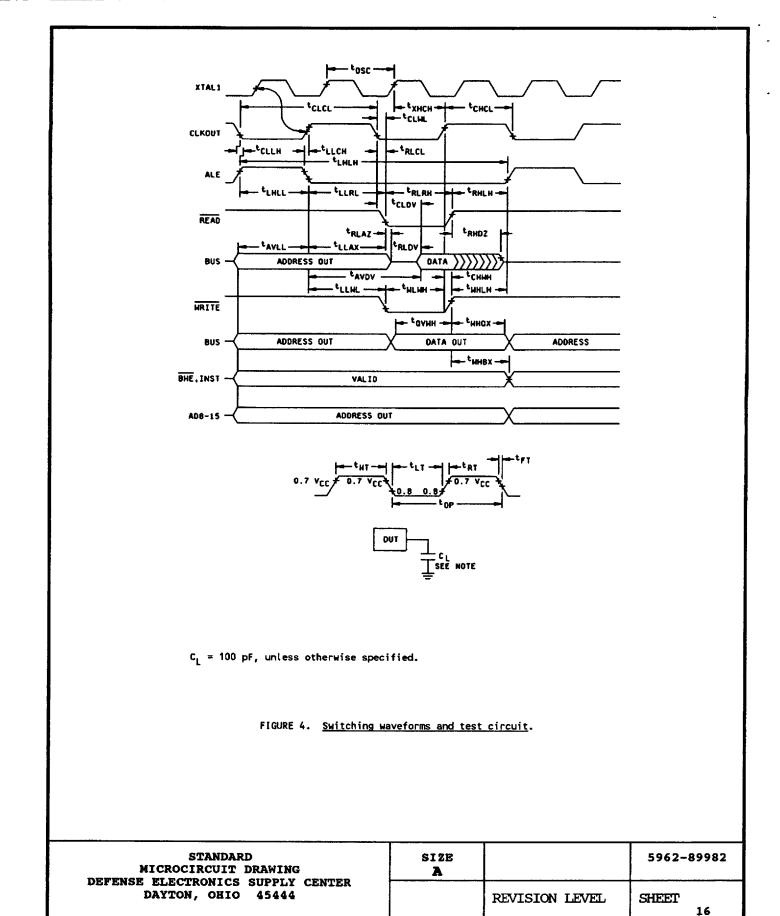

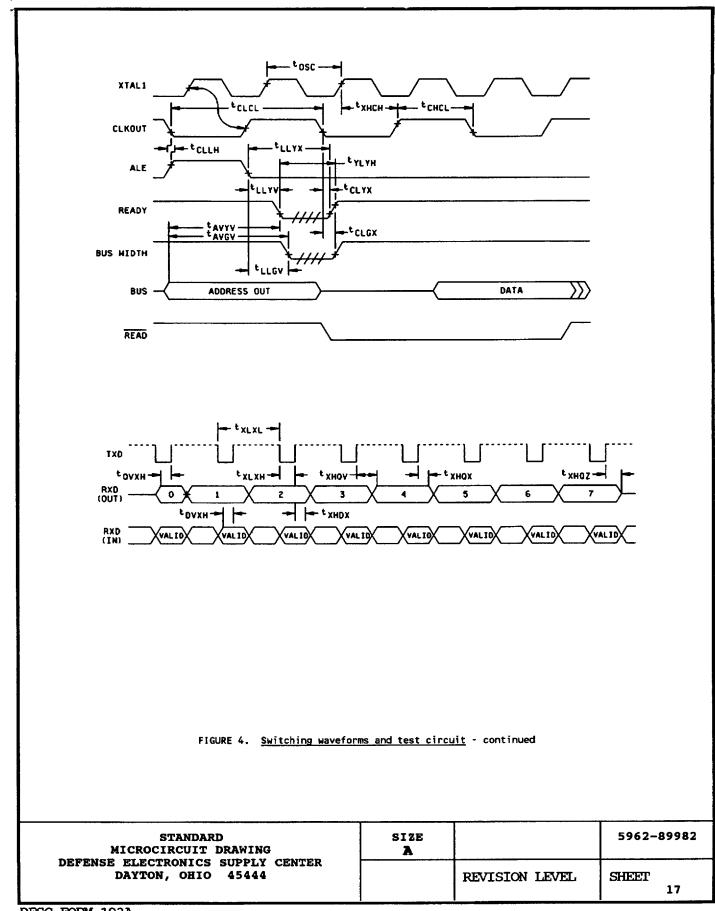

- 3.2.4 <u>Switching waveforms and test circuit</u>. The switching waveforms and test circuit shall be as specified on figure 4.

- 3.3 <u>Electrical performance characteristics</u>. Unless otherwise specified herein, the electrical performance characteristics are as specified in table I and shall apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are described in table I.

| STANDARD<br>MICROCIRCUIT DRAWING                     | SIZE<br>A |                     | 5962-89982 |

|------------------------------------------------------|-----------|---------------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL<br>A | SHEET<br>3 |

DESC FORM 193A JUL 94

🖚 9004708 0003905 TT3 🗯

TABLE I. Electrical performance characteristics.

| Test                                                        | Symbol           | Conditions<br>-55°C ≤ T <sub>C</sub> ≤ +125°C <u>1</u> /                         | Group A<br>subgroups | Device<br>type | Lim                                                                  | Units                |    |

|-------------------------------------------------------------|------------------|----------------------------------------------------------------------------------|----------------------|----------------|----------------------------------------------------------------------|----------------------|----|

|                                                             |                  | V <sub>CC</sub> = 5.0 V ±10%<br>unless otherwise specified                       | 04031 VAP            | -/             | Min                                                                  | Max                  |    |

| Input low voltage                                           | v <sub>IL</sub>  |                                                                                  | 1, 2, 3              | All            | -0.5                                                                 | 0.8                  | v  |

| Input high voltage<br>(all except RESET<br>and XTAL1)       | A <sup>I H</sup> | 1                                                                                |                      | 01             | 0.2V <sub>CC</sub><br>+1.0                                           | v <sub>cc</sub> +0.5 | v  |

|                                                             |                  | 1                                                                                |                      | 02             | 0.2V <sub>CC</sub><br>+1.1                                           | v <sub>cc</sub> +0.5 |    |

| Input high voltage<br>XTAL1                                 | V <sub>IH1</sub> | 1                                                                                |                      | All            | 0.7 V <sub>CC</sub>                                                  | v <sub>cc</sub> +0.5 | v  |

| Input high voltage<br>on RESET                              | V <sub>1H2</sub> | 1                                                                                |                      | All            | 2.2                                                                  | v <sub>cc</sub> +0.5 | ٧  |

| Output low voltage                                          | v <sub>OL</sub>  | I <sub>OL</sub> = 200 μA<br>I <sub>OL</sub> = 3.2 mA<br>I <sub>OL</sub> = 7.0 mA |                      | All            |                                                                      | 0.3<br>0.45<br>1.5   | V  |

| Output high voltage<br>(standard outputs)                   | УОН              | IOH = -200 #A<br>IOH = -3.2 mA<br>IOH = -7.0 mA                                  |                      | ALL            | V <sub>CC</sub> 0.3<br>V <sub>CC</sub> 0.7<br>V <sub>CC</sub> 1.5    |                      | v  |

| Output high voltage<br>(quasi-<br>bidirectional<br>outputs) | V <sub>OH1</sub> | 1 <sub>OH</sub> = -10 μA<br>I <sub>OH</sub> = -30 μA<br>I <sub>OH</sub> = -60 μA |                      | All            | V <sub>CC</sub> -0.3<br>V <sub>CC</sub> -0.7<br>V <sub>CC</sub> -1.5 |                      | v  |

| Input leakage<br>current (standard<br>inputs)               | ILI              | 0.0 ≤ V <sub>IN</sub> ≤ V <sub>CC</sub> -0.3 V                                   |                      | ALL            |                                                                      | ±10                  | μА |

| Input leakage<br>current (port 0)                           | I <sub>LI1</sub> | 0.0 ≤ V <sub>IN</sub> ≤ V <sub>REF</sub>                                         |                      | ALL            |                                                                      | ±3                   |    |

| 1 to 0 transition<br>current (QBD)<br>pins                  | I <sub>TL</sub>  | V <sub>IN</sub> = 2.0 V                                                          |                      | 01<br>02       |                                                                      | -650<br>-800         |    |

| Logical O input<br>current (QBD) pins                       | IIL              | V <sub>IN</sub> = 0.45 V                                                         |                      | ALL            |                                                                      | -50                  |    |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING                     | SIZE<br>A |                     | 5962-89982 |

|------------------------------------------------------|-----------|---------------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL<br>A | SHEET<br>4 |

DESC FORM 193A JUL 94

■ 9004708 000390L 93T ■

| TARIF | ١.  | Electrical  | nerformence  | characteristics  | continued |

|-------|-----|-------------|--------------|------------------|-----------|

| IABCE | 4 - | Electificat | Del Tormance | Characteristics. | continued |

| Test                                                      | Symbol            | Conditions -55°C ≤ T <sub>C</sub> ≤ +125°C <u>1</u> / V <sub>CC</sub> = 5.0 V ±10% unless otherwise specified | Group A<br>subgroups | Device<br>type | Limits  |                       | Units    |

|-----------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------|----------------------|----------------|---------|-----------------------|----------|

|                                                           |                   |                                                                                                               | subgroups            |                | Hin     | Max                   |          |

| Logical O input<br>current in RESET<br>(ALE, RD, WR, BHE, | I <sub>IL1</sub>  | V <sub>IN</sub> = 0.45 2/                                                                                     | 1, 2, 3              | 01             |         | -850                  | mA.      |

| INST, P2.0                                                |                   |                                                                                                               | 1                    | 02             | !       | -7                    | <u> </u> |

| Active mode current<br>RESET                              | <sup>1</sup> cc   | XTAL1 = 12MHz<br>V <sub>CC</sub> = V <sub>PP</sub> = V <sub>REF</sub> = 5.5 V                                 |                      | ALL            |         | 60                    | mA       |

| I/D converter<br>reference current                        | IREF              |                                                                                                               |                      | All            |         | 5                     |          |

| dle mode current                                          | IDLE              | XTAL1 = 12 MHz                                                                                                |                      | 01             |         | 22                    |          |

|                                                           |                   | V <sub>CC</sub> = V <sub>PP</sub> = V <sub>REF</sub> = 5.5 V                                                  | 1                    | 02             |         | 25                    |          |

| Active mode current                                       | I <sub>CC1</sub>  | XTAL1 = 3.5 MHz                                                                                               | 1                    | 01             |         | 22                    |          |

|                                                           | <u> </u>          |                                                                                                               | 1                    | 02             |         | 30                    | <u> </u> |

| Power down mode<br>current                                | I <sub>PD</sub>   | XTAL1 = 12MHz<br>V <sub>CC</sub> = V <sub>PP</sub> = V <sub>REF</sub> = 5.5 V                                 |                      | All            |         | 50                    | μА       |

| Reset pull-up<br>resistor                                 | R <sub>RST</sub>  |                                                                                                               | 4, 5, 6              | All            | 6K      | 50K                   | Ω        |

| Pin capacitance<br>(any pin to V <sub>SS</sub> )          | cs                | fIEST = 1.0 MHz<br>see 4.3.1c                                                                                 | 4                    | ALL            |         | 10                    | pí       |

| Address valid to<br>READY setup                           | †AVYV             | Capacitance load on all<br>pins = 100 pF, rise and                                                            | 9, 10, 11            | ALL            |         | 2t <sub>OSC</sub> -85 | ns       |

| ALE low to READY<br>setup                                 | <sup>t</sup> LLYV | fall time = 10 ns,<br>f <sub>OSC</sub> = 12 MHz,<br>see figure 4                                              |                      | All            |         | t <sub>osc</sub> -75  |          |

| Non READY time                                            | <sup>t</sup> YLYH |                                                                                                               |                      | ALL            | No uppe | er limit              |          |

| READY hold after<br>CLKOUT low                            | <sup>t</sup> CYLX |                                                                                                               |                      | ALL            | 0       | tosc-30               |          |

| READY hold efter<br>ALE low                               | t <sub>LLYX</sub> |                                                                                                               | 1                    | ALL            | tosc-15 | 2t <sub>osc</sub> -40 |          |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING                     | SIZE<br>A |                     | 5962-89982 |

|------------------------------------------------------|-----------|---------------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL<br>A | SHEET<br>5 |

DESC FORM 193A JUL 94

■ 9004708 0003907 876 **■**

| Test                                        | Symbol            | Conditions -55°C ≤ T <sub>E</sub> ≤ +125°C <u>1</u> / V <sub>CC</sub> = 5.0 V ±10% unless otherwise specified | Group A<br>subgroups | Device<br>type | Li      | mits                  | Units |     |

|---------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------|----------------------|----------------|---------|-----------------------|-------|-----|

|                                             |                   |                                                                                                               |                      |                | Min     | Max                   |       |     |

| Address valid to<br>BUS WIDTH setup         | <sup>t</sup> AVGV | Capacitive load on all<br>pins = 100 pF, rise and                                                             | 9, 10, 11            | All            |         | 2t <sub>osc</sub> -85 | ns    |     |

| ALE low to BUS<br>WIDTH setup               | <sup>t</sup> LLGV | fall time = 10 ns,<br>f <sub>OSC</sub> = 12 MHz,<br>see figure 4                                              |                      | ALL            |         | tosc <sup>-70</sup>   | ns    |     |

| BUS WIDTH hold<br>after CLKOUT low          | t <sub>CLGX</sub> |                                                                                                               |                      | All            | 0       |                       | ns    |     |

| Address valid to input data valid           | <sup>t</sup> AVDV |                                                                                                               |                      | ALL            |         | 3t <sub>OSC</sub> -67 | ns    |     |

| ND active to input<br>data valid            | t <sub>RLDV</sub> |                                                                                                               |                      | All            |         | t <sub>osc</sub> -23  | ns    |     |

| CLKOUT low to input<br>data valid           | <sup>t</sup> CLDV |                                                                                                               |                      | All            |         | t <sub>osc</sub> -50  | ns    |     |

| ind of RD to input<br>data float            | <sup>t</sup> RHDZ |                                                                                                               |                      | ALL            |         | t <sub>OSC</sub> -20  | ns    |     |

| ata hold after RD<br>inactive               | <sup>t</sup> RXDX |                                                                                                               |                      | ALL            | 0       |                       | ns    |     |

| requency on XTAL1                           | fXTAL             |                                                                                                               |                      | All            | 3.5     | 12                    | MHz   |     |

| I/f <sub>XTAL</sub>                         | <sup>t</sup> osc  |                                                                                                               |                      | ALL            | 83      | 286                   | ns    |     |

| (TAL1 high to CLKOUT high or low <u>3</u> / | txHCH             |                                                                                                               |                      |                |         | 01                    | 35    | 110 |

|                                             |                   |                                                                                                               |                      | 02             | 20      | 110                   |       |     |

| CLKOUT cycle time                           | <sup>t</sup> CLCL |                                                                                                               |                      | All            | 2t      | osc                   |       |     |

| CLKOUT high period                          | t <sub>CHCL</sub> |                                                                                                               |                      |                | tosc-10 | t <sub>osc</sub> +10  |       |     |

STANDARD

MICROCIRCUIT DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

REVISION LEVEL SHEET

A

DESC FORM 193A JUL 94

■ 9004708 0003908 702 **■**

|                                                      | TABLE                      | E I. <u>Electrical performance ch</u>                      | naracteristics       | contin         | ued                  |                     |         |

|------------------------------------------------------|----------------------------|------------------------------------------------------------|----------------------|----------------|----------------------|---------------------|---------|

| Test                                                 | Symbol                     | Conditions<br> -55°C ≤ T <sub>C</sub> ≤ +125°C <u>1</u> /  | Group A<br>subgroups | Device<br>type | Lim                  | Limits              |         |

|                                                      |                            | V <sub>CC</sub> = 5.0 V ±10%<br>unless otherwise specified | oudgi vapo           | 175-           | Min                  | Max                 |         |

| CLKOUT falling edge<br>to ALE rising                 | <sup>t</sup> CLLH          | Capacitive load on all pins = 100 pF, rise and             | 9, 10, 11            | 01             | -5                   | 15                  | ns      |

| -                                                    | <b></b>                    | fall time = 10 ns.                                         | 1                    | 02             | -10                  | 10                  | Щ       |

| ALE high period                                      | tLHLL                      | f <sub>OSC</sub> = 12 MHz<br>See figure 4                  |                      | ALL            | tosc-12              | tosc+12             | ns      |

| Address setup to ALE<br>falling edge                 | <sup>t</sup> AVLL          |                                                            |                      | All            | tosc-20              |                     | ns      |

| Address hold after<br>ALE falling edge               | <sup>t</sup> LLAX          |                                                            |                      | ALL            | tosc <sup>-40</sup>  |                     | ns      |

| ALE falling edge to<br>RD falling edge               | <sup>t</sup> LLRL          |                                                            |                      | All            | t <sub>osc</sub> -40 |                     | ns      |

| RD low to CLKOUT<br>falling edge                     | <sup>t</sup> rlcl          |                                                            | •                    | 01             | 5                    | 30                  | ns      |

|                                                      | <b></b>                    | 4 !                                                        | '                    | 02             | 4                    | 25                  | <b></b> |

| ALE falling edge to<br>CLKOUT rising                 | <sup>t</sup> llch          |                                                            | 1                    | ALL            | -15                  | 15                  | ns      |

| ALE cycle time <u>4</u> /                            | <sup>t</sup> LHLH          |                                                            |                      | ALL            | 4t <sub>0</sub>      | esc                 | ns      |

| RD low period                                        | t <sub>rlrh</sub>          |                                                            | ,                    | All            | tosc-5               |                     |         |

| RD rising edge to<br>rising edge <u>5</u> /          | <sup>t</sup> RHLH          |                                                            | !                    | All            | <sup>t</sup> osc     | tosc <sup>+25</sup> |         |

| RD low to address<br>float                           | <sup>t</sup> rlaz          |                                                            |                      | All            |                      | 10                  |         |

| ALE falling edge to<br>WR falling edge               | <sup>t</sup> LL <b>V</b> L |                                                            | :                    | All            | tosc <sup>-10</sup>  |                     |         |

| CLKOUT low to WR falling edge ee footnotes at end of | <sup>t</sup> CLWL          |                                                            |                      | ALL            | 0                    | 25                  |         |

|                            | <del></del> |

|----------------------------|-------------|

| STANDARD                   |             |

| MICROCIRCUIT DRAWING       |             |

| DEFENSE ELECTRONICS SUPPLY |             |

|                            | CENTER      |

| DAYTON, OHIO 45444         |             |

| SIZE<br><b>A</b> |                     | 5962-89982 |

|------------------|---------------------|------------|

|                  | REVISION LEVEL<br>A | SHEET 7    |

**■** 9004708 0003909 649 **■**

| TARIE I | Flectrical | performance | characteristics | continued |

|---------|------------|-------------|-----------------|-----------|

|         |            |             |                 |           |

| Test                                                                            | Symbol              |                                                                  | Group A<br>subgroups | Device<br>type |                       |                      | Units |  |    |  |

|---------------------------------------------------------------------------------|---------------------|------------------------------------------------------------------|----------------------|----------------|-----------------------|----------------------|-------|--|----|--|

|                                                                                 |                     |                                                                  | Sasar Sapa           | 1,000          | Min                   | Max                  |       |  |    |  |

| Data stable to WR<br>rising edge                                                | <sup>t</sup> qvwH   | Capacitance load on all pins = 100 pF, rise and                  | 9, 10, 11            | ALL            | t <sub>osc</sub> -23  |                      | ns    |  |    |  |

| Data hold after WR<br>rising edge                                               | t <sub>wHex</sub>   | fall time = 10 ns,<br>f <sub>OSC</sub> = 12 MHz,<br>see figure 4 |                      | 01             | t <sub>osc</sub> -10  |                      | ns    |  |    |  |

| Traing eage                                                                     |                     | see Tigure 4                                                     |                      | 02             | tosc <sup>-15</sup>   |                      |       |  |    |  |

| WR rising edge to<br>ALE rising edge                                            | twhLH               |                                                                  |                      | 01             | tosc-10               | tosc <sup>+15</sup>  | ns    |  |    |  |

| 5/                                                                              |                     |                                                                  |                      | 02             | t <sub>osc</sub> -15  | t <sub>osc</sub> +10 |       |  |    |  |

| BHE, INST holg after                                                            | t <sub>WHBX</sub>   |                                                                  |                      | 01             | t <sub>osc</sub> -10  |                      | ns    |  |    |  |

| WR rising edge                                                                  |                     |                                                                  |                      | 02             | 02                    | t <sub>osc</sub> -15 |       |  |    |  |

| Oscillator frequency                                                            | 1/t <sub>XLXL</sub> |                                                                  |                      | ALL            | 3.5                   | 12.0                 | MHz   |  |    |  |

| CLKOUT high to WR<br>rising edge                                                | t <sub>CHWH</sub>   |                                                                  |                      | 01             | -10                   | 10                   | ns    |  |    |  |

|                                                                                 |                     |                                                                  |                      |                | -5                    | 15                   | +     |  |    |  |

| WR low period                                                                   | <sup>t</sup> wlwH   |                                                                  |                      |                | t <sub>osc</sub> -30  |                      | ns    |  |    |  |

| Oscillator period                                                               | top                 |                                                                  |                      | All            | 83                    | 286                  | ns    |  |    |  |

| High time                                                                       | t <sub>HT</sub>     |                                                                  |                      | ALL            | 32                    |                      |       |  |    |  |

| Low time                                                                        | t <sub>i T</sub>    |                                                                  |                      | All            | 32                    |                      |       |  |    |  |

| Rise time                                                                       | t <sub>RT</sub>     |                                                                  |                      | ALL            |                       | 10                   |       |  |    |  |

| Fall time                                                                       | t <sub>FT</sub>     |                                                                  |                      |                |                       | A                    | All   |  | 10 |  |

| Serial port clock<br>period (BRR ≥<br>8002H) <u>3</u> /                         | <sup>t</sup> XLXL   |                                                                  |                      | All            | <sup>6t</sup> osc     |                      |       |  |    |  |

| Serial port clock<br>falling edge to<br>rising edge<br>(BRR ≥ 8002H) <u>3</u> / | <sup>t</sup> xLXH   |                                                                  |                      | All            | 4t <sub>osc</sub> ±50 |                      |       |  |    |  |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING                     | SIZE<br>A |                     | 5962-89982 |

|------------------------------------------------------|-----------|---------------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL<br>A | SHEET<br>8 |

DESC FORM 193A JUL 94

**=** 9004708 0003910 360 =

| Test                                                             | Symbol            | Conditions<br>-55°C ≤ T <sub>C</sub> ≤ +125°C <u>1</u> /                                                   | Group A   | Device | Lim                   | its                              | Units         |

|------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------|-----------|--------|-----------------------|----------------------------------|---------------|

|                                                                  |                   | V <sub>CC</sub> = 5.0 V ±10%<br>unless otherwise specified                                                 | subgroups | type   | Min                   | Max                              |               |

| Output data setup to<br>clock rising edge<br>3/                  | <sup>t</sup> QVXH | Capacitive load on all pins = 100 pF, rise and fall time = 10 ns. f <sub>OSC</sub> = 12 MHz, See figure 4. | 9, 10, 11 | All    | 2t <sub>0SC</sub> -50 |                                  | ns            |

| Output data hold<br>after clock rising<br>edge <u>3</u> /        | t <sub>XHQX</sub> |                                                                                                            |           | All    | 2t <sub>0SC</sub> -50 |                                  |               |

| Mext output data valid after clock rising edge <u>3</u> /        | <sup>t</sup> xHQV |                                                                                                            |           | All    |                       | <sup>2t</sup> 0SC <sup>+50</sup> |               |

| Serial port clock<br>period (BRR =<br>8001H) <u>3</u> /          | <sup>t</sup> XLXL |                                                                                                            |           | A11    | <sup>4t</sup> osc     |                                  |               |

| Serial port clock<br>falling edge to<br>(BRR = 8001H) <u>3</u> / | <sup>t</sup> xlxH |                                                                                                            |           | All    | 2t <sub>OSC</sub> ±50 |                                  |               |

| Input data setup<br>to clock rising<br>edge <u>3</u> /           | <sup>t</sup> ovxh |                                                                                                            |           | All    | t <sub>OSC</sub> +50  |                                  |               |

| Input data hold<br>after clock rising<br>edge <u>3</u> /         | <sup>t</sup> xHDX |                                                                                                            |           | All    | 0                     |                                  |               |

| Last clock rising to output float 3/                             | <sup>t</sup> xHQZ |                                                                                                            |           | All    |                       | <sup>t</sup> osc                 |               |

| Resolution                                                       |                   | Clock prescaler on mode 2 Ver = 5.120 V, XTAL1 = 12 MHz                                                    | 1, 2, 3   | All    | 256                   | 1024<br>10                       | level<br>bits |

| Absolute error                                                   |                   |                                                                                                            | ]         | All    | 0                     | ±4                               | LSBs          |

| Non-linearity                                                    |                   | 7                                                                                                          |           | All    | 0                     | ±4                               |               |

| See | footnotes | at | end | of | table. |  |

|-----|-----------|----|-----|----|--------|--|

| STANDARD MICROCIRCUIT DRAWING                        | SIZE<br>A |                | 5962-89982 |

|------------------------------------------------------|-----------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>9 |

■ 775 11PE000 807+00P

| TABLE | I. | Electrical | performance | characteristics | continued |

|-------|----|------------|-------------|-----------------|-----------|

|       |    |            |             |                 |           |

| Test                                | Symbol | Conditions<br>-55°C ≤ T <sub>C</sub> ≤ +125°C <u>1</u> / | Group A<br>subgroups | Device<br>type | Limits |      | Units |

|-------------------------------------|--------|----------------------------------------------------------|----------------------|----------------|--------|------|-------|

|                                     |        | V <sub>CC</sub> = 5.0 V ±10% unless otherwise specified  |                      |                | Min    | Max  |       |

| Differential non-linearity          |        |                                                          | 1, 2, 3              | All            | 0      | ±2   | LSBs  |

| Channel to channel matching         |        |                                                          |                      | ALL            | 0      | ±1   | LSBs  |

| Off isolation <u>3</u> / <u>6</u> / |        |                                                          | 4, 5, 6              | ALL            | -60    |      | dß    |

| Input resistance 3/                 |        |                                                          |                      | 01             | 1K     | 5K   | Ω     |

|                                     |        |                                                          | ·                    | 02             | 750    | 1.2K |       |

| DC input leakage                    |        |                                                          | 1, 2, 3              | All            | 0      | 3.0  | μА    |

1/ The following pins are active low: RESET, EA, ADV of ALE/ADV, RD WR/WRL, and BHE/WRH. Case temperatures are instant on. QBD\_(quasi-bidirectional pins) include port 1, P2.6 and P2.7. Standard outputs include ADO-15, RD, WR, ALE, BHE, INST, HSO pins, PWM/P2.5, CLKOUT, RESET, ports 3 and 4, TXD/P2.0, and RXD (in serial mode 0). The V<sub>OH</sub> specifications is not valid for RESET. Ports 3 and 4 are open drain outputs. Standard inputs include HSI pins, EA, READY, BUS WIDTH, NMI, RXD/P2.1, EXTINT/P2.2, T2CLK/P2.3 and T2RSTP2.4. Maximum current per pin must be externally limited to the following values if V<sub>OL</sub> is held above 0.45 V or V<sub>OH</sub> is held below

V<sub>CC</sub> -0.7 V:

I<sub>OH</sub> on output pins: 10 mA.

I<sub>OH</sub> on quasi-bidirectional pins: Self limiting.

I<sub>OH</sub> on standard output pins: 10 mA.

Maximum current per bus pin (data and control) during normal operation is ±3.2 mA.

During normal (non-transient) conditions, the following total current limits apply:

- $\underline{2}$ / Holding these pins below  $V_{ ext{IH}}$  in RESET may cause the part to enter test modes.

- 3/ Guaranteed if not tested, to the limits specified in table 1.

- 4/ CLKOUT is directly generated as a divide by 2 of the oscillator, ALE is directly generated as a divde by 4 of the oscillator.

- 5/ Assuming back-to-back bus cycles.

- 6/ DC to 100 KHz. Multiplexer break-before-make guaranteed.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br><b>A</b> |                     | 5962-89982  |

|-----------------------------------------------------------------|------------------|---------------------|-------------|

| DAYTON, OHIO 45444                                              |                  | REVISION LEVEL<br>A | SHEET<br>10 |

DESC FORM 193A JUL 94

9004708 0003912 133 📟

**7004708 0003913 07T**

|                | Dimensions |         |        |       |  |  |

|----------------|------------|---------|--------|-------|--|--|

|                |            | imeters | Inches |       |  |  |

| Symbol         | Min        | Max     | Min    | Max   |  |  |

| A              | 2.03       | 2.69    | .080   | .106  |  |  |

| В              | 0.41       | 0.51    | .016   | .020  |  |  |

| B <sub>1</sub> | 1.02       | 1.52    | .040   | .060  |  |  |

| B <sub>2</sub> | 0.76       | 1.02    | .030   | .040  |  |  |

| B <sub>3</sub> | 0.13       | 0.51    | .005   | .020  |  |  |

| С              | 0.20       | 0.31    | .008   | .012  |  |  |

| D              | 41.66      | 47.50   | 1.640  | 1.870 |  |  |

| D              | 23.75      | 24.64   | .935   | .970  |  |  |

| D <sub>2</sub> | 20.3       | 2 BSC   | .800   | BSC   |  |  |

| e1             | 1.2        | 7 BSC   | .050   | BSC   |  |  |

| L              | 9.52       | 11.43   | .375   | .450  |  |  |

| L <sub>1</sub> | 1.02       | 1.52    | .040   | .060  |  |  |

| N              | 68         |         | 6      | 8     |  |  |

| s              | 1.68       | 2.21    | .066   | .087  |  |  |

| S <sub>1</sub> | 1.27       |         | .050   |       |  |  |

## NOTES:

FIGURE 1. Case outline Y - continued

| STANDARD<br>MICROCIRCUIT DRAWING<br>DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-89982  |

|-----------------------------------------------------------------------|-----------|---------------------|-------------|

| DAYTON, OHIO 45444                                                    | _         | REVISION LEVEL<br>A | SHEET<br>12 |

DESC FORM 193A JUL 94

🖿 9004708 0003914 TO6 📟

The preferred unit of measurement is millimeters. However, this item was designed using inchpound units of measurements. In case of problems involving conflicts between the metric and inch-pound units, the inch-pound units shall rule.

**---** 9004708 0003915 942 **---**

**=** 9004708 0003916 889 =

**=** 9004708 0003917 715 **=**

9004708 0003918 651 📟

AC testing inputs are driven at 2.4 V for a logic "1" and 0.45 V for a logic "0". Timing measurements are made at 2.0 V for a logic "1" and 0.8 V for a logic "0".

For timing purposes, a port pin is no longer floating when a 100 mV change from load voltage occurs and begins to float when a 100 mV change from the loaded  $\rm V_{OH}/V_{OL}$  level occurs  $\rm I_{OL}/I_{OH}$   $^{\pm 15}$  mA.

FIGURE 4. Switching waveforms and test circuit - continued

| STANDARD<br>MICROCIRCUIT DRAWING                     | SIZE<br>A |                | 5962-89982  |

|------------------------------------------------------|-----------|----------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |           | REVISION LEVEL | SHEET<br>18 |

DESC FORM 193A JUL 94

**=** 7004708 0003920 20T **=**

- 3.5 <u>Marking</u>. Marking shall be in accordance with MIL-STD-883 (see 3.1 herein). The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked as listed in MIL-BUL-103 (see 6.6 herein).

- 3.6 <u>Certificate of compliance</u>. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-BUL-103 (see 6.6 herein). The certificate of compliance submitted to DESC-EC prior to listing as an approved source of supply shall affirm that the manufacturer's product meets the requirements of MIL-STD-883 (see 3.1 herein) and the requirements herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required in MIL-STD-883 (see 3.1 herein) shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 <u>Notification of change</u>. Notification of change to DESC-EC shall be required in accordance with MIL-STD-883 (see 3.1 herein).

- 3.9 <u>Verification and review</u>. DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 <u>Sampling and inspection</u>. Sampling and inspection procedures shall be in accordance with MIL-STD-883 (see 3.1 herein).

- 4.2 <u>Screening</u>. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition C or D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1015 of MIL-STD-883.

- (2)  $T_A = +125$ °C, minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

TABLE II. <u>Electrical test requirements</u>.

| MIL-STD-883 test requirements                                      | Subgroups<br>(in accordance with<br>method 5005, table 1) |

|--------------------------------------------------------------------|-----------------------------------------------------------|

| Interim electrical parameters<br>(method 5004)                     |                                                           |

| Final electrical test parameters (method 5004)                     | 1*,2,3,7*8,<br>9,10,11                                    |

| Group A test requirements<br>(method 5005)                         | 1,2,3,4,7,8<br>9,10,11                                    |

| Groups C and D end-point<br>electrical parameters<br>(method 5005) | 1,7,9                                                     |

<sup>\*</sup> PDA applies to subgroup 1.

| STANDARD MICROCIRCUIT DRAWING                        | SIZE<br><b>A</b> |                     | 5962-89982  |

|------------------------------------------------------|------------------|---------------------|-------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVEL<br>A | SHEET<br>19 |

■ 9004708 0003921 146 **■**

- 4.3 <u>Quality conformance inspection</u>. Quality conformance inspection shall be in accordance with method 5005 of MIL-STD-883 including groups A, B, C, and D inspections. The following additional criteria shall apply.

- 4.3.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. Subgroups 5 and 6 in table I, method 5005 of MIL-STD-883 shall be omitted.

- c. Subgroup 4 (C<sub>IN</sub> measurement) shall be measured only for the initial test and after process or design changes which may affect input capacitance. A minimum sample size of five devices with zero rejects shall be required.

- d. Subgroups 7 and 8 shall include verification of the truth table.

- 4.3.2 Groups C and D inspections.

- a. End-point electrical parameters shall be as specified in table II herein.

- b. Steady-state life test conditions, method 1005 of MIL-STD-883.

- (1) Test condition C or D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in test method 1005 of MIL-STD-883.

- (2)  $T_A = +125$ °C, minimum.

- (3) Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

- PACKAGING

- 5.1 <u>Packaging requirements</u>. The requirements for packaging shall be in accordance with MIL-STD-883 (see 3.1 herein).

- 6. NOTES

- 6.1 <u>Intended use</u>. Microcircuits conforming to this drawing are intended for use for Government microcircuit applications (original equipment), design applications, and logistics purposes.

- 6.2 <u>Replaceability</u>. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.3 <u>Configuration control of SMD's</u>. All proposed changes to existing SMD's will be coordinated with the users of record for the individual documents. This coordination will be accomplished in accordance with MIL-STD-973 using DD Form 1692, Engineering Change Proposal.

- 6.4 <u>Record of users</u>. Military and industrial users shall inform Defense Electronics Supply Center when a system application requires configuration control and the applicable SMD. DESC will maintain a record of users and this list will be used for coordination and distribution of changes to the drawings. Users of drawings covering microelectronics devices (FSC 5962) should contact DESC-EC, telephone (513) 296-6047.

- 6.5 <u>Comments</u>. Comments on this drawing should be directed to DESC-EC, Dayton, Ohio 45444-5765, or telephone (513) 296-8525.

| STANDARD MICROCIRCUIT DRAWING DEFENSE ELECTRONICS SUPPLY CENTER | SIZE<br>A |                     | 5962-89982 |

|-----------------------------------------------------------------|-----------|---------------------|------------|

| DAYTON, OHIO 45444                                              |           | REVISION LEVEL<br>A | SHEET 20   |

9004708 0003922 082 **=**

# TABLE III. Pin functions.

| Pin name         | Function                                                                                                                                                                                                                                                                                                                                                               |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| v <sub>cc</sub>  | Main supply voltage (5.0 V).                                                                                                                                                                                                                                                                                                                                           |

| v <sub>ss</sub>  | Digital circuit ground (0.0 V). There are two $V_{	extsf{SS}}$ pins, both must be connected.                                                                                                                                                                                                                                                                           |

| V <sub>REF</sub> | Reference voltage for the A/D converter (5.0 V). $V_{\rm REF}$ is also the supply voltage to the analog portion of the A/D converter and the logic used to read port 0. Must be connected for A/D and port 0 to function.                                                                                                                                              |

| ANGND            | Reference ground for the A/D converter. Must be held at nominally the same potential as $V_{\rm SS}$ .                                                                                                                                                                                                                                                                 |

| V <sub>PP</sub>  | Timing pin for the return from power down circuit. Connect this pin with a 1 $\mu$ F capacitor to $V_{SS}$ and a 1 M $\Omega$ resistor to $V_{CC}$ . If this function is not used, $V_{pp}$ may be tied to $V_{CC}$ .                                                                                                                                                  |

| XTAL1            | Input of the oscillator inverter and of the internal clock generator.                                                                                                                                                                                                                                                                                                  |

| XTAL2            | Output of the oscillator inverter.                                                                                                                                                                                                                                                                                                                                     |

| CLKOUT           | Output of the internal clock generator. The frequency of CLKOUT is one-half the oscillator frequency. It has a 50 percent duty cycle.                                                                                                                                                                                                                                  |

| RESET            | Reset input to the chip. Input low for at least four state times to reset the chip. The subsequent low-to-high transition resynchroizes CLKOUT and commences a 10-state time sequence in which the PSW is cleared, a byte read from 2018H loads CCR, and a jump location to location 2080H is excuted. Input high for normal operation. RESET has an internal pull-up. |

| BUS WIDTH        | Input for BUS WIDTH selection. If CCR bit 1 is a one, this pin selects the bus width for the bus cycle in progress. If BUS WIDTH is a 1, a 16-bit bus cycle occurs. If BUS WIDTH is a 0 an 8-bit cycle occurs. If CCR bit 1 is a 0, the bus is always an 8-bit bus.                                                                                                    |

| NMI              | A positive transition causes a vector through 203EH.                                                                                                                                                                                                                                                                                                                   |

| INST             | Output high during an external memory read indicates the read is an instruction fetch. INST is valid throughout the bus cycle. INST is activated only during external memory accesses and output low for a data fetch.                                                                                                                                                 |

| EA               | EA must be tied low. EA equal to a TTL-low causes accesses to locations 2000H                                                                                                                                                                                                                                                                                          |

| ALE/ADV          | through 3FFF to be directed to off-chip memory.                                                                                                                                                                                                                                                                                                                        |

|                  | Address latch enable or address valid output as selected by CCR. Both pin options pro <u>vide</u> a latch to demultiplex the address from the address/data bus. When the pin is ADV, it goes inactive high at <u>the</u> end of the bus cycle. ADV can be used as a chip select for external memory. ALE/ADV is activated only during external memory addresses.       |

$6.6 \ \underline{Pin\ descriptions}$ . Microcircuits conforming to this drawing shall have pin functions as specified in table III.

| STANDARD<br>MICROCIRCUIT DRAWING                     | SI ZE<br>A |                     | 5962-89982 |

|------------------------------------------------------|------------|---------------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |            | REVISION LEVEL<br>A | SHEET 21   |

DESC FORM 193A JUL 94

■ 9004708 0003923 Tl9 ■

## TABLE III. Pin functions - continued

|                   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin name          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RD                | Read signal output to external memory . $\overline{\text{RD}}$ is activated only during external memory reads.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| WR/WRL            | Write and write low output to external memory, as selected by the CCR WR will go lo <u>w o</u> nly for external writes where an even byte is being written. WR/WRL is actvated only during external memory writes.                                                                                                                                                                                                                                                                                                                                                                                  |

| BHE/WRH           | Bus high enable or write high output to external memory, as selected by the CCR. BHE = 0 selects the bank of memory that is connected to high byte of the data bus. A0 = 0 selects the the bank of memory that is connected to the low byte of the data bus. Thus acesses to a 16-wide memory can be to the low byte only (A0 = 0, BHE = 1), to the high byte only (A0 = 1, BHE = 0), or both bytes (A0 = 0, BHE = 0). If the WRH function is selected the pin_will_go low if the bus cycle is writing to an odd memory location. BHE/WRH is valid only during 16-bit external memory write cycles. |

| READY             | Ready input to lengthen external memory cycles, for interfacing to slow or dynamic memory, or for bus sharing. If the pin is high, CPU operation continues in a normal manner. If the pin is low prior to the falling edge of CLKOUT, the memory contoller goes into a wait mode until the next positive transition in CLKOUT occurs with READY high. When the external memory is not being used READY has no effect. Internal control of the number of wait states inserted into a bus cycle held not ready is available through configuration of CCR.                                             |

| нѕі               | Inputs to high speed input unit. Four HSI pins are available: HSI.0, HSI.1, HSI.2, HSI.3. Two of them (HSI.2 and HSI.3) are shared with the HSO unit. The HSI pins are also used as the SID in SLAVE programming mode.                                                                                                                                                                                                                                                                                                                                                                              |

| нѕо               | Outputs from high speed output unit. Six HSO pins are available: HSO.O, HSO.1 HSO.2, HSO.3, HSO.4 and HSO.5. Two of them (HSO.4 and HSO.5) are shared with the HS1 unit.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| port 0            | 8-bit high impedance input only port. Three pins can be used as a digital inputs and /or as analog inputs to the on-chip A/D converter These pins set the programming mode.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PORT 1            | 8-bit quasi-bidirectional I/O port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PORT 2            | 8-bit multifunctional port. All of its pins are shared with other functions in the 01 device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PORT 3,<br>PORT 4 | 8-bit bi-directional I/O ports with open drain outputs. These pins are shared with the multiplexed address/data bus which has strong internal pull-ups.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

6.7 <u>Approved sources of supply</u>. Approved sources of supply are listed in MIL-BUL-103. The vendors listed in MIL-BUL-103 have agreed to this drawing and a certificate of compliance (see 3.6 herein) has been submitted to and accepted by DESC-EC.

| STANDARD<br>MICROCIRCUIT DRAWING                     | SIZE |                | 5962-89982 |

|------------------------------------------------------|------|----------------|------------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |      | REVISION LEVEL | SHEET 22   |