# TTL 1024 x 1-Bit Random Access Memory

The 93415 is a 1024-bit Read/Write RAM organized 1024 words by 1 bit. The 93415 is designed for buffer control storage and high performance main memory applications, and has a typical access time of 35 ns.

The 93415 has full decoding on-chip, separate data input and data output lines, and an active low chip select. The device is fully compatible with standard DTL and TTL logic families and features an uncommitted collector output for ease of memory expansion.

- Uncommitted Collector Output

- TTL Inputs and Output

- Non-Inverting Data Output

- High Speed —

Access Time — 35 ns Typical Chip Select — 15 ns Typical

- Power Dissipation Decreases with Increasing Temperature

- Power Dissipation 0.5 mW/Bit Typical

- Organized 1024 Words x 1 Bit

- Order as: 93415/BEAJC = Dual-In-Line 93415/BFAJC = Flat Pack

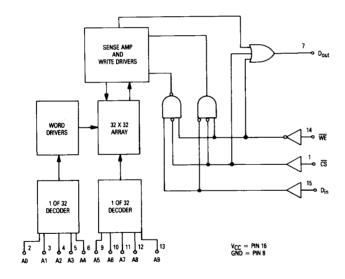

#### **BLOCK DIAGRAM**

# Military 93415

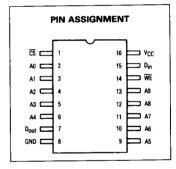

| PIN NAMES       |  |                |  |  |  |

|-----------------|--|----------------|--|--|--|

|                 |  | Chip Select    |  |  |  |

|                 |  | Address Inputs |  |  |  |

|                 |  | Write Enable   |  |  |  |

| D <sub>in</sub> |  | Data Input     |  |  |  |

| Dout            |  | Data Output    |  |  |  |

#### MOTOROLA MEMORY DATA

#### **FUNCTIONAL DESCRIPTION**

The 93415 is a fully decoded 1024-bit Random Access Memory organized 1024 words by one bit. Bit selection is achieved by means of a 10-bit address, A0 to A9.

The Chip Select input provides for memory array expansion. For large memories, the fast chip select access time permits the decoding of Chip Select (CS) from the address without affecting system performance.

The read and write operations are controlled by the state of the active low Write Enable (WE, Pin 14). With WE held low and the chip selected, the data at Din is written into the addressed location. To read, WE is held high and the chip selected. Data in the specified location is presented at Dout and is non-inverted.

Uncommitted collector outputs are provided to allow wired-OR applications. In any application an external pull-up resistor of RL value must be used to provide a

high at the output when it is off. Any RL value within the range specified below may be used.

$$\frac{V_{CC}(Min)}{I_{OL} - FO(1.6)} \leqslant R_L \leqslant \frac{V_{CC}(Min) - V_{OH}}{n(I_{CEX}) + FO(0.04)}$$

$R_1$  is in  $k\Omega$

n = number of wired-OR outputs tied together

FO = number of TTL Unit Loads (UL) driven

ICEX = Memory Output Leakage Current VOH = Required Output High Level at Output Node

IOL = Output Low Current

The minimum R<sub>L</sub> value is limited by output current sinking ability. The maximum RL value is determined by the output and input leakage current which must be supplied to hold the output at  $V_{OH}$ . One Unit Load = 40  $\mu A$ High/1.6 mA Low.

#### **ABSOLUTE MAXIMUM RATINGS** (Note 1)

| -55°C to +165°C    |

|--------------------|

| <165°C             |

| -0.5 V to +7.0 V   |

| -0.5 V to +5.5 V   |

| -0.5 V to +5.5 V   |

| + 20 mA            |

| - 12 mA to +5.0 mA |

|                    |

#### **TRUTH TABLE**

|                | Inputs |     |                   |              |  |

|----------------|--------|-----|-------------------|--------------|--|

| <del>c</del> s | WE     | Din | Open<br>Collector | Mode         |  |

| Н              | ×      | X   | н                 | Not Selected |  |

| L              | L      | L   | н                 | Write "0"    |  |

| L              | L      | н   | н                 | Write "1"    |  |

| L              | Н      | х   | Dout              | Read         |  |

H = High Voltage Level

L = Low Voltage Level

X = Don't Care (High or Low)

NOTE 1: Device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded.

## **GUARANTEED OPERATING RANGES (Note 2)**

| Supp  | ly Voltage | (V <sub>CC</sub> ) |                                       |

|-------|------------|--------------------|---------------------------------------|

| Min   | Nom        | Max                | Ambient Temperature (T <sub>A</sub> ) |

| 4.5 V | 5.0 V      | 5.5 V              | - 55°C to +125°C                      |

# DC OPERATING CONDITIONS AND CHARACTERISTICS (Full operating voltage and temperature range unless otherwise noted)

|        |                           | Limits |       |      |                                                 |  |

|--------|---------------------------|--------|-------|------|-------------------------------------------------|--|

| Symbol | Characteristic            | Min    | Max   | Unit | Conditions                                      |  |

| VOL    | Output Low Voltage        |        | 0.45  | Vdc  | V <sub>CC</sub> = Min, I <sub>OL</sub> = 16 mA  |  |

| VIH    | Input High Voltage        | 2.1    |       | Vdc  | Guaranteed Input High Voltage for All Inputs    |  |

| VIL    | Input Low Voltage         |        | 0.8   | Vdc  | Guaranteed Input Low Voltage for All Inputs     |  |

| IL     | Input Low Current         |        | -400  | μAdc | V <sub>CC</sub> = Max, V <sub>in</sub> = 0.4 V  |  |

| ΙΉ     | Input High Current        |        | 40    | μAdc | V <sub>CC</sub> = Max, V <sub>in</sub> = 4.5 V  |  |

| CEX    | Output Leakage Current    |        | 100   | μAdc | V <sub>CC</sub> = Max, V <sub>out</sub> = 5.5 V |  |

| VCD    | Input Diode Clamp Voltage |        | - 1.5 | Vdc  | V <sub>CC</sub> = Max, I <sub>in</sub> = -12 mA |  |

| lcc    | Power Supply Current      |        | 130   | mAdc | T <sub>A</sub> = +125°C                         |  |

|        |                           |        | 155   | mAdc | T <sub>A</sub> = 25°C V <sub>CC</sub> = 5.5 V,  |  |

|        |                           |        | 170   | mAdc | T <sub>A</sub> = -55°C All Inputs Grounded      |  |

#### MOTOROLA MEMORY DATA

# AC OPERATING CONDITIONS AND CHARACTERISTICS

(Full operating voltage and temperature unless otherwise noted)

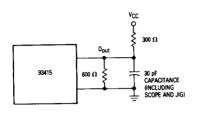

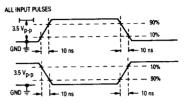

# AC TEST LOAD AND WAVEFORM

#### LOADING CONDITION

#### INPUT PULSES

|                                             |                                                                                                                                                                                                                            |                                            | 93415/BE/BF    |      |                                   |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------|------|-----------------------------------|

| Symbol                                      | Characteristic (Notes 2, 3)                                                                                                                                                                                                | Min                                        | Max            | Unit | Conditions                        |

| TACS TRCS TAA                               | DELAY TIMES Chip Select Time Chip Select Recovery Time Address Access Time                                                                                                                                                 |                                            | 45<br>50<br>60 | ns   | See Test Circuit and Waveforms    |

| WRITE MODE<br>tws                           | DELAY TIMES Write Disable Time Write Recovery Time                                                                                                                                                                         |                                            | 45<br>50       | ns   | See Test Circuit and Waveforms    |

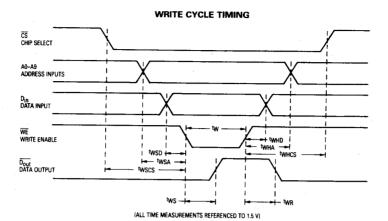

| tW<br>tWSD<br>tWHD<br>tWSA<br>tWHA<br>tWSCS | INPUT TIMING REQUIREMENTS Write Pulse Width (to guarantee write) Data Setup Time Prior to Write Data Hold Time After Write Address Setup Time (at tw = Min) Address Hold Time Chip Select Setup Time Chip Select Hold Time | 40<br>5.0<br>5.0<br>15<br>10<br>5.0<br>5.0 |                | ns   | See Test Circuit<br>and Waveforms |

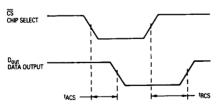

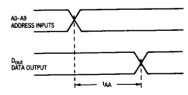

## **READ OPERATION TIMING DIAGRAM**

# PROPAGATION DELAY FROM CHIP SELECT

# PROPAGATION DELAY FROM ADDRESS INPUTS

(ALL TIME MEASUREMENTS REFERENCED TO 1.5 V)

#### MOTOROLA MEMORY DATA

Powered by ICminer.com Electronic-Library Service CopyRight 2003

8

NOTE 2: DC and AC specifications limits guaranteed with 500 linear feet per minute blown air.

|                      | θ <sub>JA</sub> (Junction to<br>Ambient)<br>Blown Still |                  |                                    |

|----------------------|---------------------------------------------------------|------------------|------------------------------------|

| Package              |                                                         |                  | θ <sub>JC</sub> (Junction to Case) |

| E Suffix<br>F Suffix | 50°C/W<br>55°C/W                                        | 85°C/W<br>90°C/W | 15°C/W<br>15°C/W                   |

NOTE 3: The AC limits are guaranteed to be the worst case bit in the memory.