### **General Description**

The DM9801 is a physical-layer, single-chip, low-power transceiver for 1M Home Phoneline Network applications. On the media side, it provides an interface to a Home Phoneline wiring system. The reconciliation layer interfaces to the DM9801 either through an IEEE802.3u subset Media Independent Interface (MII) or a pseudo-standard General Purpose Serial Interface (GPSI). A management interface is provided by MDIO/MDC when operating in MII mode, or a Serial Peripheral Interface bus when operating in GPSI mode.

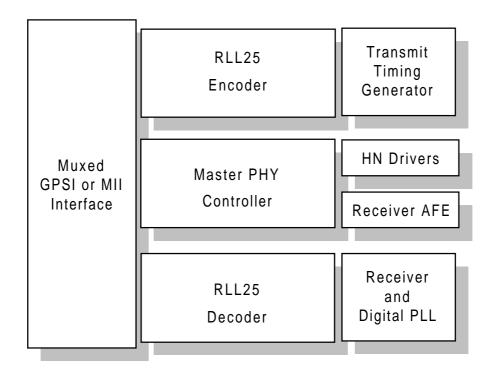

The DM9801 uses a low-power and high-performance CMOS process. It contains the entire physical layer functions of 1M as defined by Home Phoneline Network Alliance, Rev. 1.1, including the Physical Coding Sublayer, (RLL25) Encoder/Decoder (ENC/DEC), 4-wire HN Driver circuit and receiver analog front end (AFE).

### Patent-Pending Circuitry Includes:

An enhanced 4-wire Home Network transceiver circuit.

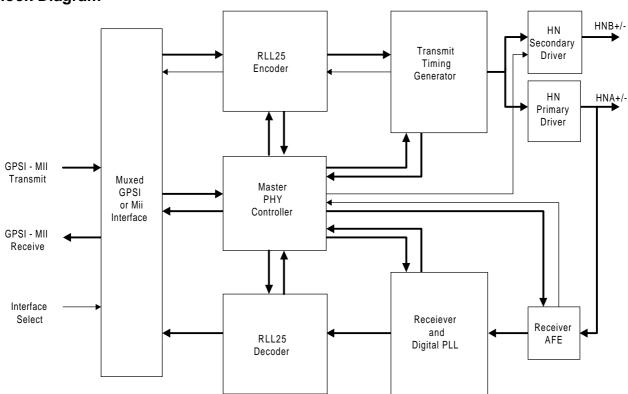

## **Block Diagram**

Preliminary Version: DM9801-DS-P02 March 20, 2000 1

#### **Features**

- 1M Home Phoneline Network physical-layer, singlechip transceiver

- Supports the MII including the MDIO/MDC serial management interface

- Supports the GPSI including a SPI serial management interface

- Supports Link Integrity function

- Smart equalizer circuit for 1M receiver

- Supports Patent Pending 4-wire operation

- Supports hardware or software speed select

- Supports Interrupt on change, eliminates management polling

- Flexible built-in LED support for TX Activity, RX Activity and Collision Indication or Activity, Link state and Collision

- Digital PLL circuit using advanced digital algorithm to reduce jitter

- Low-power, high-performance CMOS process

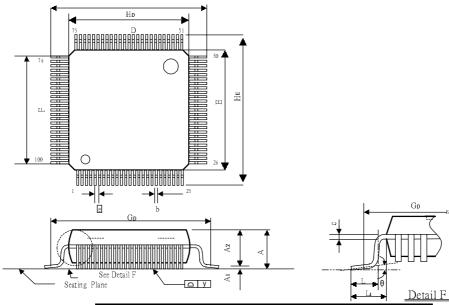

- Available in a small outline 100-pin LQFP

- 3.3V DC power with 5V DC tolerant I/O

March 20, 2000

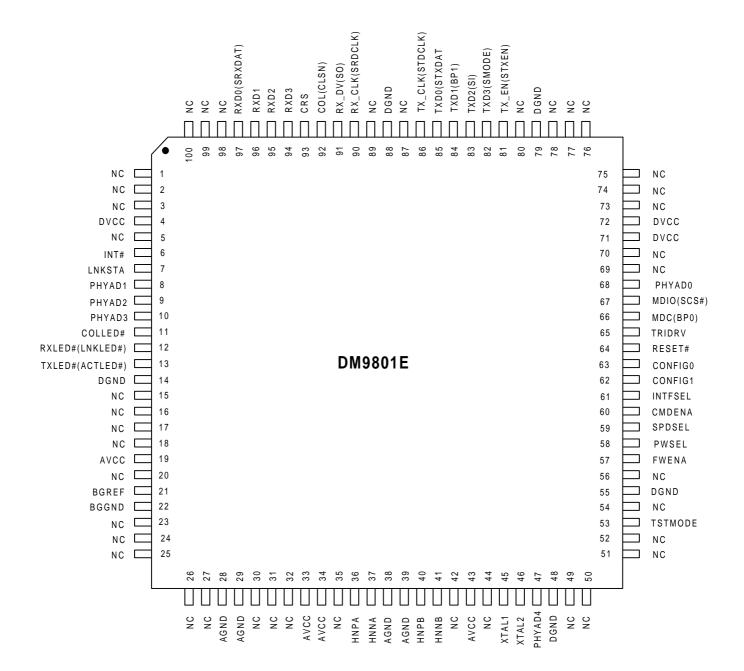

## Pin Configuration: DM9801, 100-pin LQFP

# **Pin Description**

| Pin No.    | Pin Name     | I/O     | Description                                                                                                                                                                                                                                                             |

|------------|--------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Station Ir | terface: Rec | eive Da | ta, Transmit Data and Management                                                                                                                                                                                                                                        |

| 85         | TXD0         | I       | Transmit Data Bit 0 (MII Mode, INTFSEL = 0):                                                                                                                                                                                                                            |

|            | or           |         | Transmit data input pin, bit 0, for nibble data from the MII                                                                                                                                                                                                            |

|            | STXDAT       |         | Serial Transmit Data Bit (GPSI Mode, INTFSEL = 1):                                                                                                                                                                                                                      |

|            |              |         | Transmit data input pin for serial data from the GPSI.                                                                                                                                                                                                                  |

| 84         | TXD1         | I       | Transmit Data Bit 1 (MII Mode, INTFSEL = 0):                                                                                                                                                                                                                            |

|            | or           |         | Transmit data input pin, bit 1, for nibble data from the MII                                                                                                                                                                                                            |

|            | BP1          |         | SPROM Boot Page Select 1 (GPSI Mode, INTFSEL = 1):                                                                                                                                                                                                                      |

|            |              |         | Most significant bit of a 2-bit encoded select. The BP1 and BP0 inputs, select                                                                                                                                                                                          |

|            |              |         | one of four, 64-byte, SPROM pages to initialize the DM9801 management                                                                                                                                                                                                   |

| 83         | TXD2         | - 1     | registers. Master mode must be selected using the SMODE input.  Transmit Data Bit 2 (MII Mode, INTFSEL = 0):                                                                                                                                                            |

| 03         |              | ı       | Transmit data input pin, bit 2, for nibble data from the MII                                                                                                                                                                                                            |

|            | or<br>SI     |         | Serial Data Input (GPSI Mode, INTFSEL = 1):                                                                                                                                                                                                                             |

|            | Si           |         | This is the serial data input pin to the DM9801 for the SPI bus. The SPI bus                                                                                                                                                                                            |

|            |              |         | operation is only valid if GPSI mode is selected.                                                                                                                                                                                                                       |

| 82         | TXD3         | ı       | Transmit Data Bit 3 (MII Mode, INTFSEL = 0):                                                                                                                                                                                                                            |

| 02         | or           | •       | Transmit data input pin, bit 3, for nibble data from the MII                                                                                                                                                                                                            |

|            | SMODE        |         | Serial Mode Select (GPSI Mode, INTFSEL = 1):                                                                                                                                                                                                                            |

|            |              |         | This input pin selects the SPI buses mode of operation. The SPI bus modes                                                                                                                                                                                               |

|            |              |         | of operation are:                                                                                                                                                                                                                                                       |

|            |              |         | Master Mode (SMODE = 0)                                                                                                                                                                                                                                                 |

|            |              |         | Slave Mode (SMODE = 1)                                                                                                                                                                                                                                                  |

|            |              |         | The SPI bus operation is only valid if GPSI mode is selected.                                                                                                                                                                                                           |

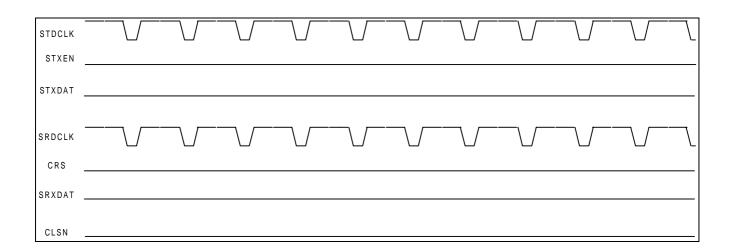

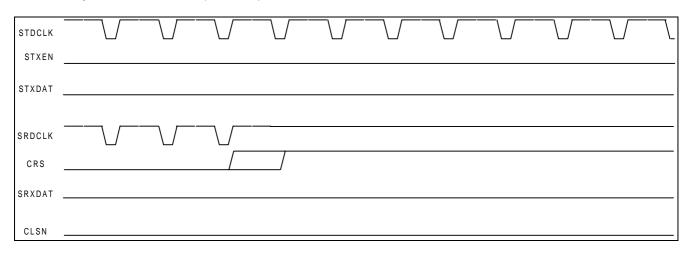

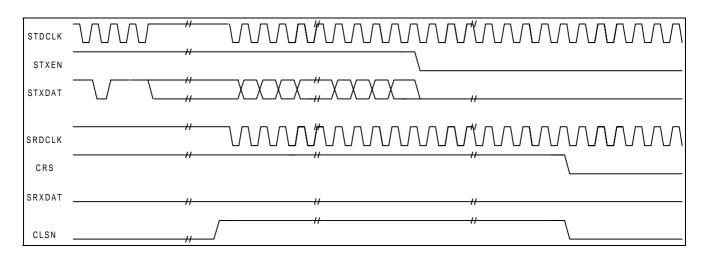

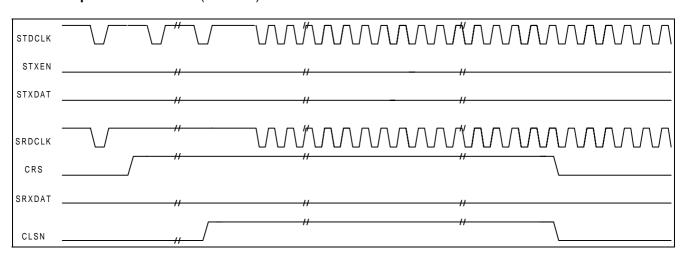

| 86         | TX_CLK       | O,Z     | MII Transmit Clock (MII Mode, INTFSEL = 0):                                                                                                                                                                                                                             |

|            | or           |         | TX_CLK is an output pin from the DM9801. Used as the transmit data                                                                                                                                                                                                      |

|            | STDCLK       |         | reference clock, to clock in nibble data from the MII when in MII interface                                                                                                                                                                                             |

|            |              |         | mode. Serial Transmit Data Clock (GPSI Mode, INTFSEL = 1):                                                                                                                                                                                                              |

|            |              |         | STDCLK is an output from the DM9801. Used as the transmit reference clock                                                                                                                                                                                               |

|            |              |         | to clock in the STXDATA when in GPSI interface mode.                                                                                                                                                                                                                    |

| 81         | TX_EN        | 1       | MII Transmit Enable (MII Mode, INTFSEL = 0):                                                                                                                                                                                                                            |

| <b>0</b> 1 | or           | •       | MII Transmit enable input, used to enable the transmit function of the MII                                                                                                                                                                                              |

|            | STXEN        |         | when in MII interface mode.                                                                                                                                                                                                                                             |

|            |              |         | Serial Transmit Enable (GPSI Mode, INTFSEL = 1):                                                                                                                                                                                                                        |

|            |              |         | Used to enable the transmit function of the GPSI when in GPSI interface                                                                                                                                                                                                 |

|            |              |         | mode.                                                                                                                                                                                                                                                                   |

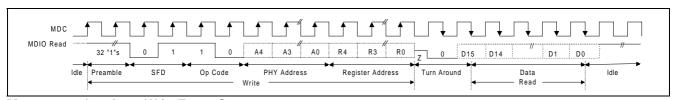

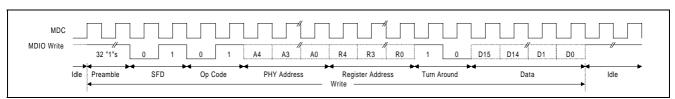

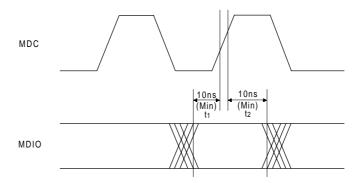

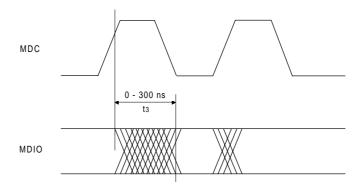

| 66         | MDC          | I       | MII Serial Management Clock (MII Mode, INTFSEL = 0):                                                                                                                                                                                                                    |

|            | or           |         | Synchronous clock to the MDIO management data input/output serial                                                                                                                                                                                                       |

|            | BP0          |         | interface which is asynchronous to transmit and receive clocks. The                                                                                                                                                                                                     |

|            |              |         | maximum clock rate is 2.5MHz.                                                                                                                                                                                                                                           |

|            |              |         |                                                                                                                                                                                                                                                                         |

|            |              |         |                                                                                                                                                                                                                                                                         |

|            |              |         |                                                                                                                                                                                                                                                                         |

|            |              |         |                                                                                                                                                                                                                                                                         |

|            |              |         | SPROM Boot Page Select 0 (GPSI Mode, INTFSEL = 1): Least significant bit of a 2-bit encoded select. The BP1 and BP0 inputs, select one of four, 64-byte, SPROM pages to initialize the DM9801 management registers. Master mode must be selected using the SMODE input. |

4 Preliminary

| Pin No.    | Pin Name       | I/O     | Description                                                                                              |

|------------|----------------|---------|----------------------------------------------------------------------------------------------------------|

| Station In | terface: Recei | ve Data | , Transmit Data and Management (Continued)                                                               |

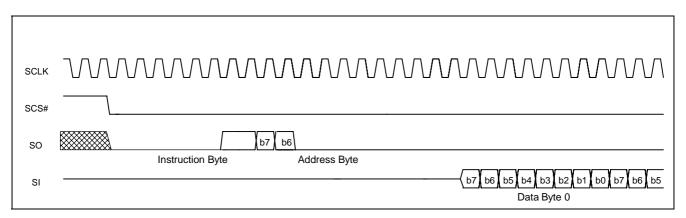

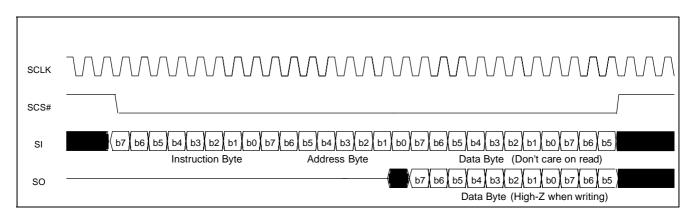

| 67         | MDIO           | I/O,Z   | MII Serial Management Data (MII Mode, INTFSEL = 0):                                                      |

|            | Or             | ,       | Bi-directional management instruction/data signal that may be driven by the                              |

|            | SCS#           |         | station management entity or the PHY. This pin requires a 1.5KΩ pull-up                                  |

|            |                |         | resistor.                                                                                                |

|            |                |         | Serial Interface Chip Select (GPSI Mode, INTFSEL = 1):                                                   |

|            |                |         | SCS# is a bi-directional management chip select signal that may be driven                                |

|            |                |         | by the station management entity or the PHY. (Active low)                                                |

| 97         | RXD0           | O,Z     | Receive Data Bit 0 (MII Mode, INTFSEL = 0):                                                              |

|            | Or             |         | Receive data output pin, bit 0, for nibble data to the MII                                               |

|            | SRXDAT         |         | Serial Receive Data Bit (GPSI Mode, INTFSEL = 1):                                                        |

|            |                |         | Receive data output pin for serial data to the GPSI.                                                     |

| 96         | RXD1           | O,Z     | Receive Data Bit 1:                                                                                      |

|            |                |         | Receive data output pin, bit 1, for nibble data to the                                                   |

| 95         | RXD2           | O,Z     | Receive Data Bit 2:                                                                                      |

|            |                |         | Receive data output pin, bit 2, for nibble data to the MII                                               |

| 94         | RXD3           | O,Z     | Receive Data Bit 3:                                                                                      |

|            |                |         | Receive data output pin, bit 3, for nibble data to the MII                                               |

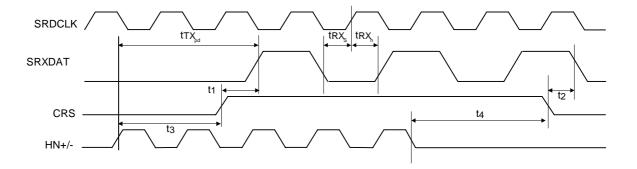

| 90         | RX_CLK         | O,Z     | MII Receive Clock (MII Mode, INTFSEL = 0):                                                               |

|            | Or             |         | RX_CLK is an output pin from the DM9801. Used as the receive data                                        |

|            | SRDCLK         |         | reference clock, to clock out nibble data from the MII when in MII interface                             |

|            |                |         | mode.                                                                                                    |

|            |                |         | Serial Receive Data Clock (GPSI Mode, INTFSEL = 1):                                                      |

|            |                |         | SRDCLK is an output from the DM9801. Used as the receive reference                                       |

| 91         | RX DV          | O,Z     | clock to clock out the SRXDATA when in GPSI interface mode.  Receive Data Valid (MII Mode, INTFSEL = 0): |

| 91         | Or             | 0,2     | RX_DV is asserted high to indicate that valid data is present on RXD[3:0].                               |

|            | SO             |         | Serial Data Output (GPSI Mode, INTFSEL = 1):                                                             |

|            | 30             |         | This is the serial data output pin from the DM9801 for the SPI bus. The SPI                              |

|            |                |         | bus operation is only valid if GPSI mode is selected.                                                    |

| 93         | CRS            | O,Z     | Carrier Sense:                                                                                           |

|            |                | J ,     | This pin is asserted high to indicate the presence of carrier due to receive                             |

|            |                |         | or transmit activities.                                                                                  |

| 92         | COL            | O,Z     | Collision Detect MII Mode, INTFSEL = 0):                                                                 |

|            | or             | ,_      | COL is asserted high to indicate detection of collision condition.                                       |

|            | CLSN           |         | Collision Detect (GPSI Mode, INTFSEL = 1):                                                               |

|            | _              |         | CLSN is asserted high to indicate detection of collision condition.                                      |

5

| DUN A : : |                 |           |                                                                                                              |

|-----------|-----------------|-----------|--------------------------------------------------------------------------------------------------------------|

|           | ress Interface: | -         | DIN 11 A 11 (2000) III (2000)                                                                                |

|           |                 |           | nique PHY address. An address selection of all zeros (00000) will result in a                                |

|           |                 |           | isolate bit description in the BMCR, address 00.                                                             |

| 68        | PHYADSEL        | I/O,Z     |                                                                                                              |

|           | (PHYAD0)        |           | PHYADSEL is an input signal that selects one of two PHY addresses within                                     |

|           | Or              |           | the 32 address range for the DM9801 MII management interface when both                                       |

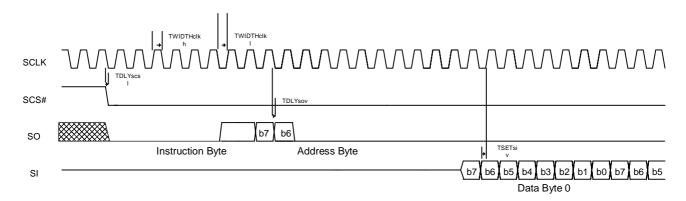

|           | SCLK            |           | CONFIG1 and CONFIG0 are not set to 1.                                                                        |

|           |                 |           | 0 = 0x01 address<br>1 = 0x1F address                                                                         |

|           |                 |           | PHY Address 0 (MII Mode, INTFSEL = 0):                                                                       |

|           |                 |           | PHY address bit 0 for multiple PHY address applications. Both CONFIG1                                        |

|           |                 |           | and CONFIG0 must be set to 1.                                                                                |

|           |                 |           | Serial Interface Clock (GPSI Mode, INTFSEL = 1):                                                             |

|           |                 |           | SCLK is a bi-directional clock signal used to synchronize SI, SO and SCS#                                    |

|           |                 |           | to and from the DM9801 SPI bus.                                                                              |

| 8         | PHYAD1          | I/O,      | PHY Address 1 (MII Mode, INTFSEL = 0):                                                                       |

|           |                 | Z         | PHY address bit 1 for multiple PHY address applications. Both CONFIG1                                        |

|           |                 |           | and CONFIG0 must be set to 1. Leave unconnected when both CONFIG1                                            |

|           |                 |           | and CONFIG0 are not 1.                                                                                       |

| 9         | PHYAD2          | I/O,      | PHY Address 2 (MII Mode, INTFSEL = 0):                                                                       |

|           |                 | Z         | PHY address bit 2 for multiple PHY address applications. Both CONFIG1                                        |

|           |                 |           | and CONFIG0 must be set to 1. Leave unconnected when both CONFIG1                                            |

|           | 51 D (4 5 5     |           | and CONFIG0 are not 1.                                                                                       |

| 10        | PHYAD3          | I/O,      | PHY Address 3 (MII Mode, INTFSEL = 0):                                                                       |

|           |                 | Z         | PHY address bit 3 for multiple PHY address applications. Both CONFIG1                                        |

|           |                 |           | and CONFIG0 must be set to 1. Leave unconnected when both CONFIG1                                            |

| 47        | PHYAD4          | 1/0       | and CONFIG0 are not 1.                                                                                       |

| 4/        | PHYAD4          | I/O,<br>Z | PHY Address 4 (MII Mode, INTFSEL = 0): PHY address bit 4 for multiple PHY address applications. Both CONFIG1 |

|           |                 | _         | and CONFIG0 must be set to 1. Leave unconnected when both CONFIG1                                            |

|           |                 |           | and CONFIGO must be set to 1. Leave unconnected when both CONFIG 1 and CONFIGO are not 1.                    |

|           | 1               |           | and CON 100 arc not 1.                                                                                       |

6 Preliminary

| Pin No.   | Pin Name       | I/O      | Description                                                              |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|-----------|----------------|----------|--------------------------------------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Configura | ation and Cont | rol Inte | rface:                                                                   |                                      | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 64        | RESET#         | I        | Reset:                                                                   | 4 4 1 - 4 1 - 14 - 11 -              | and the DM0004. Chevild remain law for 40mg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|           |                |          |                                                                          |                                      | zes the DM9801. Should remain low for 10ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|           | 00115100       | <u> </u> | after VCC has stabilized at 3.3Vdc (nominal) before it transitions high. |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 63        | CONFIG0        | I        | Configuration Select 1:0:                                                |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 62        | CONFIG1        |          | These input pi                                                           | ns select the                        | DM9801 configuration from a reset condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|           |                |          | CONFIG1                                                                  | CONFIG0                              | Configuration Selected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|           |                |          | 0                                                                        | 0                                    | TXLED, RXLED and COLLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|           |                |          |                                                                          |                                      | configuration *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|           |                |          | 0                                                                        | 1                                    | ACTLED, LNKLED and COLLED configuration *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|           |                |          | 1                                                                        | 0                                    | ACTLED, LNKLED and COLLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|           |                |          |                                                                          |                                      | configuration with MII Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|           |                |          |                                                                          |                                      | Register 0-6 emulation support *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|           |                |          | 1                                                                        | 1                                    | ACTLED, LNKLED and COLLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|           |                |          |                                                                          |                                      | Configuration with MII Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|           |                |          |                                                                          |                                      | Register 0-6 emulation and 32 PHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|           |                |          |                                                                          |                                      | addresses support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|           |                |          |                                                                          |                                      | addiococo support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|           |                |          | *see the DM98                                                            | 301 descriptio                       | n for a more detailed explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 61        | INTFSEL        | I        | Interface Select:                                                        |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

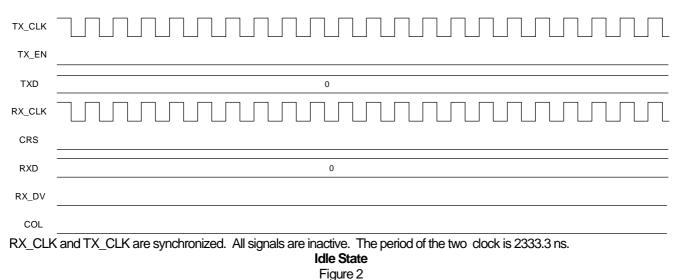

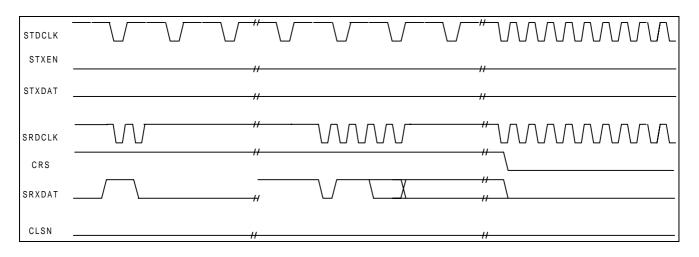

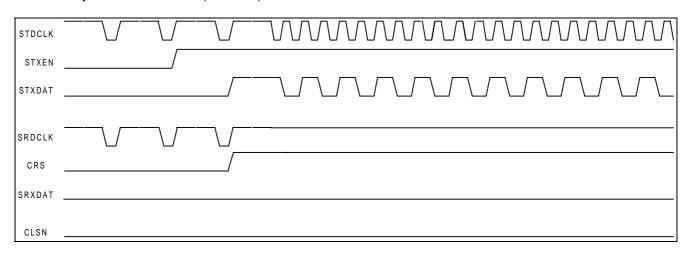

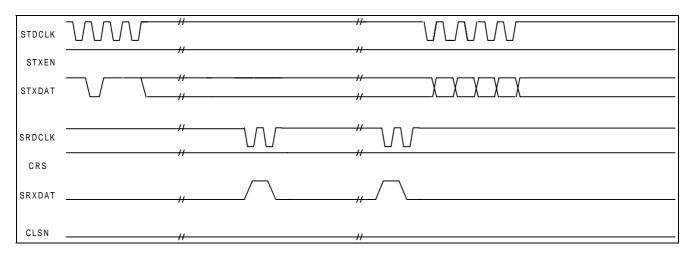

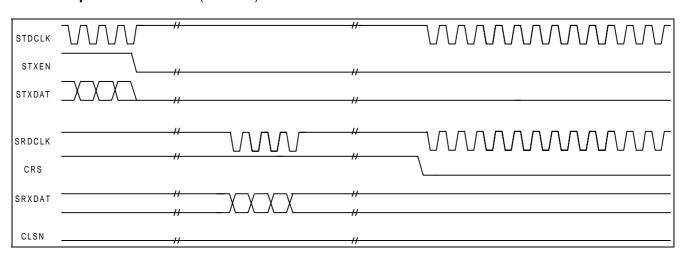

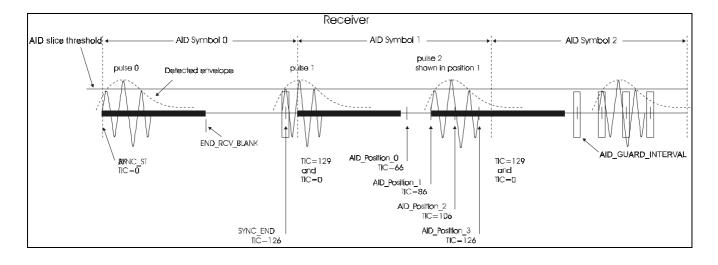

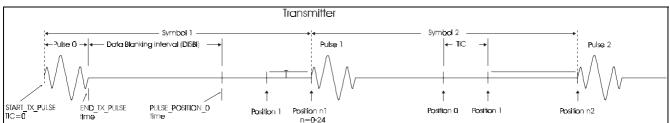

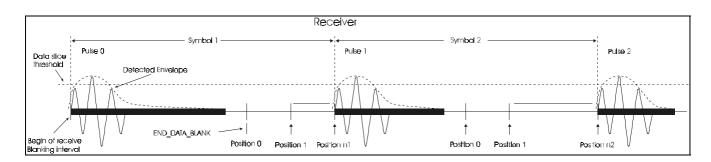

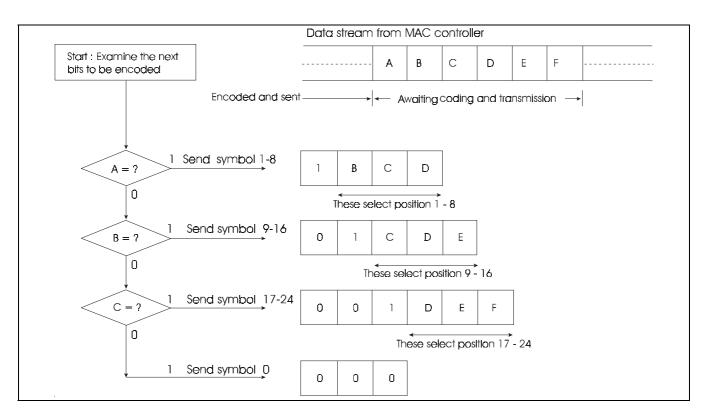

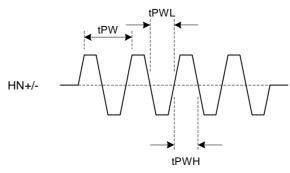

|           |                |          | This pin select                                                          | III interface or the GPSI interface. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |