International

Rectifier

# Developer's Guide

International Rectifier • 233 Kansas Street, El Segundo, CA 90245 • USA

# IRMCK203 Application Developer's Guide

February 19, 2004 Version 1.0

# **Table of Contents**

| I | Introduc  | tiontion                                                        | 5  |

|---|-----------|-----------------------------------------------------------------|----|

|   | 1.1 Cor   | nstraints                                                       | 5  |

|   | 1.2 App   | plication Connections                                           | 5  |

| 2 | Concept   | S                                                               | 7  |

|   | 2.1 Reg   | gulators                                                        | 7  |

|   | 2.1.1     | Closed Loop Current Control                                     | 7  |

|   | 2.1.2     | Closed Loop Velocity Control                                    | 7  |

|   | 2.1.3     | Rotor Angle Estimation                                          | 8  |

|   | 2.1.4     | Start-Stop Sequencer and Fault Detection                        | 8  |

|   | 2.2 Cui   | rrent Feedbacks                                                 |    |

|   | 2.2.1     | Using IR2175                                                    | 8  |

|   | 2.2.2     | Using Inverter Leg Shunt                                        | 8  |

|   | 2.3 Con   | mmunication                                                     | 8  |

|   | 2.3.1     | RS-232 Serial Interface                                         |    |

|   | 2.3.2     | SPI Interface                                                   |    |

|   | 2.3.3     | Host Parallel Interface                                         | 9  |

|   | 2.3.4     | Synchronization of PWM Cycle to an External Microprocessor      |    |

|   | 2.4 Ext   | ernal Interfaces                                                |    |

|   | 2.4.1     | Discrete I/O External Interface.                                |    |

|   | 2.4.2     | Analog I/O Interface                                            |    |

|   | 2.5 Sec   | juencing Control                                                |    |

|   |           | ılt Handling                                                    |    |

|   | 2.6.1     | Gatekill Structure and Overcurrent/Overtemperature Fault        |    |

|   | 2.6.2     | DC Bus Faults and DC Bus Braking                                |    |

|   | 2.7 LE    | D Modes                                                         |    |

| 3 |           | tart-up Supporting Tools                                        |    |

|   |           | rt-up Flow                                                      |    |

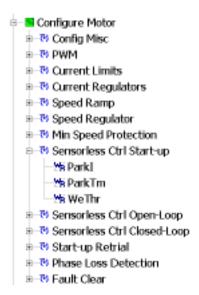

|   | 3.1.1     | Drive Parameter Setup                                           |    |

|   | 3.1.2     | Evaluating Drive Performance                                    |    |

|   | 3.1.3     | Diagnostic Mode Functions                                       |    |

|   | 3.1.4     | Miscellaneous Functions                                         |    |

|   | 3.2 Sta   | ndalone Operation and Register Initialization via Serial EEPROM |    |

|   | 3.2.1     | Register Initialization via EEPROM                              | 31 |

|   | 3.2.2     | Starting and Stopping the Motor                                 |    |

|   | 3.2.3     | Fault Processing                                                |    |

| 4 | Reference | ce                                                              |    |

|   | 4.1 Reg   | gister Access                                                   | 33 |

|   | 4.1.1     | Host Parallel Access                                            |    |

|   | 4.1.2     | SPI Register Access                                             | 33 |

|   | 4.1.3     | RS-232 Register Access                                          | 33 |

|   | 4.2 Wr    | ite Register Definitions                                        |    |

|   | 4.2.1     | PwmConfig Register Group (Write Registers)                      | 38 |

|   | 4.2.2     | CurrentFeedbackConfig Register Group (Write Registers)          |    |

|   | 4.2.3     | SystemControl Register Group (Write Registers)                  |    |

|   | 4.2.4     | TorqueLoopConfig Register Group (Write Registers)               |    |

|   | 4.2.5     | VelocityControl Register Group (Write Registers)                |    |

|   | 4.2.6     | FaultControl Register Group (Write Registers)                   |    |

|   | 4.2.7     | SystemConfig Register Group (Write Registers)                   |    |

|   | 4.2.8     | EepromControl Registers (Write Registers)                       |    |

|   | 4.2.9     | ClosedLoopAngleEstimator Registers (Write Registers)            |    |

|   | 4.2.10    | OpenLoopAngleEstimator Registers (Write Registers)              |    |

|   |           |                                                                 |    |

| 4.2.11     | StartupAngleEstimator Registers (Write Registers)           | 46 |

|------------|-------------------------------------------------------------|----|

| 4.2.12     | StartupRetrial Registers (Write Registers)                  |    |

| 4.2.13     | PhaseLossDetect Registers (Write Registers)                 |    |

| 4.2.14     | D/AConverter Registers (Write Registers)                    | 49 |

| 4.2.15     | Factory Test Register (Write Register)                      | 50 |

| 4.3 Rea    | nd Register Definitions                                     |    |

| 4.3.1      | SystemStatus Register Group (Read Registers)                | 51 |

| 4.3.2      | DcBusVoltage Register Group (Read Registers)                | 51 |

| 4.3.3      | FocDiagnosticData Register Group (Read Registers)           | 52 |

| 4.3.4      | FaultStatus Register Group (Read Registers)                 |    |

| 4.3.5      | VelocityStatus Register Group (Read Registers)              |    |

| 4.3.6      | CurrentFeedbackOffset Register Group (Read Registers)       |    |

| 4.3.7      | EepromStatus Registers (Read Registers)                     |    |

| 4.3.8      | FOCDiagnosticDataSupplement Register Group (Read Registers) |    |

| 4.3.9      | ProductIdentification Registers (Read Registers)            |    |

| 4.3.10     | Factory Register (Read Register)                            |    |

| Appendix A | Space Vector PWM Module                                     |    |

|            | Basic Theory and Transfer Characteristics                   |    |

|            | ration                                                      |    |

|            | ier Period                                                  |    |

|            | nsertion Logic                                              |    |

|            | al and Asymmetrical Mode Operation                          |    |

|            | se and Two-Phase Modulation                                 |    |

| Appendix B | IR2175 Current Sensing                                      | 64 |

# List of Figures

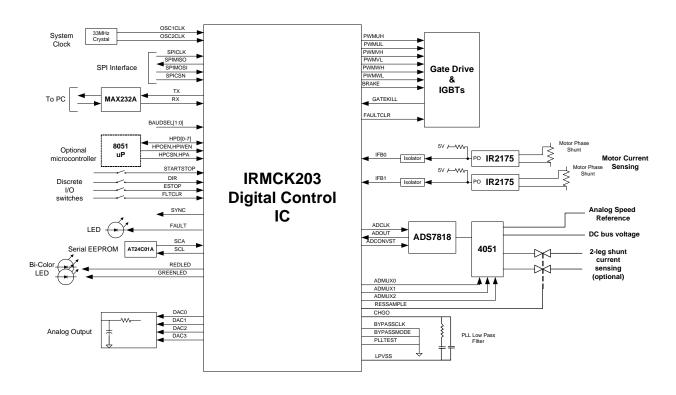

| Figure 1.  | Typical Application Connections of IRMCK203       | 6    |

|------------|---------------------------------------------------|------|

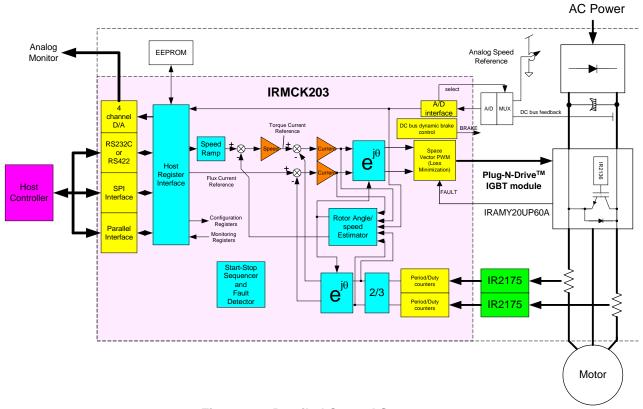

| Figure 2.  | Detailed Control Structure                        | 7    |

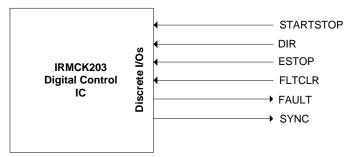

| Figure 3.  | Discrete I/O Signals                              | .10  |

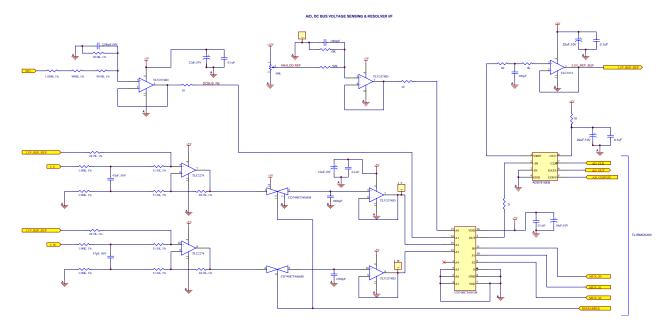

| Figure 4.  | Analog Interface Example                          | . 12 |

| Figure 5.  | State Diagram and Sequencing                      | 13   |

| Figure 6.  | Protection Circuit Block Diagram                  | 15   |

| Figure 7.  | Overview of Drive Commissioning                   | .17  |

| Figure 8.  | Motor Information in User Entries Worksheet       | 18   |

| Figure 9.  | Application Information in User Entries Worksheet | 19   |

| Figure 10. | Shunt Resistor Value in User Entries Worksheet    | 22   |

| Figure 11. | Drive Control Modes                               | 24   |

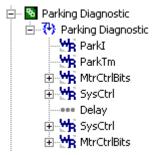

| Figure 12. | Parking Diagnostic Function                       | 25   |

| Figure 13. | Enter Optimal Parking Parameters                  | 26   |

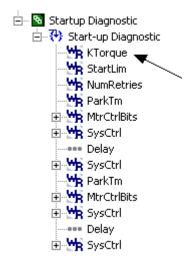

| Figure 14. | Start-up Diagnostic Function                      | 27   |

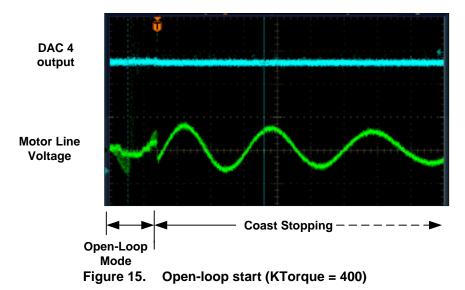

| Figure 15. | Open-loop start (KTorque = 400)                   | 27   |

| Figure 16. | Open-loop start-up (KTorque = 520)                | 28   |

| Figure 17. | Enter Optimal KTorque Parameter                   | . 28 |

| Figure 18. | Configuring the Startup Current                   |      |

| Figure 19. | Start-up Retrial Function.                        |      |

| Figure 20. | IRMCK203 Standalone System                        | 31   |

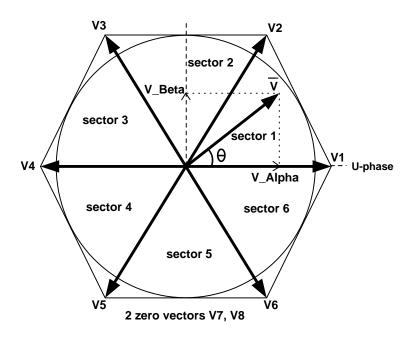

| Figure 21. | Space Vector Diagram                              | .58  |

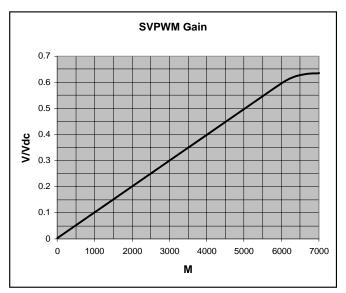

| Figure 22. | Transfer Characteristics                          | . 59 |

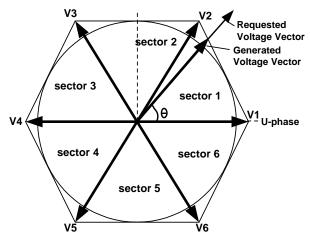

| Figure 23. | Voltage Vector Rescaling                          | . 59 |

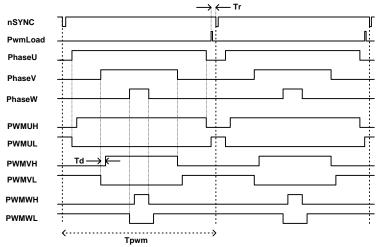

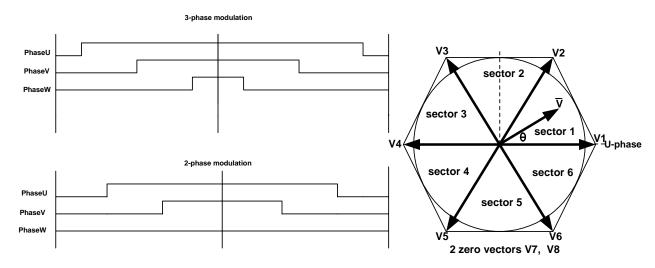

| Figure 24. | 3-phase Space Vector PWM                          |      |

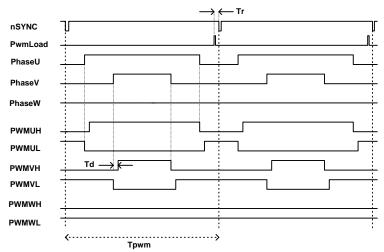

| Figure 25. | 2-phase (6-step PWM) Space Vector PWM             |      |

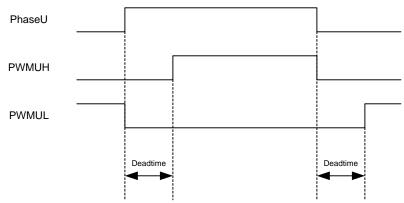

| Figure 26. | Deadtime Insertion                                | 61   |

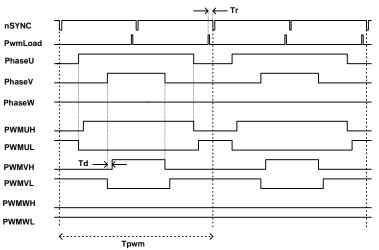

| Figure 27. | Asymmetrical PWM Mode                             | 62   |

| Figure 28. | Three-Phase and Two-Phase Modulation              |      |

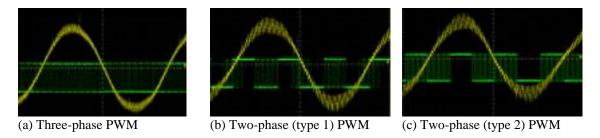

| Figure 29. | Different Types of Space Vector PWM               | 63   |

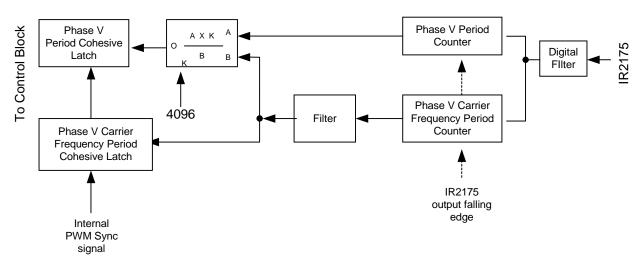

| Figure 30. | Current Feedback Measurement Block                |      |

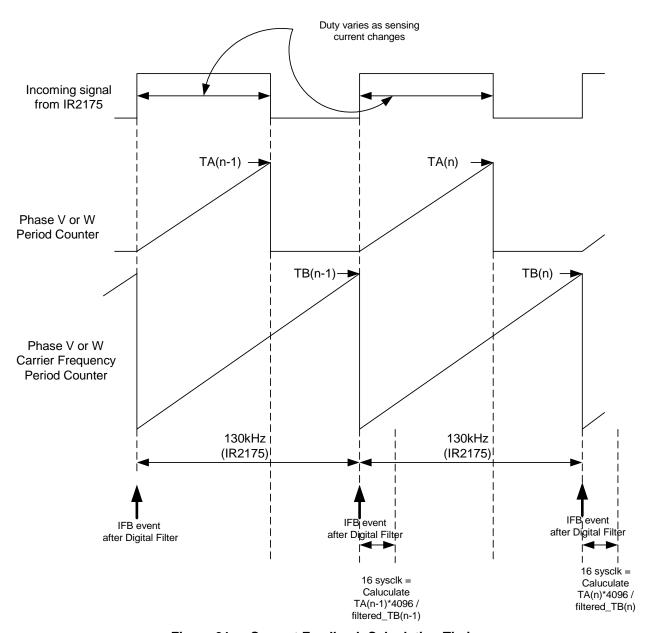

| Figure 31. | Current Feedback Calculation Timing               |      |

|            | List of Tables                                    |      |

| Table 1. B | AUD Selection Table                               | 🤆    |

|            | ternal RS-232 Signal Description                  |      |

|            | ternal SPI I/F Signal Description                 |      |

|            | ternal Host Parallel I/F Signal Description       |      |

|            | External Interface Signal Description             |      |

|            | Analog Output Data Source Selection               |      |

|            | Sequencing Control Signals                        |      |

|            | Drive Fault Conditions                            |      |

|            | Overvoltage and Undervoltage Trip Levels          |      |

| Table 10.  | Dynamic Braking Voltage Levels                    |      |

| Table 11.  | LED Modes                                         |      |

|            |                                                   |      |

## 1 Introduction

This document is provided as a supplement to the datasheet for the IRMCK203. It provides detailed information about the internal design and external interfaces of the product and describes how to configure the operation to conform to the requirements of a custom application. This document is intended for engineers who are developing an application using the IRMCK203 digital control IC.

The document is divided into three main sections. In the Concepts section, system design concepts are presented and theory of operation is described in detail. This section provides the background needed to begin IRMCK203 application development. The Techniques section provides practical "how-to" information, tips and examples to assist with the development process. The Reference section provides a complete definition of the host register map with a short description of each register and field. The registers are listed in sequential order for easy reference.

#### 1.1 Constraints

The following are constraints for use of the IRMCK203 with a custom hardware system.

#### **Analog Interface**

The IRMCK203 has a built-in interface to the ADS7818 (BurrBrown) serial A/D converter (12 bit). Dc bus voltage feedback, external speed reference and Leg Shunt current can be obtained via ADS7818 in conjunction with MUX circuitry. An analog feedback application example is given in Section 2.4.2.

#### **Current Feedback Interface**

The IRMCK203 has a built-in interface circuit for two IR2175 motor current sensing high voltage ICs. With two IR2175 and two shunt resistors, the motor phase currents can be obtained for motor control purposes. A 10-bit resolution of current feedback data can be obtained. The practical power level limit for using shunt resistors is up to 3.7 kW. For a higher horsepower application, a resistor shunt becomes impractical due to power dissipation of shunt resistors (insert in series between motor and drive).

The IRMCK203 provides other means of current feedback through the use of an ADS7818 (BurrBrown) serial A/D converter and Inverter Leg Shunt resistor. Inverter Leg Shunt currents can be used (reconstruction of phase current inside IRMCK203) instead of IR2175 current feedback. However, the Leg Shunt option is recommended only for an Inverter switching frequency less than 10KHz.

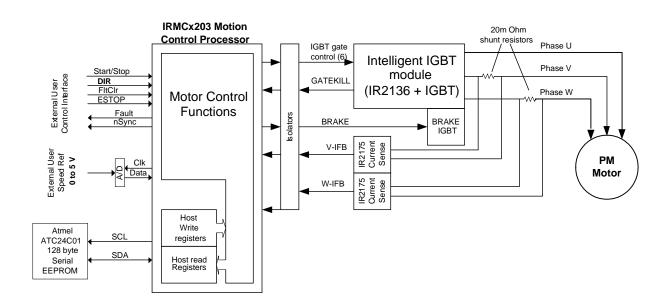

## 1.2 Application Connections

Figure 1 shows a typical application connection block diagram. In order to complete a Sensorless drive control, all necessary components are shown in connection to IRMCK203. A fully self-contained drive evaluation board (IRMCS2031) based on the IRMCK203 Digital Control IC is available for drive performance evaluation.

The figure shows a typical hardware configuration. Users can customize the design without the effort of modifying code.

Figure 1. Typical Application Connections of IRMCK203

## 2 Concepts

Figure 2 shows the block control structure of the IRMCK203.

## 2.1 Regulators

#### 2.1.1 Closed Loop Current Control

Two Proportional plus Integral (PI) type current regulators with output limits and Anti-windup control are provided for torque and flux regulation of motors. Torque current reference is supplied by Speed regulator output and Flux current reference is set to zero in order to achieve the maximum torque per ampere for a Surface-Mounted Permanent Magnet motor. The current regulator outputs are modulation depths. The modulation depths are fed to a Space Vector PWM modulator via a vector rotator (converts dc to ac waveform). Refer to Appendix A for a description of the Space Vector PWM module.

#### 2.1.2 Closed Loop Velocity Control

A PI speed regulator with output limits (torque current limit) and Anti-windup control is provided for speed regulation. The speed reference is supplied by the Ramp block (as shown in Figure 2). Both speed acceleration rate and deceleration rate can be adjusted. In addition, the Ramp block provides minimum speed protection in order to ensure optimal speed control performance for Sensorless operation. The Ramp block input is the user-desired speed reference which can be obtained internally from the host register interface or externally via the A/D interface as shown in Figure 2. Details on how to set up external speed control mode (Standalone mode) are provided in Section 3.2.

Figure 2. Detailed Control Structure

#### 2.1.3 Rotor Angle Estimation

Motor shaft angle information is required for high performance control of Permanent Magnet motors. The IRMCK203 Sensorless control IC contains a motor shaft angle estimator, which provides shaft angle and motor speed information. There is no need for encoder or hall sensor element feedback.

#### 2.1.4 Start-Stop Sequencer and Fault Detection

A Start-Stop sequencer provides total drive sequencing for handling start-stop and start-up failure retry functions. There are various fault triggers (detailed in Section 2.6) to ensure that the drive is protected under various fault conditions.

#### 2.2 Current Feedbacks

#### 2.2.1 Using IR2175

Two channels of current feedback interface logic are provided in the IRMCK203. Each module measures the incoming varying duty period of the 130 kHz carrier frequency signal at the IR2175 output. Measurement is performed for both carrier frequency period and on duty period at the same time using fast counters. Counting frequency is 133 MHz with a 33.3 MHz system clock.

The IR2175 is the unique high voltage IC capable of measuring the motor phase current through an associated shunt resistor, which can generate  $\pm 260 \text{mV}$  voltage range. The output of the IR2175 is an open drain with a 130 kHz fixed carrier frequency where the duty variance is linearly proportional to  $\pm 260 \text{ mV}$  input voltage. The counting frequency is 133.3 MHz when the system clock crystal frequency is 33.3 MHz, which yields 10-bit resolution of the current measurement data from the IR2175. A more detailed description of the IR2175 can be found in Appendix B.

#### 2.2.2 Using Inverter Leg Shunt

The IRMCK203 provides another means of current feedback through the use of an ADS7818 (BurrBrown) serial A/D converter. Inverter Leg Shunt (install in Low side) currents can be used instead of IR2175 current feedback for Sensorless motor control. The minimum requirement is two Leg Shunt feedbacks (V and W phases). An application example is given in Section 2.4.2 for interfacing Leg Shunt currents to the IRMCK203 digital control IC.

In the IRMCK203, the selection of current feedback is done via a user configuration parameter (provided in the Motor commissioning tools). The Leg Shunt option is recommended for Inverter switching frequencies less than 10KHz.

#### 2.3 Communication

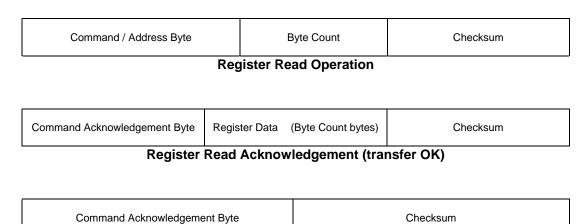

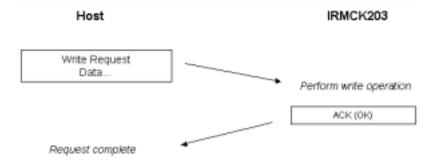

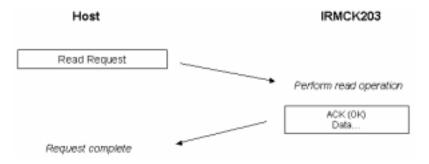

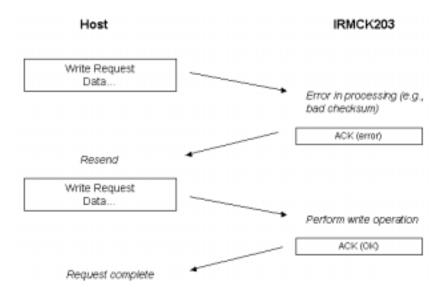

The IRMCK203 contains a rich set of externally addressable "Host" registers documented in Section 4 of this guide. There are three physical interfaces that can access the Host Registers: RS-232, SPI and Host Parallel.

#### 2.3.1 RS-232 Serial Interface

The slowest of the three, the Serial Interface, is used for inter-board communications typically using cables as the connection medium. The IRMCK203 implements an error detecting protocol layer that facilitates maintaining the integrity of the Host Registers. Prior to updating any Host Register, the incoming data must match a checksum string to detect single bit errors. Please refer to the RS-232 protocol documentation in Section 4.1.3 for the specific protocol definition. The RS-232 Serial Interface supports four baud rates based on the signal levels on pins 30 and 42 of the IRMCK203, as shown in Table 1.

| BAUDSEL1<br>PIN 42 | BAUDSEL0<br>PIN 30 | Resulting BAUD Selection |

|--------------------|--------------------|--------------------------|

| 0 or low           | 0 or low           | 19.2 K BAUD              |

| 0 or low           | 1 or high          | 38.4 K BAUD              |

| 1 or high          | 0 or low           | 57.6 K BAUD              |

| 1 or high          | 1 or high          | 1 MEG BAUD               |

**Table 1. BAUD Selection Table**

The RS-232 interface implements a byte serial physical layer in addition to an error checking protocol layer. The coding of the bit-serial data is US ASCII, 8 data bits, 1 stop bit and no parity.

Table 2 describes the physical layer signals of the RS-232 interface.

| Signal Name | Direction | Description                                                               |  |

|-------------|-----------|---------------------------------------------------------------------------|--|

| TX          | Output    | A bit-serial signal originated by the IRMCK203 in response to a           |  |

|             |           | microprocessor-generated request.                                         |  |

| RX          | Input     | Bit-serial data sent to the IRMCK203 by the microprocessor to interrogate |  |

|             |           | one of the Host Registers.                                                |  |

Table 2. External RS-232 Signal Description

#### 2.3.2 SPI Interface

The SPI Interface is also a byte serial interface, but can operate at much greater transfer rates than the RS-232 interface. Bit rates of up to 8 MHz can be achieved. The SPI Interface performs a serial byte read and write in a "full duplex" mode. Refer to the SPI Access documentation in Section 4.1.2 for the protocols required to access the Host Registers, and the SPI timing section of the IRMCK203 datasheet for the physical layer specifications.

Table 3 describes the physical layer signals of the SPI interface.

| Signal Name | Direction | Description                                                         |  |  |

|-------------|-----------|---------------------------------------------------------------------|--|--|

| SPICLK      | Input     | Serial clock generated by the SPI master logic.                     |  |  |

| SPIMOSI     | Output    | Serial data: Master Input and Slave Output.                         |  |  |

| SPIMISO     | Input     | Serial data: Master Output and Slave Input.                         |  |  |

| SPICSN      | Input     | Chip Select signal. Used to qualify the SPICLK, SPIMISO and SPIMOSI |  |  |

|             |           | signals.                                                            |  |  |

Table 3. External SPI I/F Signal Description

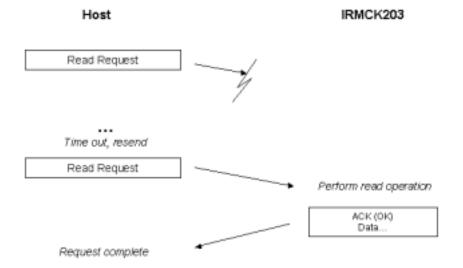

#### 2.3.3 Host Parallel Interface

Designed to transfer bytes in a bit parallel fashion, this is the fastest interface of the three. The Host Parallel interface is compatible with all popular microprocessors, including Motorola and Intel based bus protocols. Refer to the Parallel Access documentation in Section 4.1.1 for the protocols required to access the Host Registers, and the Host Parallel timing section of the IRMCK203 datasheet for the physical layer specifications.

Table 4 describes the physical layer signals of the Host Parallel interface.

| Signal Name | Direction    | Description                                                                                                                                                                                                              |  |

|-------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| HP_nOE      | Input        | When logic low, or 0, indicates the beginning of a parallel data transfer cycle.                                                                                                                                         |  |

| HP_nWE      | Input        | When logic low, or 0, indicates that the data/address transfer cycle is a write cycle, with data being sourced by the microprocessor. When high, the data cycle is a read cycle, with data being sourced by the IRMCK203 |  |

| HP_D [7:0]  | Input/Output | An 8-bit wide data bus.                                                                                                                                                                                                  |  |

| HP_A        | Input        | Address attribute signal. When high, or a logic 1, indicates that the data on the HP_D[7:0] bus is a address to be loaded into the IRMCK203 address register.                                                            |  |

Table 4. External Host Parallel I/F Signal Description

#### 2.3.4 Synchronization of PWM Cycle to an External Microprocessor

A dedicated SYNC signal is provided on the IRMCK203 (pin 52) that allows synchronization of the internal IRMCK203 logic to an external microprocessor. This synchronization is useful when external microprocessor control loops are implemented. Also, an external trace buffer could be implemented to interrogate various nodes in the IRMCK203 while the IRMCK203 is actively controlling the motor.

The SYNC signal has a long pulse width suitable to connect to an edge or level sensitive microprocessor interrupt input pin. The low going edge of this pulse is an indication to the microprocessor that the IRMCK203 is starting a new PWM cycle. Refer to the ADC System Level Timing section of the IRMCK203 datasheet for specific timing information. Both the SPI and Host Parallel Interfaces are suitable for PWM Cycle and trace buffer synchronization.

The SYNC signal offers the microprocessor a timing window to access the entire Host Register set. The number of SYNC pulses per PWM load can be configured using the support tools described in Section 3.

The SYNC pulse width is suitable for connecting opto-isolation circuitry between the IRMCK203 and the microprocessor.

#### 2.4 External Interfaces

This section describes the external interfaces supported by the IRMCK203 in addition to the host register interface described in Section 2.3. These include the discrete I/O interface used for standalone operation and the analog I/O interface provided for diagnostic purposes.

#### 2.4.1 Discrete I/O External Interface

The discrete I/O external interface signals provide a means of controlling basic motor operation without using the host register interface. In this mode of operation, the analog reference (described later in this section) is used to directly control the target speed.

Figure 3 shows a schematic diagram of the discrete I/O signals. The signals are described in Table 5.

Figure 3. Discrete I/O Signals

| Signal Name | Direction | Description                                                                                                                                          |  |  |

|-------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| STARTSTOP   | Input     | Motor start/stop control. A positive edge transition of this signal                                                                                  |  |  |

|             |           | starts the motor and a negative edge transition stops the motor.                                                                                     |  |  |

| DIR         | Input     | Motor direction control. $1 = $ forward, $0 = $ reverse. This signal is                                                                              |  |  |

|             |           | latched when the motor is started, so that changing it while the motor is running has no effect.                                                     |  |  |

| ESTOP       | Input     | Emergency stop. When this signal is set to "1", PWM is                                                                                               |  |  |

|             |           | unconditionally disabled. This signal overrides the START/STOP control                                                                               |  |  |

| FLTCLR      | Input     | A 1 µsec pulse on this signal clears a drive fault condition. Equivalent to setting the FltClr bit of the FaultControl register (see Section 4.2.6). |  |  |

| FAULT       | Output    | This signal indicates the presence of a drive fault condition. The level                                                                             |  |  |

|             |           | is high when any of the bits in the FaultStatus register are set (see                                                                                |  |  |

|             |           | Section 4.3.4).                                                                                                                                      |  |  |

| SYNC        | Output    | This signal is held low for 2 µsec on each PWM period. (The falling                                                                                  |  |  |

|             |           | edge indicates the start of the PWM period.)                                                                                                         |  |  |

Table 5. External Interface Signal Description

**NOTE:** When the ExtCtrl bit in the SystemConfig register is set to "0", the ESTOP and negative edge of the START/STOP signals are functional, but all other external interface signals are inactive.

To configure the discrete I/O interface, write a "1" to the ExtCtrl bit in the SystemConfig host write register to enable the external interface pins. (Refer to Section 4.2.7 for more information about the SystemConfig register.)

#### 2.4.2 Analog I/O Interface

IRMCK203 provides analog input capability through the use of the ADS7818 A/D converter and MUX circuitry. The intended inputs are speed reference, dc bus voltage and two Inverter Leg Shunt currents.

#### **Analog Input**

Figure 4 shows the typical hardware configuration for the analog input interface. The multiplexor input A0 (shown on the diagram) accepts voltages in the range 0 - 5V, with two possible mappings:

- 2.5V = zero speed (0 digital count), 0V = max speed (16, 383 digital count)

- 2.5V = zero speed (0 digital count), 5V = max speed (16, 383 digital count)

The example implements the first of the two mappings (0V max speed), supplying a +15 volt analog reference for an external variable resistor. (The DIR signal controls the motor direction, as described in Table 5.)

In this example circuit, the IRMCK203 automatically scans through A/D conversion of all four channels at the beginning of each PWM cycle (SYNC output). The v and w phase currents followed by dc bus voltage and speed reference are scanned in. In this example, the dc bus feedback gain is 100 times attenuation. The Leg Shunt amplifier gain for this example is 7.97 and the A/D converter scaling is 4095 digital counts per 5V. This information is required during drive commissioning for scaling of dc bus voltage and current feedback.

Leg Shunt feedback can be eliminated if IR2175 is intended for current feedback. The interface to the IR2175 is straightforward and can be found in the IR2175 data sheet.

Figure 4. Analog Interface Example

#### **Analog Output**

The diagnostic D/A interface provides four sources of diagnostic data and is intended for use with external RC filters for oscilloscope display. The user can select one of four sets of data sources by setting the value of the DacSel register in the D/AConverter write register group (see Section 4.2.14) as shown in Table 6.

| DacSe<br>l<br>Value | Se | elected Data Sources     |  |  |  |

|---------------------|----|--------------------------|--|--|--|

|                     | 0  | Flux                     |  |  |  |

| 0                   | 1  | Rotor angle              |  |  |  |

|                     | 2  | Torque current           |  |  |  |

|                     | 3  | Closed loop status       |  |  |  |

|                     | 0  | DC bus voltage           |  |  |  |

| 1 1                 |    | Alpha voltage            |  |  |  |

|                     | 2  | Torque current reference |  |  |  |

|                     | 3  | Motor speed              |  |  |  |

|                     | 0  | Q-axis command voltage   |  |  |  |

| 2                   | 1  | D-axis command voltage   |  |  |  |

|                     | 2  | Alpha current            |  |  |  |

|                     | 3  | Beta current             |  |  |  |

|                     | 0  | Flux magnitude           |  |  |  |

| 3                   | 1  | Current error at parking |  |  |  |

|                     | 2  | Parking diagnostic flag  |  |  |  |

|                     | 3  | W-phase current          |  |  |  |

Table 6. Analog Output Data Source Selection

Each signal is encoded as a pulse-width modulated 8-bit value output at a frequency of 128 KHz. Therefore, hardware filtering is required to require to extract the actual signal. The data values are updated on each sync pulse. The values for each data source are scaled so that the valid range is represented as an 8-bit unsigned value. For

example, the values of Q-axis and D-axis command voltage, which have an actual range of -16,384 to 16,383, are rescaled to the range 0-255 (so that 0 represents -16,384 and 255 represents 16,383).

## 2.5 Sequencing Control

Sequencing control is provided in the IRMCK203 system to facilitate basic I/O sequencing. The signals shown in Table 7 can be directed either by local discrete I/O pins or the host register interface. STOP is always activated by either the host interface register or the local START/STOP input pin.

| Signal                                                        | Description                                                                     |  |  |

|---------------------------------------------------------------|---------------------------------------------------------------------------------|--|--|

| START                                                         | Start motor signal from host or external user interface.                        |  |  |

| STOP Start motor signal from host or external user interface. |                                                                                 |  |  |

| ESTOP                                                         | This signal, which is not shown in figure 1, stops the motor unconditionally    |  |  |

|                                                               | regardless of the state.                                                        |  |  |

| FAULT                                                         | Indicates a pending FAULT condition. It is cleared upon FLTCLR assertion.       |  |  |

| FLTCLR                                                        | Clear pending FAULT.                                                            |  |  |

| Start OK                                                      | Signal from startup control module that indicates a successful startup occurred |  |  |

| Startup Fault                                                 | Indicates a failed startup attempt occurred                                     |  |  |

| Retries                                                       | Running count of the number of retries attempted during the startup sequence.   |  |  |

| Max Retries                                                   | User programmable register setting indicating the maximum number of retries.    |  |  |

|                                                               | The maximum value of retries can be 16. Retry is disabled when this value is 0. |  |  |

| Overvoltage                                                   | Fault conditions.                                                               |  |  |

| Undervoltag                                                   |                                                                                 |  |  |

| e                                                             |                                                                                 |  |  |

| Overcurrent                                                   |                                                                                 |  |  |

| Overspeed                                                     |                                                                                 |  |  |

Table 7. Sequencing Control Signals

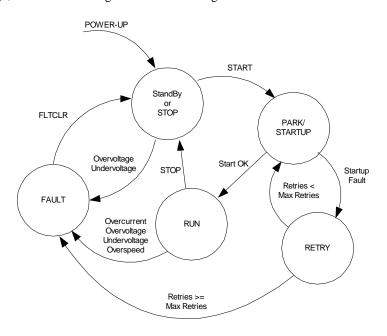

Internally, the IRMCK203 has three states: Stand-By or STOP state, RUN state, and FAULT state. Transitioning to each state can be caused either by initiation of the I/O pins described above or internal drive conditions such as overcurrent, overvoltage, etc. The state diagram is shown in Figure 5.

Figure 5. State Diagram and Sequencing

## 2.6 Fault Handling

The IRMCK203 system has built-in drive fault and protection features. Table 8 summarizes the types of drive fault conditions.

| Fault                           | Status indication on<br>Host Register<br>Interface   | Description                                                                                                                                                                                                                         |

|---------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Overcurrent<br>/Overtemperature | FltStatus Read<br>Register, field<br>GatekillFlt = 1 | Overcurrent or overtemperature occurred. The IGBT gate driver (IR2136) disables gate drive outputs, momentarily latches a fault condition and asserts GATEKILL to the IRMCK203. This activates the fault latch inside the IRMCK203. |

| Overvoltage                     | FltStatus Read<br>Register, field<br>OvFlt = 1       | Overvoltage of the DC bus occurred. Only the fault latch inside the IRMCK203 is activated.                                                                                                                                          |

| Overspeed                       | FltStatus Read<br>Register, field<br>OvrSpdFlt = 1   | The speed of the motor exceeded the maximum speed. Only the fault latch inside the IRMCK203 is activated.                                                                                                                           |

| Overrun                         | FltStatus Read<br>Register, field<br>ExecTmFlt = 1   | The computation of algorithm exceeded the selected PWM carrier frequency period. Only the fault latch inside the IRMCK203 is activated.                                                                                             |

| Low voltage                     | FltStatus Read<br>Register, field<br>LvFlt = 1       | The bus voltage dropped below a certain level (determined by the dc bus feedback scaling). Only the fault latch inside the IRMCK203 is activated.                                                                                   |

| Zero speed                      | FltStatus Read<br>Register, field<br>ZeroSpdFlt = 1  | When speed is less than MinSpd/2 (half minimum speed) for a continuous period of 2 seconds, the zero speed fault occurs. Only the fault latch inside the IRMCK203 is activated.                                                     |

| Startup retry failure           | FltStatus Read<br>Register, field<br>RetryFlt = 1    | After a configured number of start-up failures (determined by register NumRetries in the StartupRetrial write register group), this fault occurs. Only the fault latch inside the IRMCK203 is activated.                            |

| Phase loss                      | FltStatus Read<br>Register, field<br>PhsLossFlt = 1  | This fault indicates that the drive to motor phase connection may be loose. Only the fault latch inside the IRMCK203 is activated.                                                                                                  |

|                                 |                                                      |                                                                                                                                                                                                                                     |

Table 8. Drive Fault Conditions

When any drive fault occurs, the PWM output is disabled and the gate signals from the IRMCK203 device are negated. This condition remains latched until Fault\_Clear action is undertaken by the user. Fault\_Clear, a level sensitive signal event, can be initiated either through the FltClr bit in the FaultControl host register or the FLTCLR discrete I/O external interface pin. For more information about the FaultControl and FaultStatus registers, refer to Sections 4.2.6 and 4.3.4, respectively.

When a fault occurs, the LED indication is as follows: REDLED = 1, GREENLED = 0.

#### 2.6.1 Gatekill Structure and Overcurrent/Overtemperature Fault

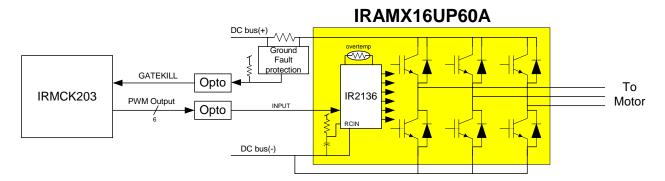

For example, the IRMCS2031 design platform for IRMCK203 has an advanced intelligent power module (IRAMX16UP60A) rated at a 600V/16A. This IGBT module contains an integrated high voltage gate drive IC (IR2136) with a thermistor.

A ground fault protection circuit is also equipped on the IRMCS2031. The signal is fed to an opto-coupler device to trigger the signal to IRMCK203 pin 37, GATEKILL.

When an overcurrent condition occurs, GATEKILL is asserted and momentarily latched within the IR2136 for the programmed period, which is approximately 9 milliseconds. After this period, the pending fault is automatically cleared. Meanwhile, the triggered GATEKILL assertion latches and inhibits all PWM output gate signals off the IRMCK203 until the user initiates a FAULT CLEAR action.

Figure 6. Protection Circuit Block Diagram

Figure 6 shows the protection circuit diagram. The IGBT module contains an RC circuit connected to RCIN input of the IR2136, which automatically initiates FAULT CLEAR in 9 milliseconds after assertion of FAULT. The IGBT module also contains an overtemperature protection circuit, which shuts down all IGBTs and performs automatic FAULT CLEAR as well. Overtemperature protection can be enabled by adding a 6.8 kOhm external resistor. The threshold level is set at approximately 110°C. The IRMCS2031 contains the ground fault protection circuit on the high side DC bus (+) node. The circuit senses positive ground fault current and sends a trigger signal to GATEKILL via a wired-OR FAULT signal.

Once any fault condition is detected, the IR2136 inside of the IGBT module momentarily latches the condition and initiates FAULT output and shutdown of all six IGBTs. Upon receiving the FAULT signal at its GATEKILL input, the IRMCK203 disables all PWM gate signals and latches GATEKILL. It also disables PWM output.

To reset a fault condition, first write a "1" to the "FltClr" bit of the Fault Control register (see Section 4.2.6). This clears the fault in the IRMCK203. Then write a "0" to the FltClr bit to re-enable fault processing. Note that PWM output does not automatically restart after a fault condition is cleared.

#### 2.6.2 DC Bus Faults and DC Bus Braking

The DC bus signal is employed for dc bus overvoltage, undervoltage protection and Brake control. It is also used for compensation of motor controller scaling internal to the IRMCK203.

It is crucial to design a suitable dc bus feedback scaling for proper drive protection. The dc bus voltage can be acquired via the ADS7818 A/D converter. The input of ADS7818 maps 0 - 5 Volts into 0 - 4095 digital counts. The overvoltage and undervoltage trip levels are given in Table 9. The analog scaling (amplifier gain) of the dc bus is restricted by the desired voltage trip levels. Therefore, the signal conditioning (amplifier gain) of dc bus voltage feedback needs to be considered carefully.

|                          | Dc bus feedback<br>IRMCK203<br>internal digital<br>counts (Fixed) | ADS7818<br>input<br>voltage | Actual DC bus voltage (assumption: amplifier gain 1/100) |

|--------------------------|-------------------------------------------------------------------|-----------------------------|----------------------------------------------------------|

| Overvoltage trip fault   | 3360                                                              | 4.1 V                       | 410V                                                     |

| Undervoltage trip fault  | 976                                                               | 1.2 V                       | 120V                                                     |

| Undervoltage clear level | 1152                                                              | 1.4 V                       | 140V                                                     |

Table 9. Overvoltage and Undervoltage Trip Levels

Some applications may require power regeneration. Under such circumstances, an external braking circuit (for dynamic braking) can be used to absorb regeneration energy from the motor. The IRMCK203 provides braking control. The braking control utilizes dc bus voltage feedback to determine when to activate and release the braking circuit. The dynamic braking voltage level is given in Table 10. The analog scaling (amplifier gain) of the dc bus presets the brake on-off levels.

| Brake<br>Condition | Dc feedback digital counts (Fixed) | ADS7818<br>Input voltage | Actual DC bus voltage (assumes amplifier gain 1/100) |

|--------------------|------------------------------------|--------------------------|------------------------------------------------------|

| Brake turn on      | 3120                               | 3.8 V                    | 380V                                                 |

| Brake turn off     | 2944                               | 3.6 V                    | 360V                                                 |

Table 10. Dynamic Braking Voltage Levels

#### 2.7 LED Modes

The operating state of the IRMCK203 is indicated by the LED module. There are three indication modes. Mode 1 indicates successful configuration of the IRMCK203. The LED is green in this mode. Thus, a green LED appears automatically right after power up.

A red LED indicates a drive fault condition. This is Mode 2.

The LED is not lit in Mode 3. This is a hardware fault condition. This means that either configuration data was not transferred to IRMCK203 correctly or the IRMCK203 itself has a hardware problem.

| Mode   | LED Indication | Description                                                                                                                           |

|--------|----------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Mode 1 | Green          | IRMCK203 configuration has been done correctly and IRMCK203 is functioning                                                            |

|        |                | normally.                                                                                                                             |

| Mode 2 | Red            | A drive fault condition is pending.                                                                                                   |

| Mode 3 | Off            | IRMCK203 is not functioning indicating either configuration is not completed correctly and/or IRMCK203 has a hardware problem itself. |

Table 11. LED Modes

## 3 Motor Start-up Supporting Tools

## 3.1 Start-up Flow

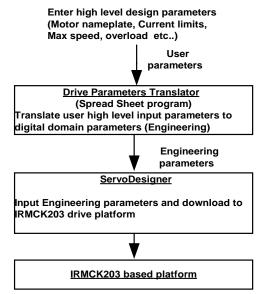

After peripheral circuitry has been implemented for the control IC, a Start-up procedure is provided to guide the user through the commissioning of the user's motor application. Configurable parameters are required to tailor the design to various applications (motor and load). These configurable parameters can be modified via the host register interface (using the ServoDesigner tool) through the communication interface. A design Spreadsheet (Drive parameters translator) is provided to aid the user for ease of drive start-up. Using the Spreadsheet, the user enters high-level parameters such as motor nameplate information, maximum application speed, current limit, speed and speed regulator bandwidth. This high-level user information is translated to engineering parameters (directly used by the drive). Figure 7 gives an overview of the commissioning steps.

Figure 7. Overview of Drive Commissioning

#### 3.1.1 Drive Parameter Setup

The IRMCK203 support software includes an Excel workbook file that partially automates the procedure of calculating the appropriate values for configuration and tuning parameters. In the workbook, the user enters motor nameplate data and parameters specific to his application, and Excel formulas calculate the appropriate values for certain write registers. In Excel, the "Save As..." function is used to export the register values to a text file, and in ServoDesigner, the text file can be imported to fill in the register values. Then, when the Configure Motor function is executed in ServoDesigner, the values are written to the IRMCK203 based platform.

#### The Excel Workbook File

The Excel workbook file is named IRMCS2031-DriveParams.xls. Double click the file to open it in Excel.

At the bottom of the workbook window, there are two sheet tabs, which select the worksheet to be displayed. The first tab selects the "User Entries" worksheet used to set up motor and application parameters. This sheet is preinitialized with values appropriate for the Sanyo Denki 400W 3000rpm motor and is provided as an example. The "User Entries" worksheet can be customized for any motor. To calculate settings for more than one motor, make copies of the IRMCS2031-DriveParams.xls file and modify each copy to define a different motor.

The second tab is labeled "Parameter Export." This worksheet shows the calculated write register values and is the sheet that needs to be exported for use in ServoDesigner.

#### **Enter Motor and Application Parameters in Excel**

The first stage of configuring drive parameters involves entering the correct settings for a specific motor and custom application requirements.

#### Step 1. Initialize a motor setup sheet for the motor.

Click on the "User Entries" sheet tab to select the motor setup worksheet. If desired, double-click the sheet tab and change the tab title to identify the motor. The first line of the motor setup worksheet describes the motor. Double click on column B and enter a description of the motor. (The description is optional; it's not used in the calculations and is not exported to ServoDesigner.)

#### **Step 2.** Enter Motor Information.

The motor information section of the "User Entries" worksheet contains parameter settings that should be available in the motor's datasheet or on its nameplate. To enter a value for each parameter, double click in column B on the same line as the parameter name. When the mouse is moved over column B for each parameter, a short description of the parameter is shown in a help bubble.

|     | Α                                        | В           | С             | D  | Е |  |  |  |

|-----|------------------------------------------|-------------|---------------|----|---|--|--|--|

| 1   | Motor:                                   | Sanyo Denki | P30B06040D>   | (3 |   |  |  |  |

| 2   |                                          |             |               |    |   |  |  |  |

| 3   | "============ Motor Information ======== |             |               |    |   |  |  |  |

| 4   |                                          |             |               |    |   |  |  |  |

| 5   | Hz =                                     | 200         | Hz            |    |   |  |  |  |

| - 6 | RPM=                                     | 3000        | rpm           |    |   |  |  |  |

| - 7 | Lq=                                      | 0.006       | Н             |    |   |  |  |  |

| 9   | R_Stator =                               | 1.6         | ohms/ph       |    |   |  |  |  |

| 10  | Amps =                                   | 2.7         | Arms          |    |   |  |  |  |

| 11  | Inertia =                                | 1.76E-03    | Kg-m2         |    |   |  |  |  |

| 12  | Kt                                       | 0.525       | N-m/Arms      |    |   |  |  |  |

| 13  | Ke                                       | 18.78       | V In-rms/krpm |    |   |  |  |  |

| 14  | Poles                                    | 8           |               |    |   |  |  |  |

| 15  |                                          |             |               |    |   |  |  |  |

Figure 8. Motor Information in User Entries Worksheet

More detailed descriptions are provided below.

Hz The rated frequency of the motor (in Hertz).

RPM The rated speed of the motor (in RPM).

Lq Motor per phase inductance (in Henry).

R\_Stator Per phase resistance of the motor plus cable (in ohms).

Amps The rated current of the motor (in Amps rms).

Inertia Total inertia (motor inertia plus load in Kg-m²). If total load inertia is not specified in the available design data, use a best estimate and adjust the value later when fine-tuning drive operation (refer to Section 3.1.2).

**Kt** Motor torque constant (in Newton-Meter per Amps rms).

Ke

Motor voltage constant (in line-to-neutral rms volts per thousand rpm). Note that some motor manufacturers provide data in line-to-line rms volts, in which case the value must be converted to line-to-neutral voltage.

**Poles**

The number of motor poles.

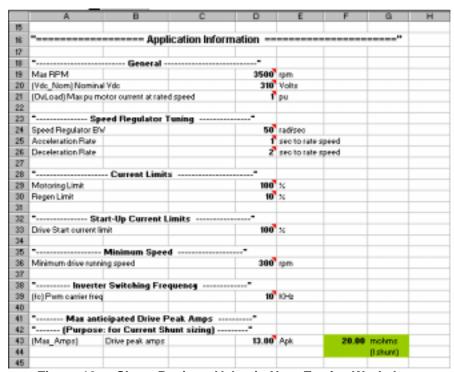

#### **Step 3.** Enter Application Information

The application information section of the "User Entries" worksheet contains parameter settings that describe the requirements of a specific application. The parameters are described below. To enter a value for each parameter, double click in column D on the same line as the parameter name.

|    | A                    | В                     | С              | D        | E                |

|----|----------------------|-----------------------|----------------|----------|------------------|

| 15 |                      |                       |                |          |                  |

| 16 | "=====               | ====== Appli          | cation Informa | tion === |                  |

| 17 |                      |                       |                |          |                  |

| 18 | "                    | General               | "              |          |                  |

| 19 | Max RPM              |                       |                | 3500     | rpm              |

| 20 | (Vdc Nom) Nomina     | al Vdc                |                |          | Volts            |

| 21 | (OvLoad) Max pu n    | notor current at rate | ed speed       | 1        | pu               |

| 22 |                      |                       |                |          |                  |

| 23 | " Spee               | d Regulator Tunir     | ıg"            |          |                  |

| 24 | Speed Regulator B    | w                     |                | 50       | rad/sec          |

| 25 | Acceleration Rate    |                       |                | 1        | sec to rate spee |

| 26 | Deceleration Rate    |                       |                | 1        | sec to rate spee |

| 27 |                      |                       |                |          |                  |

| 28 | " C                  | urrent Limits         | "              |          |                  |

| 29 | Motoring Limit       |                       |                | 100      | %                |

| 30 | Regen Limit          |                       |                | 20       | %                |

| 31 |                      |                       |                |          |                  |

| 32 | " Start-             | Up Current Limits     | "              |          |                  |

| 33 | Drive Start current  | limit                 |                | 100      | %                |

| 34 |                      |                       |                |          |                  |

| 35 | " Mi                 | nimum Speed           | "              |          |                  |

| 36 | Minimum drive run    | ning speed            |                | 300      | rpm              |

| 37 |                      |                       |                |          |                  |

| 38 | " Inverter           | Switching Freque      | ncy"           |          |                  |

| 39 | (fc) Pwm carrier fre | q                     |                | 10       | KHz              |

| 40 |                      |                       |                |          |                  |

| 41 | " Max antici         | pated Drive Peak      | Amps"          |          |                  |

| 42 | " (Purpose: 1        | for Current Shunt     | sizing)"       |          |                  |

| 43 | (Max_Amps)           | Drive peak amps       |                | 13.00    | Apk              |

| 44 |                      |                       |                |          |                  |

| 45 | "                    | Stopping Mode         | "              |          |                  |

| 46 |                      |                       |                | 1        | 0 - Coast Stop   |

| 47 |                      |                       |                |          | 1 - Ramp Stop    |

Figure 9. Application Information in User Entries Worksheet

**Max RPM**

This is the maximum speed (in rpm) required for the application. When motor speed exceeds this value, the system will generate an Overspeed trip fault. It is suggested that this value be set to the rated speed of the motor plus 20 percent.

Nominal Vdc Nominal DC bus voltage (in volts). For use with the IRMCS2031 development

platform, the nominal dc bus voltage should be set to 1.414  $\ast$  ac input voltage ( ac

input voltage: USA 110V, JAP 100V, UK 220V etc.).

**Max overload current** This is the anticipated maximum current in per unit drawn by the motor at the

motor's rated speed. Setting this parameter to 1 pu means that the system drives

100% rated current at the rated speed.

**Speed Regulator BW** Speed regulator bandwidth (in rad/sec). The system may not tolerate high speed

regulator bandwidth (due to mechanical coupling, gear box etc.), resulting in load mechanical resonance. If the correct setting for this parameter is not known, start with a value of 10 rad/sec and raise it gradually as the system is tuned.

Typical values would range between 10 and 25 rad/sec.

Acceleration Rate This parameter defines the number of seconds required for the motor to accelerate

from 0 speed to the motor's rated speed.

**Deceleration Rate** This parameter defines the number of seconds required for the motor to decelerate

from rated speed to 0 speed.

**Motoring Limit** Positive torque current limit (in percentage of rate current). Motoring power is

energy transferred from the inverter to the motor while the motor is running.

**Regen Limit** Negative torque current limit (in percentage of rate current). Regenerative

energy is transferred from the motor to the inverter when the motor decelerates. If the system does not contain a breaking resistor to absorb the regenerative energy, an increase in DC bus voltage (and potential trip fault) results. This parameter should be set to zero if the system cannot absorb regenerative power,

which is the case for the IRMCS2031 development platform as shipped.

**Drive start current limit** Drive start-up current. During initial drive start-up, this current limit will be

applied to ensure robust start-up. Input as percentage of rated motor current.

**Minimum running speed** This is the minimum allowable operating speed for the Sensorless drive. Typical

values range between 5% and 10% of rated motor speed.

**Pwm carrier freq** PWM carrier frequency. 10 KHz is the default setting for the IRMCS2031 product.

The setting of this parameter is a tradeoff between current ripple, inverter loss and

EMI noise.

**Drive peak amps**This parameter defines the anticipated maximum drive current. This parameter

should be chosen to accommodate the anticipated full current range. The current feedback resolution will degrade as a consequence of using a higher drive peak amps value. Therefore, it is best to choose the minimum value that satisfies the requirements of the application. It may be necessary to change the current feedback shunt resistor on the IRMCS2031 development platform to conform to the setting of this parameter. A shunt value calculated and displayed on the worksheet to the right of the Drive peak amps entry (column F) shows the recommended resistor value. It may be necessary to adjust the setting of the Drive peak amps parameter slightly to obtain a shunt recommendation that

corresponds to a commercially available resistor value (1% or less tolerance recommended).

#### **Stopping Mode**

The drive stopping mode can be configured using this parameter.

Coast Stop (enter 0): when stop command is issued, the inverter will switch off immediately. The motor speed will be decreased by windage and friction.

Ramp Stop (enter 1): When stop command is issued, the inverter will control the motor speed down to zero. The rate of stopping is determined by the setting of deceleration rate and Regen current limit.

Note: Ramp stop will regenerate energy back to the dc bus, hence will increase dc bus voltage during fast deceleration, please ensure brake is installed if Ramp stop mode is used.

#### **Step 4.** Enter Advance Information (Hardware Dependent)

The advanced information section of the motor setup worksheet contains parameter settings that are specific to the hardware platform. It is not necessary to modify these settings for use with the IRMCS2031 development platform.

|               | Advance Inform | nation (Hardwa  | re depende   | nt) ==== |           | =" |

|---------------|----------------|-----------------|--------------|----------|-----------|----|

|               |                |                 |              |          |           |    |

|               |                | Dead Time(usec) | dc bus Scale | I Shunt  | Amp. gain |    |

| RMCS2031 v1.0 | (ASIC)         | 0.5             | 8,1900       | 0        | 7.9705    |    |

|               | 1              |                 |              |          |           |    |

Deadtime

This parameter sets the inverter dead time delay. The enter unit is in usec. The setting depends on what type (IGBT, MOSFET etc..) of main power switches being used in the inverter. Users should refer to the Deadtime value suggested by the power device manufacturer.

Dc Bus Scale

This is the dc bus scaling in digital counts per volt of dc bus. The information is the hardware scaling of dc bus feedback. For instance: if user's hardware scales down the dc bus 100 times, then at 500 V dc bus level, 5V will appear at the A/D converter (ADS7818) input. The ADS7818 maps 5V (at Vcc = 5) to 4095 digital counts. Therefore, the Bus scaling is 4095/500 = 8.19 cts/V.

I Shunt

This parameter provides current feedback selection. Please enter "0" if using IR2175 , "1" if using Inverter Leg Shunt

**Amp Gain**

This parameter is only required if Leg Shunt is selected as the current feedback choice, and specifies the amplifier gain from Leg shunt sampling resistor to input of A/D converter. For instance, in the hardware example given in Section 2.4.2, the Leg shunt amplifier gain is 7.97.

#### **Export Drive Parameters in Excel**

In the second stage of configuring drive parameters, the parameter settings selected in the previous section are used to calculate values for a number of IRMCK203 write registers. The write register values are written to a text file in a specific format defined for use with ServoDesigner.

#### **Step 1.** Note Shunt Resistor Value

At the bottom of the "User Entries" worksheet, note the calculated current feedback shunt resistor value shown in column F (see Figure 10). If the value shown does not correspond to an available resistor, it may be necessary to modify the "Drive peak amps" setting. After modifying the value, check the shunt resistor value again.

Figure 10. Shunt Resistor Value in User Entries Worksheet

#### Step 2. Save the Settings

When all parameters are set appropriately, select Save from Excel's File menu to save the workbook file in ".xls" format.

#### **Step 3.** Export Drive Parameters

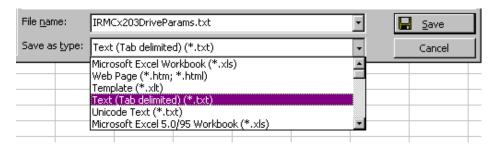

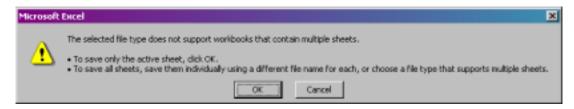

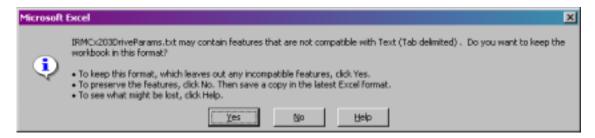

Click on the Parameter Export tab at the bottom of the workbook window. This worksheet shows the register values that were calculated settings were changed in the motor setup worksheet. From Excel's File menu, select "Save As...". In the Save As dialog, select Save as type: "Text (Tab delimited) (\*.txt)" as shown below. Then browse to the folder where the exported drive parameters file is to be saved, specify a file name, and click Save.

Click OK when the following warning message appears:

Click Yes when this warning message appears:

#### **Import Drive Parameters in ServoDesigner**

The final stage of drive parameter configuration involves loading the drive parameter settings into a ServoDesigner database and writing the registers to the IRMCK203. For information about how to use ServoDesigner, refer to the ServoDesigner User's Guide. In particular, Section 10.3 of that document describes the Import Drive Parameters feature.

The text file exported from the Excel workbook contains two sections: Parameters and Registers.

#### **The Parameters Section**

The Parameters section specifies motor configuration parameters, which are saved in the ServoDesigner configuration file (.irc file). In ServoDesigner, the settings can be viewed and modified by selecting Motor Configuration from the Preferences menu. When the drive parameters text file is imported into ServoDesigner, the motor configuration parameters in the import text file always replace the current settings in the ServoDesigner database.

#### The Registers Section

Each of the entries in the Register section of the file identifies a write register and a value to be stored in the register. In a ServoDesigner database, there are several locations where each register value can be used:

- In the register definition, the Value to Write is written to the corresponding IRMCK203 register when the register entry is double clicked.

- Also in the register definition, the EEPROM Value to Write can be saved to EEPROM and used to initialize the IRMCK203 register on power up.

- In the Function Definitions section, one or more functions may write the register value to the IRMCK203. (A function is set up to perform a sequence of operations automatically.)

When the drive parameters text file is imported into ServoDesigner, there are several options for updating any or all of these register settings with the value specified in the file.

#### Step 1. Run ServoDesigner and Open a Database

Start ServoDesigner and select Open from the File menu. ServoDesigner configuration files have the file extension ".irc". Browse to locate a ServoDesigner configuration file and open it. (To create a custom configuration file to use with a specific project, it's best to make a copy of the example file included with the release.)

#### **Step 2.** Import Drive Parameters

From the File menu, select Import, and from the Import sub-menu, select Drive Parameters. Browse to locate the text file that was exported from Excel and click Open to open it. In the Import Drive Parameters dialog, select one of the three available modes and click OK. Depending on the selected mode, ServoDesigner may prompt for confirmation before modifying each register setting or group of settings. Refer to the ServoDesigner User's Guide for more information about the available modes of operation.

#### **Step 3.** Save the New Settings

The Import Drive Parameters function in ServoDesigner updates register values in the database that's currently open. To save the new settings in the configuration file, select Save from the File menu before exiting ServoDesigner. If this is not done, the updates will be lost, and the Import Drive Parameters function will need to be repeated next time the configuration file is opened.

#### Step 4. Write the Settings to the IRMCK203

The Import Drive Parameters function does not write any values to the IRMCK203; it simply updates the register settings in the database. To transfer the register settings to the IRMCK203, it is necessary to either double click each write register individually (not recommended) or execute a function that writes the registers automatically. The Configure Motor function is pre-defined for this purpose. To execute the Configure Motor function, click the Configure Motor icon on the toolbar, or double click Configure Motor in the Function Definitions section of the tree view.

#### 3.1.2 Evaluating Drive Performance

The drive parameter translation as described in the previous section is the first step of drive commissioning. It is expected that the user parameter entries such as motor nameplate information and load inertia will have at least 10% error. This is typical due to the inaccuracy in motor datasheet and load information. The drive performance can be further refined by going through drive diagnostics as described in Section 3.1.3.

For motor control purposes, the rotor angle information is required to optimally control a Permanent Magnet AC motor. In the IRMCK203, the control is performed without a shaft encoder (Sensorless). The rotor angle is estimated utilizing motor phase (V, W) current and DC bus voltage feedback information.

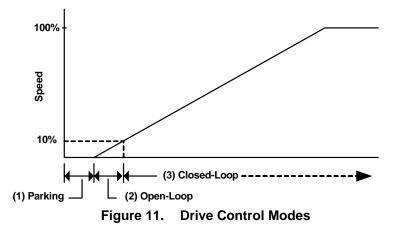

In the IRMCK203 drive controller, there are 3 control modes (Figure 11) for estimation of the rotor angle for the entire speed range including zero speed. During motor start-up phase, the controller will go through these three control modes in sequence. These control modes are described below.

1) Parking – The initial rotor angle is identified by forcing DC current into the motor and hence forcing the motor shaft to park at a certain prescribed angle.

- 2) Open-loop Immediately after Parking stage, the rotor angle is estimated in an open-loop fashion, which utilizes a simple motor-load mechanical model to estimate the rotor angle (estimate load characteristics). If the mismatch between the external load characteristics and the internal motor-load model is exceedingly large, start-up performance will suffer.

- 3) Closed-loop motor speed increases during start-up; the motor voltage also builds up due to the increase in speed. Useful information for rotor angle estimation can be then be extracted from the motor voltage (estimated by using motor current and DC bus voltage). The drive will enter Closed-loop control mode as shown in Figure 11.

#### 3.1.3 Diagnostic Mode Functions

Diagnostic mode functions are provided in the ServoDesigner tool to fine tune drive performance. It is recommended to go through diagnostic mode in the proper order (Parking Diagnostic then Start-up Diagnostic).

Figure 12. Parking Diagnostic Function

#### **Parking Diagnostic**

With the Parking diagnostic (shown in Figure 12), the optimal Parking current (ParkI) and the Parking time duration (ParkTm) can be readily determined. In addition, current controller and current feedback can also be verified.

When the Parking Diagnostic function is executed, the drive is forced to stay in Parking state for five seconds, followed by a stop. The diagnostic can be stopped anytime by executing the Stop Motor function. The characteristic of parking depends on the amount of dc current injection.

It is possible to verify current control by observing the actual current flowing through the motor windings using current sensing instrumentation (current probe). The amount of parking current injected to the motor is controlled by parameter ParkI as shown in Figure 12. The full scale of ParkI is 255 digital counts, which represents 86.7% rated motor current (in peak Amps). During motor parking, dc current is injected (by inverter) into W-phase and V-phase of the motor; the current in U-phase is regulated to zero. For instance, if motor rated current is 2.7Arms, a value of 77 digital counts in ParkI will produce 1 Amp dc current in W-phase (- 1 Amp) and V-phase (+ 1 Amp).

In practice, it is much more than sufficient to park a motor with rated motor current. If an exceedingly large value of ParkI is used, the motor shaft will hunt during parking. This will increase the time for the rotor shaft to settle and hence increase parking time. Systems with a higher inertia to friction ratio will tend to hunt more. Therefore, it is recommended to start with a lower value (say 4% ParkI = 12).

The user can experience the effect of using different ParkI values. It may be noticed that the parking characteristics will also depend on the initial rotor angle (when drive is off). Therefore, the shaft should be rotated (manually, while the drive is off) to a different position before each parking evaluation. It is recommend to use the highest possible value (not to cause excessive motor hunting) of ParkI such that the duration of parking can be minimized. Once the optimal parking current (ParkI) is determined, please note the time required for the motor shaft to settle

during parking. This time duration is the optimal parking time and should be converted to digital drive units and entered into register ParkTm. The full scale of ParkTm is 255, which represents 4 seconds.

After the parking diagnostic has been accomplished, please enter these two parameters (ParkI and ParkTm) into the Sensorless Ctrl Start-up subfunction inside the Configure Motor function, as shown in Figure 13.

Note: To resume normal mode operation (out of diagnostic), the Configure Motor function must be executed again.

Figure 13. Enter Optimal Parking Parameters

#### **Start-up Diagnostic**

This diagnostic mode is provided to fine tune open-loop start-up performance. During open-loop start-up, the IRMCK203 control IC estimates the rotor angle based on a simple motor load model, which uses only one configurable parameter (KTorque). The user parameter translator (Excel spreadsheet) also generates this parameter based on user input load inertia. Use this value as a starting point for fine tuning. The goal of this start-up diagnostic is to fine tune this parameter (KTorque) for optimal open-loop drive control performance. If a correct value of KTorque is used the drive will produce the highest torque per ampere ratio during open-loop start-up. The drive may fail to start if excessive error is present in KTorque gain.

When the Start-up Diagnostic function is executed, the drive will enter parking mode followed by open-loop start-up. The drive will coast to a stop as soon as open-loop is accomplished (determined when motor frequency exceeds the level prescribed by write register WeThr). If an optimal value of KTorque is used, the drive will accelerate the motor to a higher speed since maximum torque per ampere is achieved.

Figure 14. Start-up Diagnostic Function

Users can observe motor shaft movement during the Start-up diagnostic to determine an optimal value of KTorque. As mentioned earlier, when the Start-up diagnostic is initiated, the drive will enter parking mode for 4 seconds; thereafter open-loop start up will be initiated. There will be shaft movement due to parking of the motor during the initial 4 seconds. It is important to observe the shaft movement only in the open-loop startup period. An optimal KTorque value will generate higher starting torque and hence increased motor shaft rotation during open-loop duration.

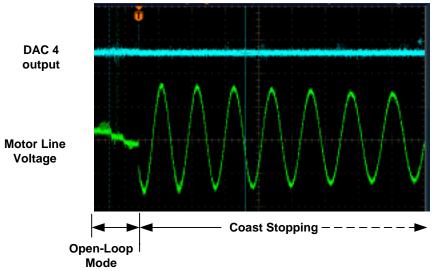

If measurement instrumentation (oscilloscope and voltage probe) is available, it can be used to observe the motor back EMF to determine the optimal KTorque value. The motor back emf is proportional to motor speed. By observing the motor line-line voltage at the end of the open-loop period (indicated by a momentary high pulse on D/A converter channel 4), it is possible to determine an optimum value of KTorque.

Figure 15 and Figure 16 illustrate two example runs of the start-up diagnostic with two different values of KTorque being used. As can be seen in these figures, after open-loop terminates, the speed of the motor coasts down. It is apparent that the KTorque value used in Figure 16 provides higher voltage and frequency; hence the motor speed is also higher.

This document is the property of International Rectifier and may not be copied or distributed without expressed consent.

Figure 16. Open-loop start-up (KTorque = 520)

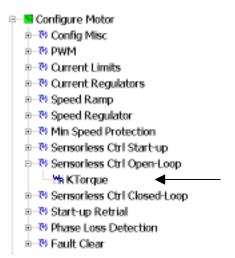

After the optimal value for KTorque has been determined, please enter the value into the Sensorless Ctrl Open-loop subfunction inside the Configure Motor function as shown in Figure 17.

#### **Resume Normal Operation**

After completing the diagnostic tests described in this section, the Configure Motor function must be executed in order to resume normal drive mode.

Figure 17. Enter Optimal KTorque Parameter

#### 3.1.4 Miscellaneous Functions

Miscellaneous functions provided in the ServoDesigner tool are described in this section.

#### **Phase Loss Detection**

This function provides detection (during start-up) of a loose wire (u, v, w) between drive and motor.

During motor parking (first stage of motor startup), a certain amount of dc current is injected into the motor windings for the purpose of initialization of rotor position. If motor feedback currents do not match the expected dc injection current level, a phase loss fault (PhsLossFlt) is triggered. This fault can be disabled via bit 4 (PhsLosFltDisable field) of the MtrCtrlBits write register.

#### **Start-up Retrial**

This function provides start-up retrials upon a start-up failure. Start-up failure may occur if the motor shaft is jammed or motor starting torque cannot overcome shaft friction during startup.

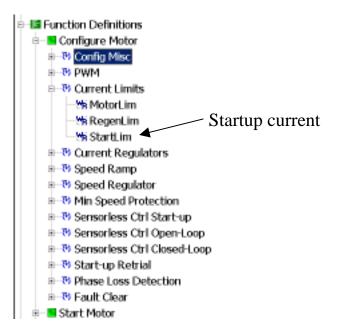

Motor starting torque can be controlled by motor starting current limit (StartLim) as shown in Figure 18. The scaling of StartLim is 4095 = rated motor current.

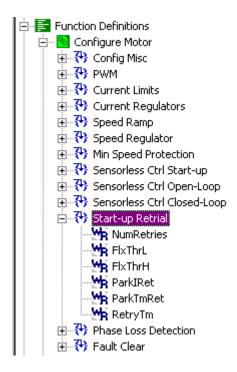

The write registers written on execution of the Startup Retrial function are described below.

The function is shown in

Figure 19.

NumRetries – This parameter determines the number of start-up retries. A value of zero will disable startup retry. The maximum number of retries is 15.

FlxThrL - The low flux threshold level for determining a successful startup (scaling: 129 = 100% flux). Please do not modify this parameter without consulting a motor drive FAE.