# AN1043

### **Unique Features of the MCP23X08/17 GPIO Expanders**

Author: Pat Richards Microchip Technology Inc.

#### INTRODUCTION

GPIO expanders provide easy I/O expansion using standard serial interfaces. GPIO products are used to increase the I/O on an MCU or provide remote I/O using a serial interface.

This application note discusses the feature set and use of the MCP23X08/17 (8-bit and 16-bit) GPIO Expanders.

The MCP23X08 are 8-bit GPIO Expanders:

- MCP23008: I<sup>2</sup>C<sup>™</sup> Interface

- MCP23S08: SPI Interface

The MCP23X17 are 16-bit GPIO Expanders:

- MCP23017: I<sup>2</sup>C Interface

- MCP23S17: SPI Interface

The functions and features of the MCP23X08 and MCP23X17 are basically the same, except where otherwise noted.

#### **FEATURES**

This application note discusses some of the features of the MCP23X08/17 and how they may be used in an application:

- I/O Port Description

- 8/16-Bit Mode (MCP23X17 only)

- Interrupt Features

- Mapping Interrupts

- Mirroring Interrupts (MCP23X17 only)

- Servicing Interrupts

- Internal Address Pointer Control

- Hardware Address Pin on SPI

#### **I/O PORT DESCRIPTION**

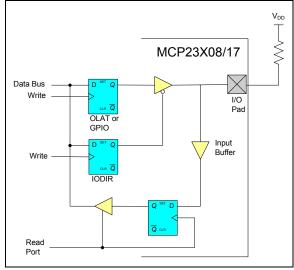

The I/O port is highly configurable for maximum flexibility. Figure 1 is a simplified block diagram of an I/O port pin. The port can either drive logic levels on the pin, or read logic levels from the pad. The level on the pad can be read at any time, regardless if the pin is configured as an input or an output.

The IODIR register controls the direction of the pins (input or output). More specifically, the IODIR registers simply enables/disables the output driver. When the driver is activated (IODIR = 0), the pad is driven to the state in the latch register (OLAT). When deactivated (IODIR = 1), the driver is high impedance.

The I/O port has multiple, individual configurations. Each pin can  $\ldots$

- ... be configured as an input. The output driver is disabled (high impedance)

- ... be configured as an output. The output driver is enabled and the value in the latch is driven on the pin.

- · ...enable a weak pull-up resistor

- ...emulate an open-drain configuration. This is accomplished by clearing the output latch (OLAT) bit to a zero and using the direction register (IODIR) to set the level on the pin. A pull-up resistor is required to pull the pin to voltage when the pin is an input

- To drive a 0: configure the pin as an output (IODIR = 0) so the port drives whatever is in OLAT (logic 0 in this case)

- To float a 1: set the pin as an input (IODIR = 1). The output driver is disabled and the pull-up resistor pulls the pin to a logic 1

#### FIGURE 1: I/O PORT BLOCK DIAGRAM

#### 8/16 BIT MODE (MCP23X17 ONLY)

The MCP23X17 has the unique ability to appear to the MCU as either two (2) 8-bit GPIO expanders, or as a single 16-bit GPIO expander.

This is accomplished by splitting the 16 I/O ports into two separate 8-bit I/O ports (Port A and Port B) via IOCON.bank.

Each port has a group of dedicated registers. Table 1 shows how the register groups (Port A and Port B) are mapped when in 8-bit or 16-bit mode.

| Note: | Unlike all other registers which are not |  |  |  |

|-------|------------------------------------------|--|--|--|

|       | shared between the two ports (Port A and |  |  |  |

|       | Port B), there is one register (IOCON).  |  |  |  |

|       | which is shared between the ports and    |  |  |  |

|       | affects both equally.                    |  |  |  |

#### 8-Bit Mode:

When in 8-bit mode, the ports' registers are separated:

- Port A register addresses range from 00h 0Ah

- Port B register addresses range from 10h 1Ah

#### 16-bit Mode:

When in 16-bit mode, the ports' registers are interleaved to emulate 16-bit wide registers:

Port A and Port B register addresses range from 00h – 15h. The registers are still addressed as 8-bit ports, meaning that the 16-bit mapping pair is always an even number (e.g., IODIR starts at 00h, IPOL starts at 02h, etc.)

#### TABLE 1: MEMORY MAP

| 8-bit M          | ode              | 16-bit Mode      |                  |  |

|------------------|------------------|------------------|------------------|--|

| Register<br>Name | Address<br>(hex) | Register<br>Name | Address<br>(hex) |  |

| IODIRA           | 00               | IODIRA           | 00               |  |

| IPOLA            | 01               | IODIRB           | 01               |  |

| GPINTENA         | 02               | IPOLA            | 02               |  |

| DEFVALA          | 03               | IPOLB            | 03               |  |

| INTCONA          | 04               | GPINTENA         | 04               |  |

| IOCON            | 05               | GPINTENB         | 05               |  |

| GPPUA            | 06               | DEFVALA          | 06               |  |

| INTFA            | 07               | DEFVALB          | 07               |  |

| INTCAPA          | 08               | INTCONA          | 08               |  |

| GPIOA            | 09               | INTCONB          | 09               |  |

| OLATA            | 0A               | IOCON            | 0A               |  |

| IODIRB           | 10               | IOCON            | 0B               |  |

| IPOLB            | 11               | GPPUA            | 0C               |  |

| GPINTENB         | 12               | GPPUB            | 0D               |  |

| DEFVALB          | 13               | INTFA            | 0E               |  |

| INTCONB          | 14               | INTFB            | 0F               |  |

| IOCON            | 15               | INTCAPA          | 10               |  |

| GPPUA            | 16               | INTCAPB          | 11               |  |

| INTFB            | 17               | GPIOA            | 12               |  |

| INTCAPB          | 18               | GPIOB            | 13               |  |

| GPIOB            | 19               | OLATA            | 14               |  |

| OLATB            | 1A               | OLATB            | 15               |  |

#### **INTERRUPT FEATURES**

The MCP23X08 has one interrupt pin and the MCP23X17 has two interrupt pins.

For the MCP23X17, each interrupt pin is associated with an 8-bit port. INTA is associated with Port A and INTB is associated with Port B.

#### **Interrupt Mapping**

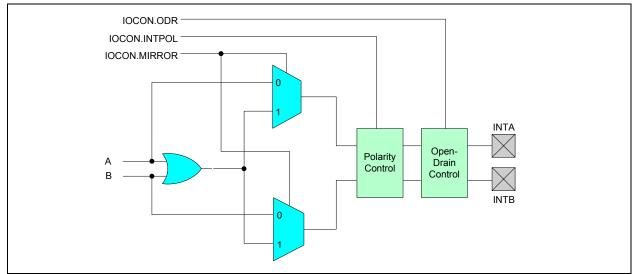

The MCP23X17 interrupt pins can be mapped in two ways (see Figure 2) as controlled by IOCON.MIRROR:

- 1. Interrupt pins operate independently. INTA reflects interrupt conditions on Port A and INTB reflects interrupt conditions on Port B.

- 2. Both interrupt pins go active when an interrupt occurs on either port.

#### **Interrupt Polarity and Open-Drain**

The interrupts can be configured to operate in three modes:

- 1. Active-High.

- 2. Active-Low.

- 3. Open-Drain.

The interrupt polarity and open-drain is configured via INTPOL and ODR bits in the IOCON register.

**Note:** For the MCP23X17, the polarity and opendrain configuration of the INTA and INTB pins are not independent. Both pins are configured the same.

#### **Interrupt Conditions**

There are several configurable interrupt conditions which allow flexible configurations.

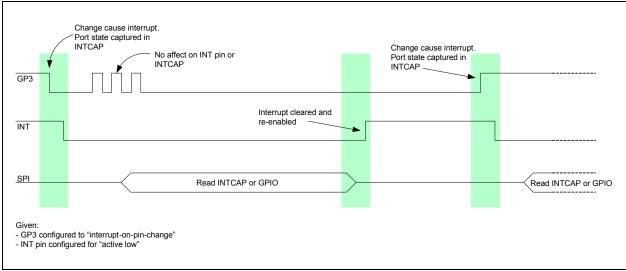

#### INTERRUPT-ON-PIN-CHANGE

Pins configured for **interrupt-on-pin-change** will cause an interrupt to occur if a pin changes to the opposite state. The default state is reset after an interrupt is serviced. For example, an interrupt occurs by an input changing from 1 to 0. The interrupt is then serviced while the pin state is still 0 by reading GPIO or INTCAP register. The **new** initial state for the pin is a logic 0. Likewise, if the pin is toggled back to a logic 1 before servicing the interrupt, the new default state is a logic 1.

The interrupt condition is cleared by reading either INTCAP or GPIO register. The new pin state default is set when the interrupt is cleared.

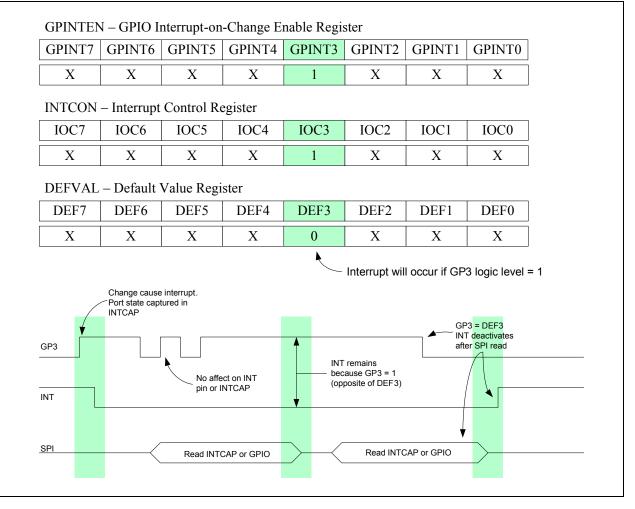

## INTERRUPT-ON-CHANGE FROM DEFVAL REGISTER VALUE

Pins configured for **interrupt-on-change from register value** will cause an interrupt to occur if the corresponding input pin differs from the register bit. The interrupt condition will remain as long as the condition exists, regardless if the INTCAP or GPIO is read.

For example, if DEFVAL<bo> = 0. An interrupt will occur if the pin changes to a logic 1 and the interrupt will remain as long as the pin remains a logic 1. The interrupt condition will clear if the pin changes back to a logic 0 and INTCAP or GPIO is read.

#### FIGURE 2: INTERRUPT BLOCK DIAGRAM

# AN1043

#### FIGURE 3: INTERRUPT-ON-PIN-CHANGE EXAMPLE

#### FIGURE 4: INTERRUPT-ON-CHANGE-FROM-DEFVAL EXAMPLE

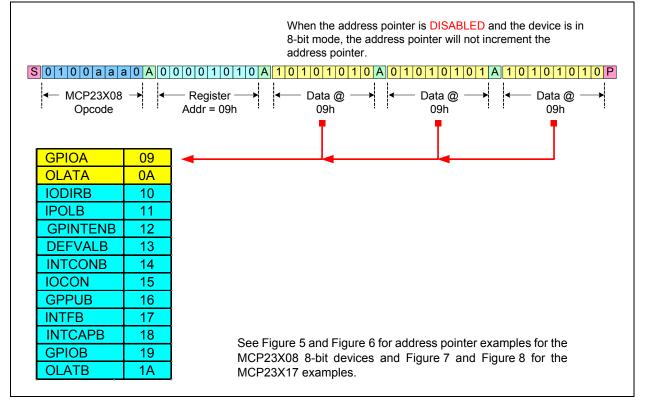

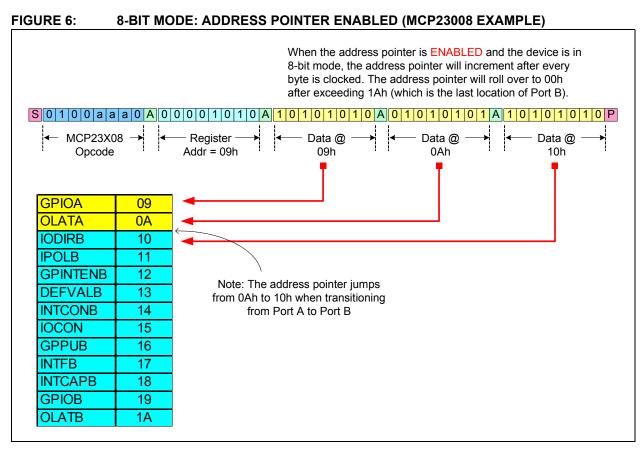

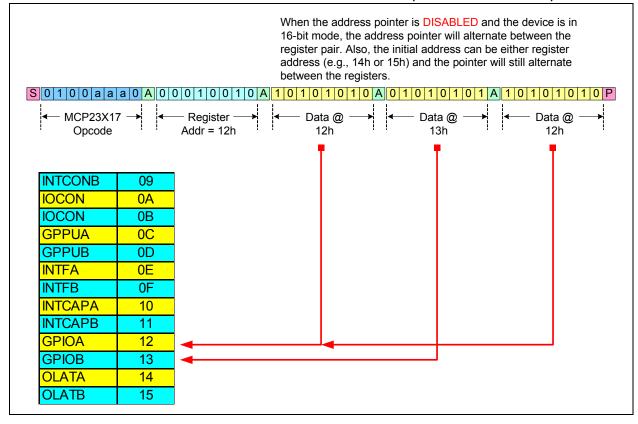

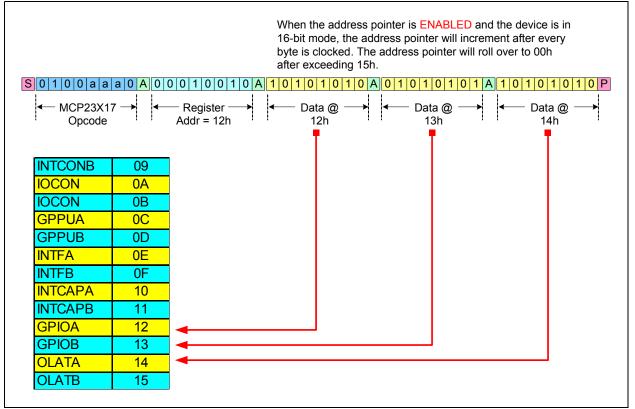

#### INTERNAL ADDRESS POINTER CONTROL

Some slave serial devices automatically increment their internal address pointer after each byte is clocked by the master. This allows the master to sequentially access multiple registers without re-sending the write or read command.

Other slave devices do not automatically increment their internal address pointer.

The MCP23X08/17 family of devices have the ability to do either by configuring a control bit (IOCON.SEQOP). This allows maximum flexibility when accessing the registers.

For example, when configuring the device, it may be desirable to allow the address pointer to automatically increment so the device does not have to be readdressed after every byte.

Likewise, when performing a continuous operation on a register (e.g., changing the outputs on a regular basis by writing to GPIO or OLAT), it may be beneficial to disable the address incrementing feature so that the register is always accessed without re-addressing the register.

#### FIGURE 5: 8-BIT MODE: ADDRESS POINTER DISABLED (MCP23008 EXAMPLE)

# AN1043

#### FIGURE 7: 16-BIT MODE: ADDRESS POINTER DISABLED (MCP23017 EXAMPLE)

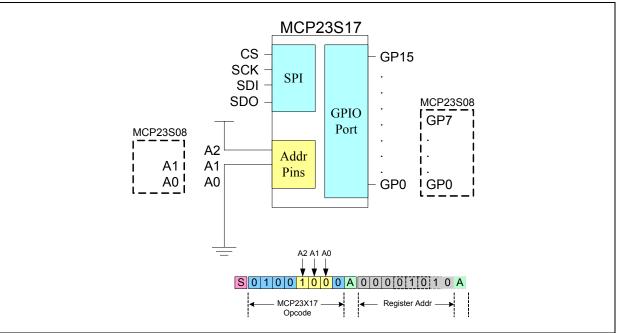

#### HARDWARE ADDRESS PINS

Address pins are typically used on I<sup>2</sup>C devices to allow multiple devices with the same base slave address to operate on the bus.

Slave devices with SPI interfaces typically use only a chip select pin to select the device. This requirement consumes one MCU pin for every SPI device on the bus.

FIGURE 9: ADDRESS PINS ON SPI DEVICES

The "S" devices (MCP23S08 and MCP23S17) have SPI interfaces. These devices use a chip select for selecting the part, however, these parts also have hardware address pins, thereby giving the advantage of attaching multiple devices on the bus while only consuming one MCU pin for chip select (see Figure 9).

#### SUMMARY

The MCP23X08/17 family of GPIO Expanders have some unique features, giving the system and module engineer maximum flexibility when designing with the MCP23X08/17.

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC, and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Migratable Memory, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Linear Active Thermistor, Mindi, MiWi, MPASM, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2006, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona, Gresham, Oregon and Mountain View, California. The Company's quality system processes and procedures are for its PICmicro® 8-bit MCUs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

### WORLDWIDE SALES AND SERVICE

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Habour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

Atlanta Alpharetta, GA Tel: 770-640-0034 Fax: 770-640-0307

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

Dallas Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

San Jose Mountain View, CA Tel: 650-215-1444 Fax: 650-961-0286

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8676-6200 Fax: 86-28-8676-6599

**China - Fuzhou** Tel: 86-591-8750-3506 Fax: 86-591-8750-3521

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

China - Shunde Tel: 86-757-2839-5507 Fax: 86-757-2839-5571

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7250 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-4182-8400 Fax: 91-80-4182-8422

India - New Delhi Tel: 91-11-5160-8631 Fax: 91-11-5160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Gumi** Tel: 82-54-473-4301 Fax: 82-54-473-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

**Malaysia - Penang** Tel: 60-4-646-8870 Fax: 60-4-646-5086

Philippines - Manila Tel: 63-2-634-9065

Fax: 63-2-634-9069 Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-572-9526 Fax: 886-3-572-6459

**Taiwan - Kaohsiung** Tel: 886-7-536-4818 Fax: 886-7-536-4803

**Taiwan - Taipei** Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-3910 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820

06/08/06