# AN10778 PCB layout guidelines for NXP MCUs in BGA packages Rev. 2 — 15 April 2011 Application

**Application note**

#### **Document information**

| Info     | Content                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords | LPC175x, LPC176x, LPC177x, LPC178x, LPC181x, LPC182x, LPC183x, LPC185x, LPC431x, LPC432x, LPC433x, LPC435x, LPC2220, LPC2292, LPC2364, LPC2368, LPC2458, LPC2468, LPC2470, LPC2478, LPC2880, LPC2888, LPC3130, LPC3131, LPC3141, LPC3143, LPC3152, LPC3154, LPC3180/01, LPC3220, LPC3230, LPC3240, LPC3250, LH79524, LH7A400, LH7A404, TFBGA100, TFBGA144, TFBGA208, TFBGA180, TFBGA296, LFBGA208, BGA256, LBGA256, LFBGA256, LF |

| Abstract | This application note is focused on Printed Circuit Board (PCB) layout issues when using (L)(LF)(TF)BGA packages from the NXP LPC Microcontroller family.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

AN10778 **NXP Semiconductors**

### PCB layout guidelines for NXP MCUs in BGA packages

#### **Revision history**

| Rev | Date     | Description                                              |

|-----|----------|----------------------------------------------------------|

| 2   | 20110415 | Added information for LPC1700/1800/4300 LBGA256 package. |

| 1   | 20090122 | Initial release.                                         |

# **Contact information**

For more information, please visit: <a href="http://www.nxp.com">http://www.nxp.com</a>

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

#### PCB layout guidelines for NXP MCUs in BGA packages

#### 1. Introduction

The plastic Ball Grid Array (BGA), including Low-profile Ball Grid Array (LBGA), Low-profile Fine pitch BGA (LFBGA) and Thin-profile Fine pitch BGA (TFBGA) packages have become, for many applications, the first choice for designers requiring medium to high pin-count IC packaging. For this reason many of the LPC Family of Microcontrollers are available in the LBGA, LFBGA or TFBGA package.

When comparing it to other common alternative packages, such as the Quad Flat Pack (QFP), the (L)(LF)(TF)BGA device has many advantages, such as:

- The (L)(LF)(TF)BGA has no easy-to-bend leads that can cause deviation from coplanarity.

- The (L)(LF)(TF)BGA is typically 20 % to 25 % smaller than an equivalently functional QFP.

- Resolution and smearing problems with respect to the stencil-print process are less because the pitch is larger, and the apertures are circular.

- The self-alignment property of the component results in a large process window for automatic placement.

- The (L)(LF)(TF)BGA is compatible with today's assembly techniques, which means that no adjustments are necessary to standard machines or materials.

# 1.1 Scope

The scope of this application note is focused on Printed Circuit Board (PCB) layout issues when using (L)(LF)(TF)BGA packages from the NXP LPC Microcontroller family. Including:

- Recommended footprint patterns for the TFBGA180, TFBGA208, TFBGA296, LBGA256 and LFBGA320 pin packages.

- Recommended trace, space and via size for fan-out routing of the TFBGA180, TFBGA208, TFBGA296, LBGA256 and LFBGA320 pin packages

It is recommended that other assembly topics such as the solder paste chemistry, reflow solder profile and solder paste stencil etching, which are affected by all components on the board level assembly and not limited to the Microcontroller BGA alone, be a collaborative effort between the system designer and the assembly contractor.

# 2. BGA package description

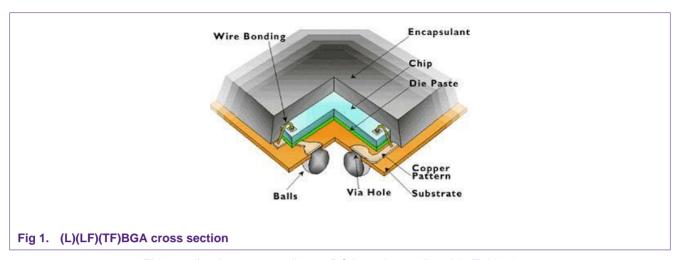

A cross section of the typical (L)(LF)(TF)BGA is shown in Fig 1.

### PCB layout guidelines for NXP MCUs in BGA packages

This application note applies to BGA packages listed in <u>Table 1</u>.

Table 1. BGA packages

| Package name | NXP outline code | Outline dimensions | Ball pitch | Ball diam | Ball configuration      |

|--------------|------------------|--------------------|------------|-----------|-------------------------|

| BGA256       | SOT1018-1[4]     | 17 x 17 x 1.35 mm  | 1.0 mm     | 0.50 mm   | 16 x 16; full matrix    |

| LBGA256      | SOT740-2[6]      | 17 x 17 x 1.55 mm  | 1.0 mm     | 0.50 mm   | 16 x 16; full matrix    |

| TFBGA100     | SOT926-1[2]      | 9 x 9 x 0.7 mm     | 0.8 mm     | 0.45 mm   | 10 x 10; full matrix    |

| TFBGA144     | SOT569-2[2]      | 12 x 12 x 0.7 mm   | 0.8 mm     | 0.45 mm   | 13 x 13; partial matrix |

| TFBGA180     | SOT570-2[2]      | 12 x 12 x 0.8 mm   | 0.8 mm     | 0.45 mm   | 14 x 14; partial matrix |

| TFBGA208     | SOT950-1[2]      | 15 x 15 x 0.7 mm   | 0.8 mm     | 0.45 mm   | 17 x 17; partial matrix |

| LFBGA208     | SOT1019-1[5]     | 14 x 14 x 1.27 mm  | 0.8 mm     | 0.45 mm   | 16 x 16; partial matrix |

| LFBGA256     | SOT1020-1[5]     | 14 x 14 x 1.25 mm  | 0.8 mm     | 0.45 mm   | 16 x 16; full matrix    |

| TFBGA296     | SOT1048-1[1]     | 15 x 15 x 0.7 mm   | 0.8 mm     | 0.45 mm   | 18 x 18; partial matrix |

| LFBGA324     | SOT1021-1[5]     | 17 x 17 x 1.25 mm  | 0.8 mm     | 0.45 mm   | 20 x 20; partial matrix |

| TFBGA208     | SOT930-1[2]      | 12 x 12 x 0.7 mm   | 0.65 mm    | 0.40 mm   | 17 x 17; partial matrix |

| TFBGA180     | SOT640-1[3]      | 10 x 10 x 0.8 mm   | 0.5 mm     | 0.30 mm   | 18 x 18; partial matrix |

| LFBGA320     | SOT824-1[2]      | 13 x 13 x 0.9 mm   | 0.5 mm     | 0.30 mm   | 24 x 24; partial matrix |

<sup>[1]</sup> Reference JEDEC MO-216

<sup>[2]</sup> Reference JEDEC MO-275

<sup>[3]</sup> Reference JEDEC MO-195

<sup>[4]</sup> Reference JEDEC MS-034

<sup>[5]</sup> Reference JEDEC MO-205

<sup>[6]</sup> Reference JEDEC MO-192

#### PCB layout guidelines for NXP MCUs in BGA packages

# 3. BGA footprints

When building a BGA footprint the number one consideration is ensuring the ball pattern and outline matches the device package. This includes correct orientation of ball A1, matching all ball column x row locations, and the ball-to-ball pitch. Solder joint reliability is also of primary concern. For cost sensitive applications, minimizing the number of PCB layers required to route the BGA is a consideration. The BGA land pattern footprint plays a key role in solder joint reliability, and the number of PCB layers required to route the balls.

#### 3.1 Land pad design

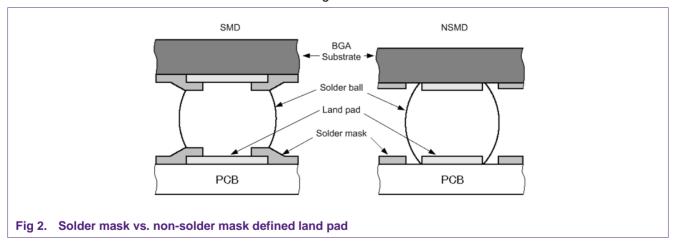

The PCB BGA land pads have to be designed to ensure solder joint reliability and provide optimum manufacturability. The two basic types of BGA land pad design are:

- The Solder Mask Defined (SMD) land pad

- The Non-Solder Mask Defined (NSMD) land pad; recommended type for PCB

#### 3.1.1 Solder Mask Defined (SMD) land pad

The SMD type of BGA land pad design is characterized by the copper pad being larger than the solder mask opening above this pad. Thus the solder joint area of the land pad is defined by the opening in the solder mask.

#### 3.1.2 Non-Solder Mask Defined (NSMD) land pad

The NSMD type of BGA land pad design is characterized by the copper pad being smaller than the solder mask opening. Thus the solder joint area of the land pad is defined by the size of the land pad. The solder mask clearance around the land pad must be large enough to ensure that no solder mask overlaps the land pad. Typical solder mask to land pad clearance is in the range 0.06 mm to 0.075 mm, depending on the PCB manufacturer's solder mask alignment tolerance.

#### PCB layout guidelines for NXP MCUs in BGA packages

### 3.2 Recommended BGA footprint

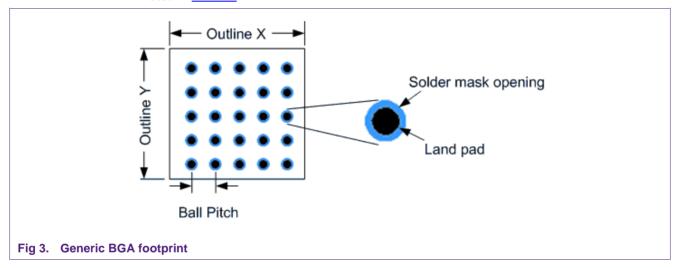

The NSMD type land pad is recommended for the PCB BGA footprint. In addition to the top surface of the land pad, the reflowed solder paste will wet to the side wall making a mechanically stronger solder joint than the SMD type pad. The smaller NSMD land pad also leaves more space for routing traces between the land pads. It has been shown that matching the solder joint area of the PCB land pad to that on the BGA package substrate equalizes the ball solder joint stress between the BGA package and PCB land pad thereby reducing the chance of a solder joint stress crack. All of the BGA packages referenced in this application note use SMD type pads. The NSMD type pads on the PCB should be approximately 10 % to 15 % smaller than the SMD pads on the BGA to achieve equalized stress. This difference between the BGA package SMD pad and recommended PCB NSMD pad for each BGA package is reflected in Table 2. A generic BGA footprint is shown in Fig 3, and the specific dimensions for each BGA package are listed in Table 2.

#### PCB layout guidelines for NXP MCUs in BGA packages

Table 2. Recommended BGA footprints

| Package Name        | Ball Pitch | Ball<br>diameter | BGA substrate<br>Land diameter | PCB land pad diameter | Solder mask diameter | Outline X & Y |

|---------------------|------------|------------------|--------------------------------|-----------------------|----------------------|---------------|

| (L)BGA256           | 1.0        | 0.50             | 0.45                           | 0.45 <u>[4]</u>       | 0.6                  | 17.6          |

| TFBGA100            | 8.0        | 0.45             | 0.4                            | 0.35[4]               | 0.5                  | 9.6           |

| TFBGA144            | 8.0        | 0.45             | 0.4                            | 0.35[4]               | 0.5                  | 12.6          |

| TFBGA180            | 0.8        | 0.45             | 0.4                            | 0.35[4]               | 0.5                  | 12.6          |

| TFBGA208 (SOT950-1) | 0.8        | 0.45             | 0.4                            | 0.35[4]               | 0.5                  | 15.6          |

| LFBGA208            | 0.8        | 0.45             | 0.4                            | 0.30[4]               | 0.42                 | 14.6          |

| LFBGA256            | 0.8        | 0.45             | 0.4                            | 0.30[4]               | 0.42                 | 14.6          |

| TFBGA296            | 0.8        | 0.45             | 0.4                            | 0.35[4] [6]           | 0. 5                 | 15.6          |

| TFBGA296            | 0.8        | 0.45             | 0.4                            | 0.30[4] [7]           | 0. 42                | 15.6          |

| LFBGA324            | 0.8        | 0.45             | 0.4                            | 0.30[4]               | 0.42                 | 17.6          |

| TFBGA208 (SOT930-1) | 0.65       | 0.4              | 0.26                           | 0.25 <u>[5]</u>       | 0.37                 | 12.4          |

| TFBGA180 (SOT640-1) | 0.5        | 0.3              | n/a                            | 0.25 <u>[5]</u>       | 0.36                 | 10.4          |

| LFBGA320            | 0.5        | 0.3              | 0.25                           | 0.25[5]               | 0.36                 | 13.4          |

#### Notes:

- [1] All dimensions are in millimeters

- [2] All BGA substrate land pads are SMD type

- [3] All PCB land pads are NSMD type

- [4] The recommended solder paste diameter is the same as the PCB land pad

- [5] The recommended solder paste diameter is 0.02 mm larger than the PCB land pad

- [6] Used for routing 1 trace between land pads

- [7] Used for routing 2 traces between land pads

PCB layout guidelines for NXP MCUs in BGA packages

# 4. Recommended fan-out trace / space guidelines

The small pitch between BGA balls and their matrix arrangement makes it impractical to route all of the BGA balls away from the BGA on a single layer. Fan-out vias (also called escape vias) are required to route the balls to other layers on the PCB. There are several via technologies used on PCB's. They are: Through-via, Blind via, Buried via, Micro via and In-pad via. Through-vias, where the drilled via hole goes through all layers on the PCB, cost considerably less than Blind, Buried, Micro and In-pad vias. Through-vias are generally larger than the other types of vias as well. All recommended fan-out examples in this application note use the through-via exclusively.

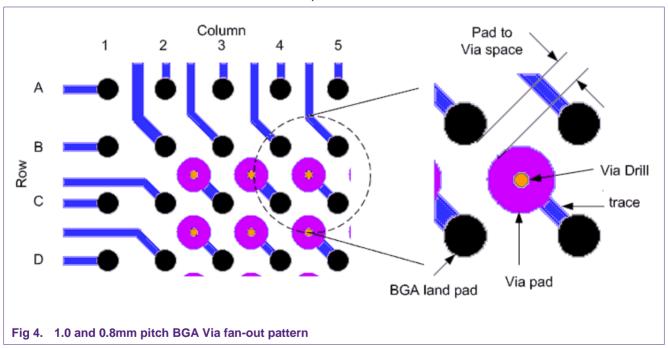

#### 4.1 Recommended 1.0 mm and 0.8 mm pitch BGA via fan-out pattern

For 1 mm and 0.8 mm pitch BGA's, the recommended via fan-out pattern centers each via within the space between four adjacent BGA land pads as shown in Fig 4. Generally, a single trace is routed between adjacent BGA land pads, allowing the two outer rows of balls to be routed without a fan-out via. For BGAs with larger than 0.8 mm ball pitch one or two traces may be routed between adjacent BGA land pads, allowing the three outer most rows of balls to be routed without a fan out via. By reducing the BGA land pad, trace width and trace-to-pad space design rules for the 0.8 mm ball pitch TFBGA296, two traces may be routed between the BGA land pads. See Table 3 for the layout tool design rules for 1.0 mm and 0.8 mm pitch BGA via fan-out.

#### PCB layout guidelines for NXP MCUs in BGA packages

| Tubic o. | 1.0 111111 | ana 0.0 mm | pitch BOA                             | layout acsign                     | ruics           |               |             |                   |             |

|----------|------------|------------|---------------------------------------|-----------------------------------|-----------------|---------------|-------------|-------------------|-------------|

|          | BGA land   |            |                                       |                                   | Land pad to via | Between v     | ias         | Between Land pads |             |

|          |            | Pad        | Drill size<br>/ finished<br>hole size | Inner plane<br>layer anti-<br>pad | space           | Trace / space | # of traces | Trace / space     | # of traces |

| 1.0      | 0.45       | 0.55       | 0.3 / 0.18                            | 0.800                             | 0.2             | 0.15          | 1           | 0.18              | 1           |

| 1.0      | 0.45       | 0.485      | 0.25 / 0.1                            | 0.695                             | 0.24            | 0.1           | 2           | 0.11              | 2           |

| 8.0      | 0.35       | 0.485      | 0.25 / 0.1                            | 0.695                             | 0.148           | 0.105         | 1           | 0.15              | 1           |

| 0.8      | 0.30       | 0.485      | 0.25 / 0.1                            | 0.695                             | 0.173           | 0.105         | 1           | 0.1               | 2           |

Table 3. 1.0 mm and 0.8 mm pitch BGA layout design rules

## 4.2 Recommended 0.65 mm pitch BGA via fan-out pattern

For 0.65 mm pitch BGA's, the recommended via fan-out pattern centers each via within the space between four adjacent BGA land pads. Instead of placing the vias 0.65 mm apart they are placed 1.3 mm from each other, skipping every other location, and staggering them between adjacent rows, as the partial fan-out example is shown in Fig 5. With this pattern the TFGBA208 package can use 0.125 mm (0.005") trace and space design rules. With a single trace routed between adjacent BGA land pads, the two outer rows of balls can be routed without a fan-out via. See Table 4 for the layout tool design rules for 0.65 mm pitch BGA via fan-out.

(1) Note: no connect pins on the LPC3152/54

Fig 5. Recommended 0.65 mm pitch BGA via fan-out pattern

#### PCB layout guidelines for NXP MCUs in BGA packages

| Table 4. | 0.65 mm pitch BGA layout design rules |

|----------|---------------------------------------|

|          |                                       |

|      | BGA land<br>pad |       |            | Land pad to via space            | o Between vias | Between<br>Land pads |               |                |

|------|-----------------|-------|------------|----------------------------------|----------------|----------------------|---------------|----------------|

|      |                 | Pad   |            | Inner<br>plane layer<br>anti-pad |                | Trace /<br>space     | Trace / space | # of<br>traces |

| 0.65 | 0.25            | 0.425 | 0.2 / 0.05 | 0.6                              | 0.122          | 0.125                | 0.125         | 1              |

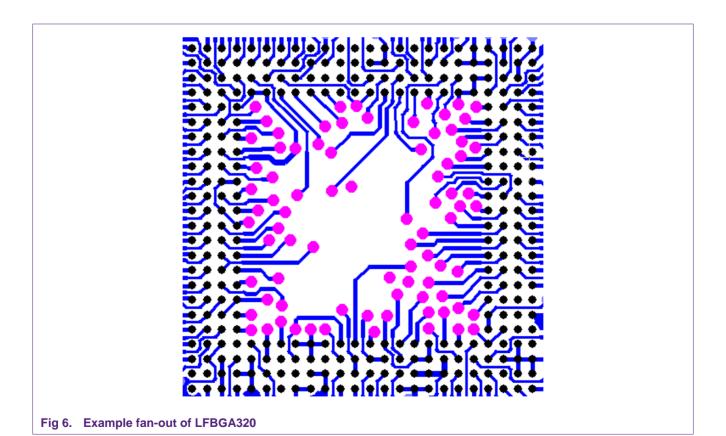

# 4.3 Recommended 0.5 mm pitch BGA via fan-out pattern

The pattern of centering the through-via within the four adjacent BGA land pads can not be used with 0.5 mm pitch BGA's. This is due to the smallest through-via pad being too large to fit in the space available between the land pads. With a single trace routed between adjacent BGA land pads, the two outer rows of balls can be routed without a fan-out via. The two inner rows of balls must be routed to vias in the center area of the BGA and escape routed on other layers. An example fan-out of the LFBGA320 package is shown in Fig 6. See Table 5 for the layout tool design rules for 0.5 mm pitch BGA via fan-out.

AN10778 © NXP B.V. 2011. All rights reserved

#### PCB layout guidelines for NXP MCUs in BGA packages

| BGA Pitch | BGA land<br>pad |                                                                |            |               | Land pad to via space | Between vias   | Between<br>Land pads |   |

|-----------|-----------------|----------------------------------------------------------------|------------|---------------|-----------------------|----------------|----------------------|---|

|           |                 | Pad Drill size Inner / finished plane layer hole size anti-pad |            | Trace / space | Trace / space         | # of<br>traces |                      |   |

| 0.5       | 0.25            | 0.4                                                            | 0.2 / 0.05 | 0.6           | 0.1                   | 0.1            | 0.08                 | 1 |

Table 5. 0.5 mm pitch BGA layout design rules

#### 5. Board cost considerations

PCB cost is affected by many factors, generally increasing in cost as:

- 1. Overall PCB area increases

- 2. As the number of layers increases

- 3. Using in-pad via, blind via, buried via, micro via

- 4. As the diameter of the through-via decreases

- 5. As the trace width decreases below 0.125 mm (5 mils)

- 6. As the space between metal features decreases below 0.125 mm (5 mils)

Therefore, selecting via size, trace width and spacing for fan-out routing of the BGA requires a balance between feature size, number of PCB layers and overall board area to get the most economical layout.

#### 5.1 Area rules

On many boards the design rules for via size, trace width and space for fan-out routing of the BGA may require smaller feature sizes than any other area on the board. If your layout tool is capable of defining multiple rule areas, it may be cost effective to limit the area around the BGA to the smaller feature sizes and use larger vias and larger trace widths and spacing for the balance of the board. In other words if all but the BGA fan-out can use 5 or 6 mil trace and space rules, then limiting 3 or 4 mil trace and space rules to the BGA fan-out area may have only a small cost premium.

#### 5.2 How many PCB layers to fan-out the BGA

Generally one trace is routed between adjacent BGA land pads, enabling the two outer rows of BGA balls to be routed on the same layer as the BGA is mounted on. The next two rows in can be routed on the next signal layer, provided the vias are spaced far enough apart to allow one trace between them, as is the case for the 1.0 mm, 0.8 mm and 0.65 mm recommended fan-out via patterns in Fig 4 and Fig 5. Each additional BGA row will take one additional PCB layer to fan-out. For example, the TFBGA296 has balls seven rows deep and will take 5 PCB layers to fan-out, including power and ground. Because PCB's are constructed in even number layers, a PCB using the TFBGA296 package would require a minimum of six layers, including one split power plane and one ground plane.

#### PCB layout guidelines for NXP MCUs in BGA packages

# 6. BGA power and ground

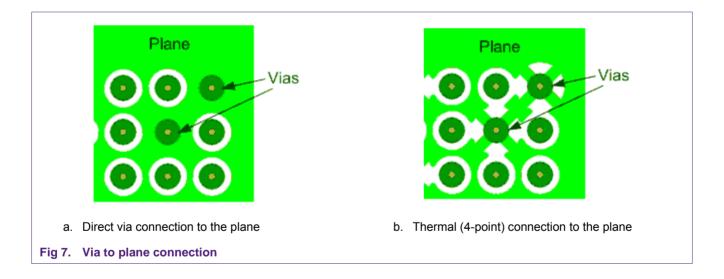

NXP LPC Microcontroller family devices have many power and ground pins. This is due to having multiple power domains, and the potential for large simultaneous switching currents when all 16-bit or 32-bit external data bus outputs change from all low to all high, or all high to all low, at the same time. It is recommended that the MCU VDD(core) and VDD(IO) power nets and VSSx be distributed on a plane layer of the PCB instead of routed by the thin traces, like those used for carrying other signals. BGA power and ground balls are typically routed to a near by fan-out via the same as any signal. It is recommended that the short trace between the BGA ball and fan-out via be no wider than 0.15 mm (6 mils). Although it is common to use a wider trace (0.5 mm) to route power and ground from other IC packages (SOIC, QFP, TSOP, etc.), using larger than 0.15 mm may begin to act like a heat sink that could adversely affect the solder joint. If a BGA power or ground pin must be routed more than 1 mm to get to a fan-out via. the trace should be routed the first 1mm with a <= 0.15 mm trace then up sized for the balance of the route. It is recommended that all power and ground vias that tie into a plane do so as a solid 360 degree connection, as shown Fig 7a. This provides a lower inductance connection to the plane and will provide a more solid ground plane throughout the BGA area. Avoid the use of thermal (4-point) connections, as shown in Fig 7b.

#### PCB layout guidelines for NXP MCUs in BGA packages

# 7. Legal information

#### 7.1 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

#### 7.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the

customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

**Evaluation products** — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer.

In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages.

Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

#### 7.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are property of their respective owners.

# PCB layout guidelines for NXP MCUs in BGA packages

# 8. Contents

| 1.    | Introduction                                | 3   |

|-------|---------------------------------------------|-----|

| 1.1   | Scope                                       |     |

| 2.    | BGA package description                     |     |

| 3.    | BGA footprints                              | 5   |

| 3.1   | Land pad design                             | 5   |

| 3.1.1 | Solder Mask Defined (SMD) land pad          |     |

| 3.1.2 | Non-Solder Mask Defined (NSMD) land pad     | 5   |

| 3.2   | Recommended BGA footprint                   | 6   |

| 4.    | Recommended fan-out trace / space guideling | nes |

|       |                                             | 8   |

| 4.1   | Recommended 1.0 mm and 0.8 mm pitch BG      |     |

|       | via fan-out pattern                         |     |

| 4.2   | Recommended 0.65 mm pitch BGA via fan-or    |     |

|       | pattern                                     |     |

| 4.3   | Recommended 0.5 mm pitch BGA via fan-out    |     |

|       | pattern                                     |     |

| 5.    | Board cost considerations                   |     |

| 5.1   | Area rules                                  | 11  |

| 5.2   | How many PCB layers to fan-out the BGA      | 11  |

| 6.    | BGA power and ground                        | 12  |

| 7.    | Legal information                           | 13  |

| 7.1   | Definitions                                 | 13  |

| 7.2   | Disclaimers                                 | 13  |

| 7.3   | Trademarks                                  | 13  |

| 8.    | Contents                                    | 14  |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in the section 'Legal information'.

© NXP B.V. 2011.

All rights reserved.