# 125 MHz LVPECL Clock Generator

### **Features**

■ One LVPECL Output Pair

■ Output Frequency: 112 MHz to 140 MHz

■ External Crystal Frequency: 22.4 MHz to 28 MHz

■ Low RMS Phase Jitter at 125 MHz, using 25 MHz Crystal

(1.875 MHz to 20 MHz): 0.4 ps (Typical)

■ Pb-free 8-Pin TSSOP Package

■ Supply Voltage: 3.3V or 2.5V

■ Commercial and Industrial Temperature Ranges

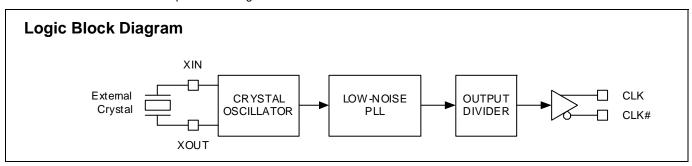

# **Functional Description**

The CY2XP21 is a PLL (Phase Locked Loop) based high performance clock generator. It is optimized to generate a 125 MHz clock, which is ideal for 10 Gb Ethernet applications. It also produces an output frequency that is five times the crystal frequency. It uses Cypress's low noise VCO technology to achieve less than 1 ps typical RMS phase jitter. The CY2XP21 has a crystal oscillator interface input and one LVPECL output pair.

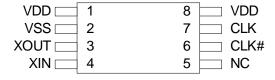

### **Pinouts**

Figure 1. Pin Diagram - 8-Pin TSSOP

Table 1. Pin Definition - 8-Pin TSSOP

| Pin Number | Pin Name  | I/O Type              | Description                         |

|------------|-----------|-----------------------|-------------------------------------|

| 1, 8       | VDD       | Power                 | 3.3V or 2.5V power supply           |

| 2          | VSS       | Power                 | Ground                              |

| 3, 4       | XOUT, XIN | XTAL output and input | Parallel resonant crystal interface |

| 5          | NC        |                       | No Connect                          |

| 6,7        | CLK#, CLK | LVPECL output         | Differential Clock Output           |

**Cypress Semiconductor Corporation** Document #: 001-52849 Rev. \*A

# **Frequency Table**

| Inputs                  | Output Frequency (MHz) |                        |

|-------------------------|------------------------|------------------------|

| Crystal Frequency (MHz) | PLL Multiplier Value   | Output Frequency (MHz) |

| 25                      | 5                      | 125                    |

| 26.6                    | 5                      | 133                    |

## **Absolute Maximum Conditions**

| Parameter           | Description                             | Conditions                  | Min  | Max                   | Unit |

|---------------------|-----------------------------------------|-----------------------------|------|-----------------------|------|

| $V_{DD}$            | Supply Voltage                          |                             | -0.5 | 4.4                   | V    |

| V <sub>IN</sub> [1] | Input Voltage, DC                       | Relative to V <sub>SS</sub> | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| T <sub>S</sub>      | Temperature, Storage                    | Non operating               | -65  | 150                   | °C   |

| T <sub>J</sub>      | Temperature, Junction                   |                             |      | 135                   | °C   |

| ESD <sub>HBM</sub>  | ESD Protection, Human Body Model        | JEDEC STD 22-A114-B         | 2000 |                       | V    |

| UL-94               | Flammability Rating                     | At 1/8 in.                  | V    | <b>/</b> –0           |      |

| $\Theta_{JA}^{[2]}$ | Thermal Resistance, Junction to Ambient | 0 m/s airflow               | 1    | 00                    | °C/W |

|                     |                                         | 1 m/s airflow               | !    | 91                    |      |

|                     |                                         | 2.5 m/s airflow             | i    | 87                    |      |

# **Operating Conditions**

| Parameter       | Description                                                                                       | Min   | Max   | Unit |

|-----------------|---------------------------------------------------------------------------------------------------|-------|-------|------|

| $V_{DD}$        | 3.3V Supply Voltage                                                                               | 3.135 | 3.465 | V    |

|                 | 2.5V Supply Voltage                                                                               | 2.375 | 2.625 | V    |

| T <sub>A</sub>  | Ambient Temperature, Commercial                                                                   | 0     | 70    | °C   |

|                 | Ambient Temperature, Industrial                                                                   | -40   | 85    | °C   |

| T <sub>PU</sub> | Power up time for all $V_DD$ to reach minimum specified voltage (ensure power ramps is monotonic) | 0.05  | 500   | ms   |

# **DC Electrical Characteristics**

| Parameter           | Description                                                                 | Test Conditions                                                      | Min                   | Тур | Max                    | Unit |

|---------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------|-----|------------------------|------|

| I <sub>DD</sub> [4] | Operating Supply Current with                                               | V <sub>DD</sub> = 3.465V, Output terminated                          | _                     | _   | 150                    | mA   |

|                     | output terminated                                                           | V <sub>DD</sub> = 2.625V, Output terminated                          | _                     | _   | 145                    | mA   |

| V <sub>OH</sub>     | LVPECL Output High Voltage                                                  | $V_{DD}$ = 3.3V or 2.5V, $R_{TERM}$ = 50 $\Omega$ to $V_{DD}$ – 2.0V | V <sub>DD</sub> –1.15 | -   | V <sub>DD</sub> -0.75  | V    |

| V <sub>OL</sub>     | LVPECL Output Low Voltage                                                   | $V_{DD}$ = 3.3V or 2.5V, $R_{TERM}$ = 50 $\Omega$ to $V_{DD}$ – 2.0V | V <sub>DD</sub> –2.0  | -   | V <sub>DD</sub> –1.625 | V    |

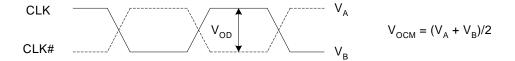

| V <sub>OD1</sub>    | LVPECL Peak-to-Peak Output<br>Voltage Swing                                 | $V_{DD}$ = 3.3V or 2.5V, $R_{TERM}$ = 50 $\Omega$ to $V_{DD}$ – 2.0V | 600                   | -   | 1000                   | mV   |

| $V_{OD2}$           | LVPECL Output Voltage Swing (V <sub>OH</sub> - V <sub>OL</sub> )            | $V_{DD}$ = 2.5V, $R_{TERM}$ = $50\Omega$ to $V_{DD}$ – 1.5V          | 500                   | -   | 1000                   | mV   |

| V <sub>OCM</sub>    | LVPECL Output Common Mode<br>Voltage (V <sub>OH</sub> + V <sub>OL</sub> )/2 | $V_{DD}$ = 2.5V, $R_{TERM}$ = $50\Omega$ to $V_{DD}$ – 1.5V          | 1.2                   | -   | _                      | V    |

| C <sub>INX</sub>    | Pin Capacitance, XIN & XOUT                                                 |                                                                      |                       | 4.5 |                        | pF   |

- The voltage on any input or IO pin cannot exceed the power pin during power up.

Simulated using Apache Sentinel TI software. The board is derived from the JEDEC multilayer standard. It measures 76 x 114 x 1.6 mm and has 4-layers of copper (2/1/1/2 oz.). The internal layers are 100% copper planes, while the top and bottom layers have 50% metalization. No vias are included in the model.

I<sub>DD</sub> includes approximately 24 mA of current that is dissipated externally in the output termination resistors.

# AC Electrical Characteristics[4]

| Parameter                 | Description               | Conditions                                                                           | Min | Тур | Max | Unit |

|---------------------------|---------------------------|--------------------------------------------------------------------------------------|-----|-----|-----|------|

| F <sub>OUT</sub>          | Output Frequency          |                                                                                      | 112 | _   | 140 | MHz  |

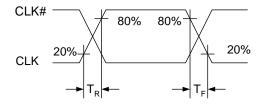

| $T_R, T_F$                | Output Rise or Fall Time  | 20% to 80% of full output swing                                                      | _   | 500 | _   | ps   |

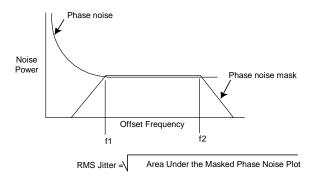

| T <sub>Jitter(\phi)</sub> | RMS Phase Jitter (Random) | 125 MHz, (1.875–20 MHz)                                                              | _   | 0.4 | _   | ps   |

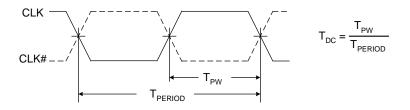

| $T_{DC}$                  | Output Duty Cycle         | Measured at zero crossing point                                                      | 48  | _   | 52  | %    |

| T <sub>LOCK</sub>         | Startup Time              | Time for CLK to reach valid frequency measured from the time $V_{DD} = V_{DD}(min.)$ | -   | _   | 10  | ms   |

# Recommended Crystal Specifications[5]

| Parameter      | Description                  | Min         | Max | Unit |

|----------------|------------------------------|-------------|-----|------|

| Mode           | Mode of Oscillation          | Fundamental |     |      |

| F              | Frequency                    | 22.4        | 28  | MHz  |

| ESR            | Equivalent Series Resistance | _           | 50  | Ω    |

| C <sub>0</sub> | Shunt Capacitance            | _           | 7   | pF   |

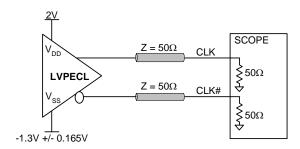

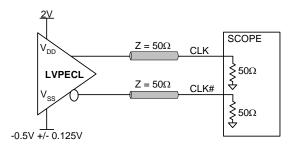

## **Parameter Measurements**

Figure 2. 3.3V Output Load AC Test Circuit

Figure 3. 2.5V Output Load AC Test Circuit

#### Notes

- 4. INot 100% tested, guaranteed by design and characterization.

- 5. Characterized using an 18 pF parallel resonant crystal.

Figure 4. Output DC Parameters

Figure 5. Output Rise and Fall Time

Figure 6. RMS Phase Jitter

Figure 7. Output Duty Cycle

# **Application Information**

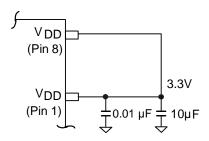

### **Power Supply Filtering Techniques**

As in any high speed analog circuitry, noise at the power supply pins can degrade performance. To achieve optimum jitter performance, use good power supply isolation practices. Figure 8 illustrates a typical filtering scheme. Since all the current flows through pin 1, the resistance and inductance between this pin and the supply is minimized. A 0.01 or 0.1  $\mu F$  ceramic chip capacitor is also located close to this pin to provide a short and low impedance AC path to ground. A 1 to 10  $\mu F$  ceramic or tantalum capacitor is located in the general vicinity of this device and may be shared with other devices.

Figure 8. Power Supply Filtering

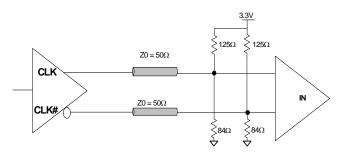

### **Termination for LVPECL Output**

The CY2XP21 implements its LVPECL driver with a current steering design. For proper operation, it requires a 50 ohm dc termination on each of the two output signals. For 3.3V operation, this data sheet specifies output levels for termination to  $V_{DD}\!-\!2.0V$ . This same termination voltage can also be used for  $V_{DD}\!=\!2.5V$  operation, or it can be terminated to  $V_{DD}\!-\!1.5V$ . Note that it is also possible to terminate with 50 ohms to ground ( $V_{SS}$ ), but the high and low signal levels differ from the data sheet values. Termination resistors are best located close to the destination device. To avoid reflections, trace characteristic impedance ( $Z_0$ ) should match the termination impedance. Figure 9 shows a standard termination scheme.

Figure 9. LVPECL Output Termination

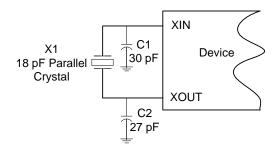

### **Crystal Interface**

The CY2XP21 is characterized with 18 pF parallel resonant crystals. The capacitor values shown in Figure 10 are determined using a 25 MHz 18 pF parallel resonant crystal and are chosen to minimize the ppm error. Note that the optimal values for C1 and C2 depend on the parasitic trace capacitance and are thus layout dependent.

Figure 10. Crystal Input Interface

### **Board Layout and NC Pin**

Pin 5 (NC) does not perform any function on the CY2XP21. Although not used electrically, it is very useful for heat dissipation. For this reason, users are advised to connect pin 5 to either a  $V_{DD}$  or  $V_{SS}$  plane. This helps to lower the thermal resistance of the board / package combination, thus reducing the die temperature.

# **Ordering Information**

| Part Number | Package Type                | Product Flow              |

|-------------|-----------------------------|---------------------------|

| CY2XP21ZXC  | 8-pin TSSOP                 | Commercial, 0°C to 70°C   |

| CY2XP21ZXCT | 8-pin TSSOP - Tape and Reel | Commercial, 0°C to 70°C   |

| CY2XP21ZXI  | 8-pin TSSOP                 | Industrial, -40°C to 85°C |

| CY2XP21ZXIT | 8-pin TSSOP - Tape and Reel | Industrial, -40°C to 85°C |

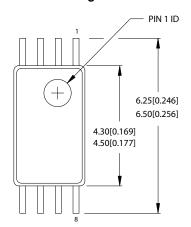

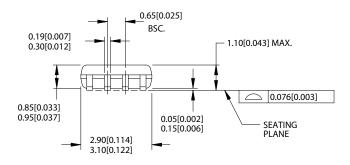

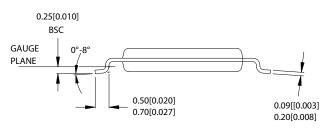

# **Package Drawing and Dimensions**

Figure 11. 8-Pin Thin Shrunk Small Outline Package (4.40 MM Body) Z8

DIMENSIONS IN MM[INCHES]  $\underline{\text{MIN.}}$  MAX.

51-85093-\*A

# **Document History Page**

| Document Title: CY2XP21 125 MHz LVPECL Clock Generator Document Number: 001-52849 |         |                    |                    |                                              |  |  |

|-----------------------------------------------------------------------------------|---------|--------------------|--------------------|----------------------------------------------|--|--|

| REV.                                                                              | ECN NO. | Submission<br>Date | Orig. of<br>Change | Description of Change                        |  |  |

| **                                                                                | 2700242 | 04/30/2009         | KVM/PYRS           | New data sheet                               |  |  |

| *A                                                                                | 2718898 | 06/15/09           | WWZ                | Minor ECN to post data sheet to external web |  |  |

# Sales, Solutions, and Legal Information

### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at cypress.com/sales.

| Products         |                      | PSoC Solutions        |                                   |

|------------------|----------------------|-----------------------|-----------------------------------|

| PSoC             | psoc.cypress.com     | General               | psoc.cypress.com/solutions        |

| Clocks & Buffers | clocks.cypress.com   | Low Power/Low Voltage | psoc.cypress.com/low-power        |

| Wireless         | wireless.cypress.com | Precision Analog      | psoc.cypress.com/precision-analog |

| Memories         | memory.cypress.com   | LCD Drive             | psoc.cypress.com/lcd-drive        |

| Image Sensors    | image.cypress.com    | CAN 2.0b              | psoc.cypress.com/can              |

|                  |                      | USB                   | psoc.cypress.com/usb              |

© Cypress Semiconductor Corporation, 2009. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document #: 001-52849 Rev. \*A

Revised June 15, 2009

Page 7 of 7