#### **Features and Benefits**

- · AEC-Q100 Qualified

- Wide input voltage range of 4.5 to 40 V for start/stop, cold crank and load dump requirements

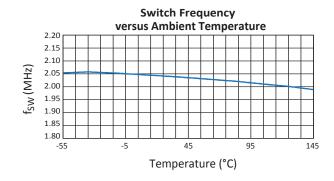

- Boost converter switching frequency up to 2 MHz, allowing operation above the AM band

- Excellent input voltage transient response

- Internal secondary OVP for redundant protection

- Fully integrated LED current sink and boost converter with 60 V DMOS FET

- Maximum LED current of 150 mA

- Drives up to 14 series LEDs

- Single EN/PWM pin interface for PWM Dimming and Enable function

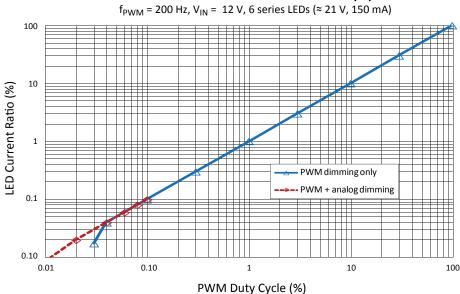

- 5000:1 PWM dimming at 200 Hz

Continued on the next page...

#### Packages:

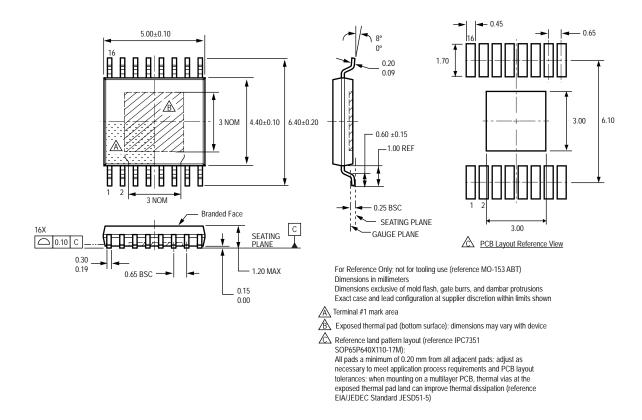

16-pin TSSOP with exposed thermal pad (LP package)

10-pin MSOP with exposed thermal pad (LY package)

#### **Description**

The A8513 is a single-output white LED (WLED) driver for LCD backlighting. It integrates a current-mode boost converter with an internal power switch and one current sink. The A8513 can operate from a single power supply from 4.5 to 40 V, to accommodate start/stop, cold crank, and load dump requirements. A 2 MHz boost converter switching frequency allows the A8513 to operate above the AM radio band.

If required, the fault flag can be used as part of a circuit to drive an external P-FET to disconnect the input supply from the system in the event of a fault. The A8513 provides protection against output short and overvoltage, open or shorted diode, open or shorted LED pin, shorted boost switch or inductor, shorted  $I_{\rm SET}$  resistor, and IC overtemperature. A dual level cycle-bycycle current limit function provides soft start and protects the internal current switch against high current overloads.

The A8513 is provided in a 10-pin MSOP package (suffix LY) and a 16-pin TSSOP package (suffix LP). Both packages have an exposed thermal pad for enhanced thermal dissipation, and are lead (Pb) free, with 100% matter tin leadframe plating.

#### **Applications:**

- LCD backlighting for:

- Automotive infotainment

- Automotive cluster

- Automotive center stack

- Industrial LCD displays

- Portable DVD players

- Flatbed Scanners

- LED Lighting

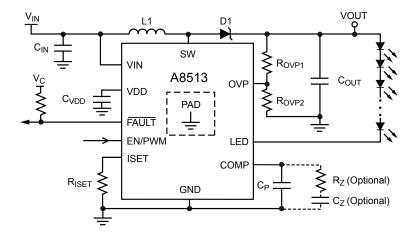

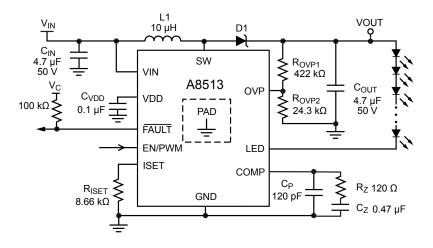

#### **Typical Application Circuit**

| Boost f <sub>SW</sub><br>(MHz) | V <sub>IN</sub> (min)<br>(V) | LEDs per<br>String (max) |

|--------------------------------|------------------------------|--------------------------|

| 0.25/0.5/1                     | 5                            | 14                       |

| 2                              | 10                           | 14                       |

| 2                              | 8                            | 12                       |

| 2                              | 6                            | 9                        |

| 2                              | 5                            | 7                        |

## A8513

## Wide Input Voltage Range, High Efficiency Fault Tolerant LED Driver

#### Features and Benefits (continued)

- Fault flag pin to alert the controller to a myriad of possible fault conditions

- Protection Features:

- Shorted output

- Open or shorted LED pin

- Output undervoltage and overvoltage

- Input undervoltage

- Shorted boost switch or inductor

- Shorted I<sub>SET</sub> resistor

- Open boost Schottky

- Overtemperature

#### Selection Guide

| Selection Guide |                                             |                                  |                                       |

|-----------------|---------------------------------------------|----------------------------------|---------------------------------------|

| Part Number     | Oscillator Frequency, f <sub>SW</sub> (MHz) | Packing*                         | Package                               |

| A8513KLYTR-T    | 2                                           | 4000 pieces per 13-in. reel      |                                       |

| A8513KLYTR-1-T  | 1                                           |                                  | 10 pin MCOD with averaged thermal and |

| A8513KLYTR-2-T  | 0.5                                         | Contact factory for availability | 10-pin MSOP with exposed thermal pad  |

| A8513KLYTR-3-T  | 0.25                                        |                                  |                                       |

| A8513KLPTR-T    | 2                                           | 4000 pieces per 13-in. reel      |                                       |

| A8513KLPTR-1-T  | 1                                           |                                  | 16 pin TCCOD with avanced thermal and |

| A8513KLPTR-2-T  | 0.5                                         | Contact factory for availability | 16-pin TSSOP with exposed thermal pad |

| A8513KLPTR-3-T  | 0.25                                        |                                  |                                       |

#### **Absolute Maximum Ratings\***

| Characteristic                | Symbol                               | Notes      | Rating      | Unit |

|-------------------------------|--------------------------------------|------------|-------------|------|

| LED Pin                       | V <sub>LED</sub>                     |            | -0.3 to 55  | V    |

| OVP Pin                       | V <sub>OVP</sub>                     |            | -0.3 to 60  | V    |

| VIN and FAULT Pins            | V <sub>IN</sub> , V <sub>FAULT</sub> |            | -0.3 to 40  | V    |

| SW Pin                        | V                                    | Continuous | -0.6 to 60  | ٧    |

| SW FIII                       | $V_{SW}$                             | t < 50 ns  | -1.0        | V    |

| ISET Pin                      | V <sub>ISET</sub>                    |            | -0.3 to 5.5 | V    |

| All Other Pins                |                                      |            | -0.3 to 7   | V    |

| Operating Ambient Temperature | T <sub>A</sub>                       | Range K    | -40 to 125  | °C   |

| Maximum Junction Temperature  | T <sub>J</sub> (max)                 |            | 150         | °C   |

| Storage Temperature           | T <sub>stg</sub>                     |            | -55 to 150  | °C   |

<sup>\*</sup>Stresses beyond those listed in this table may cause permanent damage to the device. The Absolute Maximum ratings are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Electrical Characteristics table is not implied. Exposure to Absolute Maximum-rated conditions for extended periods may affect device reliability.

<sup>\*</sup>Contact Allegro® for additional packing options

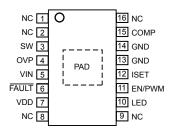

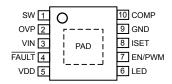

#### **Pin-out Diagram**

LP Package

LY Package

#### **Terminal List Table**

|        | Nun        | nber |                                                                                                                                                                                    |

|--------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name   | LP         | LY   | Function                                                                                                                                                                           |

| COMP   | 15         | 10   | Output of the error amplifier and compensation node. Connect compensation network from this pin to GND for control loop compensation.                                              |

| FAULT  | 6          | 4    | This pin is used to indicate fault conditions. Logic low indicates that the A8513 has a fault present.                                                                             |

| GND    | 13,14      | 9    | Ground.                                                                                                                                                                            |

| ISET   | 12         | 8    | Connect the R <sub>ISET</sub> resistor between this pin and GND to set the 100% LED current level.                                                                                 |

| LED    | 10         | 6    | Connect the cathode of the LED string to this pin.                                                                                                                                 |

| NC     | 1,2,8,9,16 | _    | No connection.                                                                                                                                                                     |

| OVP    | 4          | 2    | This pin is used to sense an overvoltage condition. Connect a resistive divider from the VOUT node to this pin to adjust the Overvoltage Protection (OVP).                         |

| PAD    | -          | _    | Exposed pad of the package providing enhanced thermal dissipation. This pad must be connected to the ground plane(s) of the PCB with at least 8 thermal vias, directly in the pad. |

| EN/PWM | 11         | 7    | PWM dimming pin. Used to control LED intensity by using pulse width modulation.                                                                                                    |

| SW     | 3          | 1    | The drain of the internal NMOS switch of the boost converter.                                                                                                                      |

| VDD    | 7          | 5    | Output of internal LDO. Connect a 0.1 µF decoupling capacitor between this pin and GND.                                                                                            |

| VIN    | 5          | 3    | Input power to the A8513.                                                                                                                                                          |

#### Thermal Characteristics\*may require derating at maximum conditions, see application information

| Thermal onal acteristics may                 | require derailing | at maximum cc | mattons, see application information                  |                                        |      |      |

|----------------------------------------------|-------------------|---------------|-------------------------------------------------------|----------------------------------------|------|------|

| Characteristic                               | Symbol            |               | Test Conditions*                                      | Value                                  | Unit |      |

|                                              |                   | LP package    | On 4-layer PCB based on JEDEC standard                | 34                                     | °C/W |      |

| Package Thermal Resistance                   | ь                 |               | On 2-layer PCB with 3.8 in.2 of copper area each side | 43                                     | °C/W |      |

| (Junction to Ambient)                        | R <sub>eJA</sub>  |               | LV naakaga                                            | On 4-layer PCB based on JEDEC standard | 48   | °C/W |

|                                              |                   | LY package    | On 2-layer PCB with 2.5 in.2 of copper area each side | 48                                     | °C/W |      |

| Package Thermal Resistance (Junction to Pad) | $R_{\theta JP}$   |               |                                                       | 2                                      | °C/W |      |

<sup>\*</sup>To be verified by characterization. Additional thermal information available on the Allegro® website.

3

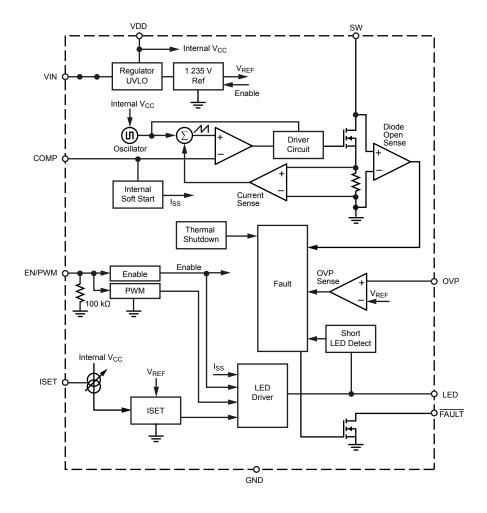

#### **Functional Block Diagram**

**ELECTRICAL CHARACTERISTICS**<sup>1</sup> Valid at  $V_{IN}$  = 16 V,  $T_A$  = 25°C, • indicates specifications guaranteed through the full operating temperature range with  $T_A$  =  $T_J$  = -40°C to125 °C, typical specifications are at  $T_A$  = 25°C; unless otherwise specified

| Characteristics                   | Symbol                 | Test Conditions                                                                                              | 'A    | Min.    | Typ.  | Max.  | Unit  |

|-----------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------|-------|---------|-------|-------|-------|

| Input Voltage Specifications      | Cymbol                 | rest conditions                                                                                              |       | 141111. | Typ.  | WIGA. | Oilit |

|                                   | \ \\                   |                                                                                                              | •     | 4.5     |       | 40    | V     |

| Operating Input Voltage Range     | V <sub>IN</sub>        | V sicios                                                                                                     | •     | 4.5     | _     | -     | V     |

| VIN Pin UVLO Start Threshold      | V <sub>UVLOrise</sub>  | V <sub>IN</sub> rising                                                                                       |       |         | _     | 4.35  | -     |

| VIN Pin UVLO Stop Threshold       | V <sub>UVLOfall</sub>  | V <sub>IN</sub> falling                                                                                      | •     |         | -     | 3.90  | V     |

| VIN Pin UVLO Hysteresis           | V <sub>UVLOhys</sub>   |                                                                                                              |       | _       | 450   | _     | mV    |

| Input Current                     | 1 .                    | T                                                                                                            | 1     |         | I     |       |       |

| Input Quiescent Current           | IQ                     | EN/PWM = V <sub>IH</sub> , SW = 2 MHz, no load                                                               |       | -       | 5     | -     | mA    |

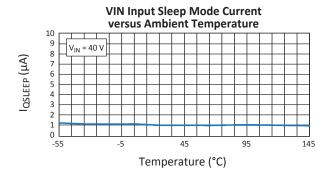

| Input Sleep Supply Current        | I <sub>QSLEEP</sub>    | VIN = 16 V, EN/PWM = 0 V                                                                                     | •     | -       | 1     | 10    | μA    |

| Input Logic Levels (EN/PWM and F7 | AULT 3)                |                                                                                                              |       |         |       |       |       |

| Input logic Level (Low)           | V <sub>IL</sub>        | 5 V < V <sub>IN</sub> < 40 V                                                                                 | •     | -       | -     | 400   | mV    |

| Input logic Level (High)          | V <sub>IH</sub>        | 5 V < V <sub>IN</sub> < 40 V                                                                                 | •     | 1.5     | -     | -     | V     |

| EN/PWM Pull-Down Resistor         | R <sub>EN/PWM</sub>    | EN/PWM = 5 V                                                                                                 |       | -       | 100   | -     | kΩ    |

| FAULT Pin Pull-Down Voltage       | V <sub>FAULT</sub>     | I <sub>FAULT</sub> = 0.5 mA                                                                                  | •     | -       | _     | 0.4   | V     |

| FAULT Pin Leakage Current         | I <sub>FAULTIkg</sub>  | V <sub>FAULT</sub> = 5 V                                                                                     |       | -       | _     | 1     | μΑ    |

| Error Amplifier                   |                        |                                                                                                              |       |         |       |       |       |

| Open Loop Voltage Gain            | A <sub>VOL</sub>       |                                                                                                              |       | -       | 45    | -     | dB    |

| Transconductance                  | 9 <sub>m</sub>         | $\Delta I_{COMP} = \pm 10 \mu A$                                                                             |       | -       | 990   | -     | μΑ/V  |

| Source Current                    | I <sub>EA(SRC)</sub>   | V <sub>COMP</sub> = 1.5 V                                                                                    |       | -       | -360  | -     | μA    |

| Sink Current                      | I <sub>EA(SINK)</sub>  | V <sub>COMP</sub> = 1.5 V                                                                                    |       | -       | 360   | -     | μA    |

| COMP Pin Pull-Down Resistance     | R <sub>COMP</sub>      | FAULT asserted                                                                                               |       | -       | 2000  | -     | Ω     |

| Output Overvoltage Protection     |                        |                                                                                                              |       |         | •     |       |       |

| Overvoltage Protection Threshold  | V <sub>OVPHI(th)</sub> | Measured at OVP Pin                                                                                          | •     | 1.168   | 1.218 | 1.268 | V     |

| OVP Pin Leakage Current           | I <sub>OVPH</sub>      | Standard CMOS input, measured at V <sub>OVP</sub> = 1.2 V                                                    | •     | -       | _     | 100   | nA    |

| OVP Pin Undervoltage Threshold    | V <sub>UVP(th)</sub>   | Measured at OVP Pin                                                                                          | •     | -       | -     | 110   | mV    |

| Secondary Overvoltage Protection  | V <sub>OVP(sec)</sub>  | Measured at SW Pin                                                                                           | •     | 53      | 55.5  | 58    | V     |

| BOOST Switch                      | , ,                    |                                                                                                              |       |         |       |       |       |

| Switch On-Resistance              | R <sub>DS(on)SW</sub>  | I <sub>SW</sub> = 750 mA, V <sub>IN</sub> = 16 V                                                             |       | -       | 450   | 800   | mΩ    |

| Switch Leakage Current            | I <sub>SWlkg</sub>     | V <sub>SW</sub> = 16 V, EN/PWM = V <sub>IL</sub> , T <sub>A</sub> = T <sub>J</sub><br>between –40°C and 85°C |       | -       | 0.1   | 1     | uA    |

| 9                                 | GVVING                 | V <sub>SW</sub> = 16 V, EN/PWM = V <sub>IL</sub> , T <sub>A</sub> = T <sub>J</sub> = 125°C                   |       | -       | 10    | -     | uA    |

| Switch Current Limit              | I <sub>SW(LIM)</sub>   |                                                                                                              | • 1.9 |         | 2.2   | 2.8   | А     |

| Secondary Switch Current Limit    | I <sub>SW(LIM2)</sub>  | Higher than I <sub>SW(LIM)</sub> (max) in all conditions, A8513 latches when detected                        | •     | 3       | 3.5   | 4.64  | А     |

| Minimum Switch On-Time            | t <sub>SW(ON)</sub>    |                                                                                                              | •     | -       | 75    | 100   | ns    |

| Minimum Switch Off-Time           | t <sub>SW(OFF)</sub>   |                                                                                                              | •     | -       | 55    | 85    | ns    |

Continued on the next page...

**ELECTRICAL CHARACTERISTICS**<sup>1</sup> (continued) Valid at  $V_{IN}$  = 16 V,  $T_A$  = 25°C, • indicates specifications guaranteed through the full operating temperature range with  $T_A$  =  $T_J$  = -40°C to 125 °C, typical specifications are at  $T_A$  = 25°C; unless otherwise specified

| Characteristics                                   | Symbol                 | Test Conditions                                                                                                                              |   | Min. | Тур.  | Max. | Unit |

|---------------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---|------|-------|------|------|

| Oscillator Frequency                              | -1                     |                                                                                                                                              |   |      |       |      |      |

|                                                   |                        | A8513KLYTR-1-T, A8513KLPTR-1-T                                                                                                               | • | 1.8  | 2     | 2.2  | MHz  |

| Ossillator Francisco                              | £                      | A8513KLYTR-2-T, A8513KLPTR-2-T •                                                                                                             |   | 0.9  | 1     | 1.1  | MHz  |

| Oscillator Frequency                              | f <sub>SW</sub>        | A8513KLYTR-3-T, A8513KLPTR-3-T                                                                                                               | • | 450  | 500   | 550  | kHz  |

|                                                   |                        | A8513KLYTR-4-T, A8513KLPTR-4-T                                                                                                               | • | 225  | 250   | 275  | kHz  |

| LED Current Sinks                                 |                        |                                                                                                                                              |   |      |       |      |      |

| LED Accuracy                                      | Err <sub>LED</sub>     | ISET = 150 μA                                                                                                                                | • | -    | -     | 3    | %    |

| LED Regulation Voltage                            | V <sub>LED</sub>       | ISET = 150 μA                                                                                                                                |   | -    | 880   | -    | mV   |

| I <sub>SET</sub> to I <sub>LED</sub> Current Gain | A <sub>ISET</sub>      | ISET = 150 μA                                                                                                                                | • | 1014 | 1045  | 1076 | A/A  |

| ISET Pin Voltage                                  | V <sub>ISET</sub>      |                                                                                                                                              |   | -    | 1.003 | -    | V    |

| Allowable ISET Current                            | I <sub>SET</sub>       |                                                                                                                                              | • | 40   | -     | 160  | μΑ   |

| Soft Start LED Current Gain                       | A <sub>ILEDSS</sub>    | Current through enabled LED pin during soft start                                                                                            |   | -    | 48    | -    | A/A  |

| Maximum PWM Dimming Off-Time                      | t <sub>PWML</sub>      | Measured while EN/PWM = low during dimming control, and internal references are powered-on (exceeding t <sub>PWML</sub> results in shutdown) |   | -    | 16    | -    | ms   |

| Minimum PWM On-Time                               | t <sub>PWMH</sub>      | First cycle when powering-up A8513                                                                                                           | • | -    | 1.5   | 3    | μs   |

| EN/PWM High to LED-On Delay                       | t <sub>dPWM(on)</sub>  | Time between PWM enable and when LED current reaches 90% of maximum; $V_{PWM}$ = 0 $\rightarrow$ 2 V                                         | • | -    | 250   | 500  | ns   |

| EN/PWM Low to LED-Off Delay                       | t <sub>dPWM(off)</sub> | Time between PWM enable going low and when LED current reaches 10% of maximum; $V_{PWM} = 2 \rightarrow 0 \text{ V}$                         |   | -    | 250   | 500  | ns   |

| Thermal Protection (TSD)                          |                        |                                                                                                                                              |   |      |       |      |      |

| Thermal Shutdown Threshold <sup>2</sup>           | T <sub>TSD</sub>       | Temperature rising                                                                                                                           |   | -    | 165   | -    | °C   |

| Thermal Shutdown Hysteresis <sup>2</sup>          | T <sub>TSDHYS</sub>    |                                                                                                                                              |   | -    | 20    | -    | °C   |

<sup>&</sup>lt;sup>1</sup>For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), and positive current is defined as going into the node or pin (sinking).

6

<sup>&</sup>lt;sup>2</sup>Ensured by design and characterization, not production tested.

<sup>&</sup>lt;sup>3</sup> FAULT pin is high voltage tolerant

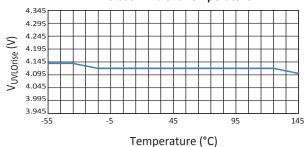

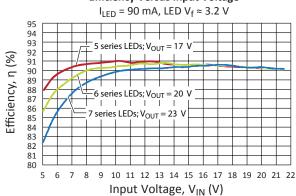

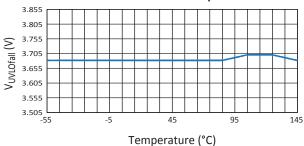

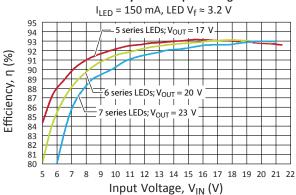

#### **Characteristic Performance**

#### **VIN UVLO Rising Threshold Voltage** versus Ambient Temperature

#### **Efficiency Versus Input Voltage**

#### **VIN UVLO Falling Threshold Voltage** versus Ambient Temperature

#### **Efficiency Versus Input Voltage**

#### Normalized LED Current Ratio versus PWM Duty Cycle

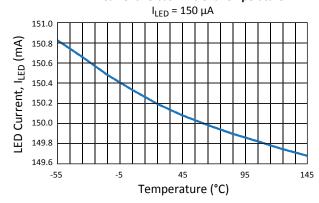

#### **LED Current versus Ambient Temperature**

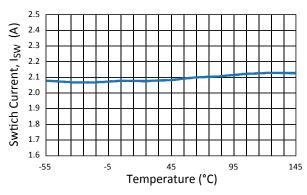

#### **Switch Current Limit versus Ambient Temperature**

#### **Functional Description**

The A8513 incorporates a current-mode boost controller with internal DMOS switch, and a single LED current sink. It can be used to drive an LED string of up to 14 white LEDs in series, with current up to 150 mA. For optimal efficiency, the output of the boost stage is adaptively adjusted to the minimum voltage required to power the LED string. This is expressed by the following equation:

$$V_{\text{OUT}} = V_{\text{LED}} + V_{\text{REG}} \tag{1}$$

where

V<sub>LED</sub> is the voltage drop across the LED string, and

$V_{REG}$  is the regulation voltage of the LED current sink (typically 0.88 V at the maximum LED current).

#### **Enabling the IC**

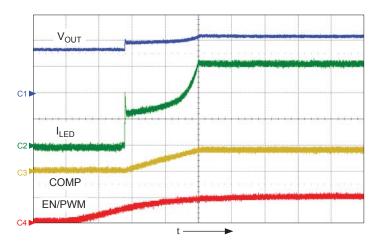

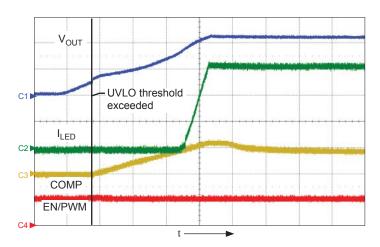

The IC turns on when a logic high signal is applied to the EN/PWM pin (figure 1), and turns off when this pin is pulled to a logic low. For the device to be enabled, the voltage on the VIN pin must be greater than  $V_{\rm UVLOrise}$  to clear the undervoltage lockout (UVLO) threshold (figure 2). Before startup, the A8513 goes through a system check to determine if there are any fault conditions that would prevent the system from functioning correctly.

#### Powering up: LED pin short to GND check

After the VIN pin goes above  $V_{UVLOrise}$ , the IC checks if the LED pin is shorted to GND by pre-charging the LED pin (figure 3). When the voltage on the LED pin exceeds 260 mV, the A8513 proceeds with soft start. If a short is present on the LED pin, the

Figure 1. Start-up by slowly ramping up EN/PWM with  $V_{IN}$  at 16 V; shows  $V_{OUT}$  (ch1, 10 V/div.),  $I_{LED}$  (ch2, 50 mA/div.), COMP (ch3, 1 V/div.), and EN/PWM (ch4, 2 V/div.), time = 2 ms/div.

IC will not power up until the short is removed. At this time the output is also checked for a  $V_{OUT}$  short, using the OVP pin. If the OVP pin does not rise above  $V_{OVPLO(th)}$  the IC will not power up.

#### Soft start function

During soft start, the COMP pin delivers a steady 80 uA current, the LED pin current gain is set to  $A_{\rm ILEDSS}$ . The lower gain will help limit the inrush current generated by charging the output

Figure 2. Start-up by slowly ramping up  $V_{IN}$  with EN/PWM at 2 V; shows  $V_{OUT}$  (ch1, 10 V/div.),  $I_{LED}$  (ch2, 50 mA/div.), COMP (ch3, 1 V/div.), and EN/PWM (ch4, 2 V/div.), time = 2 ms/div.

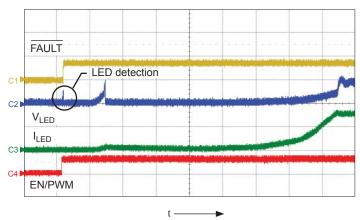

Figure 3. LED detection period; shows  $\overline{FAULT}$  (ch1, 5 V/div.), V<sub>LED</sub> (ch2, 1 V/div.), I<sub>LED</sub> (ch3, 100 mA/div.), and EN/PWM (ch4, 5 V/div.), time = 500  $\mu$ s/div.

capacitors. After the A8513 senses there is enough voltage on the LED pin, it increases the LED current to the preset regulation current. The COMP pin will continue to source 80 uA until the LEDs are able to run at the full preset current level.

#### **Boost converter frequency**

The switching frequency of the boost regulator is preset internally to one of four frequencies. The frequency options are:

| Part Number    | Switching Frequency (f <sub>SW</sub> ) (MHz) |

|----------------|----------------------------------------------|

| A8513KLYTR-1-T | 2                                            |

| A8513KLYTR-2-T | 1                                            |

| A8513KLYTR-3-T | 0.5                                          |

| A8513KLYTR-4-T | 0.25                                         |

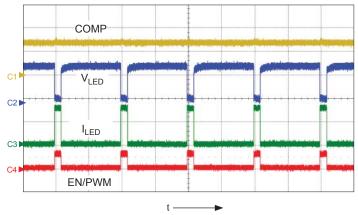

Figure 4. Typical PWM dimming sequence, with PWM dimming frequency of 1000 Hz and 10% duty cycle; shows COMP (ch1, 1 V/div.),  $V_{LED}$  (ch2, 10 V/div.),  $I_{LED}$  (ch3, 100 mA/div.), and EN/PWM (ch4, 5 V/div.), time = 500  $\mu$ s/div.

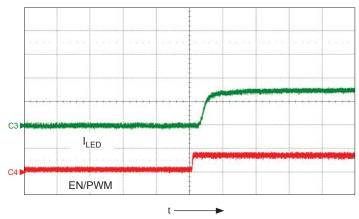

Figure 5. Typical EN/PWM signal (5 V/div.) to LED current (100 mA/div.) turn-on delay. The delay measured about 250 ns.  $V_{\rm IN}$  is 12 V,  $V_{\rm OUT}$  for 10 series LEDs is approximately 36 V,  $I_{\rm LED}$  is 150 mA. (time = 500 ns/div.)

#### LED current setting and LED dimming

The LED current,  $I_{LED}$ , is set using the ISET pin, and can range from 40 to 150 mA. Connect a resistor,  $R_{ISET}$ , between this pin and GND to set the  $I_{LED}$  current, according to the following formula:

$$I_{\text{LED}} = \frac{V_{\text{ISET}}}{R_{\text{ISET}}} \times A_{\text{ISET}}$$

$$= \frac{1.003 \text{ V}}{R_{\text{ISET}}} \times 1045$$

(2)

where  $I_{LED}$  is in A and  $R_{ISET}$  is in  $\Omega$ .

This formula sets the maximum current through the LEDs, which is referred to as the 100% current.

#### **PWM** dimming

The LED current can be reduced from the 100% current level by PWM dimming using the EN/PWM pin. When the EN/PWM pin is pulled high, the A8513 turns on and the LED pin sinks 100% current (figure 4). When EN/PWM is pulled low, the boost converter and LED sink are turned off. The compensation (COMP) pin is floated, and critical internal circuits are kept active.

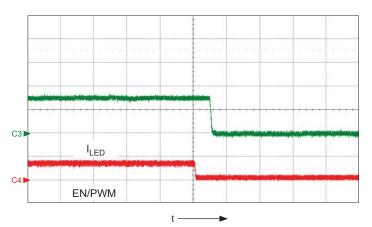

The A8513 has very fast turn-on and turn-off times during PWM dimming to minimize low PWM duty cycle errors. The typical PWM signal delay  $t_{dPWM(on)}$  is 250 ns (figure 5). The typical  $t_{dPWM(off)}$  time, between the PWM signal and the LED current going low, is shown in figure 6.

#### Analog dimming

The A8513 can also be dimmed by using an external DAC or other voltage source applied either directly to the ground side of the  $R_{\rm ISET}$  resistor or through an external resistive divider to the

Figure 5. Typical EN/PWM signal (5 V/div.) to LED current (100 mA/div.) turn-off delay. The typical delay is about 250 ns. (time = 500 ns/div.)

ISET pin. The limitation of this form of dimming is that the internal  $I_{SET}$  error amplifier is designed to work from 40 to 160  $\mu A$ , thus limiting the dimming ratios that can be achieved.

Figure 7, top panel is a typical application using a DAC to control the LED current using a single resistor connected to the ISET pin. The I<sub>SET</sub> current is controlled by the following formula:

$$I_{\text{SET}} = \frac{V_{\text{ISET}} - V_{\text{DAC}}}{R_{\text{ISET}}} \tag{3}$$

Where  $V_{\mbox{\scriptsize ISET}}$  is the ISET pin voltage and  $V_{\mbox{\scriptsize DAC}}$  is the DAC output voltage.

When the DAC voltage is equal to  $V_{\rm ISET}$ , the internal reference, there is no current through  $R_{\rm ISET}$ . When the DAC voltage starts to decrease, the ISET current starts to increase, thus increasing the LED current. When the DAC voltage is 0 V, the LED current will be at its maximum.

• For a dual-resistor configuration (lower panel of figure 7), the ISET current is controlled by the following formula:

$$I_{\text{SET}} = \frac{V_{\text{ISET}}}{R_{\text{ISET}}} - \frac{V_{\text{DAC}} - V_{\text{ISET}}}{R_1} \tag{4}$$

The advantage of this circuit is that the DAC voltage can be higher or lower, thus adjusting the LED current to a higher or

Figure 7. Simplified diagram of voltage LED current control (upper) single resistor, and (lower) dual resistors.

lower value of the preset LED current set by the R<sub>ISET</sub> resistor:

- $^{\circ}$  V<sub>DAC</sub> = 1.003 V; the output is strictly controlled by R<sub>ISET</sub>

- $^{\circ}$  V<sub>DAC</sub> > 1.003 V; the LED current is reduced

- $^{\circ}$  V<sub>DAC</sub> < 1.003 V; the LED current is increased

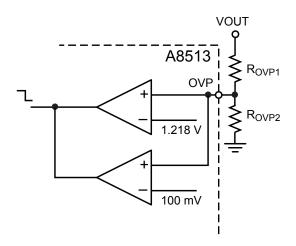

## Output Overvoltage Protection (OVP) and Output Undervoltage Protection (UVP)

The A8513 has output overvoltage protection (OVP), output undervoltage protection and secondary overvoltage protection (open diode).

**Overvoltage Protection** The OVP pin has a threshold,  $V_{OVPHI(th)}$ , of 1.218 V. A resistive divider can be used to set the  $V_{OUT}$  overvoltage protection threshold up to 45 V (see figure 8). There is no restriction on the value of the resistor chosen, but it is recommended that the divider current be kept between 10 and 60  $\mu$ A. This will minimize the effect of sense current on the accuracy of OVP, and minimize output voltage bleed-off during PWM dimming.

Formulas for calculating the OVP resistor voltage divider are shown below.

$$R_{OVP1} = (V_{OVP} - 1.218 \text{ V}) / I_{SET}$$

(5)

$$R_{OVP2} = 1.218 \text{ V} / I_{SET}$$

(6)

The OVP function is not inherently a latched fault. If the OVP condition occurs during a load dump, the IC will stop switching but not shut down.

Figure 8. Simplified diagram of the OVP pin functions.

The OVP condition can become a latched fault if, during an OVP event, the LED current is not in regulation. This typically occurs during an open LED string situation. If both faults occur simultaneously the IC will shut down and the fault flag will be set (see figures 9, 10, and 11).

**Undervoltage Protection** The OVP pin is also used to detect output undervoltage protection (UVP) against  $V_{OUT}$  short to GND. When the UVP fault is tripped, the fault flag is set (figure 12). Using an external PMOSFET interfaced to the  $\overline{FAULT}$  pin (figure 13), the user can disconnect the IC from VIN during a fault event.

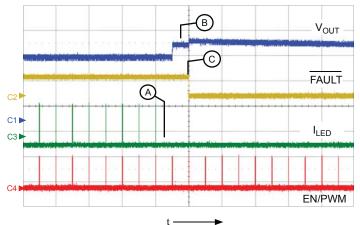

Figure 9. Open LED condition during PWM dimming. (A) The LED string (ch3, 100 mA/div.) is opened (no current flow through the LED pin) during an off-period for the PWM dimming signal (ch4, 5 V/div.). (B) At the next PWM cycle, the LED open condition is detected and the A8513 starts boosting the output voltage (ch1, 10 V/div.). (C) Upon reaching the OVP threshold and sensing no LED current flow, the A8513 shuts down and sets the fault flag (ch2, 5 V/div.). (time = 10 ms/div.)

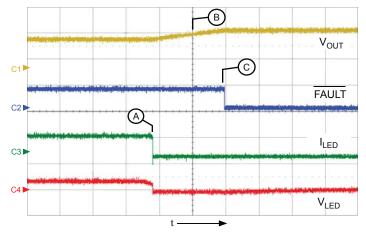

Figure 10. Open LED condition when PWM duty cycle is 100%. (A) The LED string (ch3, 200 mA/div.) is opened (no current flow through the LED pin). (B) The A8513 starts boosting the output voltage (ch1, 20 V/div.). (C) Upon reaching the OVP threshold there is still no current flow through the LED pin, and the A8513 shuts down and sets the fault flag (ch2, 5 V/div.). The LED pin voltage is ch4, 2 V/div. (time = 50  $\mu$ s/div.)

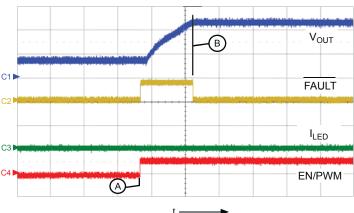

Figure 11. Power-up into an open LED situation. (A) A8513 enabled, (B) fault flag (ch2, 5 V/div.) is set when OVP threshold is reached. Shows  $V_{OUT}$  (ch1, 20 V/div.),  $I_{LED}$  (ch3, 100 mA/div.), and EN/PWM (ch4, 5 V/div.), time = 1 ms/div.

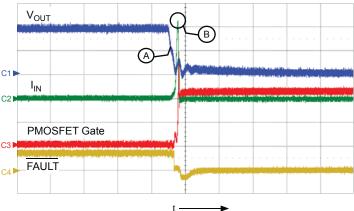

Figure 12. Input disconnect switch function during an output short. (A)  $V_{OUT}$  (ch1, 10 V/div.) falls during VOUT short to ground, (B) high peak current present due to short, before the PMOSFET (ch3, 5 V/div.) is disconnected. Shows input current (ch2, 10 A/div.) and fault flag (ch4, 5 V/div.), time = 50  $\mu$ s/div.

Figure 13. typical circuit for input disconnect switch.

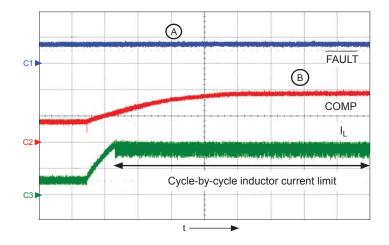

**Secondary Overvoltage Protection** The A8513 has secondary overvoltage protection for the internal boost switch in the event of an open diode condition. If the voltage on the SW pin exceeds the device safe operating voltage rating, the A8513 is disabled and remains latched off (figure 14). The EN/PWM pin must be brought low longer than  $t_{PWML}$  to clear this fault.

#### **Boost switch overcurrent protection**

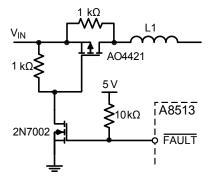

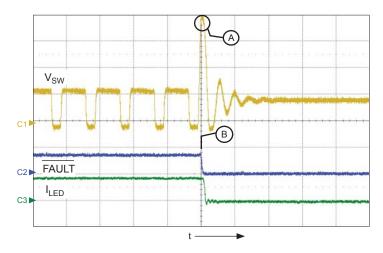

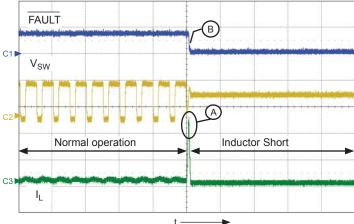

The boost switch is protected with cycle-by-cycle current limiting set to  $I_{SW(LIM)}$  (figure 15). There is also a secondary current limit that is sensed on the boost switch. When this current limit is exceeded, the A8513 immediately shuts down (figure 16). The secondary current limit is above the cycle-by-cycle current limit and protects the switch from destructive currents if the boost inductor is shorted.

Figure 15. Cycle-by-cycle current limit, inductor current is C3 (1 A/div.). (A) Fault flag (ch1, 5 V/div.) is not set during cycle-by-cycle current limit, (B) COMP pin signal (C2, 2 V/div.) is close to 3.6 V. (time = 1 ms/div.)

Figure 14. Secondary Overvoltage protection tripped when the switching diode is opened during operation. (A) High voltage is detected on SW node (ch1, 20 V/div.) and the A8513 is shut down. (B) Fault flag is set (ch2, 5 V/div.). Shows LED current (ch3, 100 mA/div.), time = 500 ns/div.

Figure 16. Secondary current limit during an inductor short condition. (A) limit is reached, (B) the IC shuts down and the fault flag is set. Shows fault flag (c1, 5 V/div.), switch node voltage (C2, 20 V/div.), and current through the inductor (C3, 2 A/div.); time = 1 µs/div.

#### **Input UVLO**

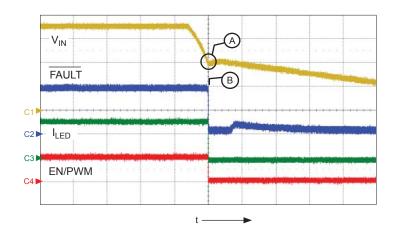

When  $V_{IN}$  rises above the UVLO threshold  $V_{UVLOrise}$ , the A8513 can be enabled by asserting EN/PWM. The A8513 is disabled when  $V_{IN}$  falls below  $V_{UVLOfall} - V_{UVLOhys}$  for more than 1  $\mu s$  (figure 17). This 1  $\mu s$  lag prevents false shut downs during momentary glitches on the input power supply.

#### VDD

The VDD pin provides regulated bias supply for internal circuits. Connect a capacitor,  $C_{VDD}$ , with a value of 0.01 to 0.1  $\mu F$  to this pin.

#### **Shutdown**

If the EN/PWM pin is pulled low for more than  $t_{PWML}$ , the device enters shutdown mode and clears all internal fault registers. In shutdown, the A8513 will disable all current sources and wait until EN/PWM goes high to re-enable the IC.

Figure 17. Input UVLO. (A) UVLO tripped ( $V_{IN}$ , ch1, 2 V/div.), (B) fault flag set (ch2, 2 V/ div.). Shows LED current (ch3, 100 mA/div.) and EN/PWM (ch4, 1 V/div.), time = 5 ms/div.

## A8513

## Wide Input Voltage Range, High Efficiency Fault Tolerant LED Driver

#### Fault protection during operation

The A8513 constantly monitors the state of the system to determine if any fault conditions occur. The response to a triggered fault condition is summarized in the table below.

Note: Some of the protection features might not be active during startup, to prevent false triggering of fault conditions.

The latching faults can be cleared in two ways:

- Keep the EN/PWM pin low for more than 16 ms.

- Cycle the power to create a UVLO condition.

Fault behavior diagrams are shown in figures 18, 19 and 20.

#### **Fault Mode Table**

| Fault Name                                                       | Туре         | Active  | Fault<br>Flag Set                                | Description                                                                                                                                                                                                                                                                                                       | Boost                  | Sink<br>driver |

|------------------------------------------------------------------|--------------|---------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------------|

| Primary Switch Current Protection (cycle-by-cycle current limit) | Auto-restart | Always  | No                                               | This fault condition is triggered by the cycle-by-cycle current limit $I_{SW(LIM)}$ . Prevents current in inductor from exceeding $I_{SW(LIM)}$ .                                                                                                                                                                 | Off for a single cycle | On             |

| Secondary Switch<br>Current Limit                                | Latched      | Always  | Yes                                              | When the current through the boost switch exceeds the secondary current SW limit, I <sub>SW(LIM2)</sub> , the A8513 immediately shuts down.                                                                                                                                                                       | Off                    | Off            |

| Secondary OVP                                                    | Latched      | Always  | Yes                                              | Secondary overvoltage protection is used for open diode detection. When diode D1 opens, the switch pin voltage will increase until V <sub>OVP(sec)</sub> is reached.                                                                                                                                              | Off                    | Off            |

| LED Pin Short<br>Protection                                      | Auto-restart | Startup | Yes                                              | This fault prevents the A8513 from starting-up if the LED pin is shorted to ground. After the short is removed, soft-start is allowed to begin.                                                                                                                                                                   | Off                    | Off            |

| ISET Short<br>Protection                                         | Auto-restart | Always  | Yes                                              | This fault occurs when the I <sub>SET</sub> current goes above 150% of the maximum Allowable ISET Current, I <sub>SET</sub> (max). The boost will stop switching and the IC will disable the LED sinks until the fault is removed. When the fault is removed, the IC tries to regulate to the preset LED current. | Off                    | Off            |

| LED String Open<br>Protection                                    | Latched      | Always  | Yes                                              | This fault occurs when the OVP pin exceeds the V <sub>OVPHI(th)</sub> threshold. The A8513 immediately stops switching. If at the same time, the LED voltage is below regulation, the IC will shut down.                                                                                                          | Off                    | Off            |

| Output Overvoltage<br>Protection                                 | Auto-restart | Always  | No                                               | This fault occurs when the OVP pin exceeds V <sub>OVPHI(th)</sub> threshold (for example, during a load dump). The A8513 immediately stops switching, but continues to sink current through the LED pin.                                                                                                          | Off                    | On             |

| Output<br>Undervoltage<br>Protection                             | Auto-restart | Always  | Yes                                              | This fault occurs when the OVP pin senses less than 110 mV on the pin.                                                                                                                                                                                                                                            | Off                    | Off            |

| Overtemperature<br>Protection                                    | Auto-restart | Always  | Yes                                              | This fault occurs when the die temperature exceeds $T_{\text{TSD}}$ .                                                                                                                                                                                                                                             | Off                    | Off            |

| VIN UVLO                                                         | NA           | Always  | Yes until<br>internal<br>regulator<br>shuts down | This fault occurs when $V_{\text{IN}}$ drops below $V_{\text{UVLOfall}}$ . This fault resets all latched faults.                                                                                                                                                                                                  | Off                    | Off            |

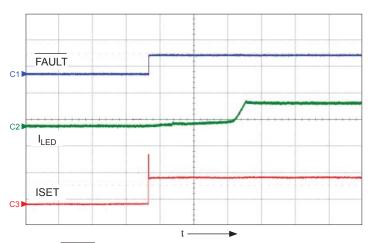

#### **ISET Short to Ground**

# C1 FAULT V<sub>SW</sub> C2 I<sub>LED</sub> C3 ISET

Figure 18.  $\overline{\text{FAULT}}$  (ch1, 5 V/div.),  $V_{\text{SW}}$  (ch2, 20 V/div.),  $I_{\text{LED}}$  (ch3, 100 mA/div.), and ISET (ch4, 1 V/div.), time = 1  $\mu$ s/div.

#### **Recovery from ISET Short to Ground**

Figure 19.  $\overline{\text{FAULT}}$  (ch1, 5 V/div.), I<sub>LED</sub> (ch2, 100 mA/div.), and ISET (ch3, 1 V/div.), time = 2 ms/div.

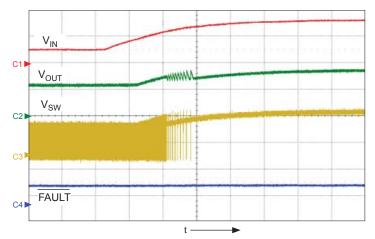

#### **OVP Tripped During Load Dump**

Figure 20.  $V_{\rm IN}$  (ch1, 20 V/div.),  $V_{\rm OUT}$  (ch2, 20 V/div.), and  $V_{\rm SW}$  (ch3, 20 V/div.),  $\overline{\rm FAULT}$  (ch4, 5 V/div.), time = 2 ms/div.

#### **Design Example**

This section provides a method for selecting component values when designing an application using the A8513. A typical circuit using this design is shown in figure 21.

Assumptions: For the purposes of this example, the following are given as the application requirements:

- V<sub>IN</sub>: 5 to 16 V

- Quantity of series LEDs, #<sub>SERIESLEDS</sub>: 6

- LED current, I<sub>LED</sub>: 120 mA

- V<sub>f</sub> at 120 mA: 3.2 V

- f<sub>SW</sub>: 2 MHz

- $T_{\Delta}$ (max): 85°C

- PWM dimming frequency: 200 Hz with a minimum duty cycle

Procedure: Select the appropriate configuration and the individual component values in an ordered sequence.

Step 1: Connect the series LED string from VOUT to the LED

Step 2: Determine the value for the I<sub>LED</sub> setting resistor, R<sub>ISET</sub>:

$$R_{\text{ISET}} = V_{\text{ISET}} \times A_{\text{ISET}} / I_{\text{LED}}$$

(7)

= (1.003 × 1045) / 120 mA = 8.74 k $\Omega$

Choose an  $8.66 \text{ k}\Omega$  resistor.

Step 3: Determine the values of the OVP resistors. The OVP resistors are connected between the OVP pin and the output voltage (VOUT) and the OVP pin and ground.

Step 3a: The first step is to determine the maximum voltage based on the LED V<sub>f</sub> requirements. To this value the regulation voltage should be added, as well as another 2 V to account for noise, output ripple, and resistor tolerances. The regulation voltage,  $V_{LED}$ , of the A8513 is 880 mV. Then:

$$V_{\text{OUT(OVP)}} = \#_{\text{SERIESLEDS}} \times V_{\text{f}} + V_{\text{LED}} + 2 \text{ V}$$

(8)

= 6 × 3.2 V+ 0.880 V + 2 V

= 22.08 V

To find the OVP resistor values, the user should choose a resistor divider that has very low current (I<sub>OVP</sub>) and R<sub>OVP</sub> should be approximately 1 M $\Omega$ . A good starting point is 50  $\mu$ A as  $I_{OVP}$ . (The I<sub>OVP</sub> current is used later in calculating the total leakage current.) Then:

$$R_{\text{OVP1}} = (V_{\text{OUT(OVP)}} - V_{\text{OVPHI(th)}}) / I_{\text{OVP}}$$

=  $(22.08 \text{ V} - 1.218 \text{ V}) / 50 \mu \text{A} = 417.2 \text{ k}\Omega$

and:

$$R_{\text{OVP2}} = V_{\text{OVPHI(th)}} / I_{\text{OVP}}$$

= 1.218 V / 50  $\mu$ A = 24.36 k $\Omega$

Choose a value of resistor that is higher value than the calculated  $R_{OVP}$ . In this case 422 k $\Omega$  was selected. Below is the actual value of the minimum OVP trip level with the selected resistor:

$$V_{\rm OUT(OVP)} = R_{\rm OVP} \times I_{\rm OVP} \times V_{\rm OVPHI(th)}$$

$$= 422 \text{ k}\Omega \times 50 \text{ } \mu\text{A} + 1.218 \text{ V} = 22.32 \text{ V}$$

(11)

STEP 3b: At this point a quick check should be done to determine if the conversion ratio is acceptable for the selected frequency:

$$D_{\text{maxofboost}} = 1 - t_{\text{SW(OFF)}} \times f_{\text{SW}}$$

$$= 1 - 85 \text{ ns} \times 2 \text{ MHz} = 83\%$$

(12)

where the Minimum Switch Off-Time,  $t_{SW(OFF)}$  is found in the Electrical Characteristics table.

The Theoretical Maximum V<sub>OUT</sub> is then calculated as:

$$V_{\text{OUT}}(\text{max}) = \frac{V_{\text{IN}}(\text{min})}{1 - D_{\text{maxofboost}}} - V_{\text{d}}$$

$$= \frac{5 \text{ V}}{1 - 0.83} - 0.4 \text{ V} = 29.01 \text{ V}$$

(13)

where V<sub>d</sub> is the diode forward voltage.

The Theoretical Maximum V<sub>OUT</sub> value must be greater than the value V<sub>OUT(OVP)</sub>. If this is not the case, a lower frequency version of the A8513 should be chosen to meet the maximum duty cycle requirements.

Step 4: Inductor selection. The inductor should be chosen such that it can handle the necessary input current. In most applications, due to stringent EMI requirements, the system must operate in continuous conduction mode throughout the whole input voltage range.

17

Step 4a: Determine the Duty Cycle:

$$D(\text{max}) = 1 - \frac{V_{\text{IN}}(\text{min})}{V_{\text{OUT}(\text{OVP})} + V_{\text{d}}}$$

$$= 1 - \frac{5 \text{ V}}{22.32 \text{ V} + 0.4 \text{ V}} = 78\%$$

(14)

where V<sub>d</sub> is the voltage drop of the boost diode.

Step 4b: Determine the maximum and minimum input current to the system. The minimum input current will dictate the inductor value. The maximum current rating will dictate the current rating of the inductor. Given  $I_{OUT} = I_{LED} = 120$  mA:

$$I_{\text{IN}}(\text{max}) = \frac{V_{\text{OUT}(\text{OVP})} \times I_{\text{OUT}}}{V_{\text{IN}}(\text{min}) \times \eta}$$

$$= \frac{22.32 \text{ V} \times 120 \text{ mA}}{5 \text{ V} \times 0.9} = 0.595 \text{ A}$$

(15)

where  $\eta$  is efficiency. Next, calculate minimum input current, as follows:

$$I_{IN}(min) = \frac{V_{OUT(OVP)} \times I_{OUT}}{V_{IN}(max) \times \eta}$$

$$= \frac{22.32 \text{ V} \times 120 \text{ mA}}{16 \text{ V} \times 0.9} = 0.19 \text{ A}$$

(16)

A good approximation of efficiency  $\eta$  can be taken from the efficiency curves located in the data sheet. A value of 90% is a good starting approximation.

STEP 4c: Determine the inductor value.

To assure that the inductor operates in continuous conduction mode the value of inductor should be set such that the  $\frac{1}{2}$  inductor ripple current is not greater than the average minimum input current. A good inductor choice for inductor ripple current is 30% of the maximum input current:

$$\Delta I_{L} = I_{IN}(\text{max}) \times 0.3$$

(17)

= 0.595 A × 0.3 = 0.18 A

then:

$$L = \frac{V_{\text{IN}}(\text{min})}{\Delta I_{\text{L}} \times f_{\text{SW}}} \times D(\text{max})$$

$$= \frac{5 \text{ V}}{0.18 \text{ A} \times 2 \text{ MHz}} \times 0.78 = 10.83 \text{ } \mu\text{H}$$

(18)

Double-check to make sure the  $\frac{1}{2}$  current ripple is less than  $I_{IN}(min)$ :

$$I_{\rm IN}(\rm min) > {}^{1}/_{2} \Delta I_{\rm L}$$

(19)

0.19 A > 0.09 A

A good inductor value to use would be 10 μH.

Step 4d: This step verifies that there is sufficient slope compensation for the inductor chosen. The required slope compensation value for different frequencies is listed below:

| f <sub>SW</sub><br>(MHz) | Slope Compensation (A/µs) |

|--------------------------|---------------------------|

| 2                        | 3.73                      |

| 1                        | 1.85                      |

| 0.500                    | 3.70                      |

| 0.250                    | 1.83                      |

Next insert the inductor value used in the design:

$$\Delta I_{\text{Lused}} = \frac{V_{\text{IN}}(\text{min}) \times D(\text{max})}{L_{\text{used}} \times f_{\text{SW}}}$$

$$= \frac{5 \text{ V} \times 0.78}{10 \text{ }\mu\text{H} \times 2.0 \text{ MHz}} = 0.20 \text{ A}$$

(20)

Calculate the minimum required slope:

Required Slope (min) =

$$\frac{\Delta I_{\text{Lused}} \times 1 \times 10^{-6}}{\frac{1}{f_{\text{SW}}} \times (1 - D(\text{max}))}$$

(21)

=

$$\frac{0.20 \text{ A} \times 1 \times 10^{-6}}{\frac{1}{2.0 \text{ MHz}} \times (1 - 0.78)} = 1.8 \text{ A/}\mu\text{s}$$

For a stable system, the required minimum slope must be smaller than the IC slope compensation.

Note: The slope compensation value is in A/ $\mu$ s; the 1×10-6 is a constant multiplier.

STEP 4e: Determine the inductor current rating:

I<sub>L</sub>minimum rating =

$$I_{IN}(max) + \frac{1}{2} \Delta I_{Lused}$$

(22)

= 0.595 A + 0.20 A / 2 = 0.695 A

Step 5: Choose the proper switching diode. The switching diode should be chosen for three characteristics when it is used in LED lighting circuitry. The first and most obvious are the current rating of the diode and the reverse voltage rating. The reverse voltage rating should be such that during operation condition the voltage rating of the device is larger than the maximum output voltage; in this case it is  $V_{OUT\,(OVP)}$ . The peak current through the diode is:

$$I_{\rm dp} = I_{\rm IN}({\rm max}) + \frac{1}{2} \Delta I_{\rm Lused}$$

(23)

= 0.595 A + 0.20 A / 2 = 0.695 A

The third major component in deciding the switching diode is the reverse current,  $I_R$ , characteristic of the diode. This characteristic is especially important when PWM dimming is implemented. During PWM off-time the boost converter is not switching. This results in a slow bleeding off of the output voltage, due to leakage currents.  $I_R$  can be a large contributor, especially at high temperatures. On the diode that was selected in this design, the current varies between 1 and 100  $\mu A$ .

Step 6: Choose the output capacitors. The output capacitors should be chosen such that they provide filtering for both the boost converter and for the PWM dimming function. The biggest factors that contribute to the size of the output capacitor is PWM dimming frequency and the PWM duty cycle. Another major contributor is leakage current,  $I_{lkg}$ . This current is a combination of the OVP resistor divider,  $I_{\rm OVP}$ , and the reverse leakage of the switching diode. In this design the PWM dimming frequency is

200 Hz and the minimum duty cycle is 1%. Typically the voltage variation on the output during PWM dimming must be less than 250 mV ( $V_{COUT}$ ) so that no audible noise can be heard. The capacitance can be calculated as follows:

$$C_{\text{OUT}} = I_{\text{lkg}} \times \frac{1 - D_{\text{dimming}}(\text{min})}{f_{\text{PWM}(\text{dimming})} \times V_{\text{COUT}}}$$

$$= 120 \,\mu\text{A} \times \frac{1 - 0.01}{200 \,\text{Hz} \times 0.250 \,\text{V}} = 2.38 \,\mu\text{F}$$

A capacitor larger than 2.38  $\mu F$  capacitor should be selected due to degradation of capacitance at high voltages on the capacitor. One ceramic 4.7  $\mu F$ , 50 V capacitor is a good choice to fulfill this requirement. Corresponding capacitors include:

| • | Vendor | Value       | Part number        |

|---|--------|-------------|--------------------|

|   | Murata | 4.7 μF 50 V | GRM32ER71H475KA88L |

|   | Murata | 2.2 µF 50 V | GRM31CR71H225KA88L |

The rms current through the capacitor is given by:

$$I_{\text{COUT}} \text{rms} = I_{\text{OUT}} \sqrt{\frac{D(\text{max}) + \frac{\Delta I_{\text{L}}}{I_{\text{IN}}(\text{max}) \times 12}}{1 - D(\text{max})}}$$

$$= 0.120 \text{ A} \sqrt{\frac{0.78 + \frac{0.20 \text{ A}}{0.595 \text{ A} \times 12}}{1 - 0.78}} = 0.23 \text{ A}$$

The output capacitor should have a current rating of at least 230 mA. The current rating of the 4.7  $\mu$ F, 50V capacitor is 1.5 A.

STEP 7: Select the input capacitor. The input capacitor should be selected such that it provides good filtering of the input voltage waveform. A good rule of thumb is to set the input voltage ripple,  $\Delta V_{IN}$  to be 1% of the minimum input voltage. The minimum input capacitor requirements are as follows:

$$C_{\rm IN} = \frac{\Delta I_{\rm L}}{8 \times f_{\rm SW} \times \Delta V_{\rm IN}}$$

$$= \frac{0.20 \text{ A}}{8 \times 2 \text{ MHz} \times 0.05 \text{ V}} = 0.25 \text{ }\mu\text{F}$$

(26)

The rms current through the capacitor is given by:

$$I_{\text{IN}} \text{rms} = \frac{I_{\text{OUT}} \times \frac{\Delta I_{\text{L}}}{I_{\text{IN}}(\text{max})}}{(1 - D(\text{max}))\sqrt{12}}$$

$$= \frac{0.120 \times \frac{0.20 \text{ A}}{0.595 \text{ A}}}{(1 - 0.78)\sqrt{12}} = 0.05 \text{ A}$$

(27)

A good ceramic input capacitor with ratings of 2.2  $\mu$ F, 50V or 4.7  $\mu$ F, 50 V will suffice for this application. Corresponding capacitors include:

| Vendor | Value       | Part number        |

|--------|-------------|--------------------|

| Murata | 4.7 μF 50 V | GRM32ER71H475KA88L |

| Murata | 2.2 µF 50 V | GRM31CR71H225KA88L |

Figure 21. A typical circuit designed using the example above in this section.

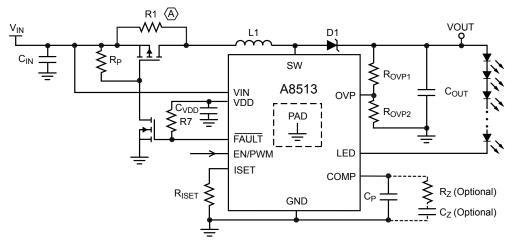

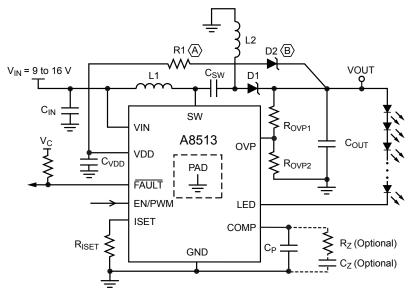

#### **Typical Application Drawings**

A R1 is used to provide a leakage path such that the OVP pin is above 100 mV during startup.

Otherwise the IC would assume the output is shorted to GND and would not proceed with soft start.

Figure 22. Typical application showing boost configuration and PMOS disconnect switch implementation

- (A) R1 is used to provide a leakage path such that the OVP pin is above 100 mV during startup.

Otherwise the IC would assume the output is shorted to GND and would not proceed with soft start.

- BD2 is a blocking diode.

Figure 23. Typical application showing SEPIC configuration

# Package LP, 16-Pin TSSOP with Exposed Thermal Pad

1.73 4.60

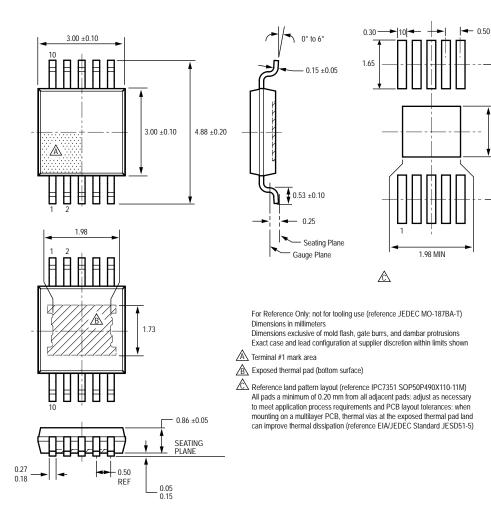

# Package LY, 10-Pin MSOP with Exposed Thermal Pad

## A8513

## Wide Input Voltage Range, High Efficiency Fault Tolerant LED Driver

#### **Revision History**

| Revision | Revision Date    | Description of Revision |

|----------|------------------|-------------------------|

| Rev. 2   | January 18, 2012 | Update Features List    |

|          |                  |                         |

Copyright ©2011-2012, Allegro MicroSystems, Inc.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in life support devices or systems, if a failure of an Allegro product can reasonably be expected to cause the failure of that life support device or system, or to affect the safety or effectiveness of that device or system.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.