# Dual Automotive, Audio Line Drivers with I<sup>2</sup>C Control and Diagnostic

### **General Description**

The MAX13325/MAX13326 dual audio line drivers provide a reliable differential interface between automotive audio components. The devices feature differential inputs and outputs, integrated output diagnostics, and are controlled using an I²C interface or operate in stand-alone mode. The outputs can deliver up to  $4V_{RMS}$  into  $100\Omega$  loads.

The MAX13325 buffers analog audio signals for transmission over long cable distances with a fixed gain of 12dB, whereas the MAX13326 provides a 0dB fixed gain. The diagnostics on the outputs report conditions on a per channel basis, including short to GND, short to battery, overcurrent, overtemperature, and excessive offset. The output amplifiers can drive capacitive loads up to 4nF to ground and 3nF differentially.

The outputs are protected according to IEC 61000-4-2  $\pm 8 \text{kV}$  Contact Discharge, and  $\pm 15 \text{kV}$  Air Gap. The MAX13325/MAX13326 are specified from -40°C to  $\pm 105$ °C and are available in a 28-pin TSSOP package with an exposed pad.

### \_Applications

Automotive Radio and Rear Seat Entertainment Professional Remote Audio Amplifiers

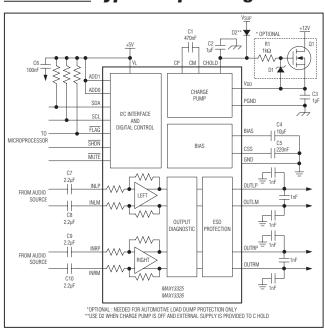

## Typical Operating Circuit

#### **Features**

- ♦ Comprehensive Programmability and Diagnostics Using I<sup>2</sup>C Interface

- ♦ Autoretry Function in Stand-Alone Mode

- ◆ Drive Capacitive Loads ≤ 3nF Differentially, ≤ 4nF to Ground

- ♦ 112dB Signal-to-Noise Ratio

- ♦ Low 0.002% THD at 4V<sub>RMS</sub> into 2.7kΩ Loads

- ♦ High PSRR (70dB at 1kHz)

- ♦ High CMRR (80dB at 1kHz)

- ♦ Low Output Noise (3µVRMS), MAX13326

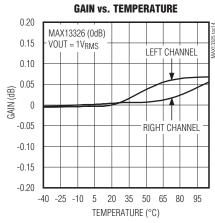

- **♦** Excellent Channel-to-Channel Matching

- **♦ Load-Dump Transient Protection**

- Protected Output Against Various Short-Circuit Conditions

- ♦ ESD Protection for ±8kV Contact Discharge, ±15kV Air Gap

- ♦ Long-Distance Drive Capability Typically Up to 15m or Greater

- ♦ Noise-Rejecting Differential Inputs and Outputs

- ♦ Low-Power Shutdown Mode < 10µA

- **♦** Hardware or Software MUTE Function

- ♦ 28-Pin TSSOP Package with Exposed Pad

## **Ordering Information**

| PART                   | PIN-<br>PACKAGE | TEMP RANGE         | GAIN<br>(dB) |

|------------------------|-----------------|--------------------|--------------|

| <b>MAX13325</b> GUI/V+ | 28 TSSOP-EP*    | -40°C to<br>+105°C | 12           |

| <b>MAX13326</b> GUI/V+ | 28 TSSOP-EP*    | -40°C to<br>+105°C | 0            |

/V denotes an automotive qualified part.

+Denotes a lead(Pb)-free/RoHS-compliant package.

\*EP = Exposed pad.

# **Dual Automotive, Audio Line Drivers** with I<sup>2</sup>C Control and Diagnostic

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to PGND           |                         |

|-----------------------------------|-------------------------|

|                                   |                         |

| V <sub>L</sub> to GND             |                         |

| GND, PGND                         | 0.3V to +0.3V           |

| OUT_ to PGND                      | 0.3V to 28V             |

| IN_, BIAS to AGND                 | -0.3V to $(VDD + 0.3V)$ |

| SCL, SDA, ADD0, ADD1, MUTE, SHDN, |                         |

| FLAG to GND                       | 0.3V to +6V             |

| OUT_ Short Circuit to PGND or VDD | Continuous              |

| Short Circuits Between Any OUT                                         | Continuous    |

|------------------------------------------------------------------------|---------------|

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) (multiplication) |               |

|                                                                        |               |

| 28-Pin TSSOP (derate 27mW/°C above +70°C)                              | 2162.2mW      |

| Operating Temperature Range40                                          | )°C to +105°C |

| Storage Temperature Range65                                            | 5°C to +150°C |

| Junction Temperature                                                   | +150°C        |

| Lead Temperature (soldering, 10s)                                      | +300°C        |

| Soldering Temperature (reflow)                                         | +260°C        |

|                                                                        |               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **PACKAGE THERMAL CHARACTERISTICS (Note 1)**

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ )..........37°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )............2°C/W

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = 14.4V, V_{L} = 5V, R_{L} = \infty, load impedance from OUT_+ to OUT_-, T_{A} = T_{J} = -40^{\circ}C$  to  $+105^{\circ}C$ , typical values are  $T_{A} = +25^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                               | SYMBOL                       | CON                                               | MIN                                            | TYP  | MAX   | UNITS |    |  |

|-----------------------------------------|------------------------------|---------------------------------------------------|------------------------------------------------|------|-------|-------|----|--|

| AMPLIFIER DC CHARACTERIST               | AMPLIFIER DC CHARACTERISTICS |                                                   |                                                |      |       |       |    |  |

| Transient Supply Voltage (Load Dump)    | VDDMAX                       | Using external nMO duration                       | S-RTR020N05, 300ms                             |      |       | 50    | V  |  |

| Operating Cumply Voltage Bange          | V <sub>DD</sub>              |                                                   |                                                | 4.5  |       | 18    | V  |  |

| Operating Supply Voltage Range          | VL                           |                                                   |                                                | 2.7  |       | 5.5   | V  |  |

| VDD OVLO Threshold                      | VDDOV                        | Rising edge                                       |                                                | 18.5 | 19.2  |       | V  |  |

| V <sub>DD</sub> UVLO Threshold          | V <sub>DDUV</sub>            | Falling edge                                      |                                                | 3.3  | 3.5   |       | V  |  |

| V <sub>L</sub> UVLO Threshold           | V <sub>LUV</sub>             | Falling edge                                      |                                                | 2.2  | 2.4   |       | V  |  |

| Supply Current                          | loo                          | $T_A = +25$ °C, no load                           |                                                |      | 39    |       | mA |  |

| Supply Current                          | IDD                          | $T_A = -40^{\circ}C$ to $+105^{\circ}C$ , no load |                                                |      |       | 50    | mA |  |

| Logic Supply Current                    | IL                           | V <sub>L</sub> = 5V                               |                                                |      | 1.7   |       | mA |  |

|                                         |                              | Inn                                               | T <sub>A</sub> = +25°C                         |      | 0.5   | 10    |    |  |

| Shutdown Supply Current                 | ISHDN                        | IDD                                               | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C$ |      | 0.5   |       | μΑ |  |

|                                         |                              | IL                                                |                                                |      | < 0.1 | 2     | μΑ |  |

| Turn-On Time (from Shutdown)            |                              | MUTE = VL                                         |                                                |      | 220   |       | ms |  |

| Turn-On Time (from Mute)                |                              | SHDN = VL, Ccss =                                 | = 220nF                                        |      | 6     |       | ms |  |

| Differential Input Resistance           | RINDIF                       | Measure across input                              |                                                | 18   | 24    | 30    | kΩ |  |

| Cia ala Fa da di ara di la cara da cara | Duri                         | Each input to ground (MAX13325)                   |                                                | 15   | 20    | 25    |    |  |

| Single-Ended Input Impedance            | RIN                          | Each input to ground (MAX13326)                   |                                                | 12   | 16    | 20    | kΩ |  |

| Oi Dth- Oi (NIt O)                      | Δ                            | MAX13325                                          |                                                | 11.8 | 12    | 12.2  | dB |  |

| Signal-Path Gain (Note 3)               | Av                           | MAX13326                                          |                                                | -0.2 | 0     | +0.2  |    |  |

# **Dual Automotive, Audio Line Drivers** with I<sup>2</sup>C Control and Diagnostic

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 14.4V, V_{L} = 5V, R_{L} = \infty, load impedance from OUT_+ to OUT_-, T_{A} = T_{J} = -40^{\circ}C$  to  $+105^{\circ}C$ , typical values are  $T_{A} = +25^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                                                                | SYMBOL | COND                                                                                                                                      | ITIONS                                                  | MIN   | TYP                 | MAX  | UNITS |  |

|--------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-------|---------------------|------|-------|--|

| Channel-to-Channel Gain<br>Tracking                                      |        |                                                                                                                                           |                                                         |       |                     | ±0.4 | dB    |  |

| Differential Mode Output Balance<br>OUT_+ to OUT (Note 4)                |        |                                                                                                                                           |                                                         |       | -40                 |      | dB    |  |

| Output Offset Voltage (OUT_+ to OUT)                                     | Voos   | $\overline{\text{MUTE}} = \text{GND}, T_{A} = + \overline{\text{MUTE}} = V_{L}, T_{A} = +25$                                              |                                                         |       | ±0.5<br>±0.2        | ±10  | mV    |  |

| BIAS Voltage                                                             | VBIAS  | Relative to V <sub>DD</sub>                                                                                                               |                                                         |       | 50                  | 52.5 | %     |  |

| BIAS Impedance                                                           | ZBIAS  | $IBIAS = \pm 10\mu A$                                                                                                                     |                                                         | 69    | 92                  | 115  | kΩ    |  |

| Output-Voltage Swing Differential                                        | 2      | $V_{DD} = 14.4V, V_{IN} = \pm V_{DD} = 5.0V, V_{IN} = \pm 5.0V$                                                                           |                                                         | ±12.5 |                     |      | V     |  |

| Power-Supply Rejection Ratio                                             | PSRR   | V <sub>DD</sub> = 4.5V to 18V<br>V <sub>DD</sub> = 14.5V, +500m\<br>V <sub>DD</sub> = 14.5V, +500m\                                       | /p-p ripple at 1kHz                                     | -80   | -96<br>-95<br>-80   |      | dB    |  |

| Common-Mode Rejection Ratio                                              | CMRR   | VIN = 1VRMS, 100Hz 1                                                                                                                      |                                                         | -48   | -80                 |      | dB    |  |

| AMPLIFIER AC CHARACTERIST                                                | ics    |                                                                                                                                           |                                                         |       |                     |      |       |  |

| Total Harmonic Distortion Plus                                           |        | $V_{OUT} = 4V_{RMS}, R_L = 2.7k\Omega$<br>$V_{OUT} = 4V_{RMS}, R_L = 1k\Omega$                                                            |                                                         |       | 0.002               |      |       |  |

| Noise (Note 5)                                                           | THD+N  | $V_{OUT} = 4V_{RMS}$ , $R_L = 100Ω$ , $V_{DD} = 8V$<br>$V_{OUT} = 7V_{RMS}$ , $R_L = 1kΩ$                                                 |                                                         |       | 0.03                |      | %     |  |

| Total Harmonic Distortion Plus<br>Noise at V <sub>DD</sub> = 5V (Note 5) | THD+N  | VOUT = 1V <sub>RMS</sub> , R <sub>L</sub> =<br>VOUT = 1V <sub>RMS</sub> , R <sub>L</sub> =<br>VOUT = 2V <sub>RMS</sub> , R <sub>L</sub> = | 1kΩ                                                     |       | 0.01<br>0.02<br>0.8 |      | %     |  |

| Capacitive-Load Stability                                                |        | VOUT = 2 VRMS, NL =                                                                                                                       | 1/22                                                    |       | 0.0                 | 3    | nF    |  |

| Capacitive-Load Drive Capability                                         |        | No sustained oscillation                                                                                                                  | C <sub>LOAD</sub> to GND C <sub>LOAD</sub> differential |       |                     | 4 3  | nF    |  |

| Signal-to-Noise Ratio (Note 5)                                           | SNR    | MAX13325, gain = 12<br>A-weighted                                                                                                         | •                                                       |       | 112                 |      | - dB  |  |

| Signal-to-Noise Hatio (Note 3)                                           | ONIT   | MAX13326, gain = 0c<br>A-weighted                                                                                                         | IB, VOUT = 4VRMS,                                       |       | 122                 |      | GD.   |  |

| Unity-Gain Bandwidth                                                     |        |                                                                                                                                           |                                                         |       | 3                   |      | MHz   |  |

| Output Slew Rate                                                         |        |                                                                                                                                           |                                                         |       | 2.5                 |      | V/µs  |  |

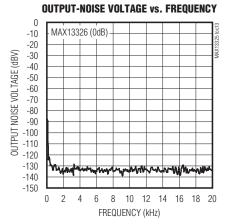

| Output-Voltage Noise                                                     |        | A-weighted, MAX1332                                                                                                                       | 25                                                      |       | 10                  |      | μV    |  |

| Output-voltage Noise                                                     |        | A-weighted, MAX13326                                                                                                                      |                                                         |       | 3                   |      | μν    |  |

| Crosstalk                                                                |        | V <sub>IN</sub> = 1V <sub>RMS</sub> , 1kHz                                                                                                |                                                         |       | -110                |      | dB    |  |

| Mute Time                                                                |        | To achieve soft mute,                                                                                                                     | Ccss = 220nF                                            |       | 4                   |      | ms    |  |

| Mute Attenuation                                                         |        | V <sub>IN</sub> = 1V <sub>RMS</sub> , 1kHz                                                                                                |                                                         |       | -75                 |      | dB    |  |

| Click-and-Pop Level (Note 6)                                             | KCP    | Into and out of mute                                                                                                                      |                                                         |       | -70                 |      | dBV   |  |

| Click-and-Pop Level (Note 6)                                             | KCP    | Into and out of shutdo                                                                                                                    | own, 1kΩ                                                |       | -45                 |      | dBV   |  |

# **Dual Automotive, Audio Line Drivers** with I<sup>2</sup>C Control and Diagnostic

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 14.4V, V_{L} = 5V, R_{L} = \infty, load impedance from OUT_+ to OUT_-, T_{A} = T_{J} = -40^{\circ}C$  to  $+105^{\circ}C$ , typical values are  $T_{A} = +25^{\circ}C$ , unless otherwise noted.) (Note 2)

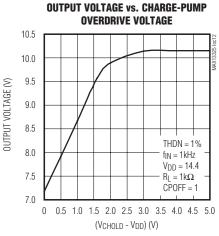

| PARAMETER                       | SYMBOL | CONDITIONS                                          |                    | MIN | TYP  | MAX | UNITS |

|---------------------------------|--------|-----------------------------------------------------|--------------------|-----|------|-----|-------|

| CHARGE PUMP                     |        |                                                     |                    |     |      |     |       |

| Charge-Pump Overdrive Voltage,  | \/     | V <sub>DD</sub> = 4.5V, I <sub>SOL</sub>            | JRCE = 6.6mA       | 3.2 | 4.0  |     | V     |

| VCHOLD - VDD (Hard Mode)        | VCPH   | V <sub>DD</sub> = 18V, I <sub>SOU</sub>             | RCE = 6.6mA        | 4.5 |      | 5.5 | V     |

| VCHOLD - VDD (Soft Mode)        | VCPS   | V <sub>DD</sub> unconnecte<br>V <sub>L</sub> = 3.3V | d, ISOURCE = 40µA, |     | 2.1  |     | V     |

|                                 |        | V <sub>L</sub> = 5V                                 |                    |     | 3.9  |     |       |

|                                 |        |                                                     | CPF[1:0] = 00      |     | 333  |     |       |

| Ola avera Division Financiani   | f      | ODOFF A                                             | CPF[1:0] = 01      |     | 190  |     | ]     |

| Charge-Pump Frequency           | fCP    | CPOFF = 0                                           | CPF[1:0] = 10      |     | 426  |     | kHz   |

|                                 |        |                                                     | CPF[1:0] = 11      |     | 260  |     |       |

| DIAGNOSTICS                     |        |                                                     |                    |     |      |     |       |

| Output Current Limit            |        | Short to GND or                                     | battery            |     | 580  |     | mA    |

| Current-Limit Warning Threshold |        |                                                     |                    |     | 230  |     | mA    |

| Open-Load Detection             |        |                                                     |                    | 10  |      |     | kΩ    |

| Output Offset Detection         |        | Valid when mute                                     | d                  |     | ±250 |     | mV    |

| Thermal Warning Threshold       |        |                                                     |                    |     | 135  |     | °C    |

| Thermal Shutdown Threshold      |        |                                                     |                    |     | 165  |     | °C    |

| Thermal Shutdown Hysteresis     |        |                                                     |                    |     | 15   |     | °C    |

| ESD PROTECTION                  |        |                                                     |                    |     |      |     |       |

| Air Gap IEC 61000-4-2           |        | OUT_ pins                                           |                    |     | ±15  |     | kV    |

| Contact Discharge IEC 61000-4-2 |        | OUT_ pins                                           |                    |     | ±8   |     | kV    |

| НВМ                             |        | All pins                                            |                    |     | ±2   |     | kV    |

# Dual Automotive, Audio Line Drivers with I<sup>2</sup>C Control and Diagnostic

#### **DIGITAL CHARACTERISTICS**

$(V_{DD} = 14.4V, V_{L} = 3.3V, T_{A} = T_{J} = -40^{\circ}C$  to  $+105^{\circ}C$ , typical values are  $T_{A} = +25^{\circ}C$ , unless otherwise noted.) (Note 2)

| PARAMETER                       | SYMBOL  | CONDITIONS                        | MIN                    | TYP | MAX                   | UNITS |

|---------------------------------|---------|-----------------------------------|------------------------|-----|-----------------------|-------|

| DIGITAL INTERFACE               |         |                                   |                        |     |                       |       |

| Input-Voltage High              | VINH    | $V_L = 2.7V \text{ to } 5.5V$     | 0.75 x VL              |     |                       | V     |

| Input-Voltage Low               | VINL    | $V_L = 2.7V \text{ to } 5.5V$     |                        |     | 0.25 x V <sub>L</sub> | V     |

| Input-Voltage Hysteresis        |         |                                   |                        | 50  |                       | mV    |

| Input Leakage Current           |         |                                   |                        |     | ±100                  | μΑ    |

| Output Low Voltage              |         | FLAG, SDA, ISINK = 3mA            |                        |     | 0.4                   | V     |

| Output Leakage Current          |         | FLAG, SDA = 5.5V                  |                        |     | 2                     | μΑ    |

| Stand-Alone FLAG Pulse Width    |         | ADD0, ADD1 = GND                  |                        | 100 |                       | ms    |

| Stand-Alone Fault Retry Time    |         | ADD0, ADD1 = GND                  |                        | 500 |                       | ms    |

| I <sup>2</sup> C TIMING         |         |                                   |                        |     |                       |       |

| Serial-Clock Frequency          | fscl    |                                   | 0                      |     | 400                   | kHz   |

| Bus Free Time                   | tBUF    | Between START and STOP conditions | 1.3                    |     |                       | μs    |

| Hold Time                       | tHD:STA | Repeated START condition          | 0.6                    |     |                       | μs    |

| SCL Low Time                    | tLOW    |                                   | 1.3                    |     |                       | μs    |

| SCL High Time                   | tHIGH   |                                   | 0.6                    |     |                       | μs    |

| Data Hold Time                  | thd:dat |                                   | 0                      |     | 900                   | ns    |

| Data Setup Time                 | tsu:dat |                                   | 100                    |     |                       | ns    |

| Bus Capacitance                 | CB      | Per bus line                      |                        |     | 400                   | pF    |

| Receiving Rise Time             | tR      | SCL, SDA                          | 20 + 0.1C <sub>B</sub> |     | 300                   | ns    |

| Receiving Fall Time             | tF      | SCL, SDA                          | 20 + 0.1C <sub>B</sub> |     | 300                   | ns    |

| Transmitting Fall Time          | tF      | SDA, V <sub>L</sub> = 3.6V        | 20 + 0.05CB            |     | 250                   | ns    |

| STOP Condition Setup Time       | tsu:sto |                                   | 0.6                    |     |                       | μs    |

| Pulse Width of Suppressed Spike | tsp     |                                   | 0                      |     | 50                    | ns    |

**Note 2:** All devices are 100% tested at  $T_A = +25$ °C. Limits over temperature are guaranteed by design.

Note 3: Signal path gain is defined as:  $20 \times log \left( \frac{\left| \left( V_{OUT_-+} \right) - \left( V_{OUT_--} \right) \right|}{\left| \left( V_{IN_-+} \right) - \left( V_{IN_--} \right) \right|} \right)$ .

Note 4: Measured in differential output mode, differential input voltage 4V<sub>P-P</sub> (for 0dB gain), 1V<sub>P-P</sub> (for 12dB gain) 1kHz.

Common-mode output balance is defined as:  $20 \times log \left( \frac{\left| \left( \left| V_{OUT_{-+}} \right| \right) - \left( \left| V_{OUT_{--}} \right| \right) \right|}{\left| \left( \left| V_{OUT_{-+}} \right| \right) + \left( \left| V_{OUT_{--}} \right| \right) \right| \times 2} \right)$

Note 5: 22Hz to 22kHz measurement bandwidth.

Note 6: KCP level is calculated as 20log[(peak voltage during mode transition, no input signal)/1V<sub>RMS</sub>]. Units are expressed in dBV.

# **Dual Automotive, Audio Line Drivers** with I<sup>2</sup>C Control and Diagnostic

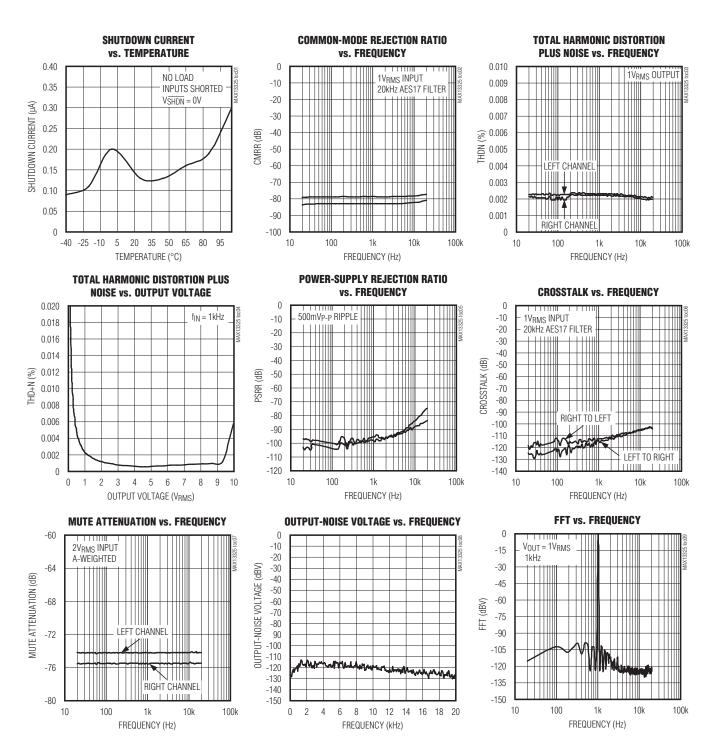

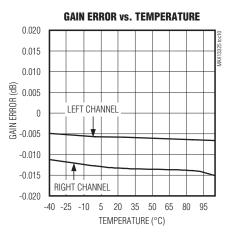

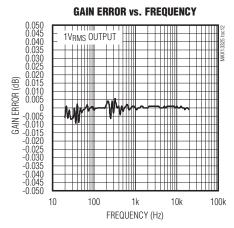

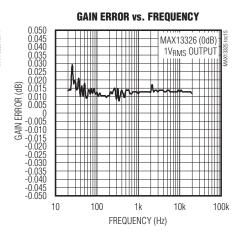

### **Typical Operating Characteristics**

$(V_{DD} = 14.4V, V_L = 5V, R_L = 1k\Omega, gain = 12dB, T_A = +25^{\circ}C, unless otherwise noted.)$

# **Dual Automotive, Audio Line Drivers** with I<sup>2</sup>C Control and Diagnostic

## Typical Operating Characteristics (continued)

$(V_{DD} = 14.4V, V_{L} = 5V, R_{L} = 1k\Omega, gain = 12dB, T_{A} = +25^{\circ}C, unless otherwise noted.)$

# **Dual Automotive, Audio Line Drivers** with I<sup>2</sup>C Control and Diagnostic

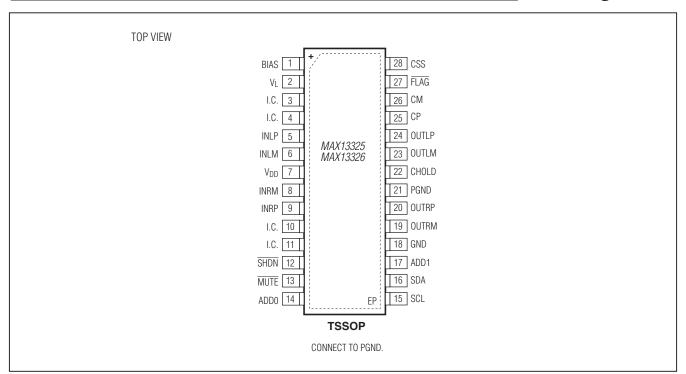

## **Pin Configuration**

# Pin Description

| PIN          | NAME | FUNCTION                                                                                                                                 |

|--------------|------|------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | BIAS | Analog Bias Voltage. Bypass BIAS to GND with a 10µF capacitor.                                                                           |

| 2            | VL   | Logic Supply Voltage. Connect V <sub>L</sub> to a 2.7V to 5V logic supply. Bypass V <sub>L</sub> to GND with a 0.1µF capacitor.          |

| 3, 4, 10, 11 | I.C. | Internally Connected. Leave unconnected.                                                                                                 |

| 5            | INLP | Left Audio Positive Input. Either input of each pair can be used as a single-ended input, with the complementary input bypassed to GND.  |

| 6            | INLM | Left Audio Negative Input. Either input of each pair can be used as a single-ended input, with the complementary input bypassed to GND.  |

| 7            | VDD  | Power-Supply Input. Connect VDD to the supply voltage. Bypass VDD to GND through a 1µF capacitor.                                        |

| 8            | INRM | Right Audio Negative Input. Either input of each pair can be used as a single-ended input, with the complementary input bypassed to GND. |

| 9            | INRP | Right Audio Positive Input. Either input of each pair can be used as a single-ended input, with the complementary input bypassed to GND. |

| 12           | SHDN | Shutdown Input. Drive SHDN low to power down the device.                                                                                 |

| 13           | MUTE | Mute Input. Drive MUTE low to mute the outputs. The outputs are low impedance in mute.                                                   |

# Dual Automotive, Audio Line Drivers with I<sup>2</sup>C Control and Diagnostic

## Pin Description (continued)

| PIN | NAME  | FUNCTION                                                                                                                                                                               |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14  | ADD0  | I <sup>2</sup> C Address Inputs. Connect ADD0 and ADD1 to V <sub>L</sub> , GND, SCL, or SDA to select 7 I <sup>2</sup> C addresses. Connect ADD0 and ADD1 to GND for stand-alone mode. |

| 15  | SCL   | Serial Clock                                                                                                                                                                           |

| 16  | SDA   | Serial-Data IO                                                                                                                                                                         |

| 17  | ADD1  | I <sup>2</sup> C Address Inputs. Connect ADD0 and ADD1 to V <sub>L</sub> , GND, SCL, or SDA to select 7 I <sup>2</sup> C addresses. Connect ADD0 and ADD1 to GND for stand-alone mode. |

| 18  | GND   | Analog Ground. Ground connection for the input bias and gain circuits.                                                                                                                 |

| 19  | OUTRM | Right Audio Negative Output. Each output is current limited.                                                                                                                           |

| 20  | OUTRP | Right Audio Positive Output . Each output is current limited.                                                                                                                          |

| 21  | PGND  | Power Ground. Ground connection for the output stage drivers.                                                                                                                          |

| 22  | CHOLD | Charge-Pump Output (When Charge Pump is On; CPOFF = 0). When the charge pump is off, provide an external supply through a diode to the CHOLD input. Bypass CHOLD with 1µF to PGND.     |

| 23  | OUTLM | Left Audio Negative Output. Each output is current limited.                                                                                                                            |

| 24  | OUTLP | Left Audio Positive Outputs. Each output is current limited.                                                                                                                           |

| 25  | CP    | Charge-Pump Flying Capacitor, Positive Connection                                                                                                                                      |

| 26  | СМ    | Charge-Pump Flying Capacitor, Negative Connection                                                                                                                                      |

| 27  | FLAG  | Open-Drain Fault Flag Output. FLAG indicates a fault on any one channel. In stand-alone mode, FLAG is stretched to a typical pulse width of 100ms.                                     |

| 28  | CSS   | Soft-Start Capacitor Connection. CSS is charged/discharged by < 100µA current to get soft mute/ play transition. Bypass to GND through a 220nF capacitor.                              |

| _   | EP    | Exposed Pad. Connect to PGND.                                                                                                                                                          |

### **Detailed Description**

The MAX13325/MAX13326 audio line drivers are designed to transmit audio data across noisy environments. The differential interface is highly resistant to noise injection from external sources common to automotive applications.

The MAX13325/MAX13326 operate in stand-alone or I<sup>2</sup>C-compatible mode with diagnostic outputs capable of detecting short to GND or battery, overcurrent, overtemperature, or excessive offset. A short across another audio output signal line is also protected.

**Table 1. Register Address Map**

| ADDRESS | REGISTER TYPE       | NAME   | READ/WRITE      | DEFAULT                   |

|---------|---------------------|--------|-----------------|---------------------------|

| 0x00    | Configuration       | CONFIG | Read/Write      | 0x00                      |

| 0x01    | Command Byte        | CMD    | Read/Write      | 0x00                      |

| 0x02    | General Fault       | GFAULT | Read            | 0x00                      |

| 0x03    | Left-Channel Fault  | LFAULT | Cleared on Read | 0x00                      |

| 0x04    | Right-Channel Fault | RFAULT | Cleared on Read | 0x00                      |

| 0x05    | Flag                | FLAG   | Read            | 0x04 (12dB)<br>0x05 (0dB) |

| 0x06    | General Mask        | GMASK  | Read/Write      | 0x00                      |

| 0x07    | Left-Channel Mask   | LMASK  | Read/Write      | 0x00                      |

| 0x08    | Right-Channel Mask  | RMASK  | Read/Write      | 0x00                      |

# **Dual Automotive, Audio Line Drivers** with I<sup>2</sup>C Control and Diagnostic

#### **Configuration Register**

**Table 2. Configuration Register Format**

| FUNCTION                  | ADDRESS    | REGISTER DATA |        |      |       |      | POR STATE |      |      |       |

|---------------------------|------------|---------------|--------|------|-------|------|-----------|------|------|-------|

| FUNCTION                  | CODE (HEX) | D7            | D6     | D5   | D4    | D3   | D2        | D1   | D0   | (HEX) |

| Configuration<br>Register | 0x00       | DIAG          | ENABLE | MUTE | CPOFF | OLDL | OLDR      | CPF1 | CPF0 | 0x00  |

DIAG: Set DIAG to 1 to enable diagnostic mode. Write '0' to disable diagnostic mode.

ENABLE: Set ENABLE bit to 1 to enable the device. Write '0' disables the device. Low on the SHDN pin overrides the ENABLE bit.

MUTE: Set the MUTE bit to 1 to mute both the output channels. Output is low impedance when in mute. Low on the MUTE pin input overrides the MUTE bit.

CPOFF: Set the CPOFF bit to 1 to turn off the charge pump. CHOLD pin must be externally supplied (see the VCPH parameter in the *Electrical Characteristics* table). Charge pump is enabled when CPOFF = 0.

OLDL: Write 1 to the OLDL bit to initiate the open-load detection for the left channel. To run OLDL again, write '0' and '1' again.

OLDR: Write 1 to the OLDR bit to initiate the open-load detection for the right channel. To run OLDR again, write '0' and '1' again.

Table 2a. Charge-Pump Frequency Bits

| CPF1 | CPF0 | FREQUENCY (kHz) |

|------|------|-----------------|

| 0    | 0    | 333             |

| 0    | 1    | 190             |

| 1    | 0    | 426             |

| 1    | 1    | 260             |

CPF[1:0]: Sets the frequency of the charge pump.

#### **Command Byte Register**

**Table 3. Command Byte Register Format**

| FUNCTION                 | ADDRESS    | REGISTER DATA |        |    |    |    |    |    |    | POR STATE |

|--------------------------|------------|---------------|--------|----|----|----|----|----|----|-----------|

| FUNCTION                 | CODE (HEX) | D7            | D6     | D5 | D4 | D3 | D2 | D1 | D0 | (HEX)     |

| Command Byte<br>Register | 0x01       | RETRYR        | RETRYL | Х  | Х  | Х  | Х  | Х  | Х  | 0x00      |

RETRYR: The right-channel power amplifier switches off after a fault condition. Write '1' to turn it back on after the fault condition.

RETRYL: The left-channel power amplifier switches off after a fault condition. Write '1' to turn on the left-channel power amplifier after the fault condition.

# Dual Automotive, Audio Line Drivers with I<sup>2</sup>C Control and Diagnostic

**General Faults**

**Table 4. General Fault Register Format**

| FUNCTION                  | ADDRESS    |    | REGISTER DATA |       |      |    |    |    |    | POR STATE |

|---------------------------|------------|----|---------------|-------|------|----|----|----|----|-----------|

| FUNCTION                  | CODE (HEX) | D7 | D6            | D5    | D4   | D3 | D2 | D1 | D0 | (HEX)     |

| General Fault<br>Register | 0x02       | Х  | TWARN         | TSHDN | DUMP | Х  | Х  | X  | х  | 0x00      |

TWARN: The TWARN bit is set to '1' when the temperature warning threshold is reached.

TSHDN: The TSHDN is set to '1' when the temperature shutdown threshold is reached.

DUMP: The DUMP bit is set to '1' when the V<sub>DD</sub> voltage exceeds the overvoltage threshold. Set the appropriate mask bit in the GMASK register to detect the general faults. See Table 8.

**Left-Channel Faults**

**Table 5. Left-Channel Fault Register Format**

|                                | ADDRESS       |       | REGISTER DATA |        |    |         |       |    |    |                    |

|--------------------------------|---------------|-------|---------------|--------|----|---------|-------|----|----|--------------------|

| FUNCTION                       | CODE<br>(HEX) | D7    | D6            | D5     | D4 | D3      | D2    | D1 | D0 | POR STATE<br>(HEX) |

| Left-Channel<br>Fault Register | 0x03          | SVDDL | SGNDL         | LIMITL | Х  | OFFSETL | OPENL | Х  | х  | 0x00               |

SVDDL: The SVDDL bit is set to '1' when a short to VDD is detected on the left channel.

SGNDL: The SGNDL bit is set to '1' when a short to GND is detected on the left channel.

LIMITL: The LIMITL bit is set to '1' when the current-limit threshold is tripped for left output.

OFFSETL: The OFFSETL bit is set to '1' when excessive offset is detected on the left-channel output.

OPENL: The OPENL bit is set to '1' when an open load is detected on the left channel.

Set the appropriate mask bit in the LMASK register to detect the faults on the left channel. See Table 9.

When any bit of the LFAULT register is high, the FLAG output is low.

#### **Right-Channel Faults**

**Table 6. Right-Channel Fault Register Format**

| •                               |               |               | •     |        |    |         |       |    |    |                    |

|---------------------------------|---------------|---------------|-------|--------|----|---------|-------|----|----|--------------------|

|                                 | ADDRESS       | REGISTER DATA |       |        |    |         |       |    |    | DOD CTATE          |

| FUNCTION                        | CODE<br>(HEX) | D7            | D6    | D5     | D4 | D3      | D2    | D1 | D0 | POR STATE<br>(HEX) |

| Right-Channel<br>Fault Register | 0x04          | SVDDR         | SGNDR | LIMITR | х  | OFFSETR | OPENR | Х  | Х  | 0x00               |

SVDDR: The SVDDR bit is set to '1' when a short to VDD is detected on the right channel.

SGNDR: The SGNDR bit is set to '1' when a short to GND is detected on the right channel.

LIMITR: The LIMITR bit is set to '1' when the current-limit threshold is tripped for right output.

OFFSETR: The OFFSETR bit is set to '1' when excessive offset is detected on the right-channel output.

OPENR: The OPENR bit is set to '1' when an open load is detected on the right channel.

Set the appropriate mask bit in the RMASK register to detect the faults on the right channel. See Table 10.

When any bit of the RFAULT register is high, the FLAG output is pulled low.

# Dual Automotive, Audio Line Drivers with I<sup>2</sup>C Control and Diagnostic

#### **FLAG Register**

### **Table 7. Flag Register Format**

|                  | ADDRESS       |      | REGISTER DATA           |        |         |         |     |                    |     | DOD STATE |

|------------------|---------------|------|-------------------------|--------|---------|---------|-----|--------------------|-----|-----------|

| FUNCTION         | CODE<br>(HEX) | D7   | D7 D6 D5 D4 D3 D2 D1 D0 |        |         |         |     | POR STATE<br>(HEX) |     |           |

| FLAG<br>Register | 0x05          | FLAG | LHIGHZ                  | RHIGHZ | OFFSETL | OFFSETR | ID2 | ID1                | ID0 | 0x04/0x05 |

FLAG: FLAG bit is set to '1' when the FLAG output is logic-low. The FLAG bit allows to quickly access the status of the device without using the FLAG output and without having to read all the fault registers.

LHIGHZ: The LHIGHZ bit is set to '1' when the left-channel output is high impedance; for example due to a short circuit.

RHIGHZ: The RHIGHZ bit is set to '1' when the right-channel output is high impedance; for example due to a short circuit.

OFFSETL: The OFFSETL bit is set to '1' when excessive offset is detected on the left-channel output.

OFFSETR: The OFFSETR bit is set to '1' when excessive offset is detected on the right-channel output.

ID[2:0]: The ID[2:0] bits indicate the device type (12dB = 100 and 0dB = 101).

#### **General Mask Register**

### **Table 8. General Mask Register Format**

|                          | ADDRESS       |    | REGISTER DATA |        |       |    |    |    |    | DOD CTATE          |

|--------------------------|---------------|----|---------------|--------|-------|----|----|----|----|--------------------|

| FUNCTION                 | CODE<br>(HEX) | D7 | D6            | D5     | D4    | D3 | D2 | D1 | D0 | POR STATE<br>(HEX) |

| General Mask<br>Register | 0x06          | 0  | MTWARN        | MTSHDN | MDUMP | X  | Х  | X  | х  | 0x00               |

MTWARN: Set MTWARN to '1' to enable the TWARN fault detection. See Table 4. MTSHDN: Set MTSHDN to '1' to enable the TSHDN fault detection. See Table 4. MDUMP: Set MDUMP to '1' to enable the DUMP fault detection. See Table 4.

#### **Left-Channel Mask Register**

## Table 9. Left-Channel Mask Register

|                               | ADDRESS       | REGISTER DATA |                         |         |   |          |        |   | POR |                |

|-------------------------------|---------------|---------------|-------------------------|---------|---|----------|--------|---|-----|----------------|

| FUNCTION                      | CODE<br>(HEX) | D7            | D7 D6 D5 D4 D3 D2 D1 D0 |         |   |          |        |   | D0  | STATE<br>(HEX) |

| Left-Channel<br>Mask Register | 0x07          | MSVDDL        | MSGNDL                  | MLIMITL | 0 | MOFFSETL | MOPENL | Х | Х   | 0x00           |

MSVDDL: Set MSVDDL to 1 to enable the short to VDD detection on the left channel.

MSGNDL: Set MSGNDL to 1 to enable the short to GND detection on the left channel.

MLIMITL: Set MLIMITL to 1 to enable overcurrent detection on the left channel.

MOFFSETL: Set MOFFSETL to 1 to enable excessive-offset detection on the left-channel output.

MOPENL: Set MOPENL to 1 to enable open-load detection on the left channel.

# Dual Automotive, Audio Line Drivers with I<sup>2</sup>C Control and Diagnostic

### Right-Channel Mask Register

Table 10. Right-Channel Mask Register

|                                | ADDRESS       |        | REGISTER DATA |         |    |          |        |    | POR |                |

|--------------------------------|---------------|--------|---------------|---------|----|----------|--------|----|-----|----------------|

| FUNCTION                       | CODE<br>(HEX) | D7     | D6            | D5      | D4 | D3       | D2     | D1 | D0  | STATE<br>(HEX) |

| Right-Channel<br>Mask Register | 0x08          | MSVDDR | MSGNDR        | MLIMITR | 0  | MOFFSETR | MOPENR | ×  | Х   | 0x00           |

MSVDDR: Set MSVDDR to 1 to enable the short to  $V_{\mbox{\scriptsize DD}}$  detection on the right channel.

MSGNDR: Set MSGNDR to 1 to enable the short to GND detection on the right channel.

MLIMITR: Set MLIMITR to 1 to enable overcurrent detection on the right channel.

MOFFSETR: Set MOFFSETR to 1 to enable excessive-offset detection on the right channel.

MOPENR: Set MOPENR to 1 to enable open-load detection on the right channel.

#### I<sup>2</sup>C and Stand-Alone Diagnostics

When the DIAG bit and the appropriate mask bits are set to 1, the MAX13325/MAX13326 enter diagnostic mode. In this mode, the MAX13325/MAX13326 detect short to GND, short to battery, overcurrent condition, overtemperature condition, excessive offset, and report the diagnosis using the I<sup>2</sup>C serial interface, FLAG bit, and the  $\overline{\text{FLAG}}$  output.

For stand-alone mode, there exists a 500ms stand-alone fault retry function (for autoretry) until the fault goes away. The FLAG output is pulsed to indicate a fault.

#### Output Short to VDD

When in diagnostic mode, the MAX13325/MAX13326 detect if any of the differential outputs is shorted to  $V_{DD}$  or battery. Upon detection of the short to  $V_{DD}$  or battery, the faulted channel is switched off and its output goes into a high-impedance state. The fault is reported using the I2C interface and the  $\overline{FLAG}$  output. See Table 11.

Table 11. Output Short to VDD/Battery Diagnostic

| FAULT CONDITION                                 | STATUS REPORT                                                       | UNMASK                                      | RECOVERY                                                                                    |

|-------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------|

|                                                 | FLAG is asserted low.                                               | 1 111101                                    | Cleared on reading the LFAULT                                                               |

|                                                 | FLAG bit set. See Table 7.                                          | In LMASK register, set MSVDDL bit to 1.     | register. See Table 5.                                                                      |

| Left-Channel Output<br>Short to V <sub>DD</sub> | SVDDL bit is set in the LFAULT register. See Table 5.               | See Table 9.                                | Note: 500ms autoretry in stand-<br>alone mode.                                              |

|                                                 | Left channel switches off and output goes to high-impedance state.  | Cannot be masked.                           | Output is enabled by setting the RETRYL bit to 1 in the Common Byte register. See Table 3.  |

|                                                 | FLAG is asserted low.                                               | L DMAOK 's land                             | Cleared on reading the RFAULT                                                               |

|                                                 | FLAG bit set. See Table 7.                                          | In RMASK register, set MSVDDR bit to 1. See | register. See Table 6.                                                                      |

| Right-Channel Output Short to VDD               | SVDDR bit is set in the RFAULT register. See Table 6.               | Table 10.                                   | Note: 500ms autoretry in stand-<br>alone mode.                                              |

| Output Short to VDD                             | Right channel switches off and output goes to high-impedance state. | Cannot be masked.                           | Output is enabled by setting the RETRYR bit to 1 in the Command Byte register. See Table 3. |

# **Dual Automotive, Audio Line Drivers** with I<sup>2</sup>C Control and Diagnostic

#### **Output Short to GND**

When in diagnostic mode, the MAX13325/MAX13326 detect if any of the differential outputs is shorted to ground. Upon detection of the short to ground, the faulted channel is switched off and its output goes into a high-impedance state. The fault is reported using the  $^{\rm I2C}$  interface and the  $\overline{\rm FLAG}$  output. See Table 12.

#### Overtemperature

When in diagnostic mode, if the MAX13325/MAX13326 exceed the overtemperature warning or temperature shutdown thresholds the device reports the condition using the I2C interface and the  $\overline{FLAG}$  output. See Table 13.

### **Table 12. Output Short to GND Diagnostic**

| FAULT CONDITION                      | STATUS REPORT                                                       | UNMASK                                         | RECOVERY                                                                                    |

|--------------------------------------|---------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------|

|                                      | FLAG is asserted low. FLAG bit set. See Table 7.                    | In LMASK register, set                         | Cleared on reading the LFAULT register. See Table 5.                                        |

| Left-Channel Output<br>Short to GND  | SGNDL bit is set in the LFAULT register. See Table 5.               | MSGNDL bit to 1. See<br>Table 9.               | Note: 500ms autoretry in stand-<br>alone mode.                                              |

| Charta divis                         | Left channel switches off and output goes to high-impedance state.  | Cannot be masked.                              | Output is enabled by setting the RETRYL bit to 1 in the Command Byte register. See Table 3. |

|                                      | FLAG is asserted low.                                               | L DMAOL ' L                                    | Cleared on reading the RFAULT                                                               |

|                                      | FLAG bit set. See Table 7.                                          | In RMASK register, set<br>MSGNDR bit to 1. See | register. See Table 6.                                                                      |

| Right-Channel Output<br>Short to GND | SGNDR bit is set in the RFAULT register. See Table 6.               | Table 10.                                      | Note: 500ms autoretry in stand-<br>alone mode.                                              |

| Short to GND                         | Right channel switches off and output goes to high-impedance state. | Cannot be masked.                              | Output is enabled by setting the RETRYR bit to 1 in the Command Byte register. See Table 3. |

### **Table 13. Overtemperature Diagnostic**

| FAULT CONDITION             | STATUS REPORT                                                               | UNMASK                                         | RECOVERY                                                                                                                                                                                |  |

|-----------------------------|-----------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Overtemperature             | FLAG is asserted low. FLAG bit set. See Table 7.                            | In GMASK register, set<br>MTWARN bit to 1. See | Die temperature falls below warning threshold.                                                                                                                                          |  |

| Warning                     | TWARN bit is set in the GFAULT register. See Table 4.                       | Table 8.                                       | Cleared on reading the GFAULT register.                                                                                                                                                 |  |

|                             | FLAG is asserted low.                                                       |                                                | Die temperature falls below                                                                                                                                                             |  |

|                             | FLAG bit set. See Table 7.                                                  | In GMASK register, set                         | shutdown threshold.  Cleared on reading the GFAULT                                                                                                                                      |  |

| Overtemperature             | TSHDN bit is set in the GFAULT<br>Register. See Table 4.                    | MTSHDN bit to 1. See<br>Table 8.               | register.  Note: 500ms autoretry in stand- alone mode.                                                                                                                                  |  |

| Overtemperature<br>Shutdown | Left and right channels switch off and output goes to high-impedance state. | Cannot be masked.                              | Left channel is enabled by setting the RETRYL bit to 1 in the Command Byte register. Right channel is enabled by setting the RETRYR bit to 1 in the Command Byte register. See Table 3. |  |

# **Dual Automotive, Audio Line Drivers** with I<sup>2</sup>C Control and Diagnostic

#### Excessive Offset

When in diagnostic mode with mute enabled, if there is excessive offset on any output, the MAX13325/MAX13326 reports the condition through the I<sup>2</sup>C interface and the FLAG output. See Table 14.

#### Overcurrent

When in diagnostic mode, if any of the output pairs is excessively loaded, the MAX13325/MAX13326 issue a warning and report the condition through the I<sup>2</sup>C interface and the FLAG output. The faulted channel is not switched off. See Table 15.

#### Open Load

When in diagnostic mode and the open-load detection is initiated, the selected channel is switched off for 1ms during which the diagnosis is taking place. Upon detecting an open load on any channel, the MAX13325/MAX13326 report the condition using the  $I^2C$  interface and the  $\overline{FLAG}$  output. See Table 16.

#### Overvoltage

When in diagnostic mode, if the MAX13325/MAX13326 exceed the VDD overvoltage threshold (for example during a load-dump condition), the device reports the condition using the I<sup>2</sup>C interface and the FLAG output. See Table 17.

### **Table 14. Excessive Offset Diagnostic**

| FAULT CONDITION                  | STATUS REPORT                                           | UNMASK                                            | RECOVERY                      |

|----------------------------------|---------------------------------------------------------|---------------------------------------------------|-------------------------------|

|                                  | FLAG is asserted low.                                   | L II LAMACIK                                      |                               |

| Excessive Output Offset on Left  | FLAG bit set. See Table 7.                              | In the LMASK register, set MOFFSETL bit to 1. See | Cleared on reading the LFAULT |

| Channel                          | OFFSETL bit is set in the LFAULT register. See Table 5. | Table 9.                                          | register.                     |

| Formation Output                 | FLAG is asserted low.                                   | In the DNAACK was into a set                      |                               |

| Excessive Output Offset on Right | FLAG bit set.                                           | In the RMASK register, set MOFFSETR bit to 1. See | Cleared on reading the RFAULT |

| Channel                          | OFFSETR bit is set in the RFAULT register. See Table 6. | Table 10.                                         | register.                     |

### **Table 15. Overcurrent Diagnostic**

| FAULT CONDITION                 | STATUS REPORT                                          | UNMASK                                 | RECOVERY                                              |  |

|---------------------------------|--------------------------------------------------------|----------------------------------------|-------------------------------------------------------|--|

| Overcurrent on Left<br>Channel  | FLAG is asserted low. FLAG bit set. See Table 7.       | In the LMASK register,                 | Load current falls below the current-limit threshold. |  |

|                                 | LIMITL bit is set in the LFAULT register. See Table 5. | set MLIMITL bit to 1. See<br>Table 9.  | Cleared on reading the LFAULT register.               |  |

| Overcurrent on Right<br>Channel | FLAG is asserted low. FLAG bit set. See Table 7.       | In the RMASK register,                 | Load current falls below the current-limit threshold. |  |

|                                 | LIMITR bit is set in the RFAULT register. See Table 6. | set MLIMITR bit to 1. See<br>Table 10. | Cleared on reading the RFAULT register.               |  |

### **Table 16. Open-Load Diagnostic**

| FAULT CONDITION STATUS REPORT |                                                       | UNMASK                                          | RECOVERY             |  |  |

|-------------------------------|-------------------------------------------------------|-------------------------------------------------|----------------------|--|--|

| Left-Channel Open<br>Load     | FLAG is asserted low.                                 | 1 11 1111017                                    |                      |  |  |

|                               | FLAG bit set. See Table 7.                            | In the LMASK register, set MOPENL bit to 1. See | Cleared on reading   |  |  |

|                               | OPENL bit is set in the LFAULT register. See Table 5. | Table 9.                                        | the LFAULT register. |  |  |

| Right-Channel Open<br>Load    | FLAG is asserted low.                                 | L II DMAOK 'I                                   |                      |  |  |

|                               | FLAG bit set. See Table 7.                            | In the RMASK register, set MOPENR bit to 1. See | Cleared on reading   |  |  |

|                               | OPENR bit is set in the RFAULT register. See Table 6. | Table 10.                                       | the RFAULT register. |  |  |

# **Dual Automotive, Audio Line Drivers** with I<sup>2</sup>C Control and Diagnostic

**Table 17. Overvoltage Diagnostic**

| FAULT CONDITION         | STATUS REPORT                                                                 | UNMASK                       | RECOVERY                                                                                                                                      |  |

|-------------------------|-------------------------------------------------------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Overvoltage<br>Shutdown | FLAG is asserted low. FLAG bit set. See Table 7.                              | In GMASK register, set       | V <sub>DD</sub> voltage falls below overvoltage threshold. Cleared on reading the GFAULT register. Note: 500ms autoretry in stand-alone mode. |  |

|                         | DUMP bit is set in the GFAULT register. See Table 4.                          | MDUMP bit to 1. See Table 8. |                                                                                                                                               |  |

|                         | Left and right channels switch off and output goes to a high-impedance state. | Cannot be masked.            | Left channel is enabled by setting the RETRYL bit to 1. Right channel is enabled by setting the RETRYR bit to 1. See Table 3.                 |  |

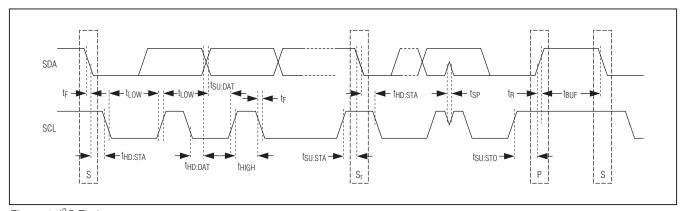

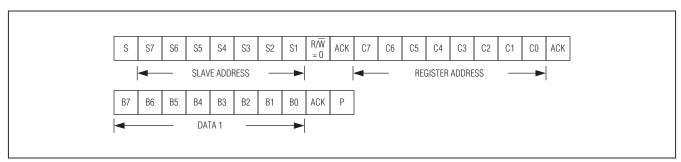

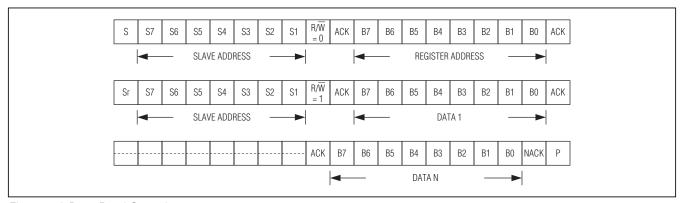

# Applications Information Serial Interface

Writing to the MAX13325/MAX13326 using I<sup>2</sup>C requires that first the master sends a START (S) condition followed by the device's I<sup>2</sup>C address. After the address, the master sends the register address of the register that is to be programmed. The master then ends communication by issuing a STOP (P) condition to relinquish

control of the bus, or a Repeated START (Sr) condition to communicate to another I<sup>2</sup>C slave (see Figure 1).

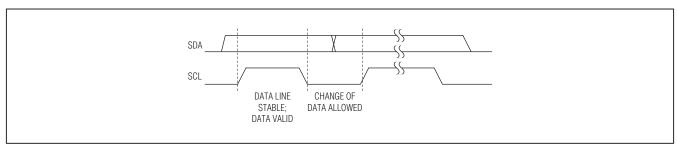

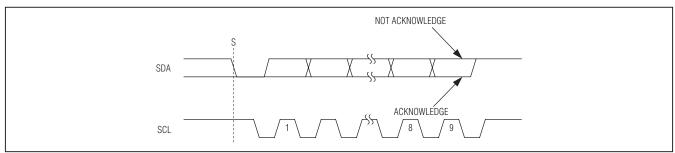

#### Bit Transfer

Each SCL rising edge transfers one data bit. The data on SDA must remain stable during the high portion of the SCL clock pulse (see Figure 2). Changes in SDA while SCL is high are read as control signals (see the *START and STOP Conditions* section). When the serial interface is inactive, SDA and SCL idle high.

Figure 1. I<sup>2</sup>C Timing

Figure 2. Bit Transfer

# **Dual Automotive, Audio Line Drivers** with I<sup>2</sup>C Control and Diagnostic

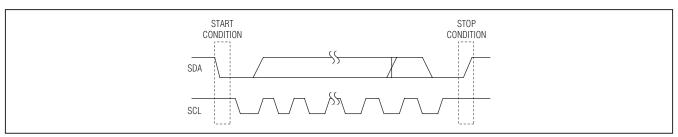

#### START and STOP Conditions

A master device initiates communication by issuing a START condition, which is a high-to-low transition on SDA with SCL high. A START condition from the master signals the beginning of a transmission to the MAX13325/MAX13326. The master terminates transmission by a STOP condition (see the *Acknowledge Bit* section). A STOP condition is a low-to-high transition on SDA while SCL is high (Figure 3). The STOP condition frees the bus. If a Repeated START condition is generated instead of a STOP condition, the bus remains active. When a STOP condition or incorrect slave ID is detected, the device internally disconnects SCL from the

serial interface until the next START or Repeated START condition, minimizing digital noise and feedthrough.

#### Acknowledge Bit

The acknowledge (ACK) bit is a clocked 9th bit that the MAX13325/MAX13326 use to handshake receipt of each byte of data when in write mode. The MAX13325/MAX13326 pull down SDA during the entire mastergenerated 9th clock pulse if the previous byte is successfully received (see Figure 4). Monitoring ACK allows for detection of unsuccessful data transfers. An unsuccessful data transfer occurs if a receiving device is busy or if a system fault has occurred. In the event

Figure 3. START/STOP Conditions

Figure 4. Acknowledge and Not-Acknowledge Bits

#### **Table 18. Slave Address**

|      | . O. O.a. |            |            |            |    |    |    |    |     |                                   |                                    |                  |

|------|-----------|------------|------------|------------|----|----|----|----|-----|-----------------------------------|------------------------------------|------------------|

| ADD1 | ADD0      | <b>A</b> 6 | <b>A</b> 5 | <b>A</b> 4 | А3 | A2 | A1 | A0 | R/W | SLAVE<br>ADDRESS<br>READ<br>(HEX) | SLAVE<br>ADDRESS<br>WRITE<br>(HEX) | MODE             |

| GND  | GND       | _          | _          | _          | _  | _  | _  | _  | _   | _                                 | _                                  | Stand-<br>alone  |

| VL   | GND       | 1          | 1          | 0          | 0  | 0  | 0  | 1  | 1/0 | 0xC3                              | 0xC2                               | I <sup>2</sup> C |

| GND  | VL        | 1          | 1          | 0          | 0  | 0  | 1  | 0  | 1/0 | 0xC5                              | 0xC4                               | I <sup>2</sup> C |

| VL   | VL        | 1          | 1          | 0          | 0  | 0  | 1  | 1  | 1/0 | 0xC7                              | 0xC6                               | I2C              |

| SCL  | VL        | 1          | 1          | 0          | 0  | 1  | 0  | 0  | 1/0 | 0xC9                              | 0xC8                               | I <sup>2</sup> C |

| SDA  | VL        | 1          | 1          | 0          | 0  | 1  | 0  | 1  | 1/0 | 0xCB                              | 0xCA                               | I <sup>2</sup> C |

| VL   | SCL       | 1          | 1          | 0          | 0  | 1  | 1  | 0  | 1/0 | 0xCD                              | 0xCC                               | I <sup>2</sup> C |

| VL   | SDA       | 1          | 1          | 0          | 0  | 1  | 1  | 1  | 1/0 | 0xCF                              | 0xCE                               | I2C              |

# **Dual Automotive, Audio Line Drivers** with I<sup>2</sup>C Control and Diagnostic

of an unsuccessful data transfer, the bus master may retry communication. The master must pull down SDA during the 9th clock cycle to acknowledge receipt of data when the MAX13325/MAX13326 are in read mode. An acknowledge must be sent by the master after each read byte to allow data transfer to continue. A not-acknowledge is sent when the master reads the final byte of data from the MAX13325/MAX13326, followed by a STOP condition.

#### Slave Address

The MAX13325/MAX13326 are programmable to one of seven I<sup>2</sup>C slave addresses. These slave addresses are unique device IDs. Connect ADD\_ to GND, VL, SCL, or SDA to set the I<sup>2</sup>C slave address. The address is defined as the seven most significant bits (MSBs) followed by the read/write bit. Set the read/write bit to 1 to configure the MAX13325/MAX13326 to read mode. Set the read/write bit to 0 to configure the device to write mode. The address is the first byte of information sent after the START condition.

### **Register Address Map** Single-Byte Write Operation

For a single-byte write operation, send the slave address as the first byte followed by the register address and then a single data byte (see Figure 5).

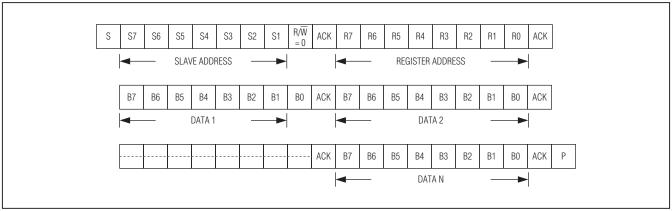

### Burst Write Operation

For a burst write operation, send the slave address as the first byte followed by the register address and then the data bytes (see Figure 6).

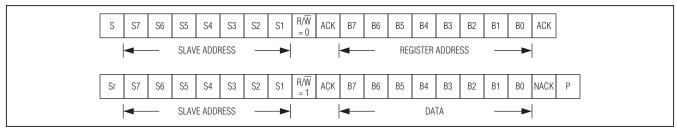

#### Single-Byte Read Operation

For a single-byte read operation, send the slave address with the read bit set, as the first byte followed by the register address. Then send a Repeated START condition followed by the slave address. After the slave sends the data byte, send a not-acknowledge followed by a STOP condition (see Figure 7).

#### **Burst Read Operation**

For a burst read operation, send the slave address with a write as the first byte followed by the register address. Then send a Repeated START condition followed by the slave address. The slave sends data bytes until a not-acknowledge condition is sent (see Figure 8).

Figure 5. A Single-Byte Write Operation

Figure 6. A Burst Write Operation

# Dual Automotive, Audio Line Drivers with I<sup>2</sup>C Control and Diagnostic

Figure 7. A Single-Byte Read Operation

Figure 8. A Burst Read Operation

#### Charge Pump

The MAX13325/MAX13326 charge pump can be disabled depending on application requirements. When charge pump is enabled [CPOFF = 0], please follow the charge-pump capacitor selections. When the charge pump is disabled [CPOFF = 1], the flying capacitor (C1) is not needed. There are internal diodes between VDD/OUT\_ to CHOLD, so it is important that CHOLD not be forced below VDD or any of the outputs. A series diode needs to be placed between the external supply (VSUP) and CHOLD. See D2 in the *Typical Operating Circuit*.

#### Charge-Pump Capacitor Selection

Use ceramic capacitors with a low ESR for optimum performance. For optimal performance over the extended temperature range, select capacitors with an X7R dielectric. Table 19 lists suggested manufacturers.

#### Flying Capacitor (C1)

The value of the flying capacitor (see the *Typical Operating Circuit*) affects the charge pump's load regulation and output resistance. A C1 value that is too small degrades the device's ability to provide sufficient current drive, which leads to a loss of output voltage. Increasing the value of C1 improves load regulation and reduces the charge-pump output resistance. For optimum performance, use a 470nF capacitor for C1. When the charge pump is disabled [CPOFF = 1], the flying capacitor (C1) is not needed.

### Hold Capacitor (C2)

The hold capacitor value (see the *Typical Operating Circuit*) and ESR directly affect the ripple at the internal negative rail. Increasing the value of C2 reduces output ripple. Likewise, decreasing the ESR of C2 reduces both ripple and output resistance. Lower capacitance values can be used in systems with low maximum output power levels. For optimum performance, use a 1µF capacitor for C2.

### **Table 19. Suggested Capacitor Vendors**

| SUPPLIER                               | PHONE        | FAX          | WEBSITE                     |

|----------------------------------------|--------------|--------------|-----------------------------|

| Murata Electronics North America, Inc. | 770-436-1300 | 770-436-3030 | www.murata-northamerica.com |

| Taiyo Yuden                            | 800-348-2496 | 847-925-0899 | www.t-yuden.com             |

| TDK Corp.                              | 847-803-6100 | 847-390-4405 | www.component.tdk.com       |

# **Dual Automotive, Audio Line Drivers** with I<sup>2</sup>C Control and Diagnostic

#### Power-Supply Bypass Capacitor (C3)

The power-supply bypass capacitor (see the *Typical Operating Circuit*) lowers the output impedance of the power supply, and reduces the impact of the MAX13325/MAX13326 charge-pump switching transients. Bypass VDD with C3, the same value as C2, and place it physically close to the VDD and PGND pins.

#### **Load-Dump Protection**

With minimal external components, the MAX13325/MAX13326 can be protected against automotive load-dump conditions. See the *Typical Operating Circuit*.

#### nMOSFET (Q1)

Q1 should be selected to withstand the full-voltage exposure (BVDSS > 45V). The gate-source turn-on voltage should be chosen to be less than VCPS to ensure initial startup. Using an external nMOS, RTR020N05, 300ms duration component provides 50V load-dump protection.

### **Chip Information**

PROCESS: BCD

#### Zener Diode (D1)

During short-to-battery condition, OUT\_ lifts up CHOLD using an internal diode. In order not to violate the maximum gate-source voltage of Q1, a zener diode of appropriate clamping voltage should be added between the gate and source terminals.

#### Series Resistor (R1)

Normally, a series resistor for current limitation is needed during short-to-battery condition. R1 should be chosen according to (18V - V<sub>DD(min)</sub> - V<sub>ZENER</sub>)/1mA so that no excessive current is being drawn from CHOLD.

#### **Layout and Grounding**

Proper layout and grounding are essential for optimum performance. Connect the EP and GND together at a single point on the PCB. Ensure ground return resistance is minimized for optimum crosstalk performance.

### \_Package Information

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE     | PACKAGE | OUTLINE | LAND PATTERN |

|-------------|---------|---------|--------------|

| TYPE        | CODE    | NO.     | NO.          |

| 28 TSSOP-EP | U28E+5  | 21-0108 | 90-0147      |

# **Dual Automotive, Audio Line Drivers** with I<sup>2</sup>C Control and Diagnostic

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                 | PAGES<br>CHANGED      |

|--------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 0                  | 1/10             | Initial release                                                                                                                             | _                     |

| 1                  | 3/10             | Updated the Typical Operating Circuit                                                                                                       | 1                     |

| 2                  | 4/10             | Added new register bits to Tables 1, 2, and 7. Revised FLAG Register section and added Table 2a and Charge Pump section.                    | 1, 4, 7, 8–12, 19, 20 |

| 3                  | 6/10             | Introduced the MAX13326. Updated the <i>Electrical Characteristics</i> table and added new <i>Typical Operating Characteristics</i> graphs. | 1, 4, 5, 7            |

| 4                  | 9/12             | Corrected slave addresses in Table 18                                                                                                       | 17                    |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.