10 Channel LED Backlight Driver with Integrated Power Supply

The 34844/A is a high efficiency, LED driver for use in backlighting LCD displays from 10" to 20"+. Operating from supplies of 7.0 to 28 V, the MC34844/A is capable of driving up to 160 LEDs in 10 parallel strings. Current in the 10 strings is matched to within  $\pm 2\%$ , and can be programmed via the I<sup>2</sup>C/SM Bus interface.

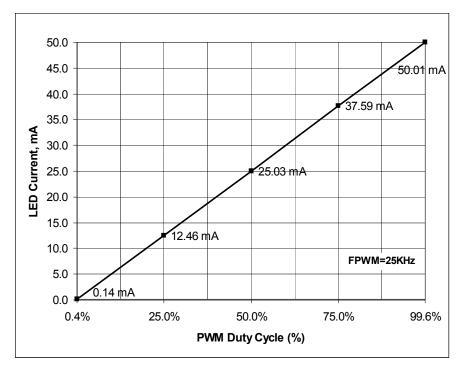

The 34844/A also includes a Pulse Width Monitor (PWM) generator for LED dimming. The LEDs can be dimmed to one of 256 levels, programmed through the  $I^2C/SM$  Bus interface. Up to 65,000:1 (256:1 PWM, 256:1 Current DAC) dimming ratio.

The integrated boost converter generates the minimum output voltage required to keep all LEDs illuminated with the selected current, providing the highest efficiency possible.

The 34844 has an integrated boost self-clocks at a default frequency of 600 kHz, but may be programmed via  $I^2C$  to 150/300/ 600/1200 kHz. The PWM frequency can be set from 100 Hz to 25 kHz, or can be synchronized to an external input. If not synchronized to another source, the internal PWM rate outputs on the CK pin. This enables multiple devices to be synchronized together.

The 34844A has a default boost frequency of 320 kHz, but may be programmed via  $I^2$ C to 160/320/650/1300 kHz. The PWM frequency can be set from 110 Hz to 27 kHz, or can be synchronized to an external input. If not synchronized to another source, the internal PWM rate outputs on the CK pin. This enables multiple devices to be synchronized together.

The 34844/A also supports optical/temperature closed loop operation and also features LED over-temperature protection, LED short protection, and LED open circuit protection. The IC also includes over-voltage protection, over-current protection, and under-voltage lockout.

#### Features

- Input voltage of 7.0 to 28 V

- · 2.5 A integrated boost FET

- Up to 50 mA on the 34844 LED current per channel

- Up to 80 mA on the 34844A LED current per channel

- 90% efficiency (DC:DC)

- I<sup>2</sup>C/SM Bus interface

- 10 channel current mirror with ±2% current matching

- Boost output voltage up to 60V, with Dynamic Headroom Control (DHC)

- PWM frequency programmable or synchronizable from 100 to 25,000 Hz for the 34844

- PWM frequency programmable or synchronizable from 110 to 27,000 Hz for the 34844A

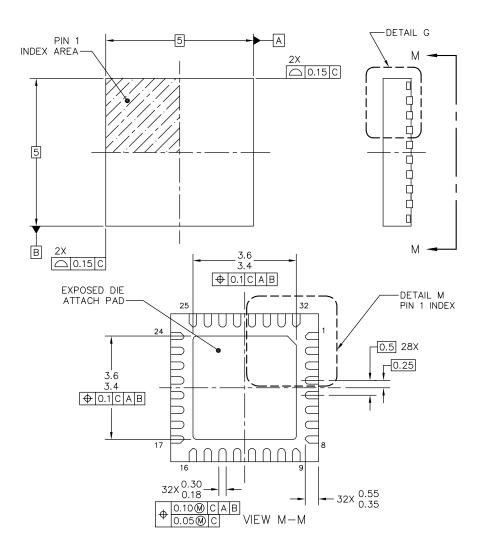

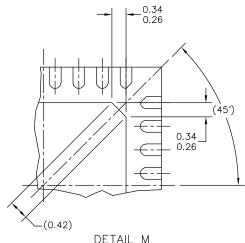

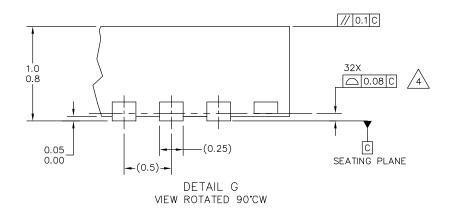

- 32-Ld 5x5x1.0mm TQFN Package

## Applications

- · Monitors and HDTV up to 42 inch

- · Personal Computer Notebooks

- GPS Screens

- Small screen Televisions

\* This document contains certain information on a new product. Specifications and information herein are subject to change without notice. © Freescale Semiconductor, Inc., 2009-2012. All rights reserved.

## Document Number: MC34844 Rev. 9.0, 3/2012

√RoHS

34844 34844A

## LED DRIVER

EP SUFFIX (PB-FREE) 98ASA10800D 32-PIN QFN-EP

#### **ORDERING INFORMATION**

| Device        | Temperature<br>Range (T <sub>A</sub> ) | Package   |

|---------------|----------------------------------------|-----------|

| MC34844EP/R2  | -40 °C to 105 °C                       | 32 QFN-EP |

| MC34844AEP/R2 | -40 0 10 105 0                         |           |

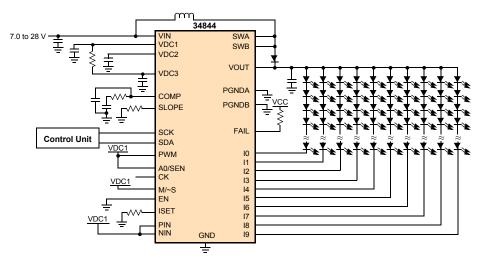

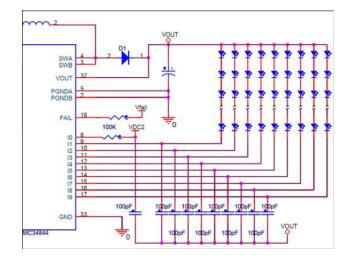

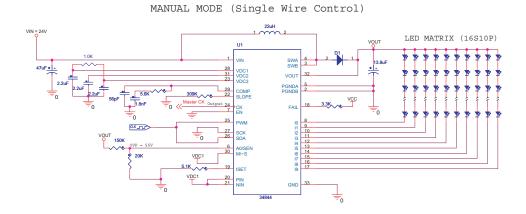

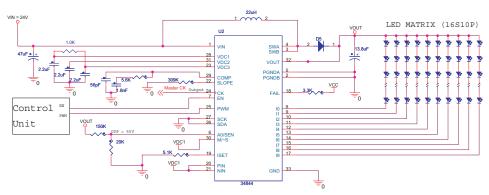

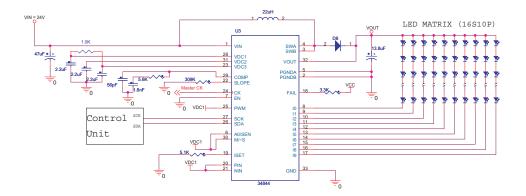

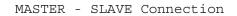

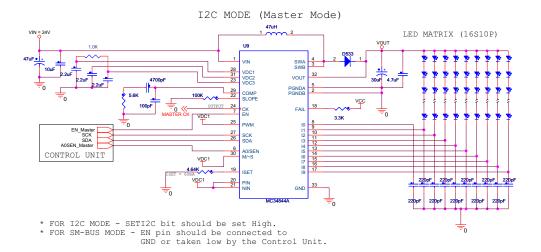

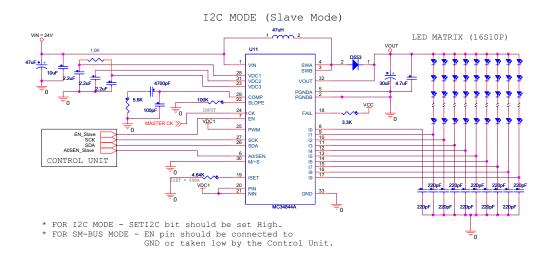

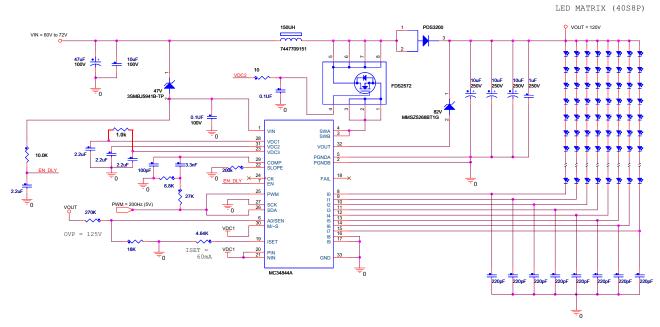

Figure 1. MC34844 Simplified Application Diagram (SM Bus Mode)

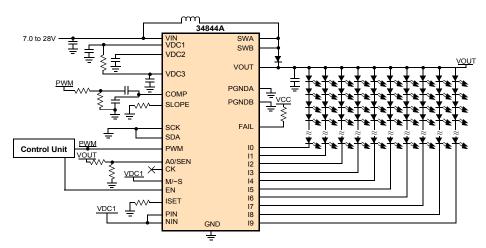

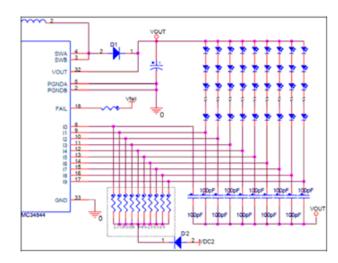

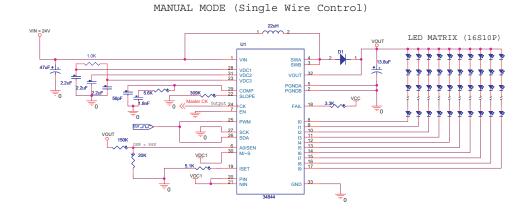

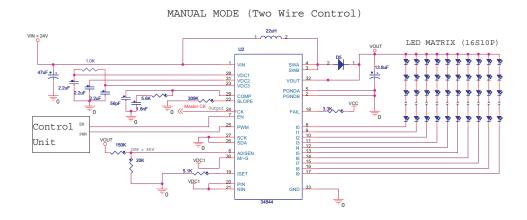

Figure 2. MC34844A Simplified Application Diagram (Manual Mode)

# **DEVICE VARIATIONS**

MC34844 is within the MC34844 Specifications Pages 4 to 31, MC34844A is within the MC34844A Specifications Pages 32 to 54

Table 1. Key Device Variations between the MC34844 and MC34844A

| Electrical Parameter <sup>(1)</sup> | Condition                               | Value       | Unit |

|-------------------------------------|-----------------------------------------|-------------|------|

| Maximum LED Current                 |                                         |             | mA   |

| 34844                               |                                         | 55          |      |

| 34844A                              |                                         | 85          |      |

| LED Channel Sink Current            |                                         | (typ)       | mA   |

| 34844                               | RISET=5.1 kΩ ±0.1%                      | 50          |      |

| 34844A                              | RISET=3.48 kΩ ±0.1%                     | 80          |      |

| Switching Frequency                 |                                         | (typ)       | MHz  |

| 34844                               | (BST [1:0]=0)                           | 0.15        |      |

|                                     | (BST [1:0]=1)                           | 0.30        |      |

|                                     | (BST [1:0]=2) [default]                 | 0.60        |      |

|                                     | (BST [1:0]=3)                           | 1.20        |      |

| 34844A                              | (BST [1:0]=0)                           | 0.16        |      |

|                                     | (BST [1:0] =1)) [default]               | 0.10        |      |

|                                     | (BST [1:0]=2)                           | 0.65        |      |

|                                     | (BST [1:0]=3)                           | 1.30        |      |

| PWM Frequency Range                 | This frequency range applies for Master |             | Hz   |

| 34844                               | mode, Slave mode, and Manual mode       | 100 - 25000 |      |

| 34844A                              |                                         | 110 - 27000 |      |

Notes

1. Refer to the respective Electrical Parameters for specific details

# MC34844 SPECIFICATIONS PAGES 4 TO 31

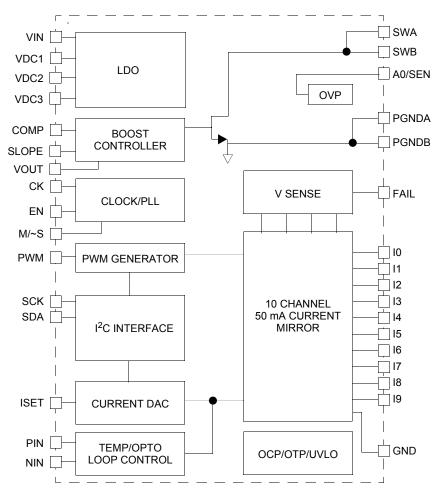

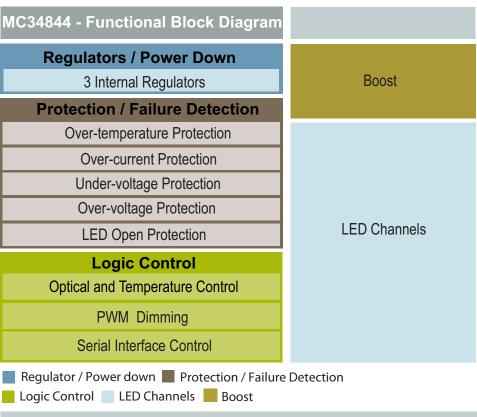

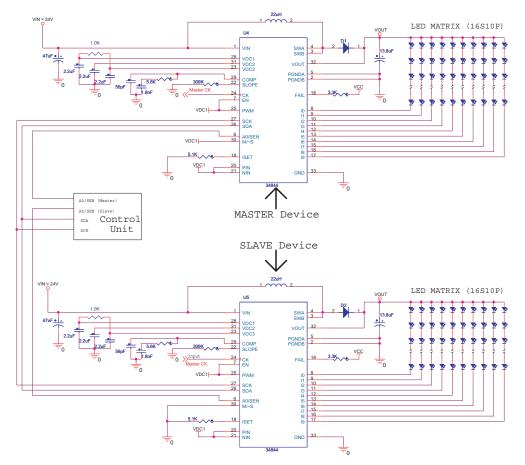

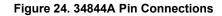

INTERNAL BLOCK DIAGRAM

Figure 3. 34844 Simplified Internal Block Diagram

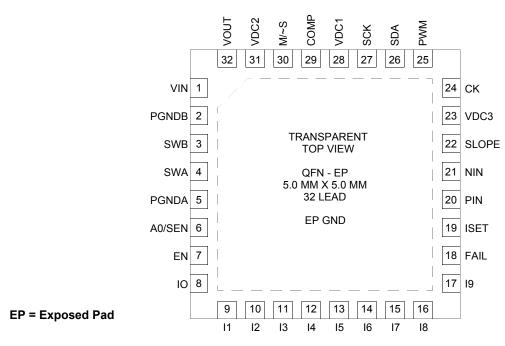

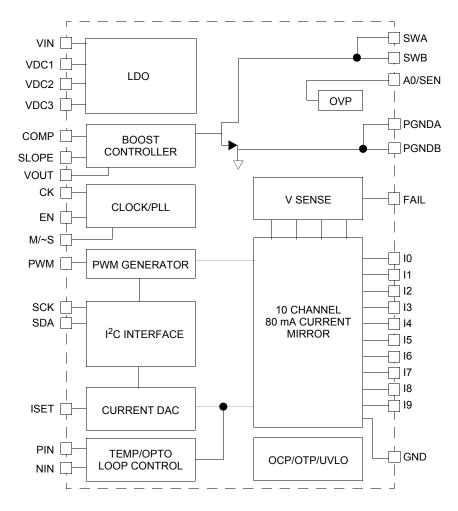

Figure 4. 34844 Pin Connections

#### Table 2. 34844 Pin Definitions

A functional description of each pin can be found in the Functional Pin Description section beginning on page 14.

| Pin Number | Pin Name | Pin Function | Formal Name            | Definition                                                                                  |

|------------|----------|--------------|------------------------|---------------------------------------------------------------------------------------------|

| 1          | VIN      | Power        | Input voltage          | Input supply                                                                                |

| 2          | PGNDB    | Power        | Power Ground           | Power ground                                                                                |

| 3          | SWB      | Input        | Switch node B          | Boost switch connection B                                                                   |

| 4          | SWA      | Input        | Switch node A          | Boost switch connection A                                                                   |

| 5          | PGNDA    | Power        | Power Ground           | Power ground                                                                                |

| 6          | A0/SEN   | Input        | Device Select          | Address select, device select pin or OVP HW control                                         |

| 7          | EN       | Input        | Enable                 | Enable pin (active high, internal pull-up)                                                  |

| 8 - 17     | 10-19    | Input        | LED Channel            | LED string connections                                                                      |

| 18         | FAIL     | Open Drain   | Fault detection        | Fault detected pin (open drain):<br>No Failure = Low-impedance<br>Failure = High-impedance  |

| 19         | ISET     | Passive      | Current set            | LED current setting resistor                                                                |

| 20         | PIN      | Input        | Positive current scale | Positive input analog current control                                                       |

| 21         | NIN      | Input        | Negative current scale | Negative input analog current control                                                       |

| 22         | SLOPE    | Passive      | Boost Slope            | Boost slope compensation Setting resistor                                                   |

| 23         | VDC3     | Output       | Internal Regulator 3   | Decoupling capacitor for internal phase locked loop power                                   |

| 24         | СК       | Input/Output | Clock signal           | Clock synchronization pin (input for M/~S = low - internal pull-up, output for M/~S = high) |

## Table 2. 34844 Pin Definitions (continued)

A functional description of each pin can be found in the Functional Pin Description section beginning on page 14.

| Pin Number | Pin Name | Pin Function  | Formal Name            | Definition                                                      |

|------------|----------|---------------|------------------------|-----------------------------------------------------------------|

| 25         | PWM      | Input         | External PWM           | External PWM input (internal pull-down)                         |

| 26         | SDA      | Bidirectional | I <sup>2</sup> C data  | I <sup>2</sup> C data Line                                      |

| 27         | SCK      | Bidirectional | I <sup>2</sup> C clock | I <sup>2</sup> C clock line                                     |

| 28         | VDC1     | Output        | Internal Regulator 1   | Decoupling capacitor for internal logic rail                    |

| 29         | COMP     | Passive       | Compensation pin       | Boost converter Type compensation pin                           |

| 30         | M/~S     | Input         | Master/Slave selector  | Selects Master mode (1) or Slave mode (0)                       |

| 31         | VDC2     | Output        | Internal Regulator 2   | Decoupling capacitor for internal regulator                     |

| 32         | VOUT     | Input         | Voltage Output         | Boost Output voltage sense pin                                  |

| EP         | GND      | -             | Ground                 | Ground Reference for all internal circuits other than Boost FET |

# **ELECTRICAL CHARACTERISTICS**

## **MAXIMUM RATINGS**

#### Table 3. Maximum Ratings

All voltages are with respect to ground, unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                      | Symbol                | Value         | Unit |

|--------------------------------------------------------------|-----------------------|---------------|------|

| ELECTRICAL RATINGS                                           |                       |               |      |

| Maximum Pin Voltages                                         | V <sub>MAX</sub>      |               | V    |

| A0/SEN                                                       |                       | 7.0           |      |

| 10, 11, 12, 13, 14, 15, 16, 17, 18, 19,EN <sup>(5)</sup>     |                       | 45            |      |

| VIN                                                          |                       | 30            |      |

| SWA, SWB, VOUT                                               |                       | 65            |      |

| FAIL, PIN, NIN, ISET, M/~S, CK, PWM                          |                       | 6.0           |      |

| Maximum LED Current                                          | I <sub>MAX</sub>      | 55            | mA   |

| ESD Voltage <sup>(2)</sup>                                   | V <sub>ESD</sub>      |               | V    |

| Human Body Model (HBM)                                       |                       | <u>+</u> 2000 |      |

| Machine Model (MM)                                           |                       | <u>+</u> 200  |      |

| THERMAL RATINGS                                              |                       |               | •    |

| Ambient Temperature Range                                    | T <sub>A</sub>        | -40 to 105    | °C   |

| Junction to Ambient Temperature <sup>(3)</sup>               | $T_{	extsf{	heta}JA}$ | 32            | °C/W |

| Junction to Case Temperature <sup>(3)</sup>                  | Τ <sub>θJC</sub>      | 3.5           | °C/W |

| Maximum junction temperature                                 | Тј                    | 150           | °C   |

| Storage temperature range                                    | T <sub>STO</sub>      | -40 to 150    | °C   |

| Peak Package Reflow Temperature During Reflow <sup>(4)</sup> | T <sub>PPRT</sub>     | 260           | °C   |

| Power Dissipation                                            |                       |               | W    |

| TA = 25 °C                                                   |                       | 3.9           |      |

| TA = 70 °C                                                   |                       | 2.5           |      |

| TA = 85 °C                                                   |                       | 2.0           |      |

| TA = 105 °C                                                  |                       | 1.4           |      |

Notes

2. ESD testing is performed in accordance with the Human Body Model (HBM) (AEC-Q100-2), and the Machine Model (MM) (AEC-Q100-003),  $R_{ZAP}$  = 0  $\Omega$

3. Per JEDEC51 Standard for Multilayer PCB

4. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

5. 45 V is the Maximum allowable voltage on all LED channels in off-state.

## STATIC AND DYNAMIC ELECTRICAL CHARACTERISTICS

#### Table 4. Static and Dynamic Electrical Characteristics

Characteristics noted under conditions V<sub>IN</sub> = 12 V, V<sub>OUT</sub> = 42 V, I<sub>LED</sub> = 50 mA, PWM = VDC1, M/~S = VDC1, PIN & NIN = VDC1, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  105 °C, PGND = 0 V, unless otherwise noted.

| Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Symbol                | Min | Тур  | Мах | Unit |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|------|-----|------|--|

| Supply Current when Shutdown Mode<br>Manual & SM Bus: EN = Low, SCK & SDA=Low<br>I^2C: EN = Low, SETI <sup>2</sup> C bit = 1, CLRI <sup>2</sup> C bit = 0IshuTDOWN-2.0- $\mu$ ASupply Current when Sleep Mode<br>SM-Bus: EN = low, SCK & SDA= Active, SETI2C bit = 0, EN bit = 0IsLEEP-3.0-mASupply Current when Operational Mode<br>Manual: EN= High, SETI <sup>2</sup> C bit = 1, CLRI <sup>2</sup> C bit = 0, EN bit = 0Ioperational-10.0-mASupply Current when Operational Mode<br>Manual: EN= High, SCK & SDA=Active, EN bit = 1, PWM=Low<br>I <sup>2</sup> C: EN = High, SETI <sup>2</sup> C bit = 1, CLRI <sup>2</sup> C bit = 0, EN bit = 1, PWM=Low<br>I <sup>2</sup> C: EN = High, SETI <sup>2</sup> C bit = 1, CLRI <sup>2</sup> C bit = 0, EN bit = 1, PWM=Low<br>I <sup>2</sup> C: EN = High, SETI <sup>2</sup> C bit = 1, CLRI <sup>2</sup> C bit = 0, EN bit = 1, PWM=Low<br>I <sup>2</sup> C: EN = High, SETI <sup>2</sup> C bit = 1, CLRI <sup>2</sup> C bit = 0, EN bit = 1, PWM=Low<br>I <sup>2</sup> C: EN = High, SETI <sup>2</sup> C bit = 1, CLRI <sup>2</sup> C bit = 0, EN bit = 1, PWM=Low<br>I <sup>2</sup> C: EN = High, SETI <sup>2</sup> C bit = 1, CLRI <sup>2</sup> C bit = 0, EN bit = 1, PWM=Low-10.0-mAUnder-voltage Lockout<br>V <sub>IN</sub> RisingUVLO5.46.06.4V |                       |     |      |     |      |  |

| Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | V <sub>IN</sub>       | 7.0 | 12   | 28  | V    |  |

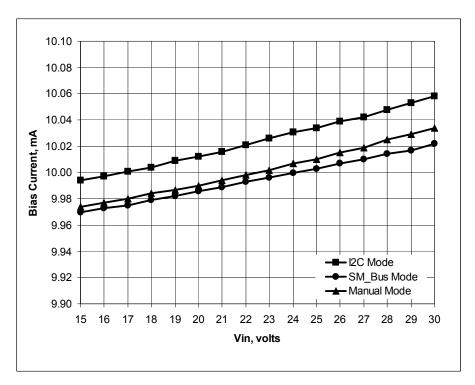

| Supply Current when Shutdown Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I <sub>SHUTDOWN</sub> |     |      |     |      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                       | -   |      | -   | μΑ   |  |

| $I^2C$ : EN = Low, SET $I^2C$ bit = 1, CLR $I^2C$ bit = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       | -   | 17   | -   |      |  |

| Supply Current when Sleep Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I <sub>SLEEP</sub>    | -   | 3.0  | -   | mA   |  |

| SM-Bus: EN = low, SCK & SDA= Active, SETI2C bit = 0, EN bit = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                       |     |      |     |      |  |

| $I^2C$ : EN = High, SETI <sup>2</sup> C bit = 1, CLRI <sup>2</sup> C bit = 0, EN bit = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                       |     |      |     |      |  |

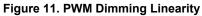

| Supply Current when Operational Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | IOPERATIONAL          | -   | 10.0 | -   | mA   |  |

| Manual: EN= High, SCK & SDA=Low, PWM=Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                       |     |      |     |      |  |

| SM-Bus: EN= Low, SCK & SDA=Active, EN bit= 1, PWM=Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                       |     |      |     |      |  |

| I <sup>2</sup> C: EN = High, SETI <sup>2</sup> C bit = 1, CLRI <sup>2</sup> C bit = 0, EN bit = 1, PWM=Low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                       |     |      |     |      |  |

| Under-voltage Lockout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | UVLO                  | 5.4 | 6.0  | 6.4 | V    |  |

| V <sub>IN</sub> Rising                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                       |     |      |     |      |  |

| Under-voltage Hysteresis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | UVLO <sub>HYST</sub>  | 150 | 200  | 250 | mV   |  |

| V <sub>IN</sub> Falling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                       |     |      |     |      |  |

| VDC1 Voltage <sup>(6)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V <sub>DC1</sub>      | 2.4 | 2.5  | 2.6 | V    |  |

| C <sub>VDC1</sub> = 2.2 μF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _                     |     |      |     |      |  |

| VDC2 Voltage <sup>(6)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V <sub>DC2</sub>      | 5.5 | 6.0  | 6.5 | V    |  |

| C <sub>VDC2</sub> = 2.2 μF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                       |     |      |     |      |  |

| VDC3 Voltage <sup>(6)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V <sub>DC3</sub>      | 2.4 | 2.5  | 2.6 | V    |  |

| C <sub>VDC3</sub> = 2.2 μF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                       |     |      |     |      |  |

| BOOST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                     |     | 1    | 1   |      |  |

| Output Voltage Range <sup>(7)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                       |     |      |     | V    |  |

| VIN = 7.0 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V <sub>OUT1</sub>     | 8.0 | -    | 43  |      |  |

| VIN = 28 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | V <sub>OUT2</sub>     | 31  | -    | 60  |      |  |

| Boost Switch Current Limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | I <sub>FET</sub>      | 2.3 | 2.5  | 2.7 | А    |  |

| DRACH (LL LEFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                     |     | 1    | 1   | 1    |  |

|                                        | IFET                    | 2.3 | 2.5 | 2.1 | A  |

|----------------------------------------|-------------------------|-----|-----|-----|----|

| RDSON of Internal FET                  | R <sub>DSON</sub>       | -   | 250 | 500 | mΩ |

| I <sub>DRAIN</sub> = 1.0 A             |                         |     |     |     |    |

| Boost Switch Off-state Leakage Current | I <sub>BOOST_LEAK</sub> | -   | -   | 10  | μΑ |

| V <sub>SWA,SWB</sub> = 65 V            |                         |     |     |     |    |

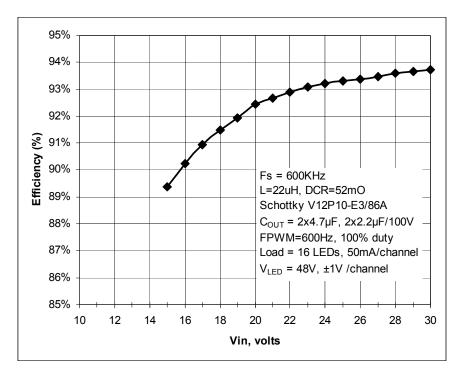

| Peak Boost Efficiency <sup>(8)</sup>   | EFF <sub>BOOST</sub>    | -   | 90  | -   | %  |

Notes

6. This output is for internal use only and not to be used for other purposes. A 1.0 k $\Omega$  resistor between the VDC3 and VDC1 pin is recommended for <-20 °C operation.

7. Minimum and Maximum output voltages are dependent on Min/Max duty cycle condition.

8. Guaranteed by design

### Table 4. Static and Dynamic Electrical Characteristics (continued)

Characteristics noted under conditions V<sub>IN</sub> = 12 V, V<sub>OUT</sub> = 42 V, I<sub>LED</sub> = 50 mA, PWM = VDC1, M/~S = VDC1, PIN & NIN = VDC1, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  105 °C, PGND = 0 V, unless otherwise noted.

| Characteristic                                                                                         | Symbol                             | Min   | Тур   | Max   | Unit |

|--------------------------------------------------------------------------------------------------------|------------------------------------|-------|-------|-------|------|

| Line Regulation <sup>(9)</sup><br>VIN=7.0 to 28 V                                                      | I <sub>OUT</sub> /V <sub>IN</sub>  | -0.2  | -     | 0.2   | %/V  |

| Load Regulation <sup>(9)</sup><br>VLED = 8.0 to 65 V (all Channels)                                    | I <sub>OUT</sub> /V <sub>LED</sub> | -0.2  | -     | 0.2   | %/V  |

| Slope compensation voltage ramp $R_{SLOPE}$ = 68 k $\Omega$                                            | V <sub>SLOPE</sub>                 | -     | 0.49  | -     | V/µs |

| Current Sense Amplifier Gain                                                                           | A <sub>CSA</sub>                   | -     | 9.0   | -     |      |

| Current Sense Resistor                                                                                 | R <sub>SENSE</sub>                 | -     | 22    | -     | mΩ   |

| OTA Transconductance                                                                                   | G <sub>M</sub>                     | -     | 200   | -     | μS   |

| Transconductance Sink and Source Current Capability                                                    | I <sub>SS</sub>                    | -     | 100   | -     | μA   |

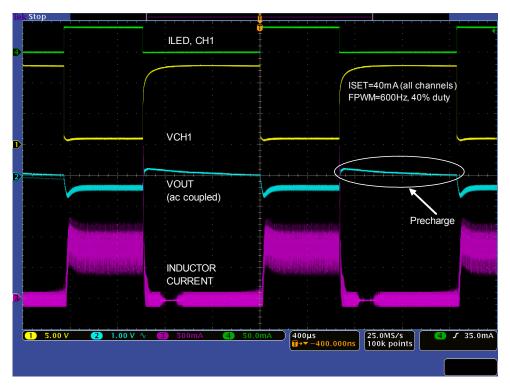

| Output Voltage Precharge                                                                               | V <sub>HOLD</sub>                  | 0.45  | 0.5   | 0.55  | V    |

| FAIL PIN                                                                                               |                                    |       |       |       |      |

| Off-state Leakage Current<br>V <sub>FAIL</sub> = 5.5 V                                                 | I <sub>FAIL_LEAK</sub>             | -     | -     | 5     | μΑ   |

| On-state Voltage Drop<br>I <sub>SINK</sub> = 4.0 mA                                                    | V <sub>OL</sub>                    | -     | -     | 0.4   | V    |

| LED CHANNELS                                                                                           |                                    |       |       |       |      |

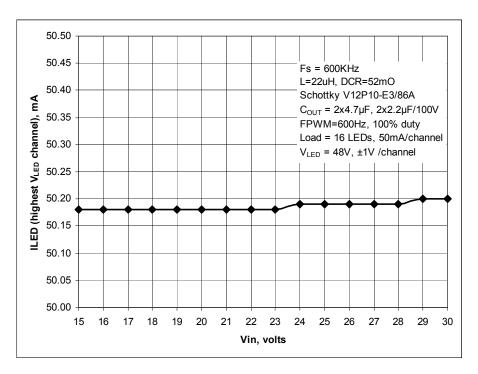

| Sink Current ICHx Register = 255, RISET=5.1 k $\Omega$ 0.1%, PIN&NIN = Disabled, T <sub>A</sub> =25 °C | I <sub>SINK</sub>                  | 49    | 50    | 51    | mA   |

| Regulated minimum voltage across drivers<br>Pulse Width > 4.0 μs                                       | V <sub>MIN</sub>                   | 675   | 750   | 825   | mV   |

| Current Matching Accuracy                                                                              | IMATCH                             | -2.0  | -     | 2.0   | %    |

| I <sub>SET</sub> Pin Voltage<br>RISET=5.1 kΩ 0.1%                                                      | V <sub>SET</sub>                   | 2.017 | 2.048 | 2.079 | V    |

| LED Current Amplitude Resolution<br>1.0 mA $\leq I_{LED} \leq 50$ mA                                   | ILED <sub>RES</sub>                | -     | 1.5   | -     | %    |

| Off-state Leakage Current, All channels<br>(V <sub>CH</sub> = 45 V)                                    | I <sub>CH_LEAK</sub>               | -     | -     | 10    | μΑ   |

| PIN INPUT                                                                                              |                                    | •     |       |       | •    |

| Voltage to Disable PIN mode                                                                            | V <sub>PIN_DIS</sub>               | 2.2   | -     | -     | V    |

| PIN Bias Current<br>PIN = V <sub>SET</sub>                                                             | I <sub>PIN</sub>                   | -2.0  | -     | 2.0   | μΑ   |

|                                                                                                        | -                                  |       |       |       |      |

I<sub>DIM\_PIN</sub>

23.75

47.50

25

50

26.25

52.50

Analog Dimming Current ICHx Register = 255, RISET=5.1 k $\Omega$  0.1% PIN = V<sub>SET</sub>/2 PIN = V<sub>SET</sub>

Notes

9. Guaranteed by design

mΑ

#### ELECTRICAL CHARACTERISTICS STATIC AND DYNAMIC ELECTRICAL CHARACTERISTICS

#### Table 4. Static and Dynamic Electrical Characteristics (continued)

Characteristics noted under conditions V<sub>IN</sub> = 12 V, V<sub>OUT</sub> = 42 V, I<sub>LED</sub> = 50 mA, PWM = VDC1, M/~S = VDC1, PIN & NIN = VDC1, -40 °C  $\leq T_A \leq 105$  °C, PGND = 0 V, unless otherwise noted.

| Characteristic                                  | Symbol               | Min   | Тур     | Max   | Unit   |

|-------------------------------------------------|----------------------|-------|---------|-------|--------|

|                                                 |                      | 1     |         |       | 1      |

| Voltage to Disable NIN mode                     | V <sub>NIN_DIS</sub> | 2.2   | -       | -     | V      |

| NIN Bias Current                                | I <sub>NIN</sub>     | -2.0  | -       | 2.0   | μA     |

| NIN = V <sub>SET</sub>                          |                      |       |         |       |        |

| Analog Dimming Current                          | I <sub>DIM_NIN</sub> |       |         |       | mA     |

| ICHx Register = 255, RISET=5.1 kΩ 0.1%          |                      |       |         |       |        |

| $NIN = V_{SET}/2$                               |                      | 23.75 | 25      | 26.25 |        |

| NIN = 0 V                                       |                      | 47.50 | 50      | 52.50 |        |

| OVER-TEMPERATURE PROTECTION                     |                      |       |         |       |        |

| Over-temperature Threshold <sup>(10)</sup>      | O <sub>TT</sub>      |       |         |       | °C     |

| Rising                                          |                      | 150   | 165     | 175   |        |

| Hysteresis                                      |                      | -     | 25      | -     |        |

| <sup>2</sup> C/SM BUS PHYSICAL LAYER [SCK, SDA] |                      |       |         |       |        |

| I <sup>2</sup> C Address                        | ADR <sub>I2C</sub>   | -     | 1110110 | -     | Binary |

| SM-Bus Address                                  | ADR <sub>SMB</sub>   | -     | 1110110 | -     | Binary |

| Input Low Voltage                               | V <sub>ILI</sub>     | -0.3  | -       | 0.8   | V      |

| Input High Voltage                              | V <sub>IHI</sub>     | 2.1   | -       | 5.5   | V      |

| Input Hysteresis                                | V <sub>HYSI</sub>    | 0.3   | -       | -     | V      |

| Output Low Voltage                              | V <sub>OLI</sub>     | -     | -       | 0.4   | V      |

| Sink Current <u>≤</u> 4.0 mA                    |                      |       |         |       |        |

| Input Current                                   | I <sub>INI</sub>     | -5.0  | -       | 5.0   | μA     |

| Input Capacitance <sup>(10)</sup>               | C <sub>INI</sub>     | -     | -       | 10    | ρF     |

| LOGIC INPUTS / OUTPUTS (CK, M/~S, PWM, A0/SEN)  |                      |       |         |       | •      |

| Input Low Voltage                               | V <sub>ILL</sub>     | -0.3  | -       | 0.5   | V      |

| Input High Voltage                              | V <sub>IHL</sub>     | 1.5   | -       | 5.5   | V      |

| Input Hysteresis                                | V <sub>HYSL</sub>    | -     | 0.1     | -     | V      |

| Input Current                                   | I                    | -5.0  | -       | 5.0   | μА     |

| Output Low Voltage (CK)                         | V <sub>OLL</sub>     | -     | -       | 0.2   | V      |

| I <sub>SINK</sub> ≤2.0 mA                       |                      |       |         |       |        |

| Output High Voltage (CK)                        | V <sub>OHL</sub>     | 2.2   | -       | 5.5   | V      |

| $I_{SOURCE} \leq 2.0 \text{ mA}$                |                      |       |         |       |        |

| Input Capacitance <sup>(10)</sup>               | C <sub>INI</sub>     | -     | -       | 5.0   | ρF     |

Notes

10. Guaranteed by design

### Table 4. Static and Dynamic Electrical Characteristics (continued)

Characteristics noted under conditions V<sub>IN</sub> = 12 V, V<sub>OUT</sub> = 42 V, I<sub>LED</sub> = 50 mA, PWM = VDC1, M/~S = VDC1, PIN & NIN = VDC1, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  105 °C, PGND = 0 V, unless otherwise noted.

| Characteristic                           | Symbol            | Min  | Тур  | Max  | Unit |

|------------------------------------------|-------------------|------|------|------|------|

| OVER-VOLTAGE PROTECTION                  |                   | 1    |      |      |      |

| Over-voltage Clamp - OVP Register Table: |                   |      |      |      |      |

| OVP = Fh                                 | OVP <sub>FH</sub> | 60.5 | 62.5 | 64.5 | V    |

| OVP = Eh                                 | OVP <sub>EH</sub> | 56.5 | 58   | 60   | V    |

| OVP = Dh                                 | OVP <sub>DH</sub> | 53   | 54   | 56   | V    |

| OVP = Ch                                 | OVP <sub>CH</sub> | 49   | 51   | 52.5 | V    |

| OVP = Bh                                 | OVP <sub>BH</sub> | 45   | 47   | 48.5 | V    |

| OVP = Ah                                 | OVP <sub>AH</sub> | 41   | 43   | 44.5 | V    |

| OVP = 9h                                 | OVP <sub>9H</sub> | 38   | 39   | 40.5 | V    |

| OVP = 8h                                 | OVP <sub>8H</sub> | 34   | 36   | 37.5 | V    |

| OVP = 7h                                 | OVP <sub>7H</sub> | 30.5 | 32   | 33.5 | V    |

| OVP = 6h                                 | OVP <sub>6H</sub> | 26   | 28   | 30   | V    |

| OVP = 5h                                 | OVP <sub>5H</sub> | 23   | 24   | 25   | V    |

| OVP = 4h                                 | OVP <sub>4H</sub> | 19   | 20   | 21   | V    |

| OVP = 3h                                 | OVP <sub>3H</sub> | 15   | 16   | 17   | V    |

| OVP = 2h                                 | OVP <sub>2H</sub> | 11   | 12   | 13   | V    |

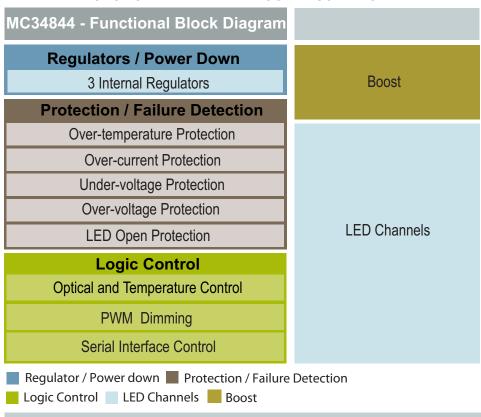

| Over-voltage threshold,                  | OVP <sub>HW</sub> | 6.15 | 6.5  | 6.85 | V    |

| Set by Hardware, Voltage at A0/SEN       |                   |      |      |      |      |

| A0/SEN Sink Current                      | ISINK_OVP         | -    | 100  | -    | μA   |

| BOOST                                    |                   |      |      |      |      |

| Switching Frequency (BST [1:0]=0)        | f <sub>SW0</sub>  | 0.14 | 0.15 | 0.17 | MHz  |

| Switching Frequency (BST [1:0]=1)        | f <sub>SW1</sub>  | 0.27 | 0.30 | 0.33 | MHz  |

| Switching Frequency (BST [1:0]=2)        | f <sub>SW2</sub>  | 0.54 | 0.60 | 0.66 | MHz  |

| Switching Frequency (BST [1:0]=3)        | f <sub>SW3</sub>  | 1.08 | 1.2  | 1.32 | MHz  |

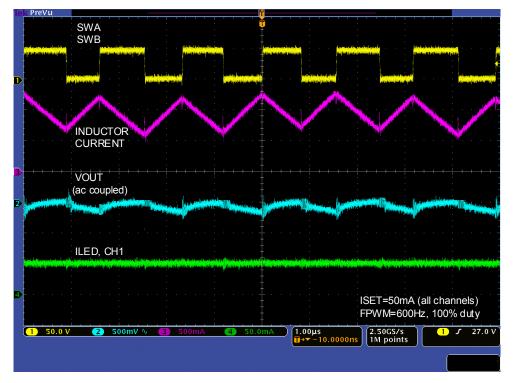

| Minimum Duty Cycle                       | D <sub>MIN</sub>  | -    | 10   | 15   | %    |

| Maximum Duty Cycle                       | D <sub>MAX</sub>  | 80   | 85   | -    | %    |

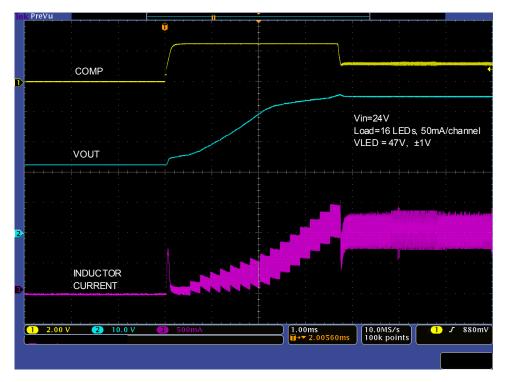

| Soft Start Period                        | t <sub>SS</sub>   | -    | 6.5  | -    | ms   |

| Boost Switch Rise Time <sup>(10)</sup>   | t <sub>TR</sub>   | -    | 15   | -    | ns   |

| Boost Switch Fall Time <sup>(10)</sup>   | t <sub>F</sub>    | -    | 25   | -    | ns   |

Notes

11. Guaranteed by design

#### ELECTRICAL CHARACTERISTICS STATIC AND DYNAMIC ELECTRICAL CHARACTERISTICS

#### Table 4. Static and Dynamic Electrical Characteristics (continued)

Characteristics noted under conditions V<sub>IN</sub> = 12 V, V<sub>OUT</sub> = 42 V, I<sub>LED</sub> = 50 mA, PWM = VDC1, M/~S = VDC1, PIN & NIN = VDC1, -40 °C  $\leq T_A \leq 105$  °C, PGND = 0 V, unless otherwise noted.

| Characteristic                                                                | Symbol                         | Min         | Тур          | Мах          | Unit |

|-------------------------------------------------------------------------------|--------------------------------|-------------|--------------|--------------|------|

| PWM GENERATOR                                                                 |                                |             |              |              |      |

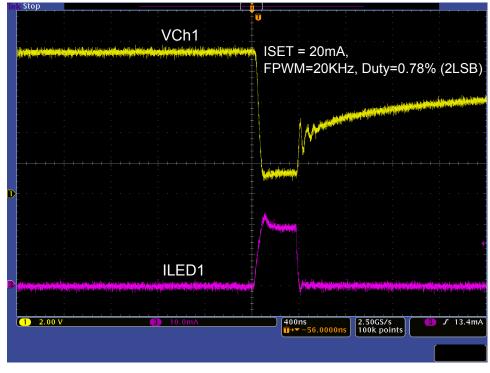

| PWM Frequency Range <sup>(13)</sup><br>M/~S = Low (Slave Mode)                | fPWM <sub>S</sub>              | 100         | -            | 25000        | Hz   |

| PWM Frequency<br>M/~S = High (Master Mode)                                    | fPWM <sub>M</sub>              |             |              |              | Hz   |

| FPWM Register = 768<br>FPWM Register = 192,000                                |                                | 22500<br>90 | 25000<br>100 | 27500<br>110 |      |

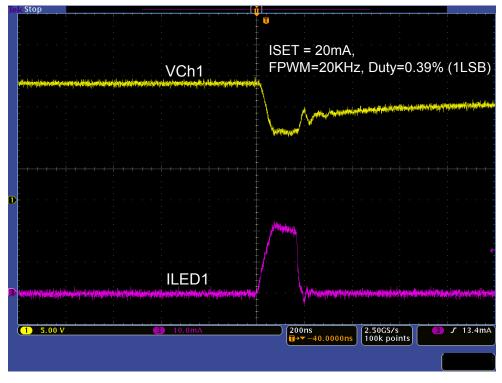

| PWM dimming resolution                                                        | t <sub>fPWM</sub>              | -           | 0.39         | -            | %    |

| PWM PIN (DIRECT PWM CONTROL)                                                  |                                |             |              |              |      |

| Input PWM Pin Minimum Pulse <sup>(13)</sup>                                   | t <sub>PWM_IN</sub>            | 150         | -            | -            | ns   |

| Input PWM Frequency Range                                                     | fPWM                           | 100         | -            | 23000        | Hz   |

| PHASE LOCK LOOP                                                               |                                |             | •            | •            |      |

| CK Slave Mode Frequency Lock Range <sup>(12)</sup><br>M/~S = Low (Slave Mode) | fCK <sub>S</sub>               | 100         | -            | 25000        | Hz   |

| CK Slave Mode Input Jitter <sup>(13)</sup><br>M/~S = Low (Slave Mode)         | fCK <sub>S_JITTER</sub>        | -           | -            | 0.1          | %    |

| Slave Mode Acquisition Time<br>M/~S = Low (Slave Mode)                        | T <sub>S_ACQ</sub>             |             |              |              |      |

| FPWM <sub>S</sub> =25 kHz                                                     |                                | -           | -            | 50           | ms   |

| FPWM <sub>S</sub> =100 Hz                                                     |                                | -           | 2000         | -            | ms   |

| CK Frequency (Master Mode)<br>FPWM Register = 768<br>FPWM Register = 192,000  | fCK <sub>MASTER</sub>          | 22500<br>90 | 25000<br>100 | 27500<br>110 | Hz   |

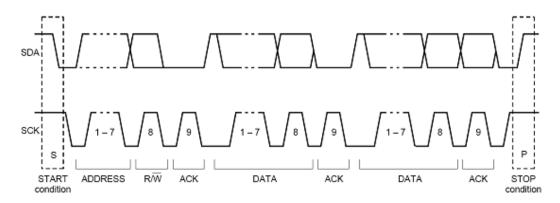

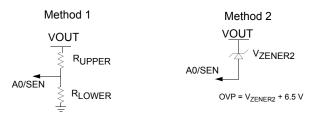

| <sup>2</sup> C/SM BUS PHYSICAL LAYER [SCK, SDA]                               |                                |             |              |              |      |

| Interface Frequency Range                                                     | f <sub>SCK</sub>               |             |              | 400          | kHz  |

| SM Bus Power-on-Reset Time                                                    | t <sub>RST</sub>               | -           | -            | 100          | ms   |

| Output fall time<br>10 ρF <u>&lt; C<sub>L</sub> &lt; 400 ρ</u> F              | t <sub>F</sub>                 | 40          | -            | 160          | ns   |

| Output rise time<br>10 ρF≤C <sub>L</sub> ≤400 ρF                              | t <sub>R</sub>                 | 20          | -            | 80           | ns   |

| LOGIC OUTPUT (CK)                                                             |                                |             |              |              |      |

| Output Rise and Fall time <sup>(12)</sup><br>C <sub>L</sub> ≤100 ρF           | t <sub>R</sub> /t <sub>F</sub> | -           | -            | 25           | ns   |

| ED CHANNELS                                                                   |                                | <u> </u>    | 1            | 1            |      |

| Channels Rise and Fall Time <sup>(13)</sup>                                   | t <sub>R</sub> /t <sub>F</sub> | -           | 23           | 50           | ns   |

| Notes                                                                         | TX T                           |             |              |              |      |

12. Special considerations should be made for frequencies between 100 Hz to 1.0 KHz. Please refer to Functional Device Operation for further details.

13. Guaranteed by design

# FUNCTIONAL DESCRIPTION

## **INTRODUCTION**

LED backlighting has become very popular for small and medium LCDs, due to some advantages over other backlighting schemes, such as the widely used cold cathode fluorescent lamp (CCFL). The advantages of LED backlighting are low cost, long life, immunity to vibration, low operational voltage, and precise control over its intensity.

However, there is an important drawback of this method. It requires more power than most of the other methods, and this is a major problem if the LCD size is large enough.

To address the power consumption problem, solid state optoelectronics technologies are evolving to create brighter LEDs with lower power consumption. These new technologies together with highly efficient power management LED drivers are turning LEDs, a more suitable solution for backlighting almost any size of LCD panel, with really conservative power consumption.

One of the most common schemes for backlighting with LED is the one known as "Array backlighting". This creates a matrix of LEDs all over the LCD surface, using defraction and diffused layers to produce an homogenous and even light at

the LCD surface. Each row or column is formed by a number of LEDs in series, forcing a single current to flow through all LEDs in each string.

Using a current control driver, per row or column, helps the system to maintain a constant current flowing through each line, keeping a steady amount of light even with the presence of line or load variations. They can also be use as a light intensity control by increasing or decreasing the amount of current flowing through each LED string.

To achieve enough voltage to drive a number of LEDs in series, a boost converter is implemented, to produce a higher voltage from a smaller one, which is typically used by the logical blocks to do their function.

The 34844 implements a single channel boost converter together with 10 input channels, for driving up to 16 LEDs per string to create a matrix of more than 160 LEDs. Together with its 90% efficiency and  $I^2C$  programmable or external current control, among other features, makes the 34844 a perfect solution for backlighting small and medium size LCD panels, on low power portable and high definition devices.

## FUNCTIONAL PIN DESCRIPTION

## **INPUT VOLTAGE SUPPLY (VIN)**

IC Power input supply voltage, is used internally to produce internal voltage regulation (VDC1, VDC3) for logic functioning, and also as an input voltage for the boost regulator.

## **INTERNAL VOLTAGE REGULATOR 1 (VDC1)**

This pin is for internal use only, and not to be used for other purposes. A capacitor of  $2.2 \ \mu F$  should be connected between this pin and ground for decoupling purposes.

## **INTERNAL VOLTAGE REGULATOR 2 (VDC2)**

This pin is for internal use only, and not to be used for other purposes. A capacitor of 2.2  $\mu$ F should be connected between this pin and ground for decoupling purposes.

## **INTERNAL VOLTAGE REGULATOR 3 (VDC3)**

This pin is for internal use only, and not to be used for other purposes. A capacitor of 2.2  $\mu$ F should be connected between this pin and ground for decoupling purposes. A 1.0 k $\Omega$  resistor between the VDC3 and VDC1 pin is recommended for <-20 °C operation.

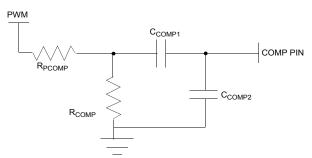

## **BOOST COMPENSATION PIN (COMP)**

Passive pin used to compensate the boost converter. Add a capacitor and a resistor in series to GND to stabilize the system.

#### IC ENABLE (EN)

The active high enable pin is internally pulled high through pull-up resistors. Applying 0 V to this pin would stop the IC from working.

## **INPUT/OUTPUT CLOCK SIGNAL (CK)**

This pin can be used as an output clock signal (master mode), or input clock signal (slave mode), to synchronize more than one device.

## MASTER/SLAVE MODE SELECTION (M/~S)

Setting this pin High puts the device into Master mode, producing an output synchronization clock at the CK pin. Setting this pin low, puts the device in Slave mode, using the CK pin as an input clock.

#### **EXTERNAL PWM INPUT (PWM)**

This pin is internally pulled down. An external PWM signal can be applied to modulate the LED channel directly in absence of an  $I^2C$  interface.

## CLOCK I<sup>2</sup>C SIGNAL (SCK)

Clock line for I<sup>2</sup>C communication.

## ADDRESS I<sup>2</sup>C SIGNAL (SDA)

Address line for I<sup>2</sup>C communication.

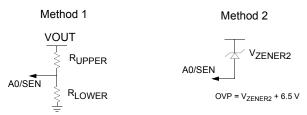

#### A0/SEN

Address select, device select pin, or Hardware Overvoltage Protection (OVP) Control.

## **CURRENT SET (ISET)**

Each LED string can drive up to 50 mA. The maximum current can be set by using a resistor from this pin to GND.

## **POSITIVE CURRENT SCALING (PIN)**

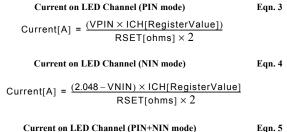

Positive current scaling factor for the external analog current control. Applying 0 V to this pin, scales the current to near 0%, and in the same way, applying 2.048 V (Vset), the scale factor is 100%. By applying a voltage higher than 2.2 V, the scaling factor is disabled, and the internal pull-ups are activated.

If PIN pin and NIN pin are used at the same time then by applying 0 V to the PIN pin and 2.048 V to NIN pin, scales the current to near 0%, and in the same way, applying 2.048 V to the PIN pin and 0 V to NIN pin, scales the current to 100%. By applying a voltage higher than 2.2 V, the scaling factor is disabled and the internal pull-ups are activated in both pins.

## **NEGATIVE CURRENT SCALING (NIN)**

Negative current scaling factor for the external analog current control. Setting 0 V to this pin scales the current to 100%, in the same way, setting 2.048 V (Vset) the scale factor is near 0%. By applying a voltage higher than 2.2 V, the scaling factor is disabled and the internal pull-ups are activated.

If PIN pin and NIN pin are used at the same time then by applying 0 V to the PIN pin and 2.048 V to NIN pin, scales the current near 0%, and in the same way, applying 2.048 V to the PIN pin and 0 V to NIN pin, scales the current to 100%.

By applying a voltage higher than 2.2 V, the scaling factor is disabled and the internal pull-ups are activated in both pins.

#### **GROUND (GND)**

Ground Reference for all internal circuits other than the Boost FET.

The Exposed Pad (EP) should be used for thermal heat dissipation.

#### 10-19

Current LED driver, each line has the capability of driving up to 50 mA.

## FAULT DETECTION PIN (FAIL)

When a fault situation is detected, this pin goes into high impedance.