# **Enhanced A/D Type 8-bit OTP MCU**

# HT46R068B/HT46R069B

Revision: 1.00 Date: January 26, 2011

www.holtek.com

# **Table of Contents**

| Features                                                                                                                                                                                                                                                                                                                                                                                                   |                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| CPU Features                                                                                                                                                                                                                                                                                                                                                                                               |                                  |

| Peripheral Features                                                                                                                                                                                                                                                                                                                                                                                        | 1                                |

| General Description                                                                                                                                                                                                                                                                                                                                                                                        | 2                                |

| Selection Table                                                                                                                                                                                                                                                                                                                                                                                            | 2                                |

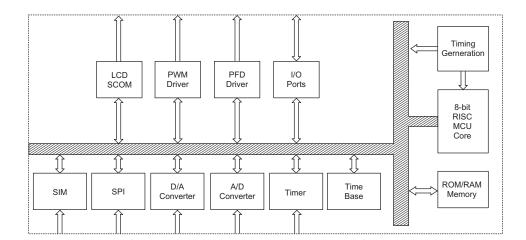

| Block Diagram                                                                                                                                                                                                                                                                                                                                                                                              | 2                                |

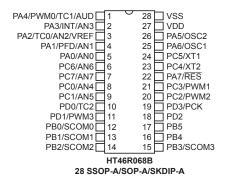

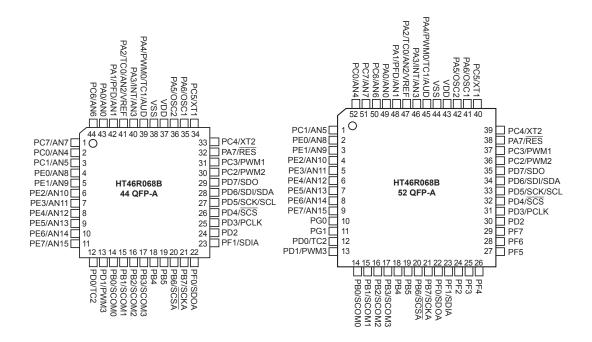

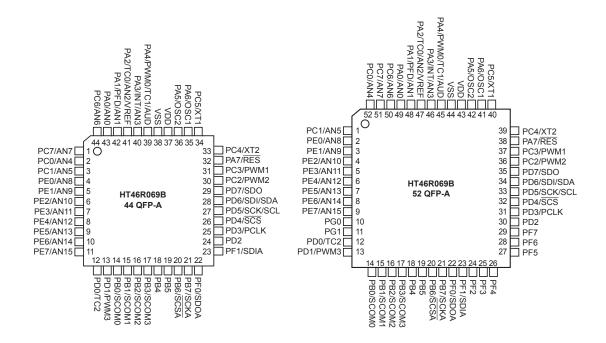

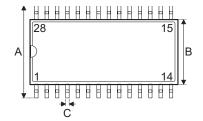

| Pin Assignment                                                                                                                                                                                                                                                                                                                                                                                             | 3                                |

| Pin Description                                                                                                                                                                                                                                                                                                                                                                                            | 5                                |

| Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                   | 7                                |

| D.C. Characteristics                                                                                                                                                                                                                                                                                                                                                                                       | 7                                |

| A.C. Characteristics                                                                                                                                                                                                                                                                                                                                                                                       | 9                                |

| ADC Characteristics                                                                                                                                                                                                                                                                                                                                                                                        | 10                               |

| DAC Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                             | 10                               |

| Power-on Reset Characteristics                                                                                                                                                                                                                                                                                                                                                                             | 10                               |

| System Architecture                                                                                                                                                                                                                                                                                                                                                                                        | 11                               |

| Clocking and Pipelining                                                                                                                                                                                                                                                                                                                                                                                    |                                  |

| Program Counter                                                                                                                                                                                                                                                                                                                                                                                            | 12                               |

| Stack                                                                                                                                                                                                                                                                                                                                                                                                      | 13                               |

| Arithmetic and Logic Unit – ALU                                                                                                                                                                                                                                                                                                                                                                            | 13                               |

|                                                                                                                                                                                                                                                                                                                                                                                                            |                                  |

| Program Memory                                                                                                                                                                                                                                                                                                                                                                                             | 14                               |

| Program Memory Structure                                                                                                                                                                                                                                                                                                                                                                                   |                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                            | 14                               |

| Structure                                                                                                                                                                                                                                                                                                                                                                                                  | 14<br>15                         |

| StructureSpecial Vectors                                                                                                                                                                                                                                                                                                                                                                                   | 14<br>15<br>15                   |

| Structure                                                                                                                                                                                                                                                                                                                                                                                                  | 14<br>15<br>15                   |

| Structure                                                                                                                                                                                                                                                                                                                                                                                                  | 14<br>15<br>15<br>16             |

| Structure                                                                                                                                                                                                                                                                                                                                                                                                  | 14<br>15<br>16<br>18             |

| Structure                                                                                                                                                                                                                                                                                                                                                                                                  | 14<br>15<br>16<br>18<br>18<br>19 |

| Structure                                                                                                                                                                                                                                                                                                                                                                                                  | 14<br>15<br>16<br>18<br>18<br>19 |

| Structure                                                                                                                                                                                                                                                                                                                                                                                                  | 14<br>15<br>16<br>18<br>18<br>19 |

| Structure                                                                                                                                                                                                                                                                                                                                                                                                  | 141516181920                     |

| Structure Special Vectors Look-up Table Table Program Example  Data Memory Structure Special Purpose Data Memory Special Function Registers Indirect Addressing Registers – IAR0, IAR1 Memory Pointers – MP0, MP1                                                                                                                                                                                          | 1415161819202020                 |

| Structure Special Vectors Look-up Table Table Program Example  Data Memory Structure Special Purpose Data Memory  Special Function Registers Indirect Addressing Registers – IAR0, IAR1 Memory Pointers – MP0, MP1 Accumulator – ACC                                                                                                                                                                       | 14151618192020202023             |

| Structure Special Vectors Look-up Table Table Program Example  Data Memory Structure Special Purpose Data Memory.  Special Function Registers Indirect Addressing Registers – IAR0, IAR1 Memory Pointers – MP0, MP1 Accumulator – ACC. Program Counter Low Register – PCL.                                                                                                                                 | 14151618192020202323             |

| Structure Special Vectors Look-up Table Table Program Example  Data Memory Structure Special Purpose Data Memory  Special Function Registers Indirect Addressing Registers – IAR0, IAR1 Memory Pointers – MP0, MP1 Accumulator – ACC Program Counter Low Register – PCL. Bank Pointer – BP.                                                                                                                |                                  |

| Structure Special Vectors Look-up Table Table Program Example  Data Memory Structure Special Purpose Data Memory  Special Function Registers Indirect Addressing Registers – IAR0, IAR1 Memory Pointers – MP0, MP1 Accumulator – ACC Program Counter Low Register – PCL Bank Pointer – BP Status Register – STATUS                                                                                         |                                  |

| Structure Special Vectors Look-up Table Table Program Example  Data Memory Structure Special Purpose Data Memory  Special Function Registers Indirect Addressing Registers – IAR0, IAR1 Memory Pointers – MP0, MP1 Accumulator – ACC Program Counter Low Register – PCL Bank Pointer – BP Status Register – STATUS Input/Output Ports and Control Registers                                                |                                  |

| Structure Special Vectors Look-up Table Table Program Example  Data Memory Structure Special Purpose Data Memory  Special Function Registers Indirect Addressing Registers – IAR0, IAR1 Memory Pointers – MP0, MP1 Accumulator – ACC Program Counter Low Register – PCL Bank Pointer – BP Status Register – STATUS Input/Output Ports and Control Registers System Control Registers – CTRL0, CTRL1, CTRL2 |                                  |

| Os  | cillator                                               | 28  |

|-----|--------------------------------------------------------|-----|

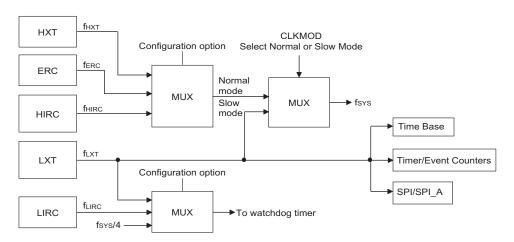

|     | System Oscillator Overview                             | .28 |

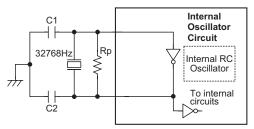

|     | External Crystal/Resonator Oscillator – HXT            | .28 |

|     | External RC Oscillator – ERC                           | .29 |

|     | Internal RC Oscillator – HIRC                          | .30 |

|     | External 32768Hz Crystal Oscillator – LXT              | .30 |

|     | LXT Oscillator Low Power Function                      | .31 |

|     | Internal Low Speed Oscillator – LIRC                   | .31 |

| On  | perating Modes                                         | 32  |

| •   | Mode Types and Selection                               |     |

|     | Mode Switching                                         | .33 |

|     | Standby Current Considerations                         | .33 |

|     | Wake-up                                                | .34 |

|     | Watchdog Timer Operation                               | .35 |

| Re  | set and Initialisation                                 | 36  |

|     | Reset Functions                                        |     |

|     | Reset Initial Conditions                               |     |

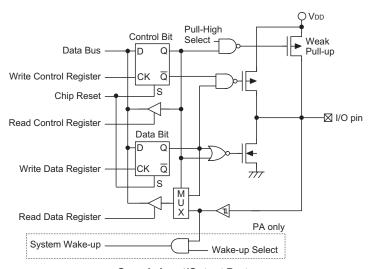

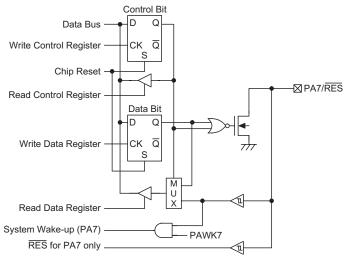

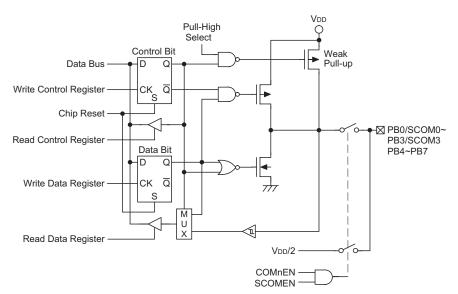

| Inr | out/Output Ports                                       |     |

|     | Pull-high Resistors                                    |     |

|     | Port A Wake-up                                         |     |

|     | I/O Port Control Registers                             |     |

|     | Pin-shared Functions                                   |     |

|     | Pin Remapping Configuration                            |     |

|     | I/O Pin Structures                                     |     |

|     | Programming Considerations                             |     |

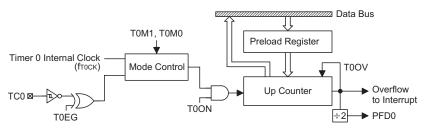

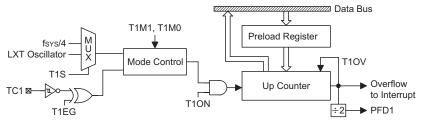

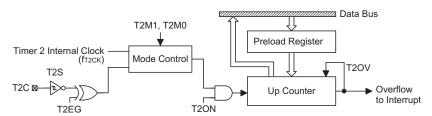

| Tir | ner/Event Counters                                     |     |

| ''' | Configuring the Timer/Event Counter Input Clock Source |     |

|     | Timer Registers – TMR0, TMR1, TMR2L, TMR2H             |     |

|     | Timer Control Registers – TMR0C, TMR1C, TMR2C          |     |

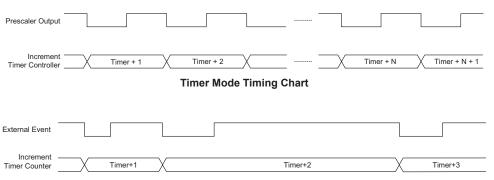

|     | Timer Mode                                             |     |

|     | Event Counter Mode                                     |     |

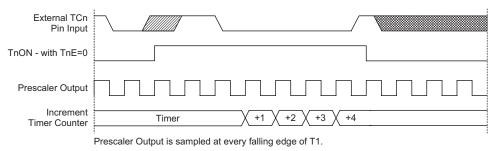

|     | Pulse Width Capture Mode                               |     |

|     | Prescaler                                              |     |

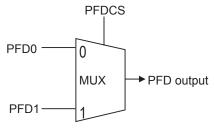

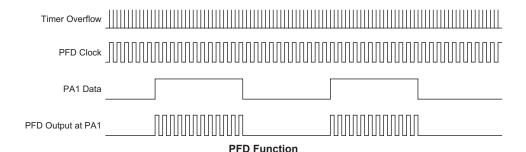

|     | PFD Function                                           |     |

|     | I/O Interfacing                                        | .55 |

|     | Programming Considerations                             |     |

|     | Timer Program Example                                  |     |

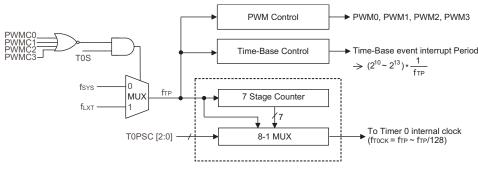

|     | Time Base                                              |     |

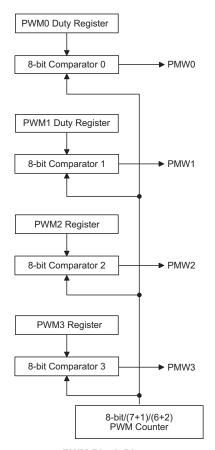

| Pu  | lse Width Modulator                                    |     |

| . u | PWM Operation                                          |     |

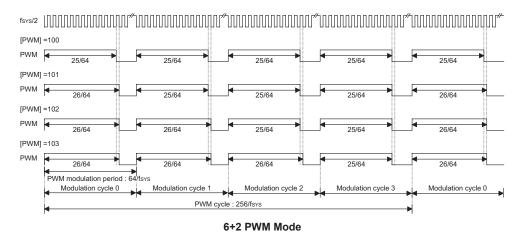

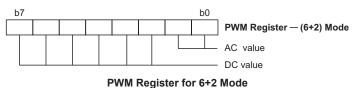

|     | 6+2 PWM Mode                                           |     |

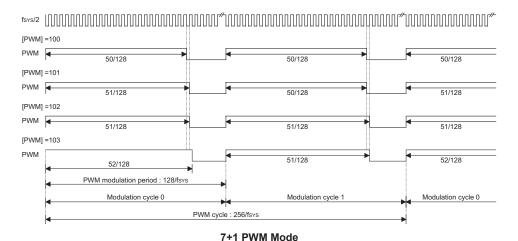

|     | 7+1 PWM Mode                                           |     |

|     | PWM Output Control                                     | 60  |

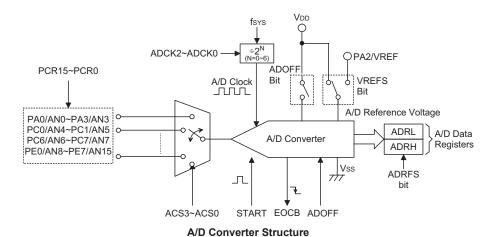

| Analog to Digital Converter                                  | 61  |

|--------------------------------------------------------------|-----|

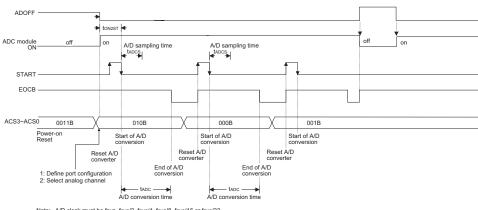

| A/D Overview                                                 | 61  |

| A/D Converter Data Registers – ADRL, ADRH                    | 61  |

| A/D Converter Control Registers – ADCR, ACSR, ANCSR1, ANCSR0 | 61  |

| A/D Input Pins                                               | 67  |

| Summary of A/D Conversion Steps                              | 67  |

| Programming Considerations                                   | 68  |

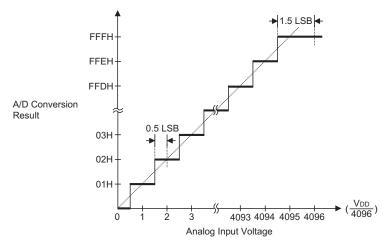

| A/D Transfer Function                                        | 68  |

| A/D Programming Example                                      | 69  |

| Interrupts                                                   | 72  |

| Interrupt Register                                           | 72  |

| Interrupt Operation                                          | 74  |

| Interrupt Priority                                           | 75  |

| External Interrupt                                           | 76  |

| Timer/Event Counter Interrupt                                | 76  |

| Multi-function Interrupt                                     | 76  |

| Programming Considerations                                   | 77  |

| LCD SCOM Function                                            | 78  |

| LCD Operation                                                |     |

| LCD Bias Control                                             |     |

| Serial Interface Module – SIM                                | 80  |

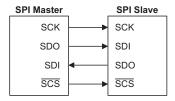

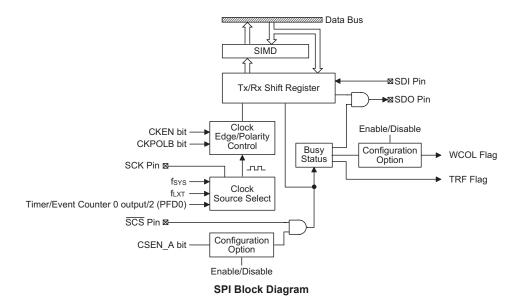

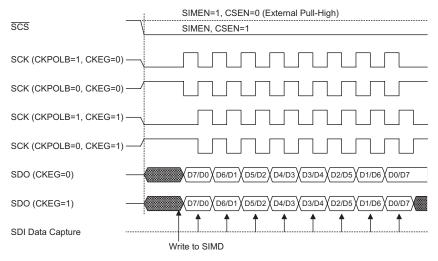

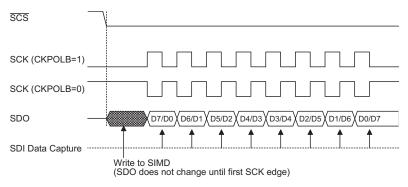

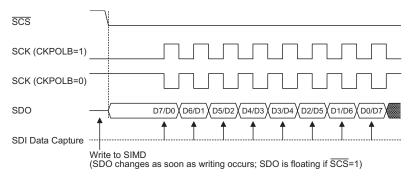

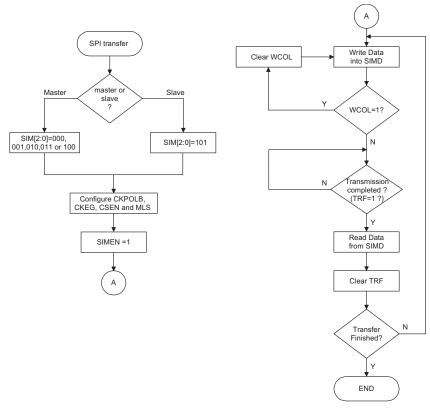

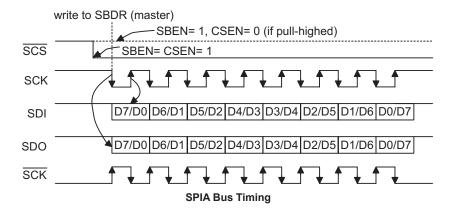

| SPI Interface                                                |     |

| SPI Registers                                                |     |

| SPI Communication                                            |     |

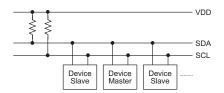

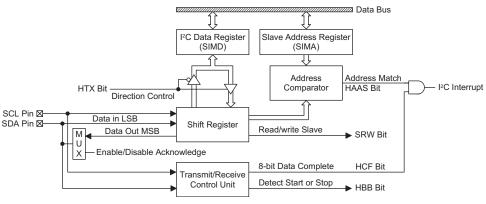

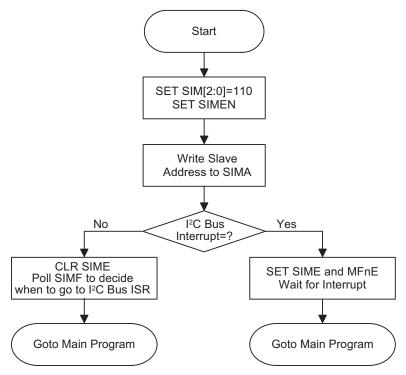

| I <sup>2</sup> C Interface                                   | 87  |

| I <sup>2</sup> C Registers                                   |     |

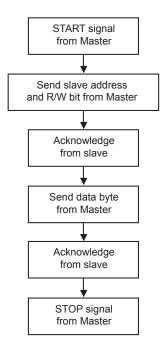

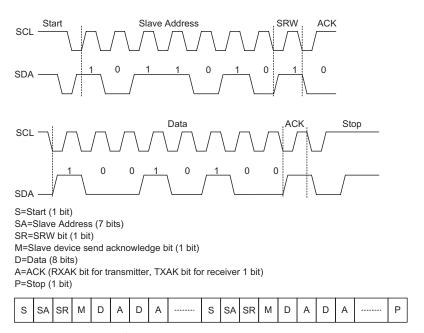

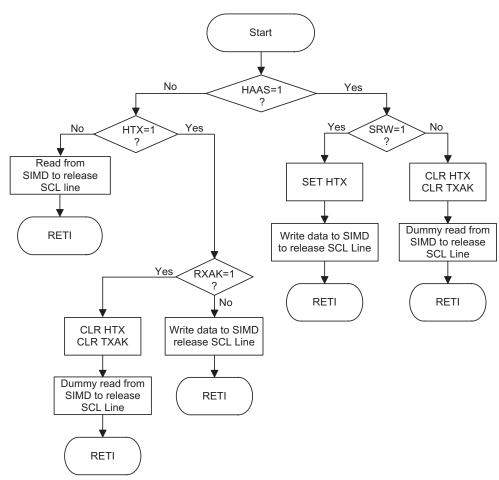

| I <sup>2</sup> C Bus Communication                           | 92  |

| I <sup>2</sup> C Bus Start Signal                            | 93  |

| Slave Address                                                | 93  |

| I <sup>2</sup> C Bus Read/Write Signal                       | 94  |

| I <sup>2</sup> C Bus Slave Address Acknowledge Signal        | 94  |

| I <sup>2</sup> C Bus Data and Acknowledge Signal             | 94  |

| Peripheral Clock Output                                      | 97  |

| Peripheral Clock Operation                                   |     |

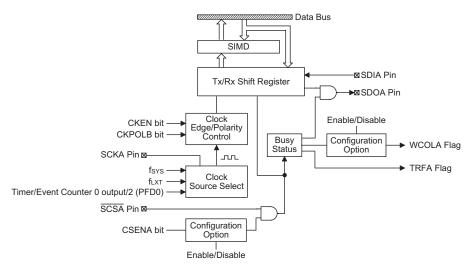

| SPIA Serial Interface – SPIA                                 | 98  |

| SPIA Interface Communication                                 |     |

| SPIA Registers                                               |     |

| SPIA Bus Enable/Disable                                      |     |

| SPIA Operation                                               |     |

| SPIA Configuration Options                                   |     |

| Error Detection                                              |     |

| Programming Considerations                                   |     |

| Digital to Analog Converter – DAC                            | 102 |

| Operation                                 | 102 |

|-------------------------------------------|-----|

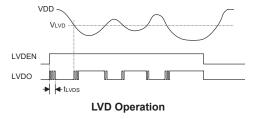

| Low Voltage Detector - LVD                |     |

| LVD Register                              |     |

| LVD Operation                             |     |

| Configuration Options                     | 104 |

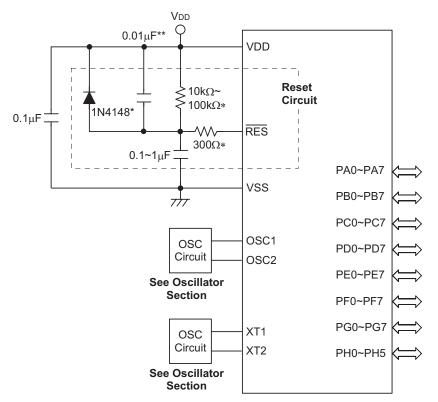

| Application Circuit                       | 106 |

| Instruction Set                           | 107 |

| Introduction                              | 107 |

| Instruction Timing                        | 107 |

| Moving and Transferring Data              | 107 |

| Arithmetic Operations                     | 107 |

| Logical and Rotate Operations             | 107 |

| Branches and Control Transfer             | 108 |

| Bit Operations                            | 108 |

| Table Read Operations                     | 108 |

| Other Operations                          | 108 |

| Instruction Set Summary                   | 109 |

| Table conventions                         | 109 |

| Instruction Definition                    | 111 |

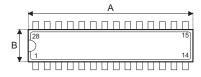

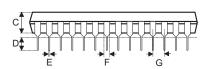

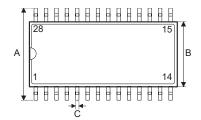

| Package Information                       | 121 |

| 28-pin SKDIP (300mil) Outline Dimensions  | 121 |

| 28-pin SOP (300mil) Outline Dimensions    | 122 |

| 28-pin SSOP (150mil) Outline Dimensions   | 123 |

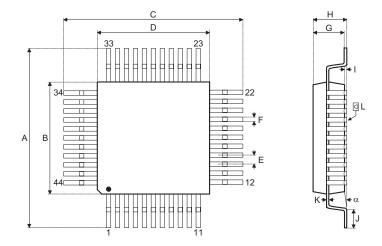

| 44-pin QFP (10mmx10mm) Outline Dimensions | 124 |

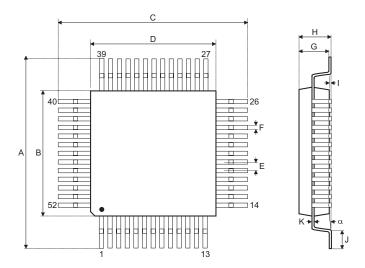

| 52-pin QFP (14mmx14mm) Outline Dimensions | 125 |

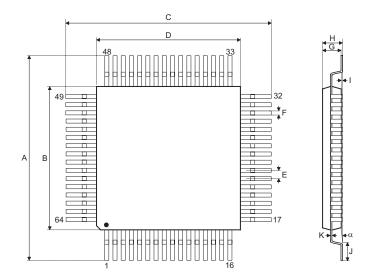

| 64-pin LQFP (7mmx7mm) Outline Dimensions  | 126 |

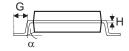

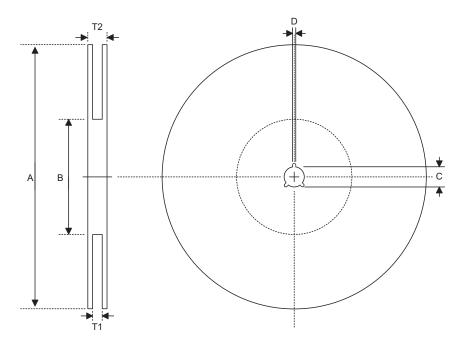

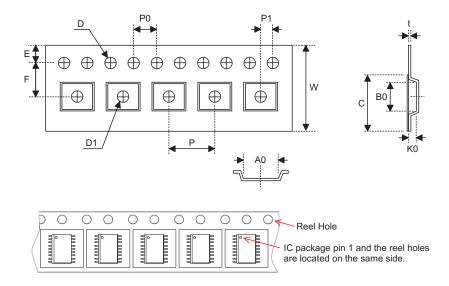

| Reel Dimensions                           | 127 |

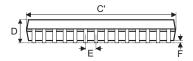

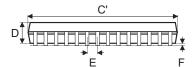

| Carrier Tane Dimensions                   | 128 |

### **Features**

#### **CPU Features**

• Operating voltage:

$f_{SYS}$ = 4MHz: 2.2V~5.5V  $f_{SYS}$ =8MHz: 3.0V~5.5V  $f_{SYS}$ =12MHz: 4.5V~5.5V

- Up to 0.33  $\mu$ s instruction cycle with 12MHz system clock at  $V_{DD}$ = 5V

- Idle/Sleep mode and wake-up functions to reduce power consumption

- Oscillator types:

External high frequency Crystal - HXT

External RC - ERC

Internal RC - HIRC

External low frequency crystal - LXT

- Four operational modes: Normal, Slow, Idle, Sleep

- Fully integrated internal 4MHz, 8MHz and 12MHz oscillator requires no external components

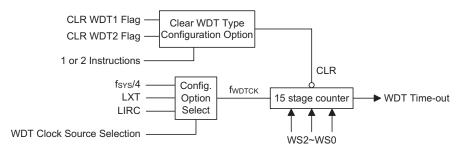

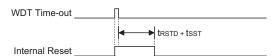

- Watchdog Timer function

- LIRC oscillator function for watchdog timer

- All instructions executed in one or two instruction cycles

- Table read instructions

- 63 powerful instructions

- Up to 8-level subroutine nesting

- Bit manipulation instruction

- Low voltage reset function

- Low voltage detect function

- Wide range of available package types

#### **Peripheral Features**

- Up to 62 bidirectional I/O lines

- Up to 16 channel 12-bit ADC

- Up to 4 channel 8-bit PWM

- Single channel 12-bit DAC

- Serial Interfaces Module with Dual SPI and I<sup>2</sup>C interfaces

- Single Serial SPI Interface

- Software controlled 4-SCOM lines LCD COM driver with 1/2 bias

- External interrupt input shared with an I/O line

- Two 8-bit programmable Timer/Event Counter with overflow interrupt and prescaler

- Single 16-bit programmable Timer/Event Counter with overflow interrupt

- Time-Base function

- Programmable Frequency Divider PFD

Rev. 1.00 1 January 26, 2011

### **General Description**

The Enhanced A/D MCUs are a series of 8-bit high performance, RISC architecture microcontrollers specifically designed for a wide range of applications. The usual Holtek microcontroller features of low power consumption, I/O flexibility, timer functions, oscillator options, power down and wake-up functions, watchdog timer and low voltage reset, combine to provide devices with a huge range of functional options while still maintaining a high level of cost effectiveness. The fully integrated system oscillator HIRC, which requires no external components and which has three frequency selections, opens up a huge range of new application possibilities for these devices, some of which may include industrial control, consumer products, household appliances subsystem controllers, etc.

### **Selection Table**

| Part No.  | Program<br>Memory | Data<br>Memory | I/O | 8-bit<br>Timer | 16-bit<br>Timer | Time<br>Base | HIRC<br>(MHz) | RTC<br>(LXT) | LCD<br>SCOM |

|-----------|-------------------|----------------|-----|----------------|-----------------|--------------|---------------|--------------|-------------|

| HT46R068B | 16Kx16            | 512x8          | 50  | 2              | 1               | 1            | 4/8/12        | √(*)         | 4           |

| HT46R069B | 32Kx16            | 1024x8         | 62  | 2              | 1               | 1            | 4/8/12        | √(*)         | 4           |

| Part No.  | A/D       | PWM     | D/A      | Interface                    | PFD | Stack | Package                           |

|-----------|-----------|---------|----------|------------------------------|-----|-------|-----------------------------------|

| HT46R068F | 12-bitx16 | 8-bitx4 | 12-bitx1 | SPI/I <sup>2</sup> C,<br>SPI | √   | 8     | 28SKDIP/<br>SOP/SSOP,<br>44/52QFP |

| HT46R069  | 12-bitx16 | 8-bitx4 | 12-bitx1 | SPI/I <sup>2</sup> C,<br>SPI | √   | 8     | 44/52QFP<br>64LQFP                |

Note: "\*" the oscillator is connected to the XT1/XT2 pins with TinyPower™ design.

### **Block Diagram**

The following block diagram illustrates the main functional blocks.

Rev. 1.00 2 January 26, 2011

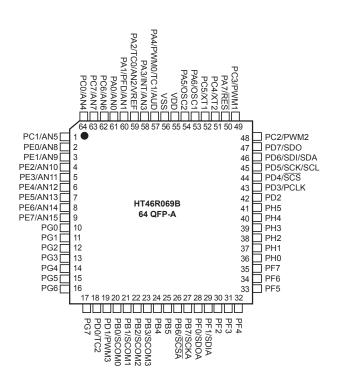

### **Pin Assignment**

Rev. 1.00 4 January 26, 2011

## **Pin Description**

| Pin Name         | Function | OPT          | I/T | O/T  | Descriptions                                               |

|------------------|----------|--------------|-----|------|------------------------------------------------------------|

| - III Italiio    |          | PAPU         |     |      | General purpose I/O. Register enabled pull-up and          |

| PA0/AN0          | PA0      | PAWK         | ST  | CMOS | wake-up.                                                   |

|                  | AN0      | ANCSR0       | AN  | _    | A/D channel 0                                              |

|                  | PA1      | PAPU<br>PAWK | ST  | CMOS | General purpose I/O. Register enabled pull-up and wake-up. |

| PA1/PFD/AN1      | PFD      | CTRL0        | _   | CMOS | PFD output                                                 |

|                  | AN1      | ANCSR0       | AN  | _    | A/D channel 1                                              |

|                  | PA2      | PAPU<br>PAWK | ST  | CMOS | General purpose I/O. Register enabled pull-up and wake-up. |

| PA2/TC0/AN2/VREF | TC0      | _            | ST  | _    | External Timer 0 clock input                               |

|                  | AN2      | ANCSR0       | AN  | _    | A/D channel 2                                              |

|                  | VREF     | ACSR         | AN  | _    | ADC reference input                                        |

|                  | PA3      | PAPU<br>PAWK | ST  | CMOS | General purpose I/O. Register enabled pull-up and wake-up. |

| PA3/INTB/AN3     | INTB     | _            | ST  | _    | External Interrupt input                                   |

|                  | AN3      | ANCSR0       | AN  | _    | A/D channel 3                                              |

|                  | PA4      | PAPU<br>PAWK | ST  | CMOS | General purpose I/O. Register enabled pull-up and wake-up. |

| PA4/PWM0/TC1/AUD | PWM0     | CTRL0        | _   | CMOS |                                                            |

|                  | TC1      | _            | ST  | _    | External Timer 1 clock input                               |

|                  | AUD      | _            | _   | AN   | DAC output                                                 |

| PA5/OSC2         | PA5      | PAPU<br>PAWK | ST  | CMOS | General purpose I/O. Register enabled pull-up and wake-up. |

|                  | OSC2     | СО           | _   | OSC  | Oscillator pin                                             |

| PA6/OSC1         | PA6      | PAPU<br>PAWK | ST  | CMOS | General purpose I/O. Register enabled pull-up and wake-up. |

|                  | OSC1     | CO           | OSC | _    | Oscillator pin                                             |

| DA7/DE0          | PA7      | PAWK         | ST  | NMOS | General purpose I/O. Register enabled wake-up.             |

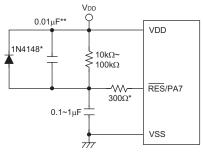

| PA7/RES          | RES      | CO           | ST  | _    | Reset input                                                |

| DD0/CCOM0        | PB0      | PBPU         | ST  | CMOS | General purpose I/O. Register enabled pull-up              |

| PB0/SCOM0        | SCOM0    | SCOMC        | _   | SCOM | Software controlled 1/2 bias LCD COM                       |

| DD1/CCOM1        | PB1      | PBPU         | ST  | CMOS | General purpose I/O. Register enabled pull-up              |

| PB1/SCOM1        | SCOM1    | SCOMC        | _   | SCOM | Software controlled 1/2 bias LCD COM                       |

| DD0/CCOM0        | PB2      | PBPU         | ST  | CMOS | General purpose I/O. Register enabled pull-up              |

| PB2/SCOM2        | SCOM2    | SCOMC        | _   | SCOM | Software controlled 1/2 bias LCD COM                       |

| PB3/SCOM3        | PB3      | PBPU         | ST  | CMOS | General purpose I/O. Register enabled pull-up              |

| FB3/3CON3        | SCOM3    | SCOMC        | _   | SCOM | Software controlled 1/2 bias LCD COM                       |

| PB4,PB5          | PB4,PB5  | PBPU         | ST  | CMOS | General purpose I/O. Register enabled pull-up              |

| PB6/SCSA         | PB6      | PBPU         | ST  | CMOS | General purpose I/O. Register enabled pull-up              |

| 1 B0/3C3A        | SCSA     | _            | ST  | _    | SPI Slave Select                                           |

| PB7/SCKA         | PB7      | PBPU         | ST  | CMOS | General purpose I/O. Register enabled pull-up              |

| 1 BHOOKA         | SCKA     | _            | ST  |      | SPI Serial Clock                                           |

| PC0/AN4          | PC0      | PCPU         | ST  | CMOS | General purpose I/O. Register enabled pull-up.             |

| 1 00///114       | AN4      | ANCSR0       | AN  | _    | A/D channel 4                                              |

| PC1/AN5          | PC1      | PCPU         | ST  | CMOS | General purpose I/O. Register enabled pull-up.             |

| I O II/AINO      | AN5      | ANCSR0       | AN  | _    | A/D channel 5                                              |

| PC2/PWM2         | PC2      | PCPU         | ST  |      | General purpose I/O. Register enabled pull-up.             |

| 1 021 VVIVIZ     | PWM2     | CTRL2        | _   |      | PWM output                                                 |

| PC3/PWM1         | PC3      | PCPU         | ST  |      | General purpose I/O. Register enabled pull-up.             |

| . 50/1 **!!!!    | PWM1     | CTRL0        | _   |      | PWM output                                                 |

| PC4/XT2          | PC4      | PCPU         | ST  |      | General purpose I/O. Register enabled pull-up.             |

| 1 07///12        | XT2      | CO           | _   | LXT  | Low frequency crystal pin                                  |

| PC5/XT1          | PC5      | PCPU         | ST  |      | General purpose I/O. Register enabled pull-up.             |

| 1 00///11        | XT1      | CO           | _   | LXT  | Low frequency crystal pin                                  |

| Pin Name    | Function | OPT    | I/T | O/T  | Descriptions                                    |

|-------------|----------|--------|-----|------|-------------------------------------------------|

|             | PC6      | PCPU   | ST  | CMOS | General purpose I/O. Register enabled pull-up . |

| PC6/AN6     | AN6      | ANCSR0 | AN  | _    | A/D channel 6                                   |

|             | PC7      | PCPU   | ST  | CMOS | General purpose I/O. Register enabled pull-up.  |

| PC7/AN7     | AN7      | ANCSR0 | AN  | _    | A/D channel 7                                   |

|             | PD0      | PDPU   | ST  | CMOS | General purpose I/O. Register enabled pull-up . |

| PD0/TC2     | TC2      | _      | ST  | _    | External Timer 2 clock input                    |

|             | PD1      | PDPU   | ST  | CMOS | General purpose I/O. Register enabled pull-up . |

| PD1/PWM3    | PWM3     | CTRL2  | _   |      | PWM output                                      |

| PD2         | PD2      | PDPU   | ST  | CMOS | General purpose I/O. Register enabled pull-up   |

| DD0/D011/   | PD3      | PDPU   | ST  |      | General purpose I/O. Register enabled pull-up . |

| PD3/PCLK    | PCLK     | _      | _   |      | Peripheral Clock output                         |

| DD 1/200    | PD4      | PDPU   | ST  |      | General purpose I/O. Register enabled pull-up . |

| PD4/SCS     | SCS      | _      | ST  |      | SPI Slave Select                                |

|             | PD5      | PDPU   | ST  | CMOS | General purpose I/O. Register enabled pull-up.  |

| PD5/SCK/SCL | SCK      | _      | ST  | CMOS | SPI Serial Clock                                |

|             | SCL      | _      | ST  | NMOS | I <sup>2</sup> C Clock                          |

|             | PD6      | PDPU   | ST  | CMOS | General purpose I/O. Register enabled pull-up.  |

| PD6/SDI/SDA | SDI      | _      | ST  | _    | SPI Data input                                  |

|             | SDA      | _      | ST  | NMOS | I <sup>2</sup> C Data                           |

| DD7/0D0     | PD7      | PDPU   | ST  | CMOS | General purpose I/O. Register enabled pull-up.  |

| PD7/SDO     | SDO      | _      | _   | CMOS | SPI Data output                                 |

| DECAMO      | PE0      | PEPU   | ST  | CMOS | General purpose I/O. Register enabled pull-up.  |

| PE0/AN8     | AN8      | ANCSR1 | AN  | _    | A/D channel 8                                   |

| DE4/ANO     | PE1      | PEPU   | ST  | CMOS | General purpose I/O. Register enabled pull-up.  |

| PE1/AN9     | AN9      | ANCSR1 | AN  | _    | A/D channel 9                                   |

| DEO/ANIAO   | PE2      | PEPU   | ST  | CMOS | General purpose I/O. Register enabled pull-up.  |

| PE2/AN10    | AN10     | ANCSR1 | AN  | _    | A/D channel 10                                  |

| DEC/ANIAA   | PE3      | PEPU   | ST  | CMOS | General purpose I/O. Register enabled pull-up.  |

| PE3/AN11    | AN11     | ANCSR1 | AN  | _    | A/D channel 11                                  |

| PE4/AN12    | PE4      | PEPU   | ST  | CMOS | General purpose I/O. Register enabled pull-up.  |

| PE4/AN12    | AN12     | ANCSR1 | AN  | _    | A/D channel 12                                  |

| PE5/AN13    | PE5      | PEPU   | ST  | CMOS | General purpose I/O. Register enabled pull-up.  |

| PESIANTS    | AN13     | ANCSR1 | AN  |      | A/D channel 13                                  |

| PE6/AN14    | PE6      | PEPU   | ST  | CMOS | General purpose I/O. Register enabled pull-up.  |

| PEO/AN14    | AN14     | ANCSR1 | AN  |      | A/D channel 14                                  |

| PE7/AN15    | PE7      | PEPU   | ST  | CMOS | General purpose I/O. Register enabled pull-up.  |

| PETIANTS    | AN15     | ANCSR1 | AN  |      | A/D channel 15                                  |

| PF0/SDOA    | PF0      | PFPU   | ST  | CMOS | General purpose I/O. Register enabled pull-up.  |

| PF0/SDOA    | SDOA     | _      | _   |      | SPI Data output                                 |

| PF1/SDIA    | PF1      | PFPU   | ST  | CMOS | General purpose I/O. Register enabled pull-up . |

| I I I/SDIA  | SDIA     | _      | ST  | _    | SPI Data input                                  |

| PF2~PF7     | PFn      | PFPU   | ST  | CMOS | General purpose I/O. Register enabled pull-up . |

| PG0~PG7     | PGn      | PGPU   | ST  |      | General purpose I/O. Register enabled pull-up . |

| PH0~PH5     | PHn      | PHPU   | ST  | CMOS | General purpose I/O. Register enabled pull-up . |

| VDD         | VDD      | _      | PWR | _    | Power supply                                    |

| VSS         | VSS      | _      | PWR | _    | Ground                                          |

Note: I/T: Input type; O/T: Output type

OPT: Optional by configuration option (CO) or register option

PWR: Power; CO: Configuration option

ST: Schmitt Trigger input; CMOS: CMOS output;

AN: Analog input or output

SCOM: Software controlled LCD COM HXT: High frequency crystal oscillator LXT: Low frequency crystal oscillator

Rev. 1.00 6 January 26, 2011

### **Absolute Maximum Ratings**

| Supply Voltage          | $V_{SS}$ -0.3V to $V_{SS}$ +6.0V |

|-------------------------|----------------------------------|

| Input Voltage           | $V_{SS}$ -0.3V to $V_{DD}$ +0.3V |

| I <sub>OL</sub> Total   | 100mA                            |

| Total Power Dissipation | 500mW                            |

| Storage Temperature     |                                  |

| Operating Temperature   |                                  |

| I <sub>OH</sub> Total   | -100mA                           |

Note: These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

### **D.C.** Characteristics

Ta=25°C

| Or made = 1       | Parameter                                    |    | Test Conditions                                          | D.d.i.o.           | Torre | Man                | I I m i 4 |

|-------------------|----------------------------------------------|----|----------------------------------------------------------|--------------------|-------|--------------------|-----------|

| Symbol            | Parameter                                    |    | Conditions                                               | Min.               | Тур.  | Max.               | Unit      |

|                   |                                              |    | f <sub>SYS</sub> =4MHz                                   | 2.2                | _     | 5.5                | V         |

| V <sub>DD</sub>   | Operating Voltage                            | _  | f <sub>SYS</sub> =8MHz                                   | 3.0                | _     | 5.5                | V         |

|                   |                                              |    | f <sub>SYS</sub> =12MHz                                  | 4.5                | _     | 5.5                | V         |

| I <sub>DD1</sub>  | Operating Current                            | 3V | No load, f <sub>sys</sub> =4MHz                          | _                  | 8.0   | 1.2                | mA        |

| וטטי              | (HXT, HIRC, ERC)                             | 5V | 140 load, 1575-411112                                    | _                  | 1.5   | 2.25               | mA        |

| I <sub>DD2</sub>  | Operating Current                            | 3V | No load, f <sub>sys</sub> =8MHz                          |                    | 1.4   | 2.1                | mA        |

| 1002              | (HXT, HIRC, ERC)                             | 5V | 10000, 1010 011112                                       | _                  | 2.8   | 4.2                | mA        |

| I <sub>DD3</sub>  | Operating Current (HXT, HIRC, ERC)           | 5V | No load, f <sub>SYS</sub> =12MHz                         | _                  | 4     | 6                  | mA        |

|                   |                                              | 3V | No load, f <sub>SYS</sub> =32768Hz<br>(LXT on OSC1/OSC2, | _                  | 5     | 10                 | μΑ        |

| I <sub>DD4</sub>  | Operating Current<br>(HIRC + LXT, Slow Mode) | 5V | LVR disabled, LXTLP=1)                                   | _                  | 12    | 24                 | μΑ        |

| 1004              |                                              | 3V | No load, f <sub>SYS</sub> =32768Hz<br>(LXT on XT1/XT2,   | _                  | 5     | 10                 | μA        |

|                   |                                              | 5V | LVR disabled, LXTLP=1)                                   | _                  | 10    | 20                 | μΑ        |

| I <sub>STB1</sub> | Standby Current                              | 3V | No load, system HALT                                     |                    |       | 5                  | μΑ        |

| 13161             | (LIRC On, LXT Off)                           | _  |                                                          | _                  |       | 10                 | μΑ        |

| I <sub>STB2</sub> | Standby Current                              | 3V | No load, system HALT                                     |                    |       | 1                  | μΑ        |

| 10152             | (LIRC Off, LXT Off)                          | 5V |                                                          | _                  |       | 2                  | μΑ        |

|                   |                                              | 3V | No load, system HALT                                     |                    |       | 5                  | μΑ        |

| I <sub>STB3</sub> | Standby Current                              | 5V | (LXT on OSC1/OSC2)                                       | _                  |       | 10                 | μΑ        |

| 0.50              | (LIRC Off, LXT On, LXTLP=1)                  | 3V | No load, system HALT                                     | _                  | _     | 3                  | μΑ        |

|                   |                                              | 5V | (LXT on XT1/XT2)                                         | _                  | _     | 5                  | μΑ        |

| V <sub>IL1</sub>  | Input Low Voltage for I/O, TCn and INT       | _  | _                                                        | 0                  | _     | 0.3V <sub>DD</sub> | V         |

| V <sub>IH1</sub>  | Input High Voltage for I/O, TCn and INT      | _  | _                                                        | 0.7V <sub>DD</sub> | _     | V <sub>DD</sub>    | V         |

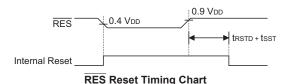

| V <sub>IL2</sub>  | Input Low Voltage (RES)                      | _  |                                                          | 0                  | 1     | 0.4V <sub>DD</sub> | V         |

| V <sub>IH2</sub>  | Input High Voltage (RES)                     | -  | _                                                        | 0.9V <sub>DD</sub> | _     | V <sub>DD</sub>    | ٧         |

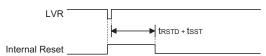

| V <sub>LVR1</sub> | Low Voltage Reset 1                          | _  | V <sub>LVR</sub> =4.2V                                   | 3.98               | 4.2   | 4.42               | V         |

| V <sub>LVR2</sub> | Low Voltage Reset 2                          | _  | V <sub>LVR</sub> =3.15V                                  | 2.98               | 3.15  | 3.32               | V         |

| V <sub>LVR3</sub> | Low Voltage Reset 3                          | _  | V <sub>LVR</sub> =2.1V                                   | 1.98               | 2.1   | 2.22               | V         |

| Cumah al          | Donomoton                              |                 | Test Conditions                     | Min   | T     | Mari  | 11       |

|-------------------|----------------------------------------|-----------------|-------------------------------------|-------|-------|-------|----------|

| Symbol            | Parameter                              | $V_{\text{DD}}$ | Conditions                          | Min.  | Тур.  | Max.  | Unit     |

| V <sub>LVD1</sub> | Low Voltage Detector Voltage 1         | _               | V <sub>LVD</sub> = 4.4 V            | 4.12  | 4.4   | 4.70  | V        |

| $V_{\text{LVD2}}$ | Low Voltage Detector Voltage 2         | _               | V <sub>LVD</sub> = 3.3 V            | 3.12  | 3.3   | 3.50  | V        |

| $V_{\text{LVD2}}$ | Low Voltage Detector Voltage 3         | _               | V <sub>LVD</sub> = 2.2 V            | 2.08  | 2.2   | 2.32  | V        |

|                   | I/O Port Sink Current                  | 3V              | Voi =0.1Vpp                         | 4     | 8     | _     | mA       |

| I <sub>OL1</sub>  | (PA, PB, PC, PD, PE, PF, PG, PH)       | 5V              | VOL=U.IVDD                          | 10    | 20    | _     | mA       |

|                   | I/O Port Source Current                | 3V              | V =0.0V                             | -2    | -4    | _     | mA       |

| Іон               |                                        | 5V              | V <sub>OH</sub> =0.9V <sub>DD</sub> | -5    | -10   | _     | mA       |

| I <sub>OL2</sub>  | PA7 Sink Current                       | 5V              | V <sub>OL</sub> =0.1V <sub>DD</sub> | 2     | 3     | _     | mA       |

| D                 | Dull high Posistance                   | 3V              | _                                   | 20    | 60    | 100   | kΩ       |

| R <sub>PH</sub>   | Pull-high Resistance                   | 5V              | _                                   | 10    | 30    | 50    | kΩ       |

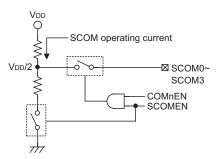

|                   |                                        |                 | SCOMC, ISEL[1:0]=00                 | 17.5  | 25.0  | 32.5  | μΑ       |

| ١,                | SCOM Operating Current                 | 5V              | SCOMC, ISEL[1:0]=01                 | 35    | 50    | 65    | μΑ       |

| I <sub>SCOM</sub> | SCOM Operating Current                 | 50              | SCOMC, ISEL[1:0]=10                 | 70    | 100   | 130   | μΑ       |

|                   |                                        |                 | SCOMC, ISEL[1:0]=11                 | 140   | 200   | 260   | μΑ       |

| V <sub>SCOM</sub> | V <sub>DD</sub> /2 Voltage for LCD COM | 5V              | No load                             | 0.475 | 0.500 | 0.525 | $V_{DD}$ |

Note: The standby current ( $I_{STB1} \sim I_{STB3}$ ) and  $I_{DD4}$  are measured with all I/O pins in input mode and tied to  $V_{DD}$ .

Rev. 1.00 8 January 26, 2011

### A.C. Characteristics

Ta=25°C

| Counch al          | Domonoston                     |                        | Test Conditions           | Min  | T     | Max.   | Unit             |

|--------------------|--------------------------------|------------------------|---------------------------|------|-------|--------|------------------|

| Symbol             | Parameter                      | <b>V</b> <sub>DD</sub> | Conditions                | Min. | Тур.  | IVIAA. | Unit             |

|                    |                                |                        | 2.2V~5.5V                 | 32   | _     | 4000   | kHz              |

| f <sub>SYS</sub>   | System Clock                   | _                      | 3.0V~5.5V                 | 32   | _     | 8000   | kHz              |

|                    |                                |                        | 4.5V~5.5V                 | 32   | _     | 12000  | kHz              |

|                    |                                | 3V/5V                  | Ta=25°C                   | -2%  | 4     | +2%    | MHz              |

|                    |                                | 3V/5V                  | Ta=25°C                   | -2%  | 8     | +2%    | MHz              |

|                    |                                | 5V                     | Ta=25°C                   | -2%  | 12    | +2%    | MHz              |

|                    |                                | 3V/5V                  | Ta=0~70°C                 | -5%  | 4     | +5%    | MHz              |

|                    |                                | 3V/5V                  | Ta=0~70°C                 | -5%  | 8     | +5%    | MHz              |

|                    |                                | 5V                     | Ta=0~70°C                 | -5%  | 12    | +5%    | MHz              |

| _                  | Cycham Clask (LUDC)            | 2.2V~3.6V              | Ta=0~70°C                 | -8%  | 4     | +8%    | MHz              |

| f <sub>HIRC</sub>  | System Clock (HIRC)            | 3.0V~5.5V              | Ta=0~70°C                 | -8%  | 4     | +8%    | MHz              |

|                    |                                | 3.0V~5.5V              | Ta=0~70°C                 | -8%  | 8     | +8%    | MHz              |

|                    |                                | 4.5V~5.5V              | Ta=0~70°C                 | -8%  | 12    | +8%    | MHz              |

|                    |                                | 2.2V~3.6V              | Ta=-40°C~85°C             | -12% | 4     | +12%   | MHz              |

|                    |                                | 3.0V~5.5V              | Ta=-40°C~85°C             | -12% | 4     | +12%   | MHz              |

|                    |                                | 3.0V~5.5V              | Ta=-40°C~85°C             | -12% | 8     | +12%   | MHz              |

|                    |                                | 4.5V~5.5V              | Ta=-40°C~85°C             | -12% | 12    | +12%   | MHz              |

|                    | System Clock (ERC)             | 5V                     | Ta=25°C, R=120KΩ*         | -2%  | 4     | +2%    | MHz              |

| _                  |                                | 5V                     | Ta=0~70°C, R=120KΩ*       | -5%  | 4     | +5%    | MHz              |

| f <sub>ERC</sub>   |                                | 5V                     | Ta=-40°C~85°C, R=120KΩ*   | -7%  | 4     | +7%    | MHz              |

|                    |                                | 2.2V~5.5V              | Ta=-40°C~85°C, R=120KΩ*   | -11% | 4     | +11%   | MHz              |

| f <sub>LXT</sub>   | System Clock (LXT)             | _                      | _                         | _    | 32768 | _      | Hz               |

|                    |                                |                        | 2.2V~5.5V                 | 0    | _     | 4000   | kHz              |

| t <sub>TIMER</sub> | Timer Input Frequency (TCn)    | _                      | 3.0V~5.5V                 | 0    | _     | 8000   | kHz              |

|                    | (1011)                         |                        | 4.5V~5.5V                 | 0    | _     | 12000  | kHz              |

| £                  | LIDC Oscillator                | 3V                     | _                         | 5    | 10    | 15     | kHz              |

| f <sub>LIRC</sub>  | LIRC Oscillator                | 5V                     | _                         | 6.5  | 13    | 19.5   | kHz              |

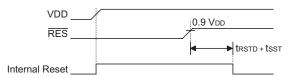

| t <sub>RES</sub>   | External Reset Low Pulse Width | _                      | _                         | 1    | _     | _      | μs               |

|                    |                                |                        | For HXT/LXT               | _    | 1204  | _      | t <sub>sys</sub> |

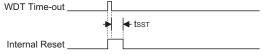

| t <sub>SST</sub>   | System Start-up time Period    | _                      | For ERC/IRC               | _    | 2     | _      | tsys             |

|                    |                                |                        | (By configuration option) |      | 1024  | _      | tsys             |

| t <sub>INT</sub>   | Interrupt Fulse Width          | _                      | _                         | 1    | _     | _      | μs               |

| t <sub>LVR</sub>   | Low Voltage Width to Reset     | _                      | _                         | 0.25 | 1     | 2      | ms               |

| RESTD              | Reset Delay Time               | _                      | _                         |      | 100   | _      | ms               |

Note: 1.  $t_{SYS}=1/f_{SYS}$

$<sup>2.*</sup>For\ f_{REC}$ , as the resistor tolerance will influence the frequency a percision resistor is recommended.

<sup>3.</sup> To maintain the accuracy of the internal HIRC oscillator frequency, a  $0.1\mu F$  decoupling capacitor should be connected between VDD and VSS and located as close to the device as possible.

### **ADC Characteristics**

Ta=25°C

| Symbol   | Parameter                      |                 | Test Conditions           | Min.    | Тур. | Max.   | Unit  |

|----------|--------------------------------|-----------------|---------------------------|---------|------|--------|-------|

| Syllibol | Farameter                      | $V_{\text{DD}}$ | Conditions                | IVIIII. | iyp. | IVIAX. | Oilit |

| DNL      | A/C Differential New Linearity |                 | t. =0 5uo                 | -2      |      | 2      | LSB   |

| DINL     | A/C Differential Non-Linearity | 5V              | -t <sub>AD</sub> =0.5μs   | -2      | _    | _      | LOB   |

| INL      | ADO lete seel New Line seite   |                 | h -0.5                    | 4       |      | 4      | LSB   |

| IINL     | ADC Integral Non-Linearity     | 5V              | 5V t <sub>AD</sub> =0.5μs | -4      | _    | 4      | LOB   |

| L        | Additional Power Consumption   | 3V              |                           | _       | 0.5  | 0.75   | mA    |

| IADC     | if A/D Converter is Used       | 5V              | _                         | _       | 1.0  | 1.5    | mA    |

### **DAC Electrical Characteristics**

| Cumbal           | Parameter             |                            | Test Conditions                                  | Min.    | Tim  | Max.   | Unit     |

|------------------|-----------------------|----------------------------|--------------------------------------------------|---------|------|--------|----------|

| Symbol           | Parameter             | V <sub>DD</sub> Conditions |                                                  | IVIIII. | Тур. | IVIAX. | Unit     |

| V <sub>DAC</sub> | DAC operating voltage | _                          | _                                                | 2.4     | _    | _      | V        |

| lα               | DAC quiescent current | 5V                         | Code= 0000H<br>V <sub>OL</sub> =00H              | _       | 2    | 3      | mA       |

| I <sub>DAC</sub> | DAC operating current | 5V                         | 1 kHz sin wave, full-scale<br>( 8K sample rate ) | _       | 3    | 4.5    | mA       |

| RES              | Resolution            | _                          | _                                                | _       | _    | 12     | bit      |

| Vo               | Output Voltage Level  | _                          | _                                                | 0.01    | _    | 0.99   | $V_{DD}$ |

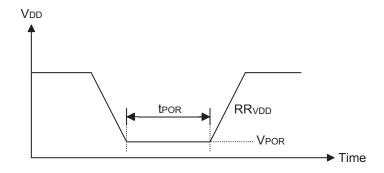

### **Power-on Reset Characteristics**

Ta=25°C

| Symbol            | Parameter                                                                 |                        | Test Conditions | Min.    | T    | Mary | Unit  |

|-------------------|---------------------------------------------------------------------------|------------------------|-----------------|---------|------|------|-------|

| Syllibol          | Farameter                                                                 | <b>V</b> <sub>DD</sub> | Conditions      | IVIIII. | Тур. | Max. | Ullit |

| V <sub>POR</sub>  | V <sub>DD</sub> Start Voltage to Ensure<br>Power-on Reset                 | _                      | _               | _       | _    | 100  | mV    |

| RRV <sub>DD</sub> | V <sub>DD</sub> Raising Rate to Ensure<br>Power-on Reset                  | _                      | _               | 0.035   | _    | _    | V/ms  |

|                   | Minimum Time for $V_{DD}$ to remain at $V_{POR}$ to ensure Power-on Reset | _                      | _               | 1       | _    | _    | ms    |

Rev. 1.00 January 26, 2011

### **System Architecture**

A key factor in the high-performance features of the Holtek range of microcontrollers is attributed to the internal system architecture. The range of devices take advantage of the usual features found within RISC microcontrollers providing increased speed of operation and enhanced performance. The pipelining scheme is implemented in such a way that instruction fetching and instruction execution are overlapped, hence instructions are effectively executed in one cycle, with the exception of branch or call instructions. An 8-bit wide ALU is used in practically all operations of the instruction set. It carries out arithmetic operations, logic operations, rotation, increment, decrement, branch decisions, etc. The internal data path is simplified by moving data through the Accumulator and the ALU. Certain internal registers are implemented in the Data Memory and can be directly or indirectly addressed. The simple addressing methods of these registers along with additional architectural features ensure that a minimum of external components is required to provide a functional I/O and A/D control system with maximum reliability and flexibility.

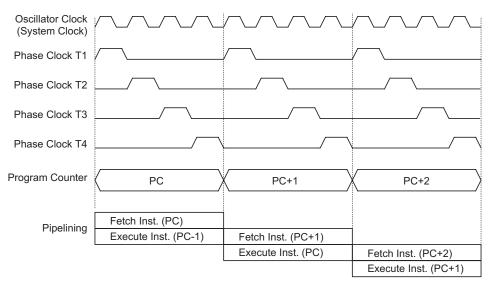

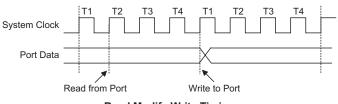

#### **Clocking and Pipelining**

The main system clock, derived from either a Crystal/Resonator or RC oscillator is subdivided into four internally generated non-overlapping clocks, T1~T4. The Program Counter is incremented at the beginning of the T1 clock during which time a new instruction is fetched. The remaining T2~T4 clocks carry out the decoding and execution functions. In this way, one T1~T4 clock cycle forms one instruction cycle. Although the fetching and execution of instructions takes place in consecutive instruction cycles, the pipelining structure of the microcontroller ensures that instructions are effectively executed in one instruction cycle. The exception to this are instructions where the contents of the Program Counter are changed, such as subroutine calls or jumps, in which case the instruction will take one more instruction cycle to execute.

For instructions involving branches, such as jump or call instructions, two instruction cycles are required to complete instruction execution. An extra cycle is required as the program takes one cycle to first obtain the actual jump or call address and then another cycle to actually execute the branch. The requirement for this extra cycle should be taken into account by programmers in timing sensitive applications.

**System Clocking and Pipelining**

| 1 |        | MOV A,[12H] |  |

|---|--------|-------------|--|

| 2 |        | CALL DELAY  |  |

| 3 |        | CPL [12H]   |  |

| 4 |        | :           |  |

| 5 |        | :           |  |

| 6 | DELAY: | NOP         |  |

| Fetch Inst. 1 | Execute Inst. 1 |                 |                |                 |

|---------------|-----------------|-----------------|----------------|-----------------|

|               | Fetch Inst. 2   | Execute Inst. 2 |                |                 |

|               |                 | Fetch Inst. 3   | Flush Pipeline |                 |

|               |                 |                 | Fetch Inst. 6  | Execute Inst. 6 |

|               |                 | ,               |                | Fetch Inst. 7   |

Instruction Fetching

### **Program Counter**

During program execution, the Program Counter is used to keep track of the address of the next instruction to be executed. It is automatically incremented by one each time an instruction is executed except for instructions, such as "JMP" or "CALL" that demand a jump to a non-consecutive Program Memory address. Note that the Program Counter width varies with the Program Memory capacity depending upon which device is selected. However, it must be noted that only the lower 8 bits, known as the Program Counter Low Register, are directly addressable by user.

When executing instructions requiring jumps to non-consecutive addresses such as a jump instruction, a subroutine call, interrupt or reset, etc., the microcontroller manages program control by loading the required address into the Program Counter. For conditional skip instructions, once the condition has been met, the next instruction, which has already been fetched during the present instruction execution, is discarded and a dummy cycle takes its place while the correct instruction is obtained.

|           | Program Counter              |              |  |  |  |

|-----------|------------------------------|--------------|--|--|--|

| DEVICE    | Program Counter<br>High Byte | PCL Register |  |  |  |

| HT46R068B | PC13~PC8                     | DCL7, DCL0   |  |  |  |

| HT46R069B | PC14~PC8                     | PCL7~PCL0    |  |  |  |

The lower byte of the Program Counter, known as the Program Counter Low register or PCL, is available for program control and is a readable and writeable register. By transferring data directly into this register, a short program jump can be executed directly, however, as only this low byte is available for manipulation, the jumps are limited to the present page of memory, that is 256 locations. When such program jumps are executed it should also be noted that a dummy cycle will be inserted.

The lower byte of the Program Counter is fully accessible under program control. Manipulating the PCL might cause program branching, so an extra cycle is needed to pre-fetch. Further information on the PCL register can be found in the Special Function Register section.

Rev. 1.00 12 January 26, 2011

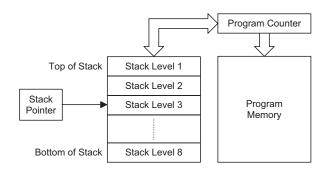

#### **Stack**

This is a special part of the memory which is used to save the contents of the Program Counter only. The stack is neither part of the Data or Program Memory space, and is neither readable nor writeable. The activated level is indexed by the Stack Pointer, SP, and is neither readable nor writeable. At a subroutine call or interrupt acknowledge signal, the contents of the Program Counter are pushed onto the stack. At the end of a subroutine or an interrupt routine, signaled by a return instruction, RET or RETI, the Program Counter is restored to its previous value from the stack. After a device reset, the Stack Pointer will point to the top of the stack.

| Device                 | Stack Levels |

|------------------------|--------------|

| HT46R068B<br>HT46R069B | 8            |

If the stack is full and an enabled interrupt takes place, the interrupt request flag will be recorded but the acknowledge signal will be inhibited. When the Stack Pointer is decremented, by RET or RETI, the interrupt will be serviced. This feature prevents stack overflow allowing the programmer to use the structure more easily. However, when the stack is full, a CALL subroutine instruction can still be executed which will result in a stack overflow. Precautions should be taken to avoid such cases which might cause unpredictable program branching.

#### Arithmetic and Logic Unit - ALU

The arithmetic-logic unit or ALU is a critical area of the microcontroller that carries out arithmetic and logic operations of the instruction set. Connected to the main microcontroller data bus, the ALU receives related instruction codes and performs the required arithmetic or logical operations after which the result will be placed in the specified register. As these ALU calculation or operations may result in carry, borrow or other status changes, the status register will be correspondingly updated to reflect these changes. The ALU supports the following functions:

- Arithmetic operations: ADD, ADDM, ADC, ADCM, SUB, SUBM, SBC, SBCM, DAA

- Logic operations: AND, OR, XOR, ANDM, ORM, XORM, CPL, CPLA

- Rotation RRA, RR, RRCA, RRC, RLA, RL, RLCA, RLC

- Increment and Decrement INCA, INC, DECA, DEC

- Branch decision, JMP, SZ, SZA, SNZ, SIZ, SDZ, SIZA, SDZA, CALL, RET, RETI

Rev. 1.00 13 January 26, 2011

### **Program Memory**

The Program Memory is the location where the user code or program is stored. The device is supplied with One-Time Programmable, OTP, memory where users can program their application code into the device. By using the appropriate programming tools, OTP devices offer users the flexibility to freely develop their applications which may be useful during debug or for products requiring frequent upgrades or program changes.

#### **Structure**

The Program Memory has a capacity of 16Kx16/32Kx16. The Program Memory is addressed by the Program Counter and also contains data, table information and interrupt entries. Table data, which can be setup in any location within the Program Memory, is addressed by separate table pointer registers.

| Device    | Capacity | Banks |  |  |

|-----------|----------|-------|--|--|

| HT46R068B | 16Kx16   | 0,1   |  |  |

| HT46R069B | 32Kx16   | 0~3   |  |  |

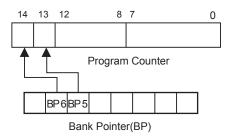

The devices have their Program Memory divided into a number of banks which are selected using the Bank Pointer register. The HT46R068B has its Program Memory divided into two Banks, Bank 0 and Bank 1. The required Bank is selected using Bit 5 of the BP Register. The HT46R069B has its Program Memory divided into four banks, from Bank0 to Bank3. The required Bank is selected using Bit 5 and Bit 6 of the BP Register.

Rev. 1.00 14 January 26, 2011

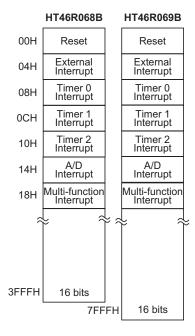

#### **Special Vectors**

Within the Program Memory, certain locations are reserved for special usage such as reset and interrupts.

#### Reset Vector

This vector is reserved for use by the device reset for program initialisation. After a device reset is initiated, the program will jump to this location and begin execution.

#### • External interrupt vector

This vector is used by the external interrupt. If the external interrupt pin on the device receives an edge transition, the program will jump to this location and begin execution if the external interrupt is enabled and the stack is not full. The external interrupt active edge transition type, whether high to low, low to high or both is specified in the CTRL1 register.

#### • Timer/Event 0/1/2 counter interrupt vector

This internal vector is used by the Timer/Event Counters. If a Timer/Event Counter overflow occurs, the program will jump to its respective location and begin execution if the associated Timer/Event Counter interrupt is enabled and the stack is not full.

#### • Multi-function interrupt vector

The Multi-function Interrupt vector is shared by several internal functions: a Time Base overflow, an SPI/I<sup>2</sup>C or SPIA data transfer completion. The program will jump to this location and begin execution if the relevant interrupt is enabled and the stack is not full.

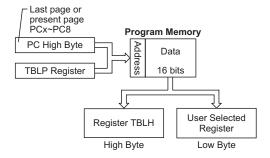

#### Look-up Table

Any location within the Program Memory can be defined as a look-up table where programmers can store fixed data. To use the look-up table, the table pointer must first be setup by placing the lower order address of the look up data to be retrieved in the table pointer register, TBLP. This register defines the lower 8-bit address of the look-up table.

After setting up the table pointer, the table data can be retrieved from the current Program Memory page or last Program Memory page using the "TABRDC[m]" or "TABRDL[m]" instructions, respectively. When these instructions are executed, the lower order table byte from the Program

Memory will be transferred to the user defined Data Memory register [m] as specified in the instruction. The higher order table data byte from the Program Memory will be transferred to the TBLH special register. Any unused bits in this transferred higher order byte will be read as "0".

The following diagram illustrates the addressing/data flow of the look-up table:

### **Table Program Example**

The accompanying example shows how the table pointer and table data is defined and retrieved from the device. This example uses raw table data located in the last page which is stored there using the ORG statement. The value at this ORG statement is "7F00H" which refers to the start address of the last page within the 32K Program Memory of the microcontrollers. The table pointer is setup here to have an initial value of "06H". This will ensure that the first data read from the data table will be at the Program Memory address "7F06H" or 6 locations after the start of the last page. Note that the value for the table pointer is referenced to the first address of the present page if the "TABRDC [m]" instruction is being used. The high byte of the table data which in this case is equal to zero will be transferred to the TBLH register automatically when the "TABRDL [m]" instruction is executed.

Because the TBLH register is a read-only register and cannot be restored, care should be taken to ensure its protection if both the main routine and Interrupt Service Routine use the table read instructions. If using the table read instructions, the Interrupt Service Routines may change the value of TBLH and subsequently cause errors if used again by the main routine. As a rule it is recommended that simultaneous use of the table read instructions should be avoided. However, in situations where simultaneous use cannot be avoided, the interrupts should be disabled prior to the execution of any main routine table-read instructions. Note that all table related instructions require two instruction cycles to complete their operation.

| Instruction(s) |      | Table Location |      |      |      |     |     |    |    |    |    |    |    |    |    |

|----------------|------|----------------|------|------|------|-----|-----|----|----|----|----|----|----|----|----|

| Instruction(s) | b14  | b13            | b12  | b11  | b10  | b9  | b8  | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| TABRDC [m]     | PC14 | PC13           | PC12 | PC11 | PC10 | PC9 | PC8 | @7 | @6 | @5 | @4 | @3 | @2 | @1 | @0 |

| TABRDL [m]     | 1    | 1              | 1    | 1    | 1    | 1   | 1   | @7 | @6 | @5 | @4 | @3 | @2 | @1 | @0 |

Note: PC14~PC8: Current Program Counter bits

@7~@0: Table Pointer TBLP bits

For the HT46R068B, the Table address location is 14 bits, i.e. from b13~b0 For the HT46R069B, the Table address location is 15 bits, i.e. from b14~b0

Rev. 1.00 16 January 26, 2011

#### **Table Read Program Example:**

```

db ?

tempreg1

; temporary register #1

db ?

tempreg2

; temporary register #2

mov a,

060h

mov bp,

а

; select the last bank of prog. memory

06h

; initialise table pointer - note that this address

mov a,

; is referenced

mov tblp,a

; to the last page or present page

tabrdl

tempreg1

; transfers value in table referenced by table pointer

; to tempregl

; data at prog. memory address "7F06" transferred to

; tempreg1 and TBLH

dec tblp

; reduce value of table pointer by one

tabrdl

tempreg2

; transfers value in table referenced by table pointer

; to tempreg2

; data at prog.memory address "7F06" transferred to

; tempreg2 and TBLH

; in this example the data "1AH" is transferred to

; tempreg1 and data "OFH" to register tempreg2

; the value "OOH" will be transferred to the high byt

; register TBLH

org7F00h

; sets initial address of last page

dc 00Ah, 00Bh, 00Ch, 00Dh, 00Eh, 00Fh, 01Ah, 01Bh

```

### **Data Memory**

The Data Memory is a volatile area of 8-bit wide RAM internal memory and is the location where temporary information is stored.

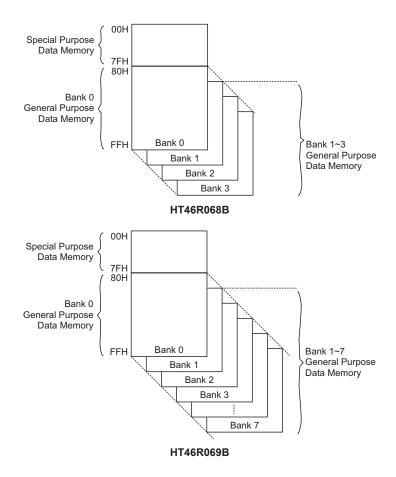

#### **Structure**

Divided into two sections, the first of these is an area of RAM where special function registers are located. These registers have fixed locations and are necessary for correct operation of the device. Many of these registers can be read from and written to directly under program control, however, some remain protected from user manipulation. The second area of Data Memory is reserved for general purpose use. All locations within this area are read and write accessible under program control.

| Device    | Capacity | Banks |  |  |

|-----------|----------|-------|--|--|

| HT46R068B | 512x8    | 0~3   |  |  |

| HT46R069B | 1024x8   | 0~7   |  |  |

The two sections of Data Memory, the Special Purpose and General Purpose Data Memory are located at consecutive locations. All are implemented in RAM and are 8 bits wide but the length of each memory section is dictated by the type of microcontroller chosen. The start address of the Data Memory for all devices is the address "00H".

All microcontroller programs require an area of read/write memory where temporary data can be stored and retrieved for use later. It is this area of RAM memory that is known as General Purpose Data Memory. This area of Data Memory is fully accessible by the user program for both read and write operations. By using the "SET [m].i" and "CLR [m].i" instructions individual bits can be set or reset under program control giving the user a large range of flexibility for bit manipulation in the Data Memory.

For some devices, the Data Memory is subdivided into several banks, which are selected using a Bank Pointer. Only data in Bank 0 can be directly addressed, data in Bank 1~Bank 7 must be indirectly addressed.

Rev. 1.00 18 January 26, 2011

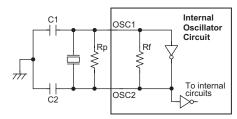

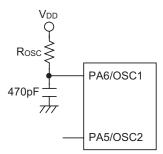

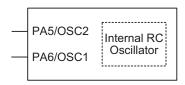

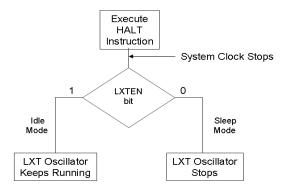

**Data Memory Structure**