# WTPB4A60SW

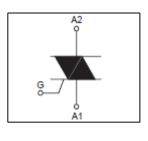

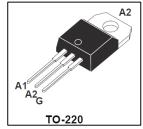

# **Bi-Directional Triode Thyristor**

### Features

- Repetitive Peak Off-State Voltage : 600V

- R.M.S On-State Current (IT(RMS)= 4 A)

- Low On-State Voltage (1.6V(Typ.) @ I<sub>™</sub>)

- High Commutation dv/dt

### **General Description**

Standard gate triggering Triac is suitable for direct coupling to TTL, HTL, CMOS and application such as various logic functions, low power AC switching applications, such as fan speed, small light controllers and home appliance equipment.

| Symbol              | Parameter                         | Condition                   |      | Ratings  | Units            |  |

|---------------------|-----------------------------------|-----------------------------|------|----------|------------------|--|

|                     | Repetitive Peak Off-State Voltage |                             |      | 600      | v                |  |

| I <sub>T(RMS)</sub> | R.M.S On-State Current            | T <sub>J</sub> = 110 °C     | C    |          |                  |  |

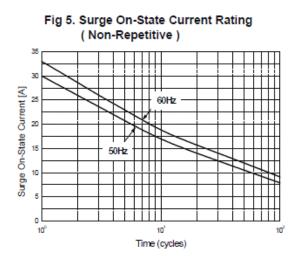

| I <sub>TSM</sub>    | Surge On-State Current            | One cycle, Peak value, non- | 50Hz | 30       |                  |  |

|                     |                                   | repetitive full cycle       | 60Hz | 31       | A                |  |

| l <sup>2</sup> t    | l <sup>2</sup> t                  |                             |      | 5.1      | A <sup>2</sup> s |  |

| P <sub>GM</sub>     | Peak Gate Power Dissipation       |                             |      | 5        | w                |  |

| P <sub>G(AV)</sub>  | Average Gate Power Dissipation    | T <sub>J</sub> = 125 °C     | 1    | w        |                  |  |

| I <sub>GM</sub>     | Peak Gate Current                 | T <sub>J</sub> = 125 °C     | 4.0  | А        |                  |  |

| V <sub>GM</sub>     | Peak Gate Voltage                 |                             |      | 7.0      | V                |  |

| TJ                  | Operating Junction Temperature    |                             |      | -40~+150 | °C               |  |

| T <sub>stg</sub>    | Storage Temperature               |                             |      | -40~+150 | °C               |  |

### Absolute Maximum Ratings (T\_= 25°C unless otherwise specified)

### **Thermal Characteristics**

| Symbol                | Parameter                                                   | Value | Units |

|-----------------------|-------------------------------------------------------------|-------|-------|

| $R_{	extsf{	heta}Jc}$ | Thermal Resistance Junction to Case(DC)                     | 2.6   | °C/W  |

| $R_{\theta JA}$       | R <sub>0JA</sub> Thermal Resistance Junction to Ambient(DC) |       | °C/W  |

### Electrical Characteristics (Tc=25°C unless otherwise noted)

| Symbol                             | Characteristics                                                                             |        |                      | Min | Тур. | Max | Unit |

|------------------------------------|---------------------------------------------------------------------------------------------|--------|----------------------|-----|------|-----|------|

|                                    | off-state leakage current $(V_{AK} = V_{DRM}/V_{RRM}$ Single phase, half wave)              |        | TJ=25℃               | -   | -    | 5   | μA   |

| I <sub>DRM</sub> /I <sub>RRM</sub> |                                                                                             |        | TJ=125<br>℃          | -   | -    | 1   | mA   |

| V <sub>TM</sub>                    | Forward "On" voltage (I <sub>T</sub> =5A, Inst. Measurement)                                |        | -                    | 1.2 | 1.6  | V   |      |

|                                    | Gate trigger current (continuous dc)<br>( $V_{AK}$ = 6 Vdc, RL = 10 $\Omega$ )              |        | T2+,G+               | -   | -    | 10  | mA   |

| I <sub>GT</sub>                    |                                                                                             |        | T2+,G-               | -   | -    | 10  |      |

|                                    |                                                                                             | Note:1 | T2-,G-               | -   | -    | 10  |      |

|                                    | Gate Trigger Voltage (Continuous dc) )<br>(V <sub>AK</sub> = 6 Vdc, RL = 10 $\Omega$ )<br>N |        | T2+,G+               | -   | -    | 1.5 | v    |

| $V_{\text{GT}}$                    |                                                                                             |        | T2+,G-               | -   | -    | 1.5 |      |

|                                    |                                                                                             | Note:1 | T2-,G-               | -   | -    | 1.5 |      |

| $V_{GD}$                           | Gate threshold Voltage $V_{D}=1/2V_{DRM}$ , RL = 3.3K $\Omega$                              |        | T <sub>J</sub> =125℃ | 0.2 | -    | -   | V    |

|                                    | Critical Rate of Rise of Off-State Voltage at Tj=125°C                                      |        |                      |     |      |     |      |

| dv/dt                              |                                                                                             |        | T <sub>J</sub> =125℃ | 40  | -    | -   | V/µs |

|                                    | (V <sub>D</sub> =0.67V <sub>DRM</sub> ;gate open)                                           | Note:2 |                      |     |      |     |      |

| I <sub>H</sub>                     | Holding Current                                                                             |        |                      | -   | -    | 15  | mA   |

| ΙL                                 | latching current                                                                            |        |                      | -   | -    | 30  | mA   |

Note 1: minimum IGT is guaranted at 5% of IGT max. 2: for both polarities of A2 referenced to A1.

# WTPB4A60SW

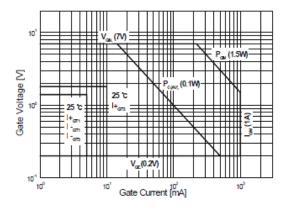

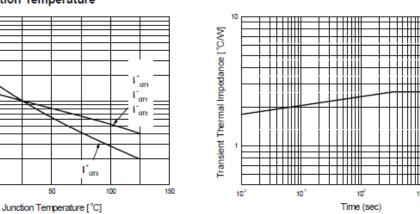

#### Fig 1. Gate Characteristics

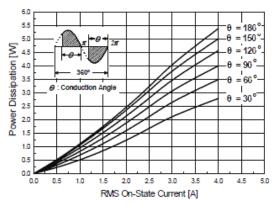

Fig 3. On State Current vs. Maximum Power Dissipation

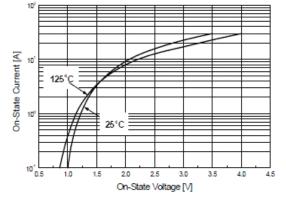

Fig 2. On-State Voltage

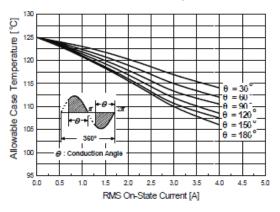

Fig 4. On State Current vs. Allowable Case Temperature

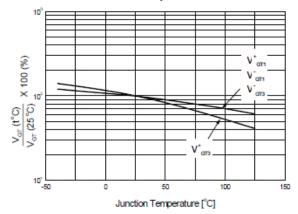

Fig 6. Gate Trigger Voltage vs. Junction Temperature

Ŵ

Steady, keep you advance

3 /5

$\frac{l_{or}(t^{\circ}C)}{l_{or}(25^{\circ}C)} \xrightarrow{X} 100 (\%)$

10

10<sup>1 L</sup> -50

0

# WTPB4A60SW

101

10

Fig 8. Transient Thermal Impedance

# Fig 7. Gate Trigger Current vs. Junction Temperature 10<sup>3</sup>

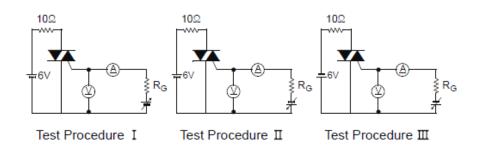

#### Fig 9. Gate Trigger Characteristics Test Circuit

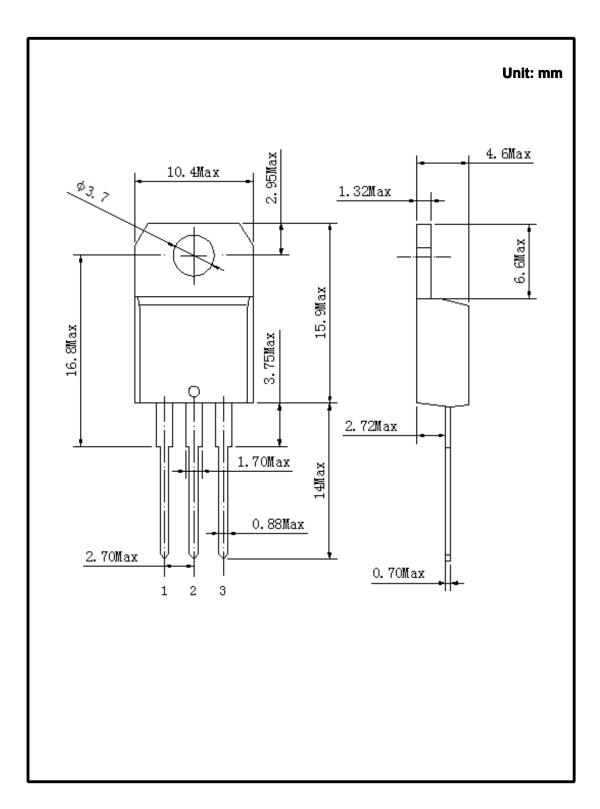

## **TO220 Package Dimension**

5 / 5