# SmartFusion2 System-on-Chip FPGAs

Microsemi's SmartFusion<sup>®</sup>2 SoC FPGAs integrate fourth generation flash-based FPGA fabric, an ARM<sup>®</sup> Cortex<sup>™</sup>-M3 processor, and high performance communications interfaces on a single chip. The SmartFusion2 family is the industry's lowest power, most reliable and highest security programmable logic solution. This next generation SmartFusion2 architecture offers up to 3.6X gate count implemented with 4-input look-up table (LUT) fabric with carry chains, giving 2X performance, and includes multiple embedded memory options and math blocks for digital signal processing (DSP). The 166 MHz ARM Cortex-M3 processor is enhanced with an embedded trace macrocell (ETM), memory protection unit (MPU), 8 Kbyte instruction cache, and additional peripherals including controller area network (CAN), Gigabit Ethernet, and high speed universal serial bus (USB). High speed serial interfaces include peripheral component interconnect express (PCIe), 10 Gbps attachment unit interface (XAUI) / XGMII extended sublayer (XGXS) + native serialization/deserialization (SERDES) communication, while double data rate 2 (DDR2)/DDR3 memory controllers provide high speed memory interfaces.

# SmartFusion2 Family

## Reliability

- Single Event Upset (SEU) Immune

- Zero FIT FPGA Configuration Cells

- Single Error Correct Double Error Detect (SECDED)

Protection on the Following:

- Ethernet Buffers

- CAN Message Buffers

- Cortex-M3 Embedded Scratch Pad Memory (eSRAMs)

- USB Buffers

- PCIe Buffer

- DDR Memory Controllers with Optional SECDED Modes

- Buffers Implemented with SEU Resistant Latches on the Following:

- DDR Bridges (MSS, MDDR, FDDR)

- Instruction Cache

- MMUART FIFOs

- SPI FIFOs

- NVM Integrity Check at Power-Up and On-Demand

- No External Configuration Memory Required—Instant-On, Retains Configuration When Powered Off

## Security

- Design Security Features (available on all devices)

- Intellectual Property (IP) Protection via Unique Security Features and Use Models New to the PLD Industry

- Encrypted User Key and Bitstream Loading, Enabling Programming in Less-Trusted Locations

- Supply-Chain Assurance Device Certificate

- Enhanced Anti-Tamper Features

- Zeroization

- Data Security Features (available on premium devices)

- Non-Deterministic Random Bit Generator (NRBG)

- User Cryptographic Services (AES-256, SHA-256, Elliptical Curve Cryptographic (ECC) Engine)

- User Physically Unclonable Function (PUF) Key Enrollment and Regeneration

- CRI Pass-Through DPA Patent Portfolio License

- Hardware Firewalls Protecting Microcontroller Subsystem (MSS) Memories

### Low Power

- Low Static and Dynamic Power

- Flash\*Freeze Mode for Fabric

- For the M2S050 Device:

- < 1 mW in Flash\*Freeze Mode</p>

- 10 mW in Standby Mode

- Based on 65 nm Nonvolatile Flash Process

## **High-Performance FPGA**

- Efficient 4-Input LUTs with Carry Chains for High Performance and Low Power

- Up to 236 Blocks of Dual-Port 18 Kbit SRAM (Large SRAM) with 400 MHz Synchronous Performance (x18, x9, x4, x2, x1)

- Up to 240 Blocks of Three-Port 1 Kbit SRAM with 2 Read Ports and 1 Write Port (micro SRAM)

- High Performance DSP Signal Processing

- Up to 240 Fast Math Blocks with 18 x 18 Signed Multiplication, 17 x 17 Unsigned Multiplication and 44-Bit Accumulator

# Microcontroller Subsystem (MSS)

- Hard 166 MHz 32-Bit ARM Cortex-M3 Processor

- 1.25 DMIPS/MHz

- 8 Kbyte Instruction Cache

- Embedded Trace Macrocell (ETM)

- Memory Protection Unit (MPU)

- Single Cycle Multiplication, Hardware Divide

- JTAG Debug (4 wires), Serial Wire Debug (SWD, 2 wires), and Serial Wire Viewer (SWV) Interfaces

- 64 KB Embedded SRAM (eSRAM)

- Up to 512 KB Embedded Nonvolatile Memory (eNVM)

- Triple Speed Ethernet (TSE) 10/100/1000 Mbps MAC

- USB 2.0 High Speed On-The-Go (OTG) Controller with ULPI Interface

- CAN Controller, 2.0B Compliant, Conforms to ISO11898-1, 32 Transmit and 32 Receive Buffers

- Two Each: SPI, I<sup>2</sup>C, Multi-Mode UARTs (MMUART) Peripherals

- Hardware Based Watchdog Timer

- 1 General Purpose 64-Bit (or two 32-bit) Timer(s)

- Real-Time Calendar/Counter (RTC)

- DDR Bridge (4 Port Data R/W Buffering Bridge to DDR Memory) with 64-Bit AXI Interface

- Non-Blocking, Multi-Layer AHB Bus Matrix Allowing Multi-Master Scheme Supporting 10 Masters and 7 Slaves

- Two AHB/APB Interfaces to FPGA Fabric (master/slave capable)

- Two DMA Controllers to Offload Data Transactions from the Cortex-M3 Processor

- 8-Channel Peripheral DMA (PDMA) for Data Transfer Between MSS Peripherals and Memory

- High Performance DMA (HPDMA) for Data Transfer Between eSRAM and DDR Memories

## **Clocking Resources**

- Clock Sources

- Up to Two High Precision 32 KHz to 20 MHz Main Crystal Oscillator

- 1 MHz Embedded RC Oscillator

- 50 MHz Embedded RC Oscillator

- Up to 8 Clock Conditioning Circuits (CCCs) with Up to 8

Integrated Analog PLLs

- Output Clock with 8 Output Phases and 45° Phase Difference (Multiply/Divide, and Delay Capabilities)

- Frequency: Input 1 to 200 MHz, Output 20 to 400 MHz

## **High Speed Serial Interfaces**

- Up to 16 SERDES Lanes, Each Supporting:

- XGXS/XAUI Extension (to implement a 10 Gbps (XGMII) Ethernet PHY interface)

- Native SERDES Interface Facilitates Implementation of Serial RapidIO in Fabric or an SGMII Interface to the Ethernet MAC in MSS

- PCI Express (PCIe) Endpoint Controller

x1, x2, x4 Lane PCI Express Core with 16-bit PIPE Interface (Gen1/Gen2)

256 Bytes Maximum Payload Size

64-/32-Bit AXI/AHB Master and Slave Interfaces to the Application Layer

### **High Speed Memory Interfaces**

- Up to 2 High Speed DDRx Memory Controllers

- MSS DDR (MDDR) and Fabric DDR (FDDR) Controllers

- Supports LPDDR/DDR2/DDR3

- Maximum 333 MHz Clock Rate

- SECDED Enable/Disable Feature

- Supports Various DRAM Bus Width Modes, x16, x18, x32, x36

- Supports Command Reordering to Optimize Memory Efficiency

- Supports Data Reordering, Returning Critical Word First for Each Command

- SDRAM Support

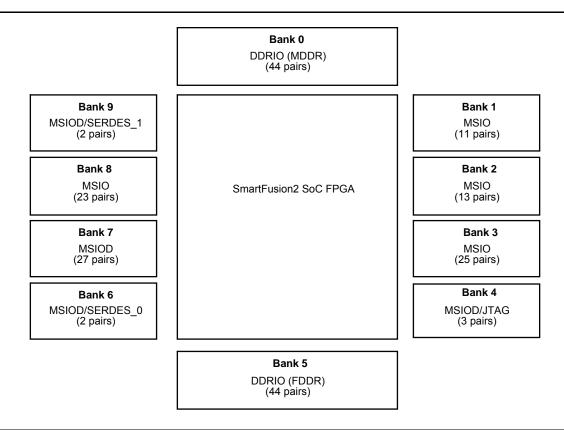

## **Operating Voltage and I/Os**

- 1.2 V Core Voltage

- Multi-Standard User I/Os (MSIO/MSIOD)

- LVTTL/LVCMOS 3.3 V

- LVCMOS 1.2 V, 1.5 V, 1.8 V, 2.5 V

- DDR (SSTL2 1, SSTL2 2)

- DDR2 (SSTL18\_1, SSTL18\_2)

- LVDS, MLVDS, Mini-LVDS, RSDS Differential Standards

- PCI

- LVPECL (receiver only)

- DDR I/Os (DDRIO)

- DDR, DDR2, DDR3, LPDDR, SSTL2, SSTL18, HSTL

- LVCMOS 1.2 V, 1.5 V, 1.8 V, 2.5 V

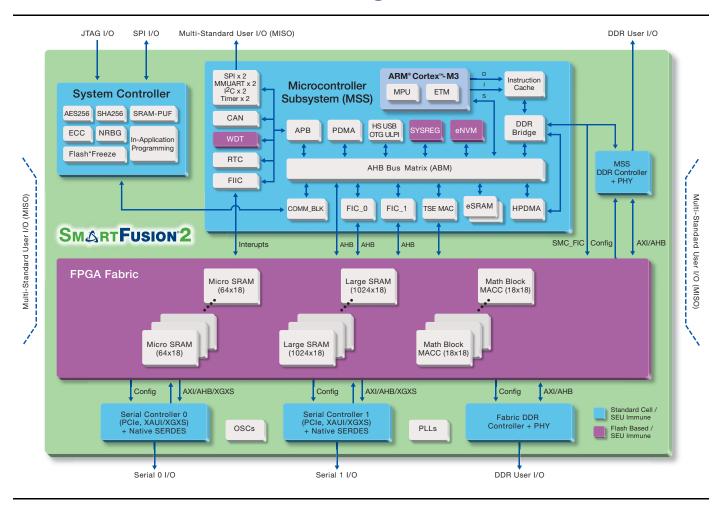

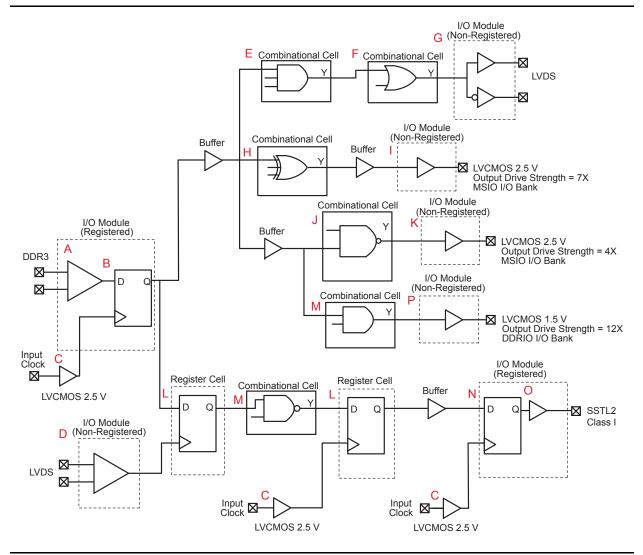

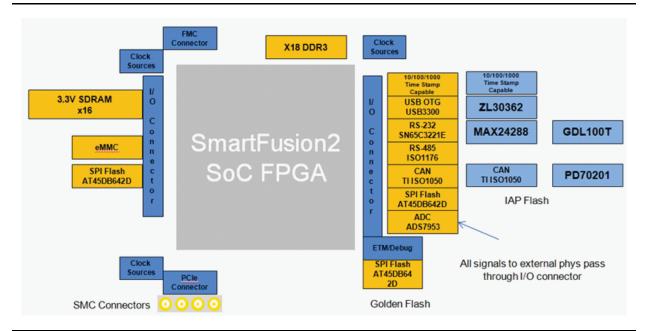

# SmartFusion2 SoC FPGA Block Diagram

## Acronyms

| AES        | Advanced Encryption Standard          |

|------------|---------------------------------------|

| AHB        | Advanced High-Performance Bus         |

| APB        | Advanced Peripheral Bus               |

| AXI        | Advanced eXtensible Interface         |

| COMM_BLK   | Communication Block                   |

| DDR        | Double Data Rate                      |

| DPA        | Differential Power Analysis           |

| ECC        | Elliptical Curve Cryptography         |

| EDAC       | Error Detection And Correction        |

| ETM        | Embedded Trace Macrocell              |

| FDDR       | DDR2/3 controller in FPGA fabric      |

| FIC        | Fabric Interface Controller           |

| FIIC       | Fabric Interface Interrupt Controller |

| HS USB OTG | High Speed USB 2.0 On-The-Go          |

| IAP        | In-Application Programming            |

| MACC       | Multiply-Accumulate                   |

|            |                                       |

| MDDR    | DDR2/3 Controller in MSS                 |

|---------|------------------------------------------|

| MMUART  | Multi-Mode UART                          |

| MPU     | Memory Protection Unit                   |

| MSS     | Microcontroller Subsystem                |

| SECDED  | Single Error Correct Double Error Detect |

| SEU     | Single Event Upset                       |

| SHA     | Secure Hashing Algorithm                 |

| SMC_FIC | Soft Memory Controller                   |

| TSE     | Triple Speed Ethernet (10/100/1000 Mbps) |

| ULPI    | UTMI + Low Pin Interface                 |

| UTMI    | USB 2.0 Transceiver Macrocell Interface  |

| WDT     | Watchdog Timer                           |

| XAUI    | 10 Gbps Attachment Unit Interface        |

| XGMII   | 10 Gigabit Media Independent Interface   |

| XGXS    | XGMII Extended Sublayer                  |

|         |                                          |

SmartFusion2 System-on-Chip FPGAs

Table 1 • SmartFusion2 SoC FPGA Product Family

|                       | Features                                | M2S005 | M2S010 | M2S025 | M2S050 | M2S080 | M2S120  |

|-----------------------|-----------------------------------------|--------|--------|--------|--------|--------|---------|

|                       | Logic Modules (4-Input LUT)             | 4,956  | 9,744  | 23,988 | 48,672 | 82,232 | 120,348 |

|                       | LSRAM 18K Blocks                        | 10     | 21     | 31     | 69     | 160    | 236     |

| ΑS                    | uSRAM 1K Blocks                         | 11     | 22     | 34     | 72     | 160    | 240     |

| FPGA                  | Total RAM (Bits)                        | 191K   | 400K   | 592K   | 1,314K | 3,040K | 4,500K  |

|                       | Math Blocks                             | 11     | 22     | 34     | 72     | 160    | 240     |

|                       | PLLs and CCCs                           | 2      | 2      | 4      | 6      | 8      | 8       |

|                       | Cortex-M3 Processor + Instruction Cache | Yes    | Yes    | Yes    | Yes    | Yes    | Yes     |

|                       | eNVM (Bytes)                            | 128K   | 256K   | 256K   | 256K   | 512K   | 512K    |

|                       | eSRAM (Bytes)                           | 64K    | 64K    | 64K    | 64K    | 64K    | 64K     |

|                       | eSRAM (Bytes non-SECDED)                | 80K    | 80K    | 80K    | 80K    | 80K    | 80K     |

|                       | CAN 2.0 A and B                         | 1      | 1      | 1      | 1      | 1      | 1       |

| MSS                   | Triple speed Ethernet 10/100/1000       | 1      | 1      | 1      | 1      | 1      | 1       |

| 2                     | USB 2.0 High Speed On-The-Go            | 1      | 1      | 1      | 1      | 1      | 1       |

|                       | Multi-Mode UART                         | 2      | 2      | 2      | 2      | 2      | 2       |

|                       | SPI                                     | 2      | 2      | 2      | 2      | 2      | 2       |

|                       | 12C                                     | 2      | 2      | 2      | 2      | 2      | 2       |

|                       | Timer                                   | 2      | 2      | 2      | 2      | 2      | 2       |

| Ϋ́Е                   | DDR Controllers                         | 1x18   | 1x18   | 1x18   | 2x36   | 2x36   | 2x36    |

| Memory,<br>Serial I/F | SERDES Channels                         | 0      | 4      | 4      | 8      | 8      | 16      |

| Me<br>Sei             | PCIe Endpoint × 4                       | 0      | 1      | 1      | 2      | 2      | 4       |

|                       | 3.3 V Multi-Standard User I/Os (MSIOs)  | 123    | 123    | 159    | 139    | 292    | 292     |

|                       | MSIOD I/Os                              | 28     | 40     | 40     | 62     | 106    | 106     |

| r I/o                 | DDRIO I/Os                              | 66     | 70     | 90     | 176    | 176    | 176     |

| Jser                  | Total User I/Os                         | 217    | 233    | 289    | 377    | 574    | 574     |

|                       | SERDES I/Os                             | 0      | 16     | 16     | 32     | 64     | 64      |

|                       | Total User I/Os + SERDES I/Os           | 217    | 249    | 305    | 409    | 638    | 638     |

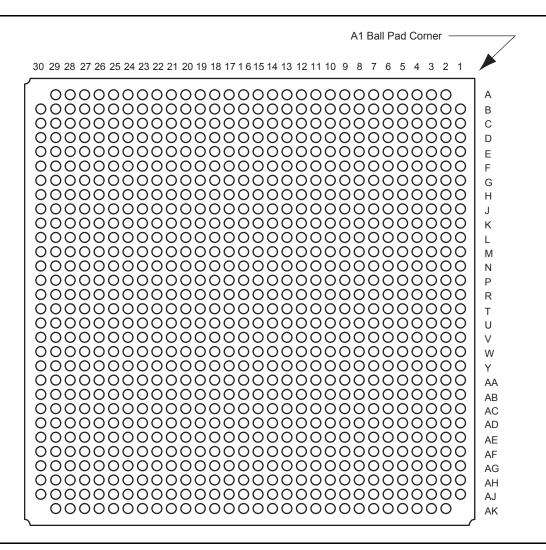

# I/Os Per Package

Table 2 • I/Os per Package and Package Options

| Package Options        | VF   | 400     | FG   | 484             | FG   | 896   | FC1152 |       |

|------------------------|------|---------|------|-----------------|------|-------|--------|-------|

| Pin Count              | 40   | 400     |      | 484             |      | 896   |        | 52    |

| Ball Pitch (mm)        | 0    | .8      | 1.0  |                 | 1.0  |       | 1      | .0    |

| Length × Width (mm\mm) | 17 ፡ | 17 × 17 |      | 23 × 23 31 × 31 |      | 35 :  | × 35   |       |

|                        | l/Os | XCVRs   | I/Os | XCVRs           | l/Os | XCVRs | l/Os   | XCVRs |

| M2S005                 | 160  | -       | 217  | -               | -    | -     | -      | -     |

| M2S010                 | 160  | 4       | 233  | 4               | _    | -     | _      | -     |

| M2S025                 | 160  | 4       | 267  | 4               | -    | -     | -      | -     |

| M2S050                 | 160  | 4       | 267  | 4               | 377  | 8     | -      | -     |

| M2S080                 | -    | -       | _    | -               | _    | -     | 574    | 8     |

| M2S120                 | -    | -       | _    | -               | _    | -     | 574    | 16    |

Note: User I/Os do not include the SERDES and JTAG pins.

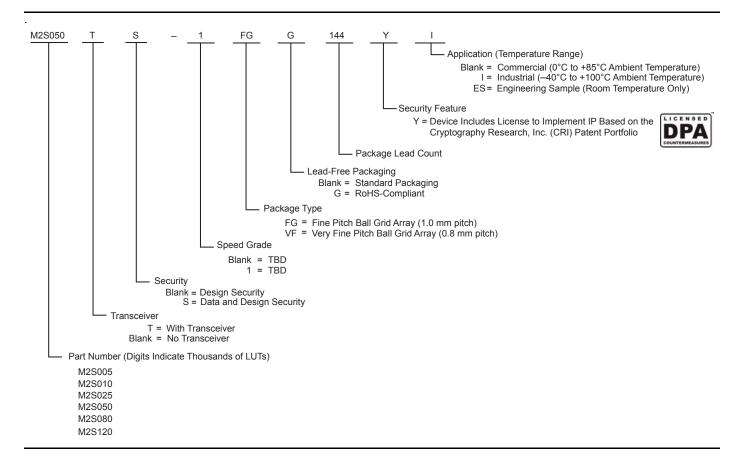

# **SmartFusion2 Ordering Information**

# **SmartFusion2 Valid Part Numbers**

Table 3 • SmartFusion2 Valid Part Numbers for Devices with Design Security

| Com              | mercial         | Industrial                     |                               |  |  |  |

|------------------|-----------------|--------------------------------|-------------------------------|--|--|--|

| Std. Speed Grade | -1 Speed Grade  | -1 Speed Grade                 | -1 Speed Grade, Data Security |  |  |  |

| M2S005-VF400     | M2S005-1VF400   | M2S005-1VF400I                 | M2S005S-1VF400I               |  |  |  |

| M2S010-VF400     | M2S010-1VF400   | M2S010-1VF400I                 | M2S010S-1VF400I               |  |  |  |

| M2S025-VF400     | M2S025-1VF400   | M2S025-1VF400I                 | M2S025S-1VF400I               |  |  |  |

| M2S050-VF400     | M2S050-1VF400   | M2S050-1VF400I                 | M2S050S-1VF400I               |  |  |  |

| M2S005-FG484     | M2S005-1FG484   | M2S005-1FG484I                 | M2S005S-1FG484I               |  |  |  |

| M2S010-FG484     | M2S010-1FG484   | M2S010-1FG484I                 | M2S010S-1FG484I               |  |  |  |

| M2S025-FG484     | M2S025-1FG484   | M2S025-1FG484I                 | M2S025S-1FG484I               |  |  |  |

| M2S050-FG484     | M2S050-1FG484   | M2S050-1FG484I                 | M2S050S-1FG484I               |  |  |  |

| M2S050-FG896     | M2S050-1FG896   | M2S050-1FG896I                 | M2S050S-1FG896I               |  |  |  |

| M2S080-FC1152    | M2S080-1FC1152  | M2S080-1FC1152I                | M2S080S-1FC1152I              |  |  |  |

| M2S120-FC1152    | M2S120-1FC1152  | M2S120-1FC1152I                | M2S120S-1FC1152I              |  |  |  |

| Transceivers     | Transceivers    | Transceivers                   | Transceivers                  |  |  |  |

| M2S010T-VF400    | M2S010T-1VF400  | M2S010T-1VF400I                | M2S010TS-1VF400I              |  |  |  |

| M2S025T-VF400    | M2S025T-1VF400  | M2S025T-1VF400I                | M2S025TS-1VF400I              |  |  |  |

| M2S050T-VF400    | M2S050T-1VF400  | M2S050T-1VF400I                | M2S050TS-1VF400I              |  |  |  |

| M2S010T-FG484    | M2S010T-1FG484  | M2S010T-1FG484I                | M2S010TS-1FG484I              |  |  |  |

| M2S025T-FG484    | M2S025T-1FG484  | M2S025T-1FG484I                | M2S025TS-1FG484I              |  |  |  |

| M2S050T-FG484    | M2S050T-1FG484  | M2S050T-1FG484I M2S050TS-1F    |                               |  |  |  |

| M2S050T-FG896    | M2S050T-1FG896  | M2S050T-1FG896I M2S050TS-1FG   |                               |  |  |  |

| M2S080T-FC1152   | M2S080T-1FC1152 | M2S080T-1FC1152I M2S080TS-1FC1 |                               |  |  |  |

| M2S120T-FC1152   | M2S120T-1FC1152 | M2S120T-1FC1152I               | M2S120TS-1FC1152I             |  |  |  |

# **SmartFusion2 Device Status**

| Family Devices | Status  |

|----------------|---------|

| M2S050T        | Advance |

Contact your local Microsemi SoC Products Group representative for device availability:

http://www.microsemi.com/soc/contact/default.aspx.

# **Table of Contents**

# SmartFusion2 Device Family Overview

| Reliability                                           | 1-2 |

|-------------------------------------------------------|-----|

| Highest Security Devices                              | 1-2 |

| Low Power                                             | 1-3 |

| High Performance FPGA Fabric                          | 1-3 |

| Microcontroller Subsystem (MSS)                       | 1-4 |

| Clock Sources: On-Chip Oscillators, PLLs, and CCCs    | 1-8 |

| High Speed Serial Interfaces                          | 1-8 |

| High Speed Memory Interfaces: DDRx Memory Controllers | 1-9 |

## SmartFusion2 DC and Switching Characteristics

| Seneral Specifications                                     | 2-1  |

|------------------------------------------------------------|------|

| Calculating Power Dissipation                              | 2-5  |

| verage Fabric Temperature and Voltage Derating Factors 2   | 2-14 |

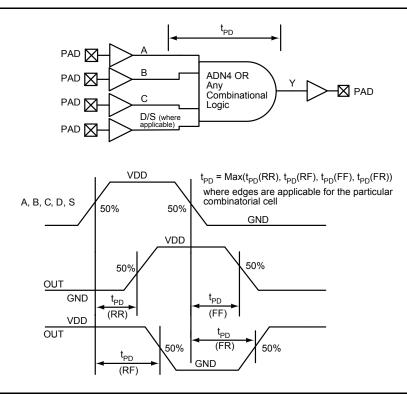

| iming Model                                                | 2-15 |

| Iser I/O Characteristics                                   | 2-17 |

| ogic Module Specifications                                 | 2-73 |

| Blobal Resource Characteristics                            | 2-76 |

| PGA Fabric SRAM                                            | 2-77 |

| On-Chip Oscillators                                        | 2-80 |

| Nock Conditioning Circuits (CCC)                           | 2-82 |

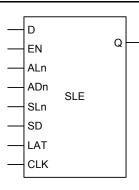

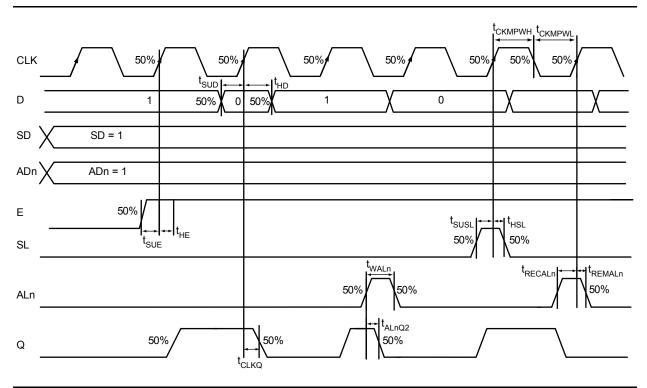

| erial Peripheral Interface (SPI) Characteristics 2         |      |

| nter-Integrated Circuit (I <sup>2</sup> C) Characteristics | 2-85 |

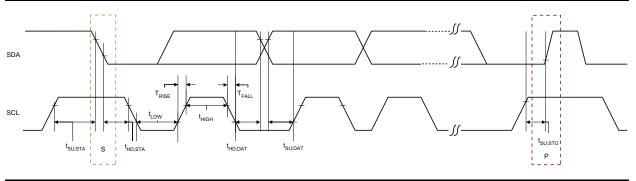

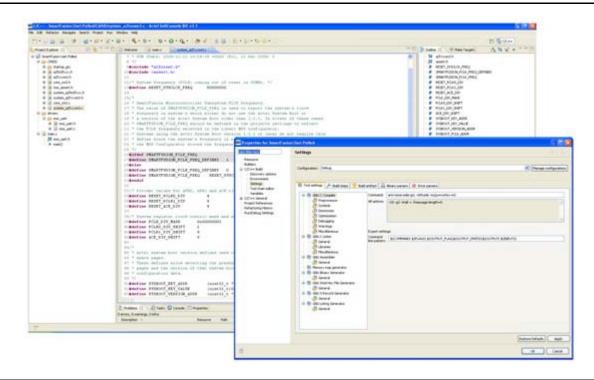

# SmartFusion2 Development Tools

| Libero SoC                      | 3-1  |

|---------------------------------|------|

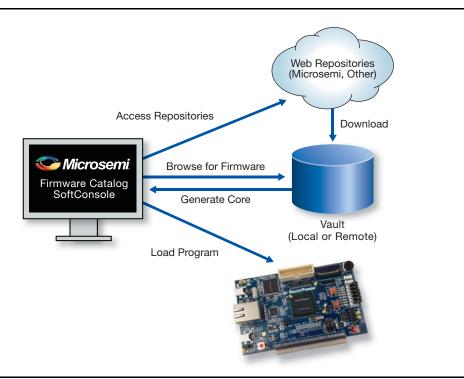

| SoftConsole                     | 3-4  |

| SoftConsole User Interface      | 3-5  |

| Firmware Catalog                | 3-6  |

| Firmware Catalog User Interface | 3-7  |

| SoC FPGA Ecosystem              | 3-8  |

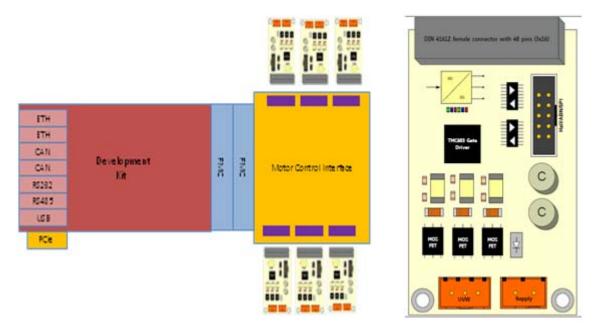

| SmartFusion2 Development Kit    | 3-12 |

# **Pin Descriptions**

| Supply Pins                             | 4-1  |

|-----------------------------------------|------|

| Dedicated Global I/O Naming Conventions | 4-4  |

| Jser I/O Naming Conventions             | 4-4  |

| Multi-Standard I/O                      | 4-5  |

| JTAG Pins                               | 4-9  |

| Microcontroller Subsystem (MSS)         | 4-10 |

| Multi-Function I/Os                     | 4-12 |

| -G896                                   | 4-13 |

# **Datasheet Information**

| Datasheet Categories                                                    | 5-1 |

|-------------------------------------------------------------------------|-----|

| Safety Critical, Life Support, and High-Reliability Applications Policy | 5-1 |

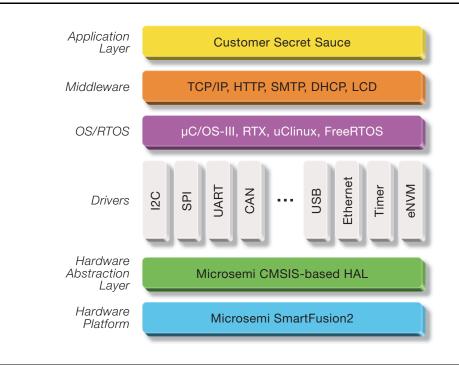

# 1 – SmartFusion2 Device Family Overview

Microsemi's SmartFusion2 SoC FPGAs integrate fourth generation flash-based FPGA fabric, an ARM Cortex-M3 processor and high performance communications interfaces on a single chip. The SmartFusion2 family is the industry's lowest power, highest reliability and most secure programmable logic solution. This next generation SmartFusion2 architecture offers up to 3.6X gate count implemented with 4-input look-up table (LUT) fabric with carry chains, giving 2X performance, and includes multiple embedded memory options and math blocks for DSP. The 166 MHz ARM Cortex-M3 processor is enhanced with ETM and 8 Kbyte instruction cache, and additional peripherals including CAN, Gigabit Ethernet, and high speed USB. High speed serial interfaces enable PCIe, XAUI / XGXS + Native SERDES communication while DDR2/DDR3 memory controllers provide high speed memory interfaces.

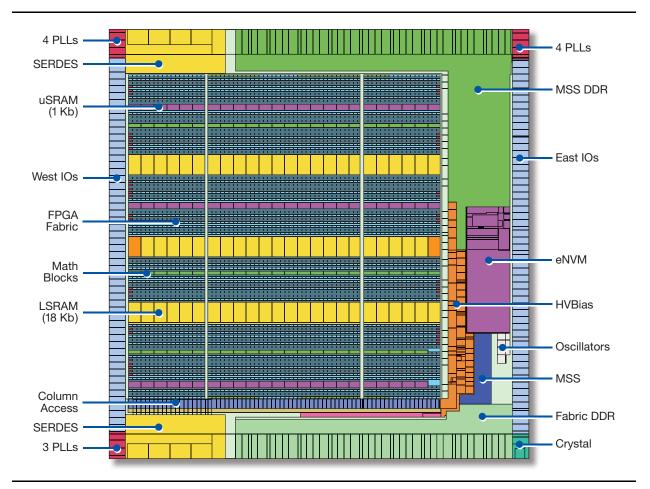

# SmartFusion2 Chip Layout

SmartFusion2 Device Family Overview

# Reliability

SmartFusion2 flash-based fabric has zero FIT configuration rate due to its single event upset (SEU) immunity, which is critical in reliability applications. The flash fabric also has the advantage that no external configuration memory is required, making the device instant-on; it retains configuration when powered off. To complement this unique FPGA capability, SmartFusion2 adds reliability to many other aspects of the device. Single Error Correct Double Error Detect (SECDED) protection is implemented on the Cortex-M3 embedded scratch pad memory, Ethernet, CAN and USB buffers, and is optional on the DDR memory controllers. This means that if a one-bit error is detected, it will be corrected. Errors of more than one bit are detected only and not corrected. SECDED error signals are brought to the FPGA fabric to allow the user to monitor the status of these protected internal memories. Other areas of the architecture are implemented with latches, which are not subject to SEUs. Therefore, no correction is needed in these locations: DDR Bridges (MSS, MDDR, FDDR), Instruction Cache and MMUART, SPI, and PCIe FIFOs.

# **Highest Security Devices**

Building further on the intrinsic security benefits of flash nonvolatile memory technology, the SmartFusion2 family incorporates essentially all the legacy security features that made the original SmartFusion, Fusion<sup>®</sup>, IGLOO<sup>®</sup>, and ProASIC<sup>®</sup>3 third-generation flash FPGAs and cSoCs the gold standard for secure devices in the PLD industry. In addition, the fourth-generation flash-based SmartFusion2 SoC FPGAs add many unique design and data security features and use models new to the PLD industry.

# **Design Security vs. Data Security**

When classifying security attributes of programmable logic devices (PLDs), a useful distinction is made between design security and data security.

## **Design Security**

Design security is protecting the intent of the owner of the design, such as keeping the design and associated bitstream keys confidential, preventing design changes (insertion of Trojan Horses, for example), and controlling the number of copies made throughout the device life cycle. Design security may also be known as intellectual property (IP) protection. It is one aspect of anti-tamper (AT) protection. Design security applies to the device from initial production, includes any updates such as in-the-field upgrades, and can include decommissioning of the device at the end of its life, if desired. Good design security is a prerequisite for good data security.

The following are the main design security features supported:

- User key and bitstream loading in less-trusted locations

- Encrypted key loading using device-unique built-in factory key

- · Methods to verify devices are programmed correctly, even if done in less-trusted locations

- · Supply-chain assurances to eliminate counterfeiting

- Differential power analysis (DPA) and enhanced anti-tamper features to address non-invasive, semi-invasive, and invasive attacks

- · Ability to zeroize (destroy) all sensitive stored data in the event of tampering

- The M2S080 and M2S120 also have the following features:

- Elliptic Curve Cryptography (ECC) for securely loading user keys

- An SRAM-type Physically Unclonable Function (SRAM-PUF) for device authentication

# Data Security

Data security is protecting the information the FPGA is storing, processing, or communicating in its role in the end application. If, for example, the configured design is implementing the key management and encryption portion of a secure military radio, data security could entail encrypting and authenticating the radio traffic, and protecting the associated application-level cryptographic keys. Data security is closely related to the terms information assurance (IA) and information security.

All SmartFusion2 devices incorporate enhanced design security, making them the most secure programmable logic devices ever made. Select SmartFusion2 models also include an advanced set of on-chip data security features that make designing secure information assurance applications easier and better than ever before.

The following are the main data security features supported:

- Non-deterministic random bit generator (NRBG) service

- User Cryptographic services (e.g., AES-128/-256, SHA-256, and HMAC)

- Hardware firewalls protecting MSS memories

- Cryptography Research Inc. (CRI) pass-through Differential Power Analysis (DPA) Patent Portfolio license

- The M2S080 and M2S120 also have the following features:

- Elliptic Curve Cryptography (ECC) cryptographic computation services

- User PUF key enrollment and regeneration for advanced design and data security applications

# **Low Power**

Microsemi's flash-based FPGA fabric results in extremely low power design implementation with static power on the M2S050 device as low as 10 mW. Flash\*Freeze (F\*F) technology provides an ultra-low power static mode (Flash\*Freeze mode) for SmartFusion2 devices, with power less than 1 mW. F\*F mode entry retains all the SRAM and register information and the exit from F\*F mode achieves rapid recovery to active mode.

# **High Performance FPGA Fabric**

Built on 65 nm process technology, the SmartFusion2 FPGA fabric is composed of 4 building blocks: the logic module, the large SRAM, the micro SRAM and the Math block. The logic module is the basic logic element and has advanced features:

- A fully permutable 4-input LUT (look-up table) optimized for lowest power

- A dedicated carry chain based on carry look-ahead technique

- · A separate flip-flop which can be used independently from the LUT

The 4-input look-up table can be configured either to implement any 4-input combinatorial function or to implement an arithmetic function where the LUT output is XORed with carry input to generate the sum output.

## **Dual-Port Large SRAM (LSRAM)**

Large SRAM (RAM1Kx18) is targeted for storing large memory for use with various operations. Each LSRAM block can store up to 18,432 bits. Each RAM1Kx18 block contains two independent data ports: Port A and Port B. The LSRAM is synchronous for both Read and Write operations. Operations are triggered on the rising edge of the clock. The data output ports of the LSRAM have pipeline registers which have control signals that are independent of the SRAM's control signals.

## **Three-Port Micro SRAM (uSRAM)**

Micro SRAM (RAM64x18) is the second type of SRAM which is embedded in the fabric of SmartFusion2 devices. RAM64x18 uSRAM is a 3-port SRAM; it has two read ports (Port A and Port B) and one write

SmartFusion2 Device Family Overview

port (Port C). The two read ports are independent of each other and can perform Read operations in both synchronous and asynchronous modes. The write port is always synchronous. The uSRAM block is approximately 1 Kb (1,152 bits) in size. These uSRAM blocks are primarily targeted for building embedded FIFOs to be used by any embedded fabric masters.

# Math Blocks for DSP Applications

The fundamental building block in any digital signal processing algorithm is the multiply-accumulate function. SmartFusion2 implements a custom 18x18 Multiply-Accumulate (18x18 MACC) block for efficient implementation of complex DSP algorithms such as finite impulse response (FIR) filters, infinite impulse response (IIR) filters, and fast Fourier transform (FFT) for filtering and image processing applications.

Each Math block has the following capabilities:

- Supports 18x18 signed multiplications natively (a[17:0] x b[17:0])

- Supports dot product; the multiplier computes:

(A[8:0] x B[17:9] + A[17:9] x B[8:0]) x 2<sup>9</sup>

• Built-in addition, subtraction, and accumulation units to combine multiplication results efficiently

In addition to the basic MACC function, DSP algorithms typically need small amounts of RAM for coefficients and larger RAMs for data storage. SmartFusion2 micro RAMs are ideally suited to serve the needs of coefficient storage while the large RAMs are used for data storage.

# **Microcontroller Subsystem (MSS)**

The microcontroller subsystem (MSS) contains a high-performance integrated Cortex-M3 processor, running at up to 166 MHz. The MSS contains an 8 Kbyte instruction cache to provide low latency access to internal eNVM and external DDR memory. The MSS provides multiple interfacing options to the FPGA fabric in order to facilitate tight integration between the MSS and user logic in the fabric.

## **ARM Cortex-M3 Processor**

The MSS uses the latest revision (r2p1) of the ARM Cortex-M3 processor. Microsemi's implementation includes the optional embedded trace macrocell (ETM) features for easier development and debug and the memory protection unit (MPU) for real-time operating system support.

## **Cache Controller**

In order to minimize latency for instruction fetches when executing firmware out of off-chip DDR or on-chip eNVM, an 8 kbyte, 4-way set associative instruction cache is implemented. This provides zero wait state access for cache hits and is shared by both I and D Code buses of the Cortex-M3 processor. In the event of cache misses, cache lines are filled, replacing existing cache entries based on a least recently used (LRU) algorithm.

There is a configurable option available to operate the cache in a locked mode, whereby a fixed segment of code from either the DDR or eNVM is copied into the cache and locked there, so that it is not replaced when cache misses occur. This would be used for performance-critical code.

It is also possible to disable the cache altogether, which is desirable in systems requiring very deterministic execution times.

The cache is implemented with SEU tolerant latches.

## **DDR Bridge**

The DDR bridge is a data bridge between four AHB bus masters and a single AXI bus slave. The DDR bridge accumulates AHB writes into write combining buffers prior to bursting out to external DDR memory. The DDR bridge also includes read combining buffers, allowing AHB masters to efficiently read data from the external DDR memory from a local buffer. The DDR bridge optimizes reads and writes from multiple masters to a single external DDR memory. Data coherency rules between the four masters and

the external DDR memory are implemented in hardware. The DDR Bridge contains three write combining / read buffers and one read buffer. All buffers within the DDR bridge are implemented with SEU tolerant latches and are not subject to the single event upsets (SEUs) that SRAM exhibits. SmartFusion2 devices implement three DDR bridges in the MSS, FDDR, and MDDR subsystems.

# AHB Bus Matrix (ABM)

The AHB bus matrix (ABM) is a non-blocking, AHB-Lite multi-layer switch, supporting 10 master interfaces and 7 slave interfaces. The switch decodes access attempts by masters to various slaves, according to the memory map and security configurations. When multiple masters are attempting to access a particular slave simultaneously, an arbiter associated with that slave decides which master gains access, according to a configurable set of arbitration rules. These rules can be configured by the user to provide different usage patterns to each slave. For example, a number of consecutive access opportunities to the slave can be allocated to one particular master, to increase the likelihood of same type accesses (all reads or all writes), which makes more efficient usage of the bandwidth to the slave.

# System Registers

The MSS System registers are implemented as an AHB slave on the AHB bus matrix. This means the Cortex-M3 processor or a soft master in the FPGA fabric may access the registers and therefore control the MSS. The System registers can be initialized by user-defined flash configuration bits on power-up. Each register also has a flash bit to enable write protecting the contents of the registers. This allows the MSS system configuration to be reliably fixed for a given application.

# Fabric Interface Controller (FIC)

The FIC block provides two separate interfaces between the MSS and the FPGA fabric: the MSS Master (MM) and Fabric Master (FM). Each of these interfaces can be configured to operate as AHB-Lite or APB3. Depending on device density, there are up to two FIC blocks present in the MSS (FIC\_0 and FIC\_1).

# Embedded SRAM (eSRAM)

The MSS contains two blocks of 32 KB eSRAM, giving a total of 64 KB. Having the eSRAM arranged as two separate blocks allows the user to take advantage of the Harvard architecture of the Cortex-M3 processor. For example, code could be located in one eSRAM, while data, such as the stack, could be located in the other.

The eSRAM is designed for Single Error Correct Double Error Detect (SECDED) protection. When SECDED is disabled, the SRAM usually used to store SECDED data may be reused as an extra 16 KB of eSRAM.

# Embedded NVM (eNVM)

The MSS contains up to 512 KB of eNVM (64 bits wide). Accesses to the eNVM from the Cortex-M3 processor are cacheable.

# **DMA Engines**

Two DMA engines are present in the MSS: high performance DMA and peripheral DMA.

### High Performance DMA (HPDMA)

The high-performance DMA (HPDMA) engine provides efficient memory to memory data transfers between an external DDR memory and internal eSRAM. This engine has two separate AHB-Lite interfaces—one to the MDDR bridge and the other to the AHB bus matrix. All transfers by the HPDMA are full word transfers.

### Peripheral DMA (PDMA)

The peripheral DMA engine (PDMA) is tuned for offloading byte-intensive operations, involving MSS peripherals, to and from the internal eSRAMs. Data transfers can also be targeted to user logic/RAM in the FPGA fabric.

# **APB Configuration Bus**

On every SmartFusion2 device memory, an APB configuration bus is present to allow the user to initialize the SERDES ASIC blocks, the fabric DDR memory controller, and user instantiated peripherals in the FPGA fabric.

## Peripherals

A large number of communications and general purpose peripherals are implemented in the MSS.

### **USB** Controller

The MSS contains a high speed USB 2.0 On-The-Go (OTG) controller with the following features:

- Operates either as the function controller of a high-speed / full-speed USB peripheral or as the host/peripheral in point-to-point or multi-point communications with other USB functions.

- Complies with the USB 2.0 standard for high-speed functions and with the *On-The-Go* supplement to the USB 2.0 specification.

- Supports OTG communications with one or more high-speed, full-speed, or low-speed devices.

## **TSE Ethernet MAC**

The Triple Speed Ethernet (TSE) MAC supports IEEE 802.3 10/100/1000Mbps Ethernet operation. The following PHY interfaces are directly supported by the MAC:

- RMII

- GMII

- MII

- TBI

The Ethernet MAC hardware implements the following functions:

- 4 KB internal transmit FIFO and 8 KB internal receive FIFO

- IEEE 802.3X full-duplex flow control

- DMA of Ethernet frames between internal FIFOs and system memory (such as eSRAM or DDR)

- Cut-through operation

- SECDED protection on internal FIFOs

### SGMII PHY Interface

SGMII mode is implemented by means of configuring the MAC for 10-bit interface (TBI) operation, allocating one of the high-speed serial channels to SGMII and by implementing custom logic in the fabric. 10 Gbps Ethernet

Support for 10 Gbps Ethernet is achieved by programming the SERDES interface to XAUI mode. In this mode, a soft 10G EMAC with XGMII interface can be directly connected to the SERDES. interface.

# Communication Block (COMM\_BLK)

The COMM block provides a UART-like communications channel between the MSS and the System Controller. System services are initiated through the COMM block. System services such as *Enter Flash\*Freeze Mode* are initiated though this block.

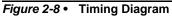

### SPI

The serial peripheral interface controller is compliant with the Motorola SPI, Texas Instruments synchronous serial, and National Semiconductor MICROWIRE™ formats. In addition, the SPI supports interfacing to large SPI flash and EEPROM devices by way of the slave protocol engine. The SPI controller supports both Master and Slave modes of operation.

The SPI controller embeds two 4×32 (depth × width) FIFOs for receive and transmit. These FIFOs are accessible through RX data and TX data registers. Writing to the TX data register causes the data to be written to the transmit FIFO. This is emptied by transmit logic. Similarly, reading from the RX data register causes data to be read from the receive FIFO.

## Multi-Mode UART (MMUART)

SmartFusion2 devices contain two identical multi-mode universal asynchronous/synchronous receiver/transmitter (MMUART) peripherals that provide software compatibility with the popular 16550 device. They perform serial-to-parallel conversion on data originating from modems or other serial devices, and perform parallel-to-serial conversion on data from the Cortex-M3 processor to these devices.

The following are the main features supported:

- · Fractional baud rate capability

- Asynchronous and synchronous operation

- Full programmable serial interface characteristics

- Data width is programmable to 5, 6, 7, or 8 bits

- Even, odd, or no-parity bit generation/detection

- 1,1<sup>1</sup>/<sub>2</sub>, and 2 stop bit generation

- 9-bit address flag capability used for multidrop addressing topologies

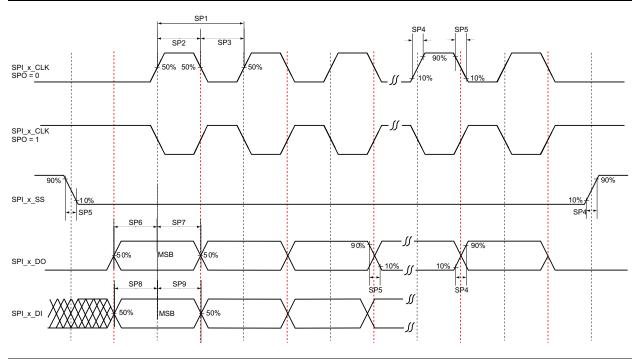

## βĈ

SmartFusion2 devices contain two identical master/slave I<sup>2</sup>C peripherals that perform serial to-parallel conversion on data originating from serial devices, and perform parallel-to-serial conversion on data from the ARM Cortex-M3 processor, or any other bus master, to these devices. The following are the main features supported:

- I<sup>2</sup>C v2.1

- 100 Kbps

- 400 Kbps

- Dual-slave addressing

- SMBus v2.0

- PMBus v1.1

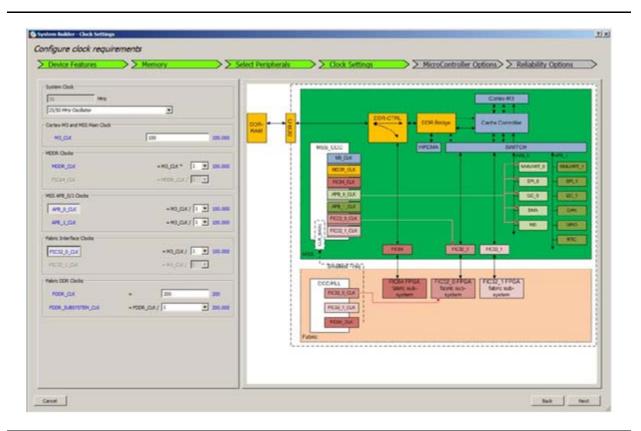

# **Clock Sources: On-Chip Oscillators, PLLs, and CCCs**

SmartFusion2 devices have two on-chip RC oscillators—a 1 MHz RC oscillator and a 50 MHz RC oscillator—and up to two main crystal oscillators (32 KHz–20 MHz). These are available to the user for generating clocks to the on-chip resources and the logic built on the FPGA fabric array. The second crystal oscillator available on the SmartFusion2 devices is dedicated for RTC clocking. These oscillators (except the RTC crystal oscillator) can be used in conjunction with the integrated user phase-locked loops (PLLs) and FAB\_CCCs to generate clocks of varying frequency and phase. In addition to being available to the user, these oscillators are also used by the system controller, power-on reset circuitry, MSS during Flash\*Freeze mode, and the RTC.

SmartFusion2 devices have up to eight fabric CCC (FAB\_CCC) blocks and a dedicated PLL associated with each CCC to provide flexible clocking to the FPGA fabric portion of the device. The user has the freedom to use any of the eight PLLs and CCCs to generate the fabric clocks and the internal MSS clock from the base fabric clock (CLK\_BASE). There is also a dedicated CCC block for the MSS (MSS\_CCC) and an associated PLL (MPLL) for MSS clocking and de-skewing the CLK\_BASE clock. The fabric alignment clock controller (FACC), part of the MSS CCC, is responsible for generating various aligned clocks required by the MSS for correct operation of the MSS blocks and synchornous communication with the user logic in the FPGA fabric.

# **High Speed Serial Interfaces**

# **SERDES** Interface

SmartFusion2 has up to four 5 Gbps SERDES transceivers, each supporting the following:

- 4 SERDES/PCS lanes

- The native SERDES interface facilitates implementation of Serial RapidIO (SRIO) in fabric or an SGMII interface for the Ethernet MAC in MSS

# PCI Express (PCIe)

PCIe is a high speed, packet-based, point-to-point, low pin count, serial interconnect bus. The SmartFusion2 family has two hard high-speed serial interface blocks. Each SERDES block contains a PCIe (PCI Express) system block. The PCIe system is connected to the SERDES block and following are the main features supported:

- Supports x1, x2 and x4 lane configuration

- · Endpoint configuration only

- PCI Express Base Specification Revision 2.0

- 2.5 and 5.0 Gbps compliant

- Embedded Receive (2 KB), Transmit (1 KB) and Retry (1 KB) buffer dual-port RAM implementation

- 256 bytes maximum payload size

- 64-bit AXI or 32-bit/64-bit AHBL Master and Slave interface to the application layer

- 32-bit APB interface to access configuration and status registers of PCIe system

- Up to 3 x 64 bit base address registers

- 1 virtual channel (VC)

- Intel's PIPE interface (8-bit/16-bit) to interface between the PHY MAC and PHY (SERDES)

- Fully compliant PHY PCS sub-layer (125/250 MHz)

## XAUI/XGXS Extension

The XAUI/XGXS extension allows the user to implement a 10 Gbps (XGMII) Ethernet PHY interface by connecting the Ethernet MAC fabric interface through an appropriate soft IP block in the fabric.

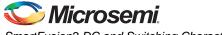

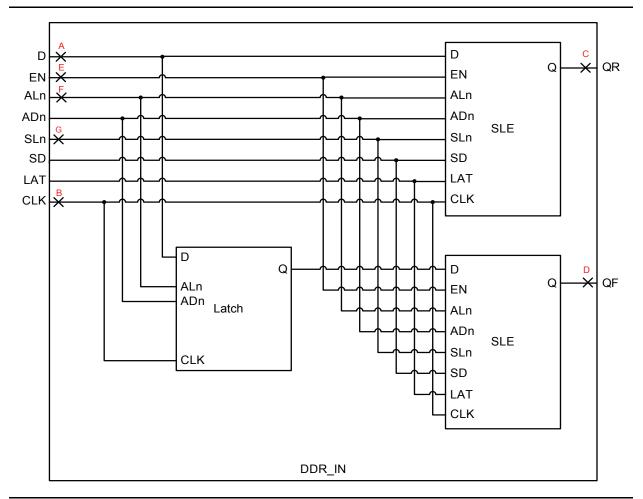

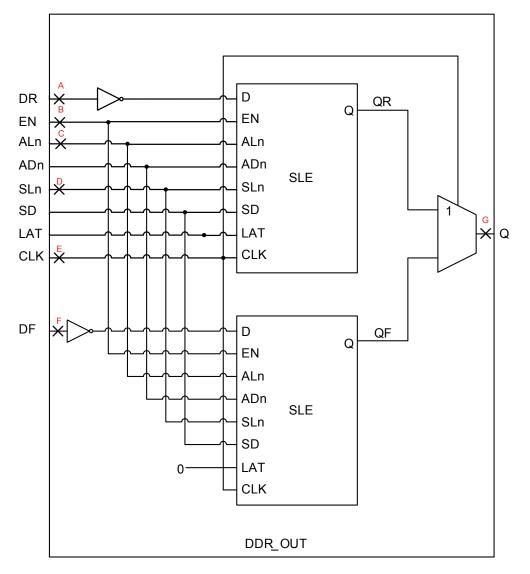

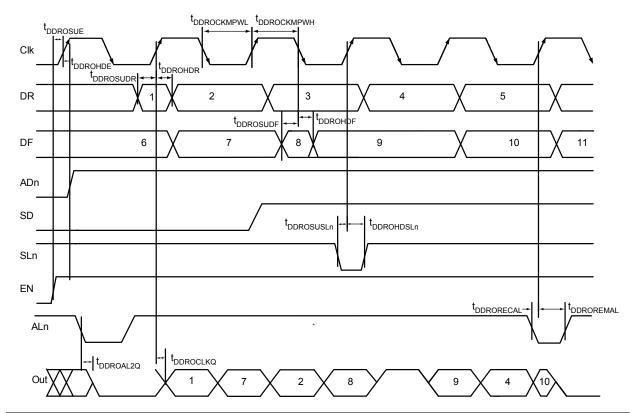

# High Speed Memory Interfaces: DDRx Memory Controllers

There are up to two DDR subsystems, MDDR (MSS DDR) and FDDR (Fabric DDR) present in SmartFusion2 devices. Each subsystem consists of a DDR controller, PHY and a wrapper. The MDDR has an interface from the MSS and fabric and FDDR provides an interface from the fabric.

The following are the main features supported by FDDR and MDDR:

- · Support for LPDDR, DDR2, and DDR3 memories

- Support for SDRAM memories

- Simplified DDR command interface to standard AMBA AXI/AHB interface

- Up to 667 Mbps (333 MHz double data rate) performance

- Supports 1, 2, or 4 ranks of memory

- Supports different DRAM Bus width modes: x16, x18, x32, and x36

- Supports DRAM burst length of 2, 4, or 8 in full bus-width mode; supports DRAM burst length of 2, 4, 8, or 16 in half bus-width mode

- Supports memory densities up to 4 GB

- Supports a maximum of 8 memory banks

- SECDED enable/disable feature

- Embedded physical interface (PHY)

- Read and Write buffers in fully associative CAMs, configurable in powers of 2, up to 64 Reads plus 64 Writes

- Support for dynamically changing clock frequency while in self-refresh.

- · Supports command reordering to optimize memory efficiency

- Supports data reordering, returning critical word first for each command

### **MDDR Subsystem**

The MDDR subsystem has two interfaces to the DDR. One is an AXI 64-bit bus from the DDR bridge within the MSS. The other is a multiplexed interface from the FPGA fabric, which can be configured as either a single AXI 64-bit bus or two 32-bit AHB-Lite buses. There is also a 16-bit APB configuration bus, which is used to initialize the majority of the internal registers within the MDDR subsystem after reset. This APB configuration bus can be mastered by the MSS directly or by a master in the FPGA fabric.

## **FDDR Subsystem**

The FDDR subsystem has one interface to the DDR. This is a multiplexed interface from the FPGA fabric, which can be configured as either a single AXI 64-bit bus or two 32-bit AHB-Lite buses. There is also a 16-bit APB configuration bus, which is used to initialize the majority of the internal registers within the FDDR subsystem after reset. This APB configuration bus can be mastered by the MSS directly or by a master in the FPGA fabric.

# **General Specifications**

# **Operating Conditions**

| Symbol           | Parameter                                                    | Conditions         | Min.            | Тур.           | Max.            | Units | Notes |

|------------------|--------------------------------------------------------------|--------------------|-----------------|----------------|-----------------|-------|-------|

| TJ               | Junction temperature                                         | Commercial         | 0               | 25             | 85              | °C    |       |

|                  | Junction temperature                                         | Industrial         | -40             | 25             | 100             | °C    |       |

| VDD              | DC core supply voltage                                       |                    | 1.14            | 1.2            | 1.26            | V     |       |

| VPP              | Power supply for charge pumps (for                           | 2.5 V range        | 2.375           | 2.5            | 2.625           | V     |       |

|                  | normal opeartion and programming)                            | 3.3 V range        | 3.15            | 3.3            | 3.45            | V     |       |

| PLLx_VDDA        | Analog power supply for PLL0 to                              | 2.5 V range        | 2.375           | 2.5            | 2.625           | V     |       |

|                  | PLL5                                                         | 3.3 V range        | 3.15            | 3.3            | 3.45            | V     |       |

| PLL_PCIE_X_VDDA  | Auxiliary power supply voltage by                            | 2.5 V range        | 2.375           | 2.5            | 2.625           | V     |       |

|                  | core to macro                                                | 3.3 V range        | 3.15            | 3.3            | 3.45            | V     |       |

| PLL_MDDR_VDDA    | Analog power supply for PLL                                  | 2.5 V range        | 2.375           | 2.5            | 2.625           | V     |       |

|                  | MDDR                                                         | 3.3 V range        | 3.15            | 3.3            | 3.45            | V     |       |

| PLL_FDDR_VDDA    | Analog power supply for PLL FDDR                             | 2.5 V range        | 2.375           | 2.5            | 2.625           | V     |       |

|                  |                                                              | 3.3 V range        | 3.15            | 3.3            | 3.45            | V     |       |

| PCIExVDD         | PCIe/PCS power supply                                        | 1.14               | 1.2             | 1.26           | V               |       |       |

| PCIExVDDIO[L/R]  | Tx/Rx analog I/O voltage supply                              | 1.14               | 1.2             | 1.26           | V               |       |       |

| PCIExVDDPLL[L/R] | Anlog power supply for SERDES PL                             | 2.375              | 2.5             | 2.625          | V               |       |       |

| VDDIx            | 1.2 V DC supply voltage                                      |                    | 1.14            | 1.2            | 1.26            | V     |       |

|                  | 1.5 V DC supply voltage                                      | 1.425              | 1.5             | 1.575          | V               |       |       |

|                  | 1.8 V DC supply voltage                                      |                    | 1.71            | 1.8            | 1.89            | V     |       |

|                  | 2.5 V DC supply voltage                                      | 2.375              | 2.5             | 2.625          | V               |       |       |

|                  | 3.3 V DC supply voltage                                      |                    | 3.15            | 3.3            | 3.45            | V     |       |

|                  | LVDS differential I/O                                        |                    | 2.375           | 2.5            | 3.45            | V     |       |

|                  | B-LVDS, M-LVDS, Mini-LVDS, RSDS                              | 6 differential I/O | 2.375           | 2.5            | 2.625           | V     |       |

|                  | LVPECL differential I/O                                      |                    | 3.15            | 3.3            | 3.45            | V     |       |

| VREFx            | Reference voltage supply for FDDR (bank 0) and MDDR (bank 5) |                    | 0.49<br>* VDDI0 | 0.5<br>* VDDI0 | 0.51<br>* VDDI0 | V     |       |

| VCCENVM          | Embedded nonvolatile memory                                  | 2.5 V range        | 2.375           | 2.5            | 2.625           | V     |       |

|                  | supply                                                       | 3.3 V range        | 3.15            | 3.3            | 3.45            | V     |       |

### Table 2-1 • Recommended Operating Conditions

| Product Grade | Storage<br>Temperature                                  | Programming<br>Temperature                              | Element        | Grade Programming<br>Cycles | Retention |

|---------------|---------------------------------------------------------|---------------------------------------------------------|----------------|-----------------------------|-----------|

| Commercial    | Min. T <sub>J</sub> = 0°C<br>Max. T <sub>J</sub> = 85°C | Min. T <sub>J</sub> = 0°C<br>Max. T <sub>J</sub> = 85°C | FPGA           | 500                         | 20 years  |

|               |                                                         | Min. T <sub>J</sub> = 0°C                               | Embedded Flash | < 1,000                     | 20 years  |

|               |                                                         | Max. T <sub>J</sub> = 85°C                              |                | < 10,000                    | 10 years  |

| Industrial    | Min. $T_J = -40^{\circ}C$<br>Max. $T_J = 100^{\circ}C$  | Min. T <sub>J</sub> = 0°C<br>Max. T <sub>J</sub> = 85°C | FPGA           | 500                         | 20 years  |

|               |                                                         | Min. T <sub>J</sub> = –40°C                             | Embedded Flash | < 1,000                     | 20 years  |

|               | Max. T <sub>J</sub> = 100°C                             |                                                         |                | < 10,000                    | 10 years  |

# Power Supply Sequencing and Power-On Reset (Commercial and Industrial)

Sophisticated power-up management circuitry is designed into every SmartFusion2 SoC FPGA. These circuits ensure easy transition from powered-off state to powered-up state of the device. The SmartFusion2 system controller is responsible for systematic power-on reset whenever the device is powered on or reset. All the I/Os are held in a high-impedance state by the system controller until all power supplies are at their required levels and the system controller has completed the reset sequence. The power-on reset circuitry in SmartFusion2 devices requires the VDD supply to ramp at a predefined rate. Four ramp rate options are available during design generation: 50 µs, 100 µs, 1 ms, and 100 ms.

# **Thermal Characteristics**

### Introduction

The temperature variable in the SoC Products Group Designer software refers to the junction temperature, not the ambient, case, or board temperatures. This is an important distinction because dynamic and static power consumption will cause the chip's junction temperature to be higher than the ambient, case, or board temperatures. EQ 1 through EQ 3 give the relationship between thermal resistance, temperature gradient, and power.

$$\theta_{JA} = \frac{T_J - \theta_A}{P}$$

$\theta_{JB} = \frac{T_J - T_B}{P}$

$\theta_{JC} = \frac{T_J - T_C}{P}$

EQ 1

where

- $\theta_{JA}$  = Junction-to-air thermal resistance

- $\theta_{JB}$  = Junction-to-board thermal resistance

- $\theta_{JC}$  = Junction-to-case thermal resistance

- T<sub>J</sub> = Junction temperature

- T<sub>A</sub> = Ambient temperature

- T<sub>B</sub> = Board temperature (measured 1.0 mm away from the package edge)

T<sub>C</sub> = Case temperature

P = Total power dissipated by the device

### Table 2-3 • Package Thermal Resistance

|               | θJA       |         |         |             |               |       |

|---------------|-----------|---------|---------|-------------|---------------|-------|

| Product       | Still Air | 1.0 m/s | 2.5 m/s | $\theta$ JC | $\theta_{JB}$ | Units |

| M2S050T-FG896 | 14.7      | 12.5    | 10.9    | 7.2         | 4.9           | °C/W  |

# Theta-JA

Junction-to-ambient thermal resistance ( $\theta_{JA}$ ) is determined under standard conditions specified by JEDEC (JESD-51), but it has little relevance in actual performance of the product. It should be used with caution but is useful for comparing the thermal performance of one package to another.

The maximum power dissipation allowed is calculated using EQ 4.

Maximum Power Allowed =

$$\frac{T_{J(MAX)} - T_{A(MAX)}}{\theta_{JA}}$$

EQ 4

The absolute maximum junction temperature is 100°C. EQ 5 shows a sample calculation of the absolute maximum power dissipation allowed for the M2S050T-FG896 package at commercial temperature and in still air, where

$\theta_{JA}$  = 14.7°C/W (taken from Table 2-3 on page 2-3).

$T_A = 85^{\circ}C$

Maximum Power Allowed =

$$\frac{100^{\circ}C - 85^{\circ}C}{14.7^{\circ}C/W} = 1.088 \text{ W}$$

EQ 5

The power consumption of a device can be calculated using the Microsemi SoC Products Group power calculator. The device's power consumption must be lower than the calculated maximum power dissipation by the package. If the power consumption is higher than the device's maximum allowable power dissipation, a heat sink can be attached on top of the case, or the airflow inside the system must be increased.

### Theta-JB

Junction-to-board thermal resistance ( $\theta_{JB}$ ) measures the ability of the package to dissipate heat from the surface of the chip to the PCB. As defined by the JEDEC (JESD-51) standard, the thermal resistance from junction to board uses an isothermal ring cold plate zone concept. The ring cold plate is simply a means to generate an isothermal boundary condition at the perimeter. The cold plate is mounted on a JEDEC standard board with a minimum distance of 5.0 mm away from the package edge.

### Theta-JC

Junction-to-case thermal resistance ( $\theta_{JC}$ ) measures the ability of a device to dissipate heat from the surface of the chip to the top or bottom surface of the package. It is applicable for packages used with external heat sinks. Constant temperature is applied to the surface in consideration and acts as a boundary condition. This only applies to situations where all or nearly all of the heat is dissipated through the surface in consideration.

# **Calculating Power Dissipation**

# **Quiescent Supply Current**

### Table 2-4 • Quiescent Supply Current Characteristics

|           |                   | M2S050T     |       |

|-----------|-------------------|-------------|-------|

| Parameter | Modes             | VDD = 1.2 V | Units |

| IDC1      | Active mode       | 7.5         | mA    |

| IDC2      | Standby mode      | 7.5         | mA    |

| IDC3      | Flash*Freeze mode | 0.387       | mA    |

## I/O Power

# Table 2-5 • Summary of I/O Input Buffer Power (per pin) Using Default Software Setting with Technology Selected

|                                 | MSIO I          | /O Bank          | MSIOD           | l/O Bank         | DDR I           | /O Bank          |       |

|---------------------------------|-----------------|------------------|-----------------|------------------|-----------------|------------------|-------|

|                                 | Static<br>Power | Dynamic<br>Power | Static<br>Power | Dynamic<br>Power | Static<br>Power | Dynamic<br>Power |       |

|                                 | PDC8<br>(mW)    | PAC9<br>(µW/MHz) | PDC8<br>(mW)    | PAC9<br>(µW/MHz) | PDC8<br>(mW)    | PAC9<br>(µW/MHz) | Notes |

| Single Ended I/O Standards      |                 |                  |                 |                  |                 |                  |       |

| 1.2 V LVCMOS (JESD8-11)         | 0.00            | 11.72            | 0.00            | 11.72            | 0.00            | 11.72            |       |

| 1.5 V LVCMOS (JESD8-11)         | 0.00            | 8.32             | 0.00            | 8.32             | 0.00            | 8.32             |       |

| 1.8 V LVCMOS                    | 0.00            | 10.69            | 0.00            | 10.69            | 0.00            | 10.69            |       |

| 2.5 V LVCMOS                    | 0.00            | 4.14             | 0.00            | 4.14             | 0.00            | 4.14             |       |

| 3.3 V LVTTL / 3.3 V LVCMOS      | 0.00            | 5.47             | -               | -                | -               | -                |       |

| 3.3 V PCI/PCIX                  | 0.00            | 1.82             | -               | -                | -               | -                |       |

| Memory Interface and Voltage R  | eference S      | tandard          |                 |                  |                 | •                |       |

| HSTL 1.5 V                      | 2.21            | 5.57             | 2.21            | 5.57             | 2.21            | 5.57             |       |

| HSTL 1.5 V – True differential  | 1.25            | 47.38            | 1.25            | 47.38            | 1.25            | 47.38            |       |

| SSTL2/DDR                       | 10.02           | 42.68            | 10.02           | 42.68            | 10.02           | 42.68            |       |

| SSTL2/DDR – True differential   | 4.39            | 12.35            | 4.39            | 12.35            | 4.39            | 12.35            |       |

| SSTL18/DDR2                     | 3.88            | 3.81             | 3.88            | 3.81             | 3.88            | 3.81             |       |

| SSTL18/DDR2 – True differential | 1.97            | 56.80            | 1.97            | 56.80            | 1.97            | 56.80            |       |

| SSTL15/DDR3                     | _               | _                | -               | -                | 2.20            | 18.00            |       |

| SSTL15/DDR3 – True differential | _               | _                | -               | -                | 1.23            | 46.81            |       |

| LPDDR                           | _               | _                | -               | -                | 3.88            | 4.46             |       |

| LPDDR – True differential       | _               | _                | -               | -                | 1.97            | 5.08             |       |

| Differential Standards          |                 |                  |                 |                  |                 | •                |       |

| LVDS                            | 5.74            | 17.65            | 5.74            | 17.65            | _               | -                |       |

| B-LVDS                          | 5.65            | 8.76             | 5.65            | 8.76             | -               | -                |       |

| M-LVDS                          | 5.65            | 8.76             | 5.65            | 8.76             | -               | -                |       |

| RSDS                            | 5.74            | 0.93             | 5.74            | 0.93             | -               | -                |       |

| Mini-LVDS                       | TBD             | TBD              | TBD             | TBD              | _               | -                |       |

| LVPECL                          | TBD             | TBD              | -               | -                | -               | -                |       |

# Table 2-6 • Summary of I/O Output Buffer Power (per pin) Default Software Setting with Technology selected

|                                                            |                 | /O Bank          | MSIOD           | I/O Bank         | DDR I           | /O Bank          |       |

|------------------------------------------------------------|-----------------|------------------|-----------------|------------------|-----------------|------------------|-------|

|                                                            | Static<br>Power | Dynamic<br>Power | Static<br>Power | Dynamic<br>Power | Static<br>Power | Dynamic<br>Power |       |

|                                                            | PDC9<br>(mW)    | PAC9<br>(µW/MHz) | PDC9<br>(mW)    | PAC9<br>(µW/MHz) | PDC9<br>(mW)    | PAC9<br>(µW/MHz) | Notes |

| Single Ended I/O Standards                                 |                 |                  |                 | _                |                 | -                |       |

| 1.2 V LVCMOS (JESD8-11)                                    | 0.00            | 16.74            | 0.00            | 16.74            | 0.00            | 16.74            |       |

| 1.5 V LVCMOS (JESD8-11)                                    | 0.00            | 26.31            | 0.00            | 26.31            | 0.00            | 26.31            |       |

| 1.8 V LVCMOS                                               | 0.00            | 38.23            | 0.00            | 38.23            | 0.00            | 38.23            |       |

| 2.5 V LVCMOS                                               | 0.00            | 75.35            | 0.00            | 75.35            | 0.00            | 75.35            |       |

| 3.3 V LVTTL / 3.3 V LVCMOS                                 | 0.00            | 137.04           | _               | _                | 1               | _                |       |

| 3.3 V PCI/PCIX                                             | 0.00            | TBD              | _               | _                | -               | _                |       |

| Memory Interface and Voltage Reference Stat                | ndard           |                  |                 | <u>.</u>         | -               |                  |       |

| HSTL 1.5 V Class I                                         | 6.45            | 60.17            | 6.45            | 60.17            | 6.45            | 60.17            |       |

| HSTL 1.5 V Class I – True differential                     | 12.90           | 80.30            | 12.90           | 80.30            | 12.90           | 80.30            |       |

| HSTL 1.5 V Class II                                        | I               | -                | _               | -                | 12.56           | 104.21           |       |

| HSTL 1.5 V Class II – True differential                    | -               | -                | -               | -                | 25.08           | 87.09            |       |

| SSTL2 Class I / DDR Reduced Drive                          | 18.12           | 76.44            | 18.12           | 76.44            | 18.12           | 76.44            |       |

| SSTL2 Class I / DDR Reduced Drive<br>– True differential   | 36.16           | 218.81           | 36.16           | 218.81           | 36.16           | 218.81           |       |

| SSTL2 Class II / DDR Full Drive                            | 37.20           | 317.68           | 37.20           | 317.68           | 37.20           | 317.68           |       |

| SSTL2 Class II / DDR Full Drive<br>– True differential     | 74.41           | 110.90           | 74.41           | 110.90           | 74.41           | 110.90           |       |

| SSTL18 Class I / DDR2 Reduced Drive                        | 9.06            | 15.09            | 9.06            | 15.09            | 9.06            | 15.09            |       |

| SSTL18 Class I / DDR2 Reduced Drive<br>– True differential | 18.09           | 56.33            | 18.09           | 56.33            | 18.09           | 56.33            |       |

| SSTL18 Class II / DDR2 Full Drive                          | 18.63           | 170.66           | 18.63           | 170.66           | 18.63           | 170.66           |       |

| SSTL18 Class II / DDR2 Full Drive<br>– True differential   | 37.28           | 9.12             | 37.28           | 9.12             | 37.28           | 9.12             |       |

| SSTL15 Class I / DDR3 Reduced Drive                        | -               | -                | _               | -                | 11.28           | 62.13            |       |

| SSTL15 Class I / DDR3 Reduced Drive<br>– True differential | -               | -                | -               | -                | 22.52           | 131.80           |       |

| SSTL15 Class II / DDR3 Full Drive                          | -               | -                | -               | -                | 12.15           | 47.65            |       |

| SSTL15 Class II / DDR3 Full Drive<br>– True differential   | -               | -                | -               | -                | 24.29           | 142.98           |       |

| LPDDR Reduced Drive                                        | -               | -                | _               | -                | 18.62           | 331.33           |       |

| LPDDR Reduced Drive – True differential                    | -               | -                | _               | -                | 37.28           | 9.12             |       |

| LPDDR Full Drive                                           | _               | -                | _               | -                | 9.06            | 46.40            |       |

| LPDDR Full Drive – True differential                       | _               | -                | _               | -                | 18.09           | 56.33            |       |

| Differential Standards                                     |                 |                  |                 |                  |                 |                  |       |

| LVDS                                                       | 13.48           | 63.84            | 13.48           | 63.84            | _               | _                |       |

| B-LVDS                                                     | 18.37           | 30.73            | _               | -                | _               | _                |       |

| M-LVDS                                                     | 18.37           | 30.73            | _               | -                | _               | _                |       |

| RSDS                                                       | 8.50            | 82.76            | 8.50            | 82.76            | -               | -                |       |

| Mini-LVDS                                                  | TBD             | TBD              | TBD             | TBD              | _               | _                |       |

# **Power Consumption of Various Internal Resources**

### Table 2-7 • Different Components Contributing to Dynamic Power Consumption in SmartFusion2 Devices

|        |                                                                                                             | Powe | er Supply                | Device                   |        |       |

|--------|-------------------------------------------------------------------------------------------------------------|------|--------------------------|--------------------------|--------|-------|

| Param. | Definition                                                                                                  | Name | Domain                   | M2S050T                  | Units  | Notes |

| PAC1   | Global Clock contribution of a GB                                                                           | VDD  | 1.2 V                    | 3.50                     | µW/MHz |       |

| PAC2   | Global Clock contribution of a RGB                                                                          | VDD  | 1.2 V                    | 0.87                     | µW/MHz |       |

| PAC3   | Global Clock contribution of a sequential module.                                                           | VDD  | 1.2 V                    | 0.02                     | µW/MHz |       |

| PAC4   | Clock contribution of a sequential module.                                                                  | VDD  | 1.2 V                    | 0.01                     | µW/MHz |       |

| PAC5   | Data contribution of a sequential module.                                                                   | VDD  | 1.2 V                    | 0.06965                  | µW/MHz |       |

| PAC6   | Average contribution of a combinatorial module.                                                             | VDD  | 1.2 V                    | 0.709                    | µW/MHz |       |

| PAC7   | Average contribution of a combinatorial module with carry chain.                                            | VDD  | 1.2 V                    | 0.821657                 | µW/MHz |       |

| PAC8   | Average contribution of a routing net.                                                                      | VDD  | 1.2 V                    | 0.87                     | µW/MHz |       |

| PAC9   | Contribution of an I/O input pin (standard dependent)                                                       | VDDI | Table 2-5<br>on page 2-5 | Table 2-5<br>on page 2-5 | -      |       |

| PAC10  | Contribution of an I/O output pin (standard dependent)                                                      | VDDI | Table 2-6<br>on page 2-6 | Table 2-6<br>on page 2-6 | _      |       |

| PAC11  | Average contribution of a uSRAM block during a read operation.                                              | VDD  | 1.2 V                    | 2.39                     | µW/MHz |       |

| PAC12  | Average contribution of a uSRAM block during a write operation.                                             | VDD  | 1.2 V                    | 7.01                     | µW/MHz |       |

| PAC13  | Average contribution of a LSRAM block during a read operation.                                              | VDD  | 1.2 V                    | 19.85                    | µW/MHz |       |

| PAC14  | Average contribution of a LSRAM block during a write operation.                                             | VDD  | 1.2 V                    | 24.85                    | µW/MHz |       |

| PAC15  | CCC contribution                                                                                            | VDD  | 1.2 V                    | 8.00                     | mW     |       |

| PAC16  | Main Crystal Oscillator contribution                                                                        | VDD  | 1.2 V                    | 55.51                    | µW/MHz |       |

| PAC17  | 1 MHz RC Oscillator contribution                                                                            | VDD  | 1.2 V                    | 37.2                     | mW     |       |

| PAC18  | 50 MHz RC Oscillator contribution                                                                           | VDD  | 1.2 V                    | 7.30                     | mW     |       |

| PAC19  | Math Block contribution                                                                                     | VDD  | 1.2 V                    | TBD                      | mW     |       |

| PAC20  | MSS Dynamic Power Contribution with<br>MDDR/USB/Ethernet OFF,<br>Clock Frequency = 100 MHz                  | VDD  | 1.2 V                    | 91.986                   | mW     | 1     |

| PAC21  | MSS Dynamic Power Contribution with USB/Ethernet<br>OFF, Clock Frequency = 100 MHz,<br>MDDR mode–MSS Bridge | VDD  | 1.2 V                    | 137.43                   | mW     | 1     |

Notes:

1. For a different use of MSS peripherals and resources, refer to SmartPower.

2. Dynamic power contribution of FDDR does not include the DDRIO power. Use I/O power for calculation of I/O power. For a different use of the FDDR, refer to SmartPower.

3. For a different use of the SERDES block, refer to SmartPower.

### Table 2-7 • Different Components Contributing to Dynamic Power Consumption in SmartFusion2 Devices (continued)

|        |                                                                                       | Power Supply |        | Device  |       |       |

|--------|---------------------------------------------------------------------------------------|--------------|--------|---------|-------|-------|

| Param. | Definition                                                                            | Name         | Domain | M2S050T | Units | Notes |

| PAC22  | FDDR Dynamic Power Contribution<br>with frequency = 100 MHz, DDR Clock Multiplier = 2 | VDD          | 1.2 V  | 108.81  | mW    | 2     |

| PAC23  | SERDES Dynamic Power Contribution configured as PCIe_GEN1 with 1 Lane at 125 MHz      | VDD          | 1.2 V  | 91.70   | mW    | 3     |

Notes:

1. For a different use of MSS peripherals and resources, refer to SmartPower.

- 2. Dynamic power contribution of FDDR does not include the DDRIO power. Use I/O power for calculation of I/O power. For a different use of the FDDR, refer to SmartPower.

- 3. For a different use of the SERDES block, refer to SmartPower.

### Table 2-8 • Different Components Contributing to the Static Power Consumption in SmartFusion Devices

|        |                                                                                 | Power Supply |        |              | Device                       |       |

|--------|---------------------------------------------------------------------------------|--------------|--------|--------------|------------------------------|-------|

| Param. | Definition                                                                      | Name         | Domain | Mode         | M2S050T                      | Units |

| PDC1   | Core static power contribution in Active Operating mode                         | VDD          | 1.2 V  | Active       | 9.000                        | mW    |

| PDC2   | Core static power contribution in Standby<br>Operating mode                     | VDD          | 1.2 V  | Standby      | 9.000                        | mW    |

| PDC3   | Core static power contribution in Flash*Freeze<br>Operating mode                | VDD          | 1.2 V  | Flash*Freeze | 0.465                        | mW    |

| PDC4   | LSRAM static power contribution in Flash*Freeze configured in "Sleep" State     | VDD          | 1.2 V  | Flash*Freeze | 1.250                        | uW    |

| PDC5   | LSRAM static power contribution in Flash*Freeze configured in "Suspended" State | VDD          | 1.2 V  | Flash*Freeze | 10.140                       | uW    |

| PDC6   | USRAM static power contribution in Flash*Freeze configured in "Sleep" State     | VDD          | 1.2 V  | Flash*Freeze | 0.500                        | uW    |

| PDC7   | USRAM static power contribution in Flash*Freeze configured in "Suspend" State   | VDD          | 1.2 V  | Flash*Freeze | 4.970                        | uW    |

| PDC8   | I/O Input static power contribution in Active<br>Operating mode                 | VDDI         | VDDI   | Active       | See Table 2-5<br>on page 2-5 | uW    |

| PDC9   | I/O Output static power contribution in Active Operating mode                   | VDDI         | VDDI   | Active       | See Table 2-6<br>on page 2-6 | uW    |

# **Power Methodology**

This section describes a simplified method to estimate power consumption of an application. For more accurate and detailed power estimations, use the SmartPower tool in the Libero IDE software. The power calculation methodology described below uses the following variables:

- The number of PLLs/CCCs as well as the number and the frequency of each output clock generated

- · The number of combinatorial and sequential cells used in the design

- The internal clock frequencies

- The number and the standard of I/O pins used in the design

- · The number of RAM blocks used in the design

- Toggle rates of I/O pins as well as the logic module—guidelines are provided in Table 2-9 on page 2-13.

- Enable rates of output buffers—guidelines are provided for typical applications in Table 2-10 on page 2-13.

- Read rate and write rate to the memory—guidelines are provided for typical applications in Table 2-10 on page 2-13.

The calculation should be repeated for each clock domain defined in the design.

### Methodology

### Total Power Consumption—PTOTAL

### Active, Standby and Flash\*Freeze Mode