## **Load-Dump/Reverse-Voltage Protection Circuits**

### **General Description**

The MAX16128/MAX16129 load-dump/reverse-voltage protection circuits protect power supplies from damaging input-voltage conditions, including overvoltage, reverse-voltage, and high-voltage transient pulses. Using a built-in charge pump, the devices control two external back-to-back n-channel MOSFETs that turn off and isolate downstream power supplies during damaging input conditions, such as an automotive load-dump pulse or a reverse-battery condition. Operation is guaranteed down to 3V that ensures proper operation during automotive cold-crank conditions. These devices feature a flag output (FLAG) that asserts during fault conditions.

For reverse-voltage protection, external back-to-back MOSFETs outperform the traditional reverse-battery diode, minimizing the voltage drop and power dissipation during normal operation.

The devices use fixed overvoltage and undervoltage thresholds, minimizing the external component count.

The MAX16129 provides limiter-mode fault management for overvoltage and thermal-shutdown conditions; whereas the MAX16128 provides switch-mode fault management for overvoltage and thermal shutdown conditions. In the limiter mode, the output voltage is limited and FLAG is asserted low during a fault. In the switch mode, the external MOSFETs are switched off and FLAG is asserted low after a fault. The switch mode is available in four options—Latch mode, 1 Autoretry mode, 3 Autoretry mode, and Always autoretry mode.

The MAX16128/MAX16129 are available in an 8-pin  $\mu MAX^{(\!R\!)}$  package and operate over the automotive temperature range (-40°C to +125°C).

### Applications

Automotive Industrial Avionics Telecom/Server/Networking

### **Features**

- Operates Down to +3V, Riding Out Cold-Crank Conditions

- ♦ -36V to +90V Wide Input-Voltage Protection Range

- Minimal Operating Voltage Drop Reverse-Voltage Protection

- Fast Gate Shutoff During Fault Conditions with Complete Load Isolation

- Fixed Undervoltage/Overvoltage Thresholds

- Thermal Shutdown Protection

- Low Supply Current and Low Shutdown Current

- Internal Charge-Pump Circuit Enhances External n-Channel MOSFET

- ♦ FLAG Output Identifies Fault Condition

- Automotive Qualified

- ♦ -40°C to +125°C Operating Temperature Range

- ♦ Available in 3mm x 3mm, 8-Pin µMAX Package

Ordering Information appears at end of data sheet.

µMAX is a registered trademark of Maxim Integrated Products, Inc.

## **Load-Dump/Reverse-Voltage Protection Circuits**

### **ABSOLUTE MAXIMUM RATINGS**

(All pins referenced to GND.)

| IN                               | 36V to +90V                              |

|----------------------------------|------------------------------------------|

| SHDN                             | 0.3V to max (0V, V <sub>IN</sub> + 0.3V) |

| SRC, GATE                        | 36V to +45V                              |

| SRC to GATE                      | 36V to +30V                              |

| OUT                              | -0.3V to +45V                            |

| FLAG                             | 0.3V to +45V                             |

| Continuous Sink/Source (all pins | s)±100mA                                 |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) ( | (multilayer board) |

|---------------------------------------------------------|--------------------|

| µMAX (derate 12.9mW/°C above +70°C)                     | 1030.9mW           |

| Operating Temperature Range                             | -40°C to +125°C    |

| Junction Temperature                                    | +150°C             |

| Storage Temperature Range                               | -60°C to +150°C    |

| Lead Temperature (soldering, 10s)                       | +300°C             |

| Soldering Temperature (reflow)                          | +260°C             |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## PACKAGE THERMAL CHARACTERISTICS (Note 1)

μΜΑΧ

Junction-to-Ambient Thermal Resistance  $(\theta_{JA})$  ......77.6°C/W

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/thermal-tutorial</u>.

### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 12V, C_{GATE-SOURCE} = 1nF, T_A = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at T\_A = +25°C.) (Note 2)

| PARAMETER                                     | SYMBOL              | CONDITIONS             |                                      | MIN                       | ТҮР                       | MAX                       | UNITS |

|-----------------------------------------------|---------------------|------------------------|--------------------------------------|---------------------------|---------------------------|---------------------------|-------|

| Input Voltage Denge                           |                     | Operating range        |                                      | 3                         |                           | 30                        | V     |

| Input Voltage Range                           | V <sub>IN</sub>     | Protection ran         | Protection range                     |                           |                           | +90                       | V     |

|                                               |                     |                        | $V_{IN} = V_{SRC} = V_{IN} =$<br>12V |                           | 224                       | 320                       | - μΑ  |

|                                               |                     | SHDN = high            | $V_{IN} = V_{SRC} = V_{IN} = 30V$    |                           | 260                       | 380                       |       |

| Input Supply Current                          | IIN                 |                        | $V_{IN} = V_{SRC} = V_{IN} =$<br>12V |                           | 34                        | 50                        |       |

|                                               |                     | SHDN = low             | $V_{IN} = V_{SRC} = V_{IN} =$<br>30V |                           | 64                        | 100                       |       |

|                                               |                     | $V_{IN} = V_{SRC} =$   | 12V                                  |                           | 36                        | 200                       | 0     |

| SRC Input Current                             | ISRC                | $V_{IN} = V_{SRC} =$   | 30V                                  |                           | 240                       | 350                       | μA    |

| Internal Undervoltage Threshold               | V <sub>UV_TH</sub>  | V <sub>IN</sub> rising |                                      | 0.97 x<br>V <sub>UV</sub> | V <sub>UV</sub>           | 1.03 x<br>V <sub>UV</sub> | V     |

| Internal Undervoltage-Threshold<br>Hysteresis | V <sub>UV_HYS</sub> |                        |                                      |                           | 0.05 x<br>V <sub>UV</sub> |                           | V     |

| Internal Overvoltage Threshold                | V <sub>OV_TH</sub>  | V <sub>IN</sub> rising |                                      | 0.97 x<br>V <sub>OV</sub> | V <sub>OV</sub>           | 1.03 x<br>V <sub>OV</sub> | V     |

| Internal Overvoltage-Threshold<br>Hysteresis  | V <sub>OV_HYS</sub> |                        |                                      |                           | 0.05 x<br>V <sub>OV</sub> |                           | V     |

# Load-Dump/Reverse-Voltage Protection Circuits

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 12V, C_{GATE-SOURCE} = 1nF, T_A = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                       | SYMBOL               | CONDITIONS                                                                                                                                                                                                                                                                                                                | MIN                        | ТҮР                        | MAX                        | UNITS |

|-------------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------|----------------------------|-------|

| Internal Cold-Crank Threshold                   | V <sub>CCK</sub>     | V <sub>IN</sub> falling                                                                                                                                                                                                                                                                                                   | 0.97 x<br>V <sub>CCK</sub> | V <sub>CCK</sub>           | 1.03 х<br>V <sub>CCK</sub> | V     |

| Internal Cold-Crank Threshold Hysteresis        | V <sub>CCK_HYS</sub> |                                                                                                                                                                                                                                                                                                                           |                            | 0.05 x<br>V <sub>CCK</sub> |                            | V     |

| OUT Input Resistance to Ground                  | R <sub>OUT</sub>     | MAX16128                                                                                                                                                                                                                                                                                                                  |                            | 4                          |                            | mΩ    |

|                                                 | 1001                 | MAX16129                                                                                                                                                                                                                                                                                                                  |                            | 2                          |                            |       |

| POK Threshold Rising                            | V <sub>POK+</sub>    |                                                                                                                                                                                                                                                                                                                           |                            | $0.9 \times V_{IN}$        |                            | V     |

| POK Threshold Falling                           | V <sub>POK-</sub>    |                                                                                                                                                                                                                                                                                                                           |                            | 0.87 x<br>V <sub>IN</sub>  |                            | V     |

| Startup Response Time                           | t <sub>START</sub>   | (Note 3)                                                                                                                                                                                                                                                                                                                  |                            | 150                        |                            | μs    |

| Autoretry Timeout                               | t <sub>RETRY</sub>   |                                                                                                                                                                                                                                                                                                                           |                            | 150                        |                            | ms    |

| GATE Rise Time                                  | t <sub>RISE</sub>    | $V_{GATE}$ rising (GND to $V_{SRC}$ + 8V)                                                                                                                                                                                                                                                                                 |                            | 1                          | -                          | ms    |

| Overvoltage-to-GATE Propagation Delay           | tovg                 | $ \begin{array}{l} V_{\text{IN}} \text{ rising (MAX16128) from} \\ (0.9 \times V_{\text{OV}_{\text{TH}}}) \text{ to (1.1 } \times V_{\text{OV}_{\text{TH}}}), \\ V_{\text{OUT}} \text{ rising (MAX16129) from} \\ (0.9 \times V_{\text{OV}_{\text{TH}}}) \text{ to (1.1 } \times V_{\text{OV}_{\text{TH}}}) \end{array} $ |                            | 1                          |                            | μs    |

| Undervoltage-to-GATE Propagation<br>Delay       | tuvg                 | $V_{IN}$ falling from (1.1 x $V_{UV_{TH}}$ ) to (0.9 x $V_{UV_{TH}}$ )                                                                                                                                                                                                                                                    | 21                         |                            |                            | μs    |

| Overvoltage to FLAG Propagation Delay           | t <sub>OV</sub>      | $ \begin{array}{l} V_{\text{IN}} \text{ rising (MAX16128) from} \\ (0.9 \times V_{\text{OV}_{\text{TH}}}) \text{ to (1.1 } \times V_{\text{OV}_{\text{TH}}}) \\ V_{\text{OUT}} \text{ rising (MAX16129) from} \\ (0.9 \times V_{\text{OV}_{\text{TH}}}) \text{ to (1.1 } \times V_{\text{OV}_{\text{TH}}}) \end{array} $  | 1                          |                            |                            | μs    |

|                                                 |                      | $V_{IN} = V_{SRC} = V_{OUT} = 3V,$<br>$I_{GATE} = -1\mu A$                                                                                                                                                                                                                                                                | 5                          | 5                          | 5.5                        |       |

| GATE Output Voltage High Above V <sub>SRC</sub> | Vee                  | $V_{IN} = V_{SRC} = V_{OUT} = 12V,$<br>$I_{GATE} = -1\mu A$                                                                                                                                                                                                                                                               | 8                          | 9                          | 10                         | V     |

| arrie output voltage high ribove vSHC           | V <sub>GS</sub>      | $V_{IN} = V_{SRC} = V_{OUT} = 24V,$<br>$I_{GATE} = -1\mu A$                                                                                                                                                                                                                                                               | 7                          | 8.5                        | 10                         | v     |

|                                                 |                      | $V_{IN} = V_{SRC} = V_{OUT} = 30V,$<br>$I_{GATE} = -1\mu A$                                                                                                                                                                                                                                                               | 6.25                       | 8                          | 9.5                        |       |

| GATE Pulldown Current                           | I <sub>PD</sub>      | V <sub>GATE</sub> = 12V                                                                                                                                                                                                                                                                                                   | 8.8                        |                            |                            | mA    |

| GATE Charge-Pump Current                        | IGATE                | $V_{IN} = V_{GATE} = V_{SRC} = 12V$                                                                                                                                                                                                                                                                                       | 180                        |                            |                            | μA    |

| Thermal Shutdown                                | T+                   |                                                                                                                                                                                                                                                                                                                           | +145                       |                            | °C                         |       |

| Thermal-Shutdown Hysteresis                     | ΔΤ                   |                                                                                                                                                                                                                                                                                                                           |                            | 15                         |                            | °C    |

| SHDN Logic-High Input Voltage                   | VIH                  |                                                                                                                                                                                                                                                                                                                           | 1.4                        |                            |                            | V     |

| SHDN Logic-Low Input Voltage                    | VIL                  |                                                                                                                                                                                                                                                                                                                           |                            |                            | 0.4                        | V     |

**Typical Operating Characteristics**

# Load-Dump/Reverse-Voltage Protection Circuits

### **ELECTRICAL CHARACTERISTICS (continued)**

(VIN = 12V, CGATE-SOURCE = 1nF, TA = -40°C to +125°C, unless otherwise noted. Typical values are at TA = +25°C.) (Note 2)

| PARAMETER                   | SYMBOL           | CONDITIONS                  | MIN | TYP | MAX | UNITS |

|-----------------------------|------------------|-----------------------------|-----|-----|-----|-------|

| SHDN Input Pulse Width      | t <sub>PW</sub>  |                             | 6   |     |     | μs    |

| SHDN Input Pulldown Current | I <sub>SPD</sub> |                             |     | 0.8 | 1.2 | μA    |

| FLAG Output Voltage Low     | V <sub>OL</sub>  | FLAG sinking 1mA            |     |     | 0.4 | V     |

| FLAG Leakage Current        | ١                | $V_{\overline{FLAG}} = 12V$ |     |     | 0.5 | μA    |

Note 2: All parameters are production tested at  $T_A = +25$  °C. Limits over the operating temperature range are guaranteed by design and characterization.

**Note 3:** The MAX16128/MAX16129 power up with the external MOSFETs in off mode ( $V_{GATE} = V_{SRC}$ ). The external MOSFETs turn on t<sub>START</sub> after the devices are powered up and all input conditions are valid.

#### SUPPLY CURRENT SHUTDOWN SUPPLY CURENT vs. SUPPLY VOLTAGE **SUPPLY CURRENT vs. TEMPERATURE** vs. SUPPLY VOLTAGE 300 310 100 SHDN = HIGH SHDN = HIGH 90 SHDN = LOW 290 GATE ENHANCED GATE ENHANCED 250 80 270 SUPPLY CURRENT (µA) SUPPLY CURRENT (µA) SUPPLY CURRENT (µA) 70 250 200 60 230 50 150 210 40 190 30 100 170 20 50 150 10 0 80 15 21 27 13 23 33 -40 -20 20 40 60 100 120 3 9 3 SUPPLY VOLTAGE (V) TEMPERATURE (°C) SUPPLY VOLTAGE (V) SHUTDOWN SUPPLY CURRENT **SHDN PULLDOWN CURRENT** vs. TEMPERATURE vs. TEMPERATURE 50 1.0 0.9 SHDN = LOW 45 SHDN PULLDOWN CURRENT (µA) 0.8 40 SUPPLY CURRENT (µA) 0.7 35 0.6 30 0.5 0.4 25 0.3 20 0.2 15 0.1 10 0 -40 -25 -10 5 20 35 50 65 80 95 110 125 -40 -25 -10 5 20 35 50 65 80 95 110 125 TEMPERATURE (°C) TEMPERATURE (°C)

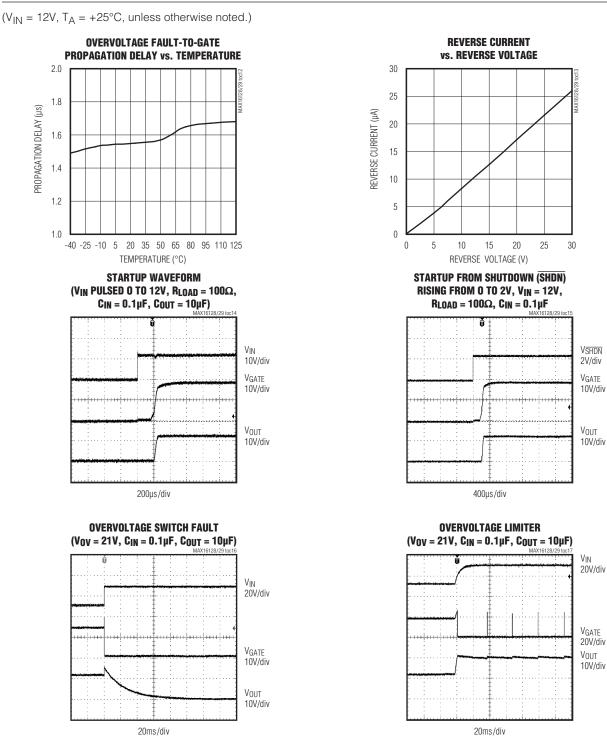

( $V_{IN}$  = 12V,  $T_A$  = +25°C, unless otherwise noted.)

## **Load-Dump/Reverse-Voltage Protection Circuits**

### **Typical Operating Characteristics (continued)**

Maxim Integrated

## **Load-Dump/Reverse-Voltage Protection Circuits**

### **Typical Operating Characteristics (continued)**

# Load-Dump/Reverse-Voltage Protection Circuits

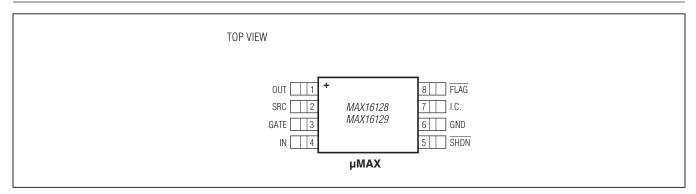

## **Pin Configuration**

### **Pin Description**

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | OUT  | Output Voltage-Sense Input. Connect OUT to the load with a 100 $\!\Omega$ series resistor. Bypass with a minimum 10 $\!\mu\text{F}$ capacitor to GND.                                                                                                                                                                                                                                                                                                  |

| 2   | SRC  | Source Input. Connect SRC to the common source connection of the external MOSFETs. When the MOSFETs are turned off, this connection is clamped to GND. An external zener diode between SRC and GATE protects the gates of the external MOSFETs.                                                                                                                                                                                                        |

| 3   | GATE | Gate-Driver Output. Connect GATE to the gates of the external n-channel MOSFETs. GATE is the charge-<br>pump output during normal operation. GATE is quickly pulled low during a fault condition or when SHDN<br>is pulled low.                                                                                                                                                                                                                        |

| 4   | IN   | Positive Supply Input Voltage. Connect IN to the positive side of the input voltage. Bypass IN with a $0.1\mu$ F ceramic capacitor to GND.                                                                                                                                                                                                                                                                                                             |

| 5   | SHDN | Shutdown Input. Drive $\overline{SHDN}$ low to force GATE and $\overline{FLAG}$ low and turn off the external n-channel MOSFETs. Connect a 100k $\Omega$ resistor from $\overline{SHDN}$ to IN for normal operation.                                                                                                                                                                                                                                   |

| 6   | GND  | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7   | I.C. | Internally connected to GND                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8   | FLAG | $\overline{\text{FLAG}}$ Output. During startup, $\overline{\text{FLAG}}$ is low as long as V <sub>OUT</sub> is lower than 90% of V <sub>IN</sub> and after that it is high impedance. It asserts low during shutdown mode, an overvoltage, thermal shutdown, or undervoltage fault or when V <sub>OUT</sub> falls below 90% of V <sub>IN</sub> . $\overline{\text{FLAG}}$ asserts low during a cold-crank fault to signal reverse-current protection. |

## **Load-Dump/Reverse-Voltage Protection Circuits**

### **Detailed Description**

The MAX16128/MAX16129 transient protection circuits are suitable for automotive and industrial applications where high-voltage transients are commonly present on supply voltage inputs. The devices monitor the input voltage and control two external common-source n-channel MOSFETs to protect downstream voltage regulators during loaddump events or other automotive pulse conditions.

The devices feature an overvoltage and an undervoltage comparator for voltage window detection. A flag output (FLAG) asserts when a fault event occurs.

Two external back-to-back n-channel MOSFETs provide reverse-voltage protection and also prevent reverse current during a fault condition. Compared to a traditional reverse-battery diode, this approach minimizes power dissipation and voltage drop.

The MAX16129 provides a limiter-mode fault management for overvoltage and thermal-shutdown conditions, whereas the MAX16128 provides switch-mode fault management for overvoltage and thermal-shutdown conditions. In the limiter mode, the MOSFETs cycle on and off so the output voltage is limited. In the switch mode, the external MOSFETs are switched off, disconnecting the load from the input. In both cases, FLAG asserts to indicate a fault.

### **Gate Charge Pump**

The devices use a charge pump to generate the GATE to SRC voltage and enhance the external MOSFETs. After the input voltage exceeds the input undervoltage threshold, the charge pump turns on after a 150µs delay.

During a fault condition, GATE is pulled to ground with an 8.8mA (min) pulldown current. Note that an external zener diode is required to be connected between the gate and source of the external MOSFETs (see the *Applications Information* section).

#### **Overvoltage Protection**

The devices detect overvoltage conditions using a comparator that is connected through an internal resistive divider to the input or output voltage. An overvoltage condition causes the GATE output to go low, turning off the external MOSFETs. FLAG also asserts to indicate the fault condition.

### Overvoltage Limiter (MAX16129)

In overvoltage-limiter mode, the output voltage is regulated at the overvoltage-threshold voltage and continues to supply power to downstream devices. In this mode, the device operates like a voltage regulator.

During normal operation, GATE is enhanced 9V above SRC. The output voltage is monitored through an internal resistive divider. When OUT rises above the overvoltage threshold, GATE goes low and the MOSFETs turn off. As the voltage on OUT falls below the overvoltage threshold minus the threshold hysteresis, GATE goes high and the MOSFETs turn back on again, regulating OUT in a switched-linear mode at the overvoltage threshold.

The switching frequency depends on the gate charge of the MOSFETs, the charge-pump current, the output load current, and the output capacitance.

Caution must be exercised when operating the MAX16129 in voltage-limiting mode for long durations. Since MOSFETs can dissipate power continuously during this interval, proper heatsinking should be implemented to prevent damage to them.

#### Overvoltage Switch (MAX16128)

In the overvoltage switch mode, the internal overvoltage comparator monitors the input voltage and the load is completely disconnected from the input during an overvoltage event. When the input voltage exceeds the overvoltage threshold, GATE goes low and the MOSFETs turn off, disconnecting the input from the load. After that, for the autoretry-mode version, the autoretry timer starts, while for the latched-mode version a power cycle to IN or a cycle on SHDN is needed to turn the external MOSFETs back on.

The MAX16128 can be configured to latch off (suffix D) even after the overvoltage condition ends. The latch is cleared by cycling IN below the undervoltage threshold or by toggling SHDN.

The devices can also be configured to retry:

- One time, then latch off (suffix B)

- Three times, then latch off (suffix C)

- Always retry and never latch off (suffix A)

There is a fixed 150ms (typ) delay between each retry attempt. If the overvoltage-fault condition is gone when a retry is attempted, GATE goes high and power is restored to the downstream circuitry.

## **Load-Dump/Reverse-Voltage Protection Circuits**

#### **Undervoltage Protection**

The devices monitor the input voltage for undervoltage conditions. If the input voltage is below the undervoltage threshold (V<sub>IN</sub> < V<sub>UV-TH</sub> - V<sub>UV-HYS</sub>), GATE goes low, turning off the external MOSFETs and FLAG asserts. When the input voltage exceeds the undervoltage threshold (V<sub>IN</sub> > V<sub>UV\_TH</sub>), GATE goes high after a 150µs delay (typ).

For the MAX16128/MAX16129, the undervoltage threshold is determined by the part number suffix option (see Table 2).

#### **Cold-Crank Monitoring**

Cold-crank faults occur when the input voltage decreases from its steady-state condition. A cold-crank comparator monitors IN through an internal resistive divider. The MAX16128/MAX16129 offer two ways to handle this kind of fault depending on a part number suffix (see the *Selector Guide*):

- The cold-crank comparator is disabled and external MOSFETs stay on during the falling input-voltage transient unless the input voltage falls below the undervoltage threshold (see Table 2).

- The cold-crank comparator is enabled and external MOSFETs are switched off by pulling down GATE if the input voltage falls below the cold-crank threshold to avoid load discharge due to reverse current from OUT to IN (see Table 4).

In the last case, cold-crank protection is enabled as long as V<sub>OUT</sub> is higher than 90% of V<sub>IN</sub> (with a 3% hysteresis) and V<sub>IN</sub> is higher than the undervoltage threshold. When the monitored input voltage falls below the falling cold-crank fault threshold (V<sub>IN</sub> < V<sub>CCK</sub>), the GATE is pulled down and FLAG is asserted low. When the input voltage rises back above the rising cold-crank fault threshold (V<sub>IN</sub> > V<sub>CCK</sub> + V<sub>CLK\_HYS</sub>), FLAG is released and the charge pump enhances GATE above SRC, reconnecting the load to the input.

#### Thermal Shutdown

The devices' thermal-shutdown feature turns off the MOSFETs if the internal die temperature exceeds  $145^{\circ}C$  (T<sub>J</sub>). By ensuring good thermal coupling between the MOSFETs and the devices, the thermal shutdown can turn off the MOSFETs if they overheat.

When the junction temperature exceeds  $T_J = +145^{\circ}C$  (typ), the internal thermal sensor signals the shutdown logic, pulling the GATE voltage low and allowing the device to cool. When  $T_J$  drops by 15°C (typ), GATE goes

Maxim Integrated

high and the MOSFETs turn back on. Do not exceed the absolute maximum junction-temperature rating of  $T_J = +150^{\circ}C$ .

#### Flag Output (FLAG)

An open-drain  $\overline{FLAG}$  output indicates fault conditions. During startup,  $\overline{FLAG}$  is initially low and goes high impedance when  $V_{OUT}$  is greater than 90% of  $V_{IN}$  if no fault conditions are present.  $\overline{FLAG}$  asserts low during shutdown mode, an overvoltage, thermal shutdown, or undervoltage fault, or when  $V_{OUT}$  falls below 90% of  $V_{IN}$ . In the versions where the cold-crank comparator is enabled,  $\overline{FLAG}$  asserts low during a cold-crank fault.

#### **Reverse-Voltage Protection**

The devices integrate reverse-voltage protection, preventing damage to the downstream circuitry caused by battery reversal or negative transients. The devices can withstand reverse voltage to -6V without damage to themselves or the load. During a reverse-voltage condition, the two external n-channel MOSFETs are turned off, protecting the load. Connect a  $0.1\mu$ F ceramic capacitor from IN to GND, connect a  $10\mu$ F capacitor from OUT to GND, and minimize the parasitic capacitance from GATE to SRC, connect a 10 $\mu$ F capacitor from GATE to have fast reverse-battery voltage-transient protection. During normal operation, both MOSFETs are turned on and have a minimal forward-voltage drop, providing lower power dissipation and a much lower voltage drop than a reverse-battery protection diode.

### **Applications Information**

#### Automotive Electrical Transients (Load Dump)

Automotive circuits generally require supply voltage protection from various transient conditions that occur in automotive systems. Several standards define various pulses that can occur. <u>Table 1</u> summarizes the pulses from the ISO 7637-2 specification:

Most of the pulses can be mitigated with capacitors and zener clamp diodes (see the <u>Typical Operating</u> <u>Characteristics</u> and also the <u>Increasing the Operating</u> <u>Voltage Range</u> section). The load dump (pulse 5a and 5b) occurs when the alternator is charging the battery and a battery terminal gets disconnected. Due to the sudden change in load, the alternator goes out of regulation and the bus voltage spikes. The pulse has a rise time of about 10ms and a fall time of about 400ms but can extend out to 1s or more depending on the characteris-

# Load-Dump/Reverse-Voltage Protection Circuits

| NAME DESCRIPTION | PEAK VOLTAGE (V) (max)*        | DURATION                         |                 |

|------------------|--------------------------------|----------------------------------|-----------------|

| NAIVIE           | DESCRIPTION                    | 12V SYSTEM                       | DURATION        |

| Pulse 1          | Inductive load disconnection   | -100                             | 1 to 2ms        |

| Pulse 2a         | Inductive wiring disconnection | 50                               | 0.05ms          |

| Pulse 3a         | Switching transients           | -150                             | 0.000           |

| Pulse 3b         | Switching transients           | 100                              | 0.2µs           |

| Pulse 4          | Cold crank                     | -7                               | 100ms (initial) |

| Puise 4          |                                | -6                               | Up to 20s       |

| Pulse 5a         | Load dump (unsuppressed)       | 87                               | 100ma (aingle)  |

| Pulse 5b         | Load dump (suppressed)         | (Varies, but less than pulse 5a) | 400ms (single)  |

### Table 1. Summary of ISO 7637-2 Pulses

\*Relative to system voltage

tics of the charging system. The magnitude of the pulse depends on the bus voltage and whether the system is unsuppressed or uses central load-dump suppression (generally implemented using very large clamp diodes built into the alternator). <u>Table 1</u> lists the worst-case values from the ISO 7637-2 specification.

Cold crank (pulse 4) occurs when activating the starter motor in cold weather with a marginal battery. Due to the large load imposed by the starter motor, the bus voltage sags. Since the devices can operate down to 3V, the downstream circuitry can continue to operate through a cold-crank condition. If desired, the undervoltage threshold can be increased so that the MOSFETs turn off during a cold crank, disconnecting the downstream circuitry. An output reservoir capacitor can be connected from OUT to GND to provide energy to the circuit during the coldcrank condition.

Refer to the ISO 7637-2 specification for details on pulse waveforms, test conditions, and test fixtures.

### **MOSFET Selection**

MOSFET selection is critical to design a proper protection circuit. Several factors must be taken into account: the gate capacitance, the drain-to-source voltage rating, the on-resistance ( $R_{DS(ON)}$ ), the peak power-dissipation capability, and the average power-dissipation limit. In general, both MOSFETs should have the same part number. For size-constrained applications, a dual MOSFET can save board area. Select the drain-to-source voltage so that the MOSFETs can handle the highest voltage that might be applied to the circuit. Gate capacitance is not as critical but it does determine the maximum turn-on and turn-off time. MOSFETs with more gate capacitance tend to respond more slowly.

### **MOSFET** Power Dissipation

The R<sub>DS(ON)</sub> must be low enough to limit the MOSFET power dissipation during normal operation. Power dissipation (per MOSFET) during normal operation can be calculated using this formula:

### $P = I_{LOAD}^2 \times R_{DS(ON)}$

where P is the power dissipated in each MOSFET and  $I_{\rm LOAD}$  is the average load current.

During a fault condition in switch mode, the MOSFETs turn off and do not dissipate power. Limiter mode imposes the worst-case power dissipation. The average power can be computed using the following formula:

### $\mathsf{P} = \mathsf{I}_{\mathsf{LOAD}} \times (\mathsf{V}_{\mathsf{IN}} - \mathsf{V}_{\mathsf{OUT}})$

where P is the average power dissipated in both MOSFETs,  $I_{LOAD}$  is the average load current,  $V_{IN}$  is the input voltage, and  $V_{OUT}$  is the average limited voltage on the output. In limiter mode, the output voltage is a sawtooth wave with characteristics determined by the  $R_{DS(ON)}$  of the MOSFETs, the output load current, the output capacitance, the gate charge of the MOSFETs, and the GATE charge-pump current.

Since limiter mode can involve high switching currents when the GATE is turning on at the start of a limiting cycle (especially when the output capacitance is high), it is important to ensure the circuit does not violate the peak power rating of the MOSFETs. Check the pulse power ratings in the MOSFET data sheet.

### **MOSFET Gate Protection**

## **Load-Dump/Reverse-Voltage Protection Circuits**

To protect the gate of the MOSFETs, connect a zener clamp diode from the gate to the source. The cathode connects to the gate, and the anode connects to the source. Choose the zener clamp voltage to be above 10V and below the MOSFET  $V_{GS}$  maximum rating.

#### **Increasing the Operating Voltage Range**

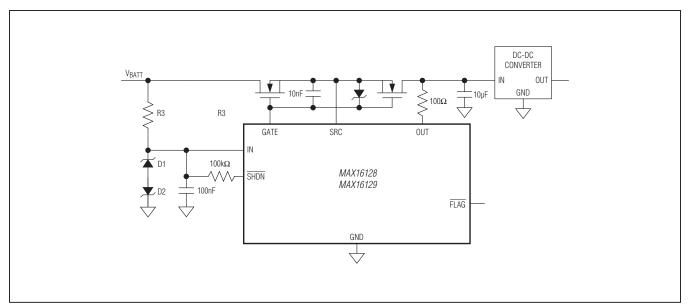

The devices can tolerate -36V to +90V. To increase the positive input-voltage protection range, connect two back-to-back zener diodes from IN to GND, and connect a resistor in series with IN and the power-supply input to limit the current drawn by the zener diodes (see Figure 1).

Zener diode D1 clamps positive voltage excursions and D2 clamps negative voltage excursions. Set the zener voltages so the worst-case voltages do not exceed the ratings of the part. Also ensure that the zener diode power ratings are not exceeded. The combination of the series resistor and the zener diodes also help snub pulses on the supply voltage input and can aid in clamping the low-energy ISO 7637-2 pulses.

It is important to compute the peak power dissipation in the series resistor. Most standard surface-mount resistors are not able to withstand the peak power dissipation during certain pulse events. Check the resistor data sheets for pulse-power derating curves. If necessary, connect multiple resistors in parallel or use automotiverated resistors.

The shutdown input needs a series resistor to limit the current if V<sub>IN</sub> exceeds the clamped voltage on IN. A good starting point is  $100k\Omega$ .

#### **Output Reservoir Capacitor**

The output capacitor can be used as a reservoir capacitor to allow downstream circuitry to "ride out" fault transient conditions. Since the voltage at the output is protected from input-voltage transients, the capacitor voltage rating can be less than the expected maximum input voltage.

Figure 1. Circuit to Increase Input-Voltage Protection Range

# Load-Dump/Reverse-Voltage Protection Circuits

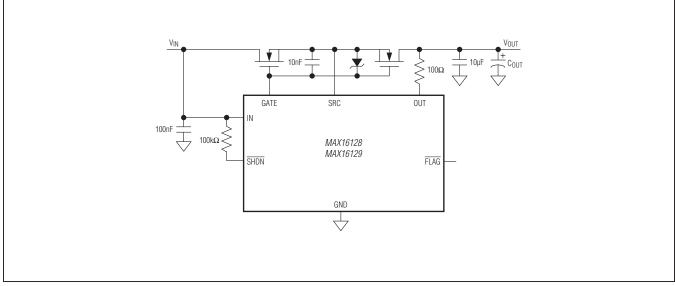

**Typical Operating Circuit**

Figure 2. MAX16128/MAX16129 Typical Operating Circuit

# Load-Dump/Reverse-Voltage Protection Circuits

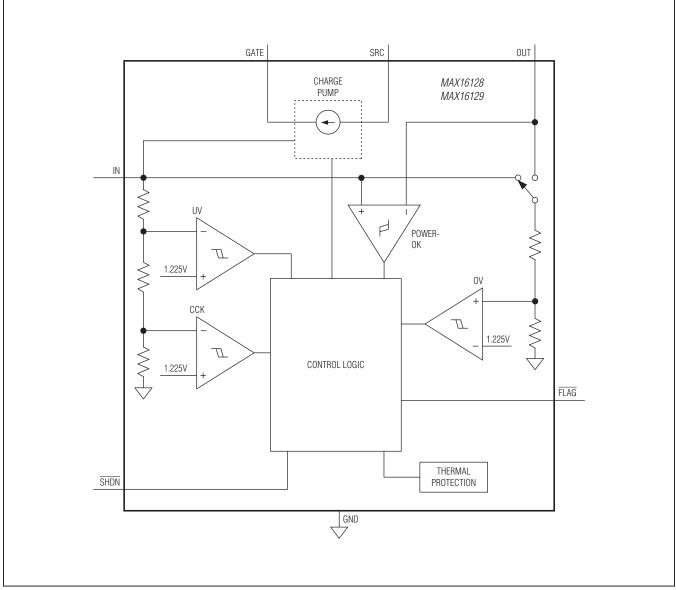

## **Functional Diagram**

Figure 3. MAX16128/MAX16129 Functional Diagram

# Load-Dump/Reverse-Voltage Protection Circuits

### Table 2. UV Threshold (V) (First Suffix)

| PART SUFFIX | UV THRESHOLD (TYP) (V) |

|-------------|------------------------|

| A           | 3                      |

| В           | 5                      |

| С           | 5.98                   |

| D           | 7.03                   |

| E           | 8.13                   |

| F           | 9.09                   |

| G           | 10.3                   |

### Table 3. OV Threshold (V) (Second Suffix)

| PART SUFFIX | OV THRESHOLD (TYP) (V) |

|-------------|------------------------|

| А           | 13.64                  |

| В           | 15                     |

| С           | 18.6                   |

| D           | 20.93                  |

| E           | 24.16                  |

| F           | 28.66                  |

| G           | 31.62                  |

### Table 4. CCK Threshold (Third Suffix)

| PART SUFFIX | CCK THRESHOLD (TYP) (V) |

|-------------|-------------------------|

| A           | No CCK                  |

| В           | 5.64                    |

| С           | 7.65                    |

| D           | 9.67                    |

### Table 5. Switch Mode Option (MAX16128 Only)

| PART SUFFIX | SWITCH MODE               |

|-------------|---------------------------|

| А           | Always autoretry          |

| В           | One retry, then latch     |

| С           | Three retries, then latch |

| D           | Latch mode                |

## **Selector Guide**

| PART             | PIN-<br>PACKAGE | TOP<br>MARK | FUNCTION     |

|------------------|-----------------|-------------|--------------|

| MAX16128AUAACAC+ | 8 μΜΑΧ          | +AACE       | Switch Mode  |

| MAX16129AUAEBD+  | 8 µMAX          | +AACG       | Limiter Mode |

## **Ordering Information**

| PART         | TEMP RANGE      | PIN-PACKAGE | FUNCTION     |

|--------------|-----------------|-------------|--------------|

| MAX16128AUA+ | -40°C to +125°C | 8 µMAX      | Switch Mode  |

| MAX16129AUA+ | -40°C to +125°C | 8 µMAX      | Limiter Mode |

**Note:** The first "\_" is a placeholder for the undervoltage threshold. A desired undervoltage threshold is set by the letter suffix found in <u>Table 2</u>. The second "\_" is a placeholder for the overvoltage threshold. A desired overvoltage threshold is set by the letter suffix found in <u>Table 3</u>. The third "\_" is a placeholder for the CCK threshold set by the letter suffix found in <u>Table 4</u>. For MAX16128 options, the fourth "\_" is a placeholder for the switch-mode option. A desired switch mode is set by the letter suffix found in <u>Table 5</u>. +Denotes a lead(Pb)-free/RoHS-compliant package.

## **Chip Information**

### PROCESS: BICMOS

## **Package Information**

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE | PACKAGE | OUTLINE        | LAND           |

|---------|---------|----------------|----------------|

| TYPE    | CODE    | NO.            | PATTERN NO.    |

| 8 µMAX  | U8+1    | <u>21-0036</u> | <u>90-0092</u> |

# Load-Dump/Reverse-Voltage Protection Circuits

### **Revision History**

15

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                                            | PAGES<br>CHANGED |

|--------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 12/11            | Initial release                                                                                                                                                                        |                  |

| 1                  | 9/12             | Updated the <i>Features, Electrical Characteristics, Typical Operating Characteristics, Cold-Crank Monitoring, Increasing the Operating Voltage Range</i> sections, and Tables 3 and 4 | 1–5, 9, 11, 14   |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

#### Maxim Integrated 160 Rio Robles, San Jose, CA 95134 USA 1-408-601-1000

© 2012 Maxim Integrated

The Maxim logo and Maxim Integrated are trademarks of Maxim Integrated Products, Inc.