## **MCU** for DSL

# **DATA SHEET**

Rev 1.8 Oct. 25, 2001

SAMSUNG Electronics Co., LTD.

### **IMPORTANT NOTICE**

SAMSUNG reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

## CONTENTS

| 1.    | GENERAL DESCRIPTION                                         | 5  |

|-------|-------------------------------------------------------------|----|

| 2.    | FEATURES                                                    | 6  |

| 3.    | FUNCTIONAL BLOCK DESCRIPTIONS                               | 7  |

| 3.1.  | BLOCK DIAGRAM                                               | 7  |

|       | $1.1 \qquad Mode \ 1 \ (1 \ SAR + 1 \ MII + 1 \ USB) \dots$ |    |

|       | $1.2 \qquad Mode 2 (1 SAR + 2 MII + 1 USB) \dots$           |    |

| 3.2.  | ARCHITECTURE                                                |    |

| 3.3.  | System Manager                                              |    |

| 3.4.  | UNIFIED INSTRUCTION/DATA CACHE                              |    |

| 3.5.  | SAR/UTOPIA INTERFACE                                        |    |

| 3.6.  | ETHERNET                                                    | 9  |

| 3.7.  | USB CONTROLLER                                              | 10 |

| 3.8.  | DMA CONTROLLER                                              | 10 |

| 3.9.  | UART                                                        | 10 |

| 3.10. | TIMERS                                                      | 10 |

| 3.11. | PROGRAMMABLE I/O                                            | 10 |

| 3.12. | INTERRUPT CONTROLLER                                        |    |

| 3.13. | I <sup>2</sup> C Serial Interface                           |    |

| 3.14. | SPI                                                         | 11 |

| 3.15. | PLLS                                                        | 11 |

| 4.    | PIN DESCRIPTIONS                                            | 12 |

| 4.1.  | PIN CONFIGURATION                                           | 12 |

| 4.2.  | LOGIC SYMBOL DIAGRAM                                        |    |

| 4.    | 2.1 $Mode \ 1 \ (1 \ SAR + 1 \ MII + 1 \ USB)$              |    |

| 4.    | $2.2 \qquad Mode \ 2 \ (1 \ SAR + 2 \ MII + 1 \ USB) \dots$ |    |

| 4.3   | PIN DESCRIPTIONS WITH THE PIN NUMBER AND PAD TYPE           |    |

| 4.4   | PAD DESCRIPTIONS                                            | 18 |

| 5.    | OPERATION DESCRIPTION                                       | 19 |

| 5.1.  | CPU CORE OVERVIEW                                           | 19 |

| 5.2.  | INSTRUCTION SET                                             | 20 |

| 5.3.  | OPERATING STATES                                            | 21 |

| 5.4.  | OPERATING MODES                                             | 21 |

| 5.5.  | REGISTERS                                                   | 21 |

| 5.6.  | EXCEPTIONS                                                  | 22 |

| 6.    | HARDWARE STRUCTURE                                          | 23 |

| 6.1.  | System Manager                                              | 23 |

|       | 1.3. Overview                                               | 23 |

| 6.    | 1.4. System Manager Registers                               | 23 |

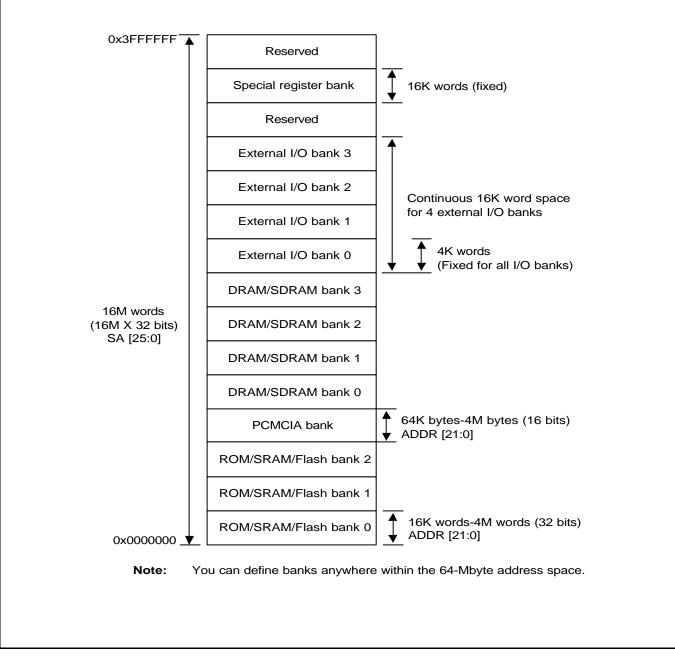

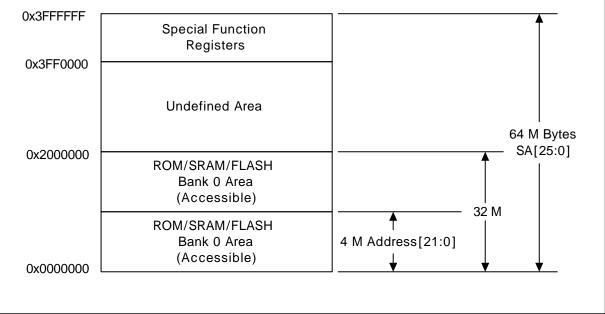

| 6.    | 1.5. System Memory Map                                      | 25 |

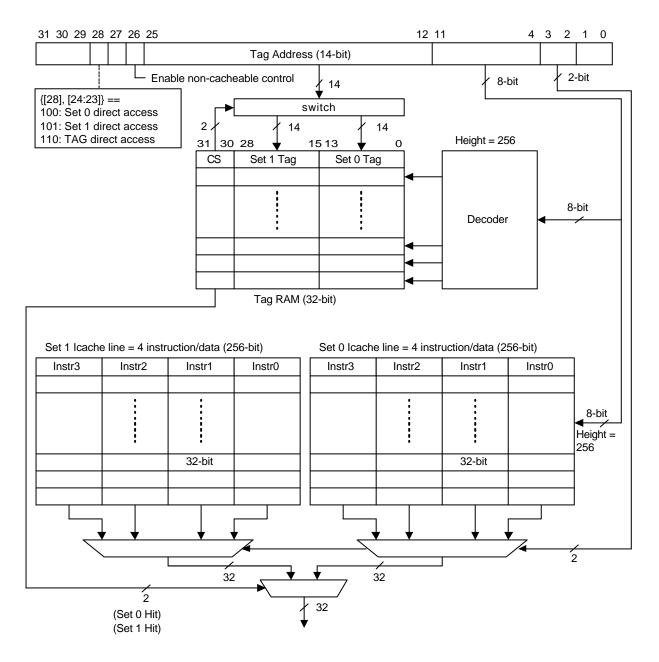

| 6.2.  | INSTRUCTION / DATA CACHE                                    |    |

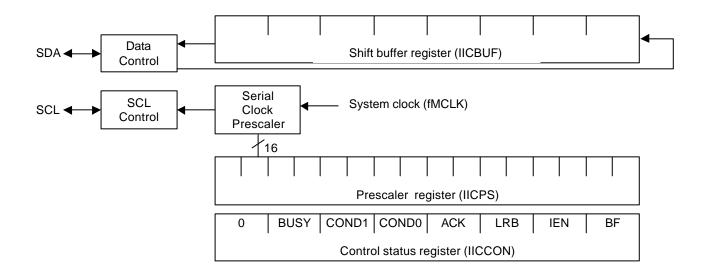

| 6.3.  | I <sup>2</sup> C Bus Controller                             | 28 |

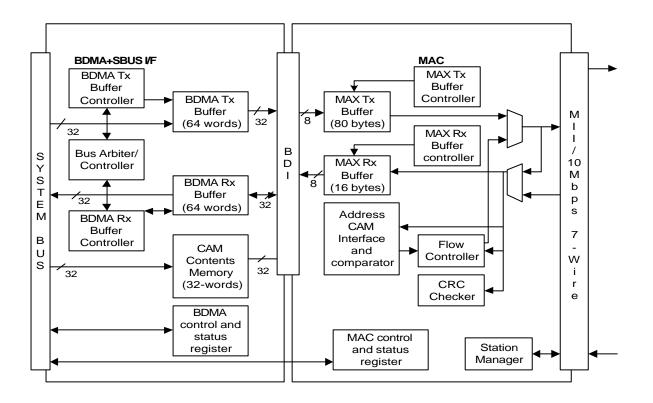

| 6.4.  | ETHERNET CONTROLLER                                         | 29 |

| 6.    | 4.1. Block Diagram                                          | 29 |

DSL Group SAMSUNG ELECTRONICS

October 26, 2001 Rev 1.8

#### S5N8947 (MCU for DSL)

| 6.4.2 | 2. Features and Benefits         |    |

|-------|----------------------------------|----|

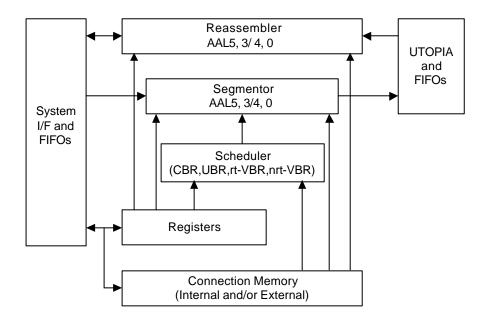

| 6.5.  | SAR AND UTOPIA INTERFACE         |    |

| 6.5.1 |                                  |    |

| 6.5.2 |                                  |    |

| 6.6.  | USB CONTROLLER                   |    |

| 6.6.1 |                                  |    |

| 6.7.  | DMA CONTROLLER                   |    |

| 6.8.  | UART                             |    |

| 6.9.  | TIMERS                           |    |

| 6.10. | I/O PORTS                        |    |

| 6.11. | INTERRUPT CONTROLLER             |    |

| 6.12. | SPI                              |    |

| 7. SI | SPECIAL FUNCTION REGISTERS       | 41 |

| 8. E  | ELECTRIC CHARACTERISTICS         | 45 |

| 8.1.  | ABSOLUTE MAXIMUM RATINGS         |    |

| 8.2.  | RECOMMENDED OPERATING CONDITIONS |    |

| 8.3.  | DC ELECTRICAL CHARACTERISTICS    |    |

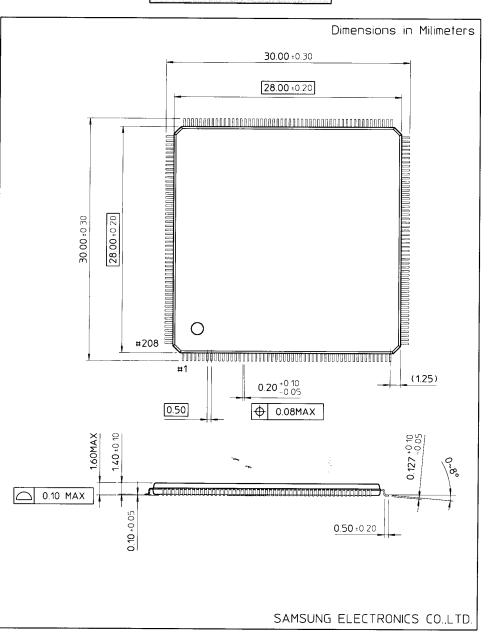

| 9. P/ | PACKAGE DIMENSION                | 47 |

## **1. GENERAL DESCRIPTION**

Samsung's S5N8947 16/32-bit RISC microcontroller is a cost-effective, high-performance microcontroller solution. The S5N8947 is designed as 2-channel 10/100Mbps Ethernet controller for use in managed communication hubs and routers. The S5N8947 also provides ATM Layer SAR (Segmentation and Reassembly) function with UTOPIA interface and the full-rate USB (Universal Serial Bus) function.

The S5N8947 is built around an outstanding CPU core: the 16/32-bit ARM7TDMI RISC processor designed by Advanced RISC Machines, Ltd. The ARM7TDMI core is a low-power, general purpose, microprocessor macro-cell that was developed for use in application-specific and custom-specific integrated circuits. Its simple, elegant, and fully static design is particularly suitable for cost-sensitive and power-sensitive applications.

Important peripheral functions including an UART channel, 2-channel GDMA, three 32-bit timers, watchdog timer, I<sup>2</sup>C bus controller, SPI, and programmable I/O ports are supported. Built-in logic including an interrupt controller, DRAM controller, and a controller for ROM/SRAM and flash memory are also supported. The S5N8947's System Manager provides an internal 32-bit system bus arbiter and an external memory controller including control logic for a PCMCIA socket interface.

To reduce total system cost, the S5N8947 offers a unified cache, 2-channel 10/100Mbps Ethernet controller, SAR and USB. Most of the on-chip function blocks have been designed using an HDL synthesizer and the S5N8947 has been fully verified in Samsung's state-of-the-art ASIC test environment.

| Item                | S5N8946                      | S5N8947                          |

|---------------------|------------------------------|----------------------------------|

| Architecture        | Only one mode                | Two modes are supported:         |

|                     | -                            | Mode 1. MII + UTOPIA + USB       |

|                     |                              | Mode 2. 2*MII + UTOPIA + USB     |

|                     | 2 Timer                      | 3 Timer                          |

|                     | -                            | 1 Watchdog Timer                 |

|                     | -                            | SPI Interface support            |

|                     | -                            | PCMCIA support                   |

| Function            | UTOPIA Level 1 Support       | UTOPIA Level 1/2 Support         |

|                     | Seven Wire Support           | MII/Seven Wire Support           |

|                     | (10 Mbps Ethernet Support)   | (10/100 Mbps Ethernet Support)   |

|                     | USB support Byte access.     | USB support Word access and DMA  |

|                     |                              | operation.                       |

|                     | SAR support hardwired little | SAR support hardwired Big/Little |

|                     | Endian.                      | Endian.                          |

| Performance         | 50 MHz operation             | 72 MHz operation                 |

|                     | 4K Unified Cache             | 8K Unified Cache                 |

| Operation condition | 3.3V                         | 1.8V                             |

| Package             | 240 QFP                      | 208 LQFP                         |

Table 1 S5N8946 vs. S5N8947

## 2. FEATURES

- ✓ 8-Kbyte unified cache

- ✓ SAR (Segmentation and Reassembly)

- ✓ UTOPIA (the Universal Test & Operations PHY Interface for ATM) Level 1/2 Interface

- ✓ 2-channel 10/100Mbps Ethernet

- ✓ Full-rate USB controller

- ✓ 2-CH GDMA (General Purpose Direct Memory Access)

- ✓ UART (Universal Asynchronous Receiver and Transmtter)

- ✓ 3 programmable 32bits Timers

- ✓ Watchdog Timer

- ✓ 18 Programmable I/O ports

- ✓ Interrupt controller

- ✓  $I^2C$  controller

- ✓ SPI (Serial Peripheral Interface)

- ✓ Built-in PLLs for System/USB

- ✓ PCMCIA 'memory and I/O' master modes

- ✓ Cost effective JTAG-based debug solution

- ✓ Boundary scan

- ✓ 3.3V I/Os and 1.8V core supply voltage

- ✓ Operating Frequency Up to 72MHz

- ✓ 208 LQFP Package

## **3. FUNCTIONAL BLOCK DESCRIPTIONS**

### 3.1. Block Diagram

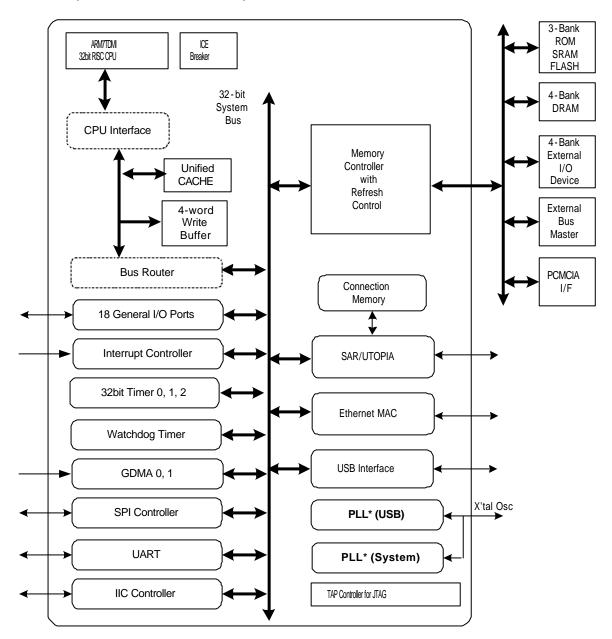

#### 3.1.1 Mode 1 (1 SAR + 1 MII + 1 USB)

Figure 1 Top Block Diagram: Mode 1

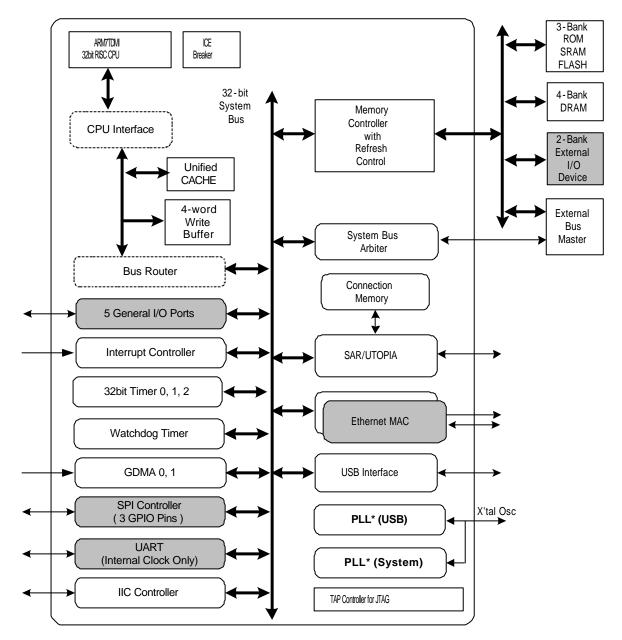

3.1.2 Mode 2 (1 SAR + 2 MII + 1 USB)

Figure 2 Top Block Diagram: Mode 2

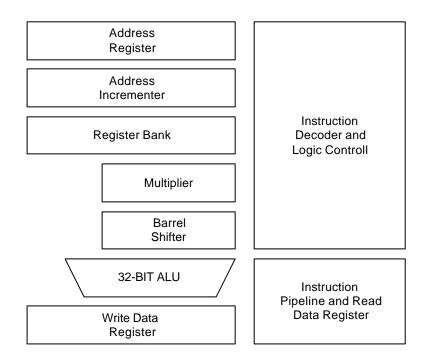

### 3.2. Architecture

Integrated system for embedded Ethernet / USB / SAR Fully 16/32-bit RISC architecture Efficient and powerful ARM7TDMI core Little/Big-Endian mode is fully supported. (The internal register supports word access only.) Cost-effective JTAG-based debug solution Supports Boundary Scan

### 3.3. System Manager

8/16/32-bit external bus support for ROM/SRAM, flash memory, DRAM and external I/O One external bus master with bus request/acknowledge pins Supports EDO/normal or SDRAM Programmable access cycle Four-word depth write buffer Cost-effective memory-to-peripheral DMA interface Supports PCMCIA 'memory and I/O' master mode

### 3.4. Unified Instruction/Data Cache

Two-way set-associative unified cache (8Kbytes) Supports LRU (least recently used) Protocol

### 3.5. SAR/UTOPIA Interface

Directly supports ATM Adaptation Layer Five (AAL5) Segmentation And Reassembly Segments and reassembles data up to 70Mbps A glueless UTOPIA level 1/2 interface is supprted (for receiving and transmitting ATM cells with SAR, it is a standard ATM interface between ATM link and physical layer).

DSL Group

### 3.6. ETHERNET

2-Channel 10/100Mbps Ethernet Controller4 DMA engines with burst modeFull compliance with IEEE standard 802.3Supports MII interface (7-wire 10-Mbps interface is also supported).

SAMSUNG ELECTRONICS

October 26, 2001 Rev 1.8

CONFIDENTIAL

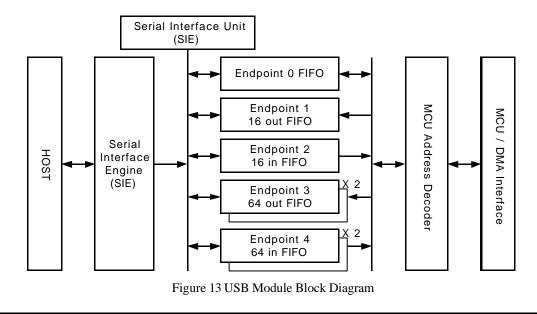

### 3.7. USB Controller

Supports 12Mbps full rate function for universal serial bus

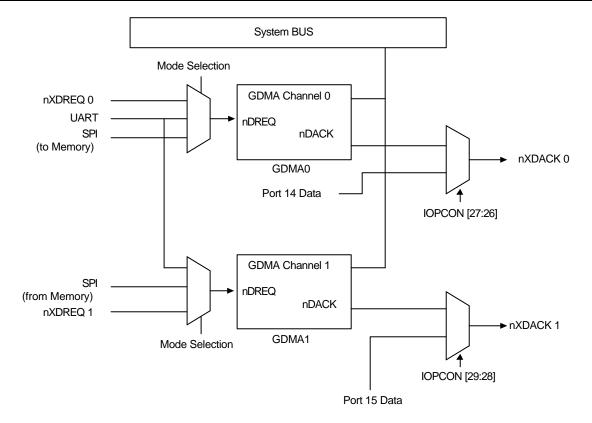

### 3.8. DMA Controller

2-channel general purpose DMA (for memory-to-memory, memory-to-SPI, SPI-to-memory, UART-tomemory, memory-to-UART data transfers without CPU intervention) Initiated by a software or a external DMA request Increments or decrements source or destination address in 8-bit, 16-bit or 32-bit data transfers

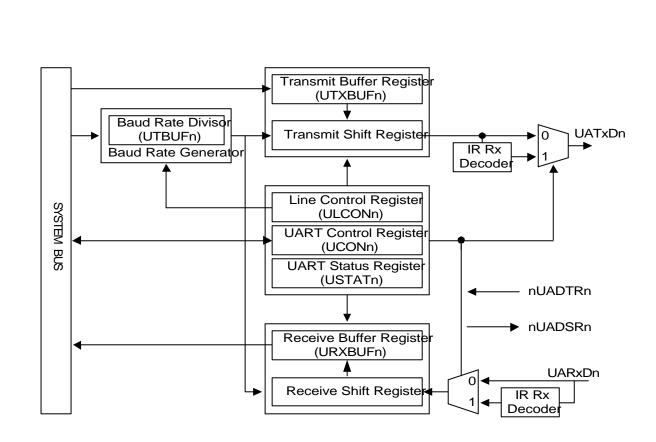

### 3.9. UART

UART block with DMA-based or interrupt-based operation Supports 5-bit, 6-bit, 7-bit, or 8-bit serial data transmit and receive Programmable baud rates Infra-red (IR) TX/RX support (IrDA)

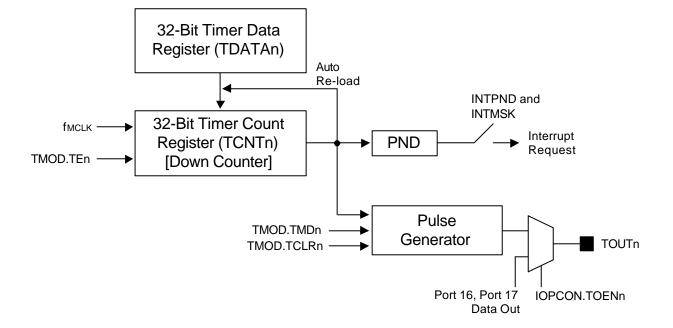

### 3.10. Timers

Three programmable 32-bit timers Interval mode or toggle mode operation Supports a watchdog timer

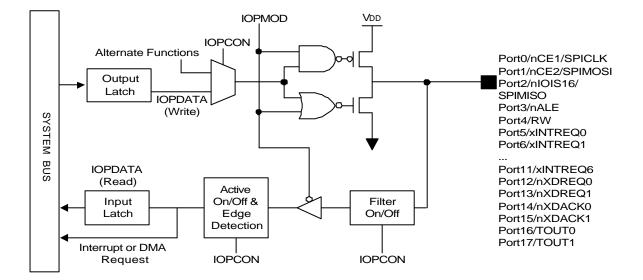

### 3.11. Programmable I/O

18 programmable I/O ports Pins individually configurable to input, output, or I/O mode for dedicated signals

### 3.12. Interrupt Controller

23 interrupt sources, including 7 external interrupt sources Normal or fast interrupt mode (IRQ, FIQ) Prioritized interrupt handling

### 3.13. I<sup>2</sup>C Serial Interface

Single master mode operation only

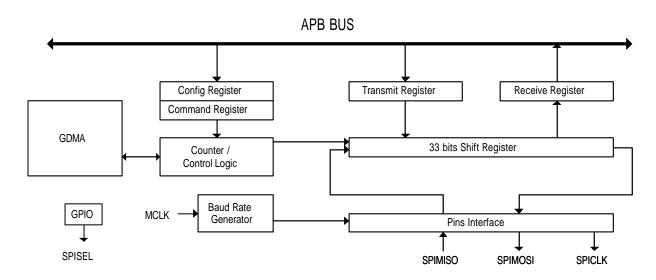

### 3.14. SPI

Full duplex operation Work with data characters from 4 to 32 bits long Supports GDMA mode for SPI transmission and reception Single master SPI modes only supported Programmable baud rate generator Programmable clock phase and polarity

### 3.15. PLLs

The external clock can be multiplied by on-chip PLLs to provide high frequency System/USB clock The input frequency is fixed to 12 MHz

The output frequency is 6 times the input clock for System

The output frequency is 4 times the input clock for USB

## 4. PIN DESCRIPTIONS

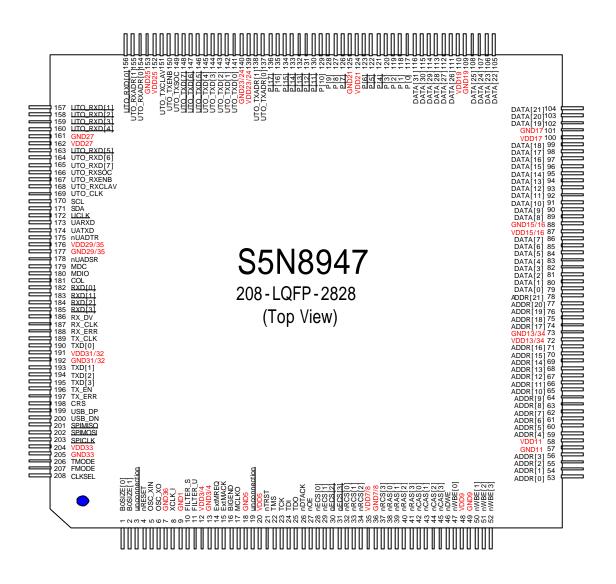

### 4.1. Pin Configuration

Figure 3 S5N8947 Pin Configuration

#### NOTES

$\checkmark$  <u>Under-bar</u> in the Figure 2 means the muxing pins.

### 4.2. Logic Symbol Diagram

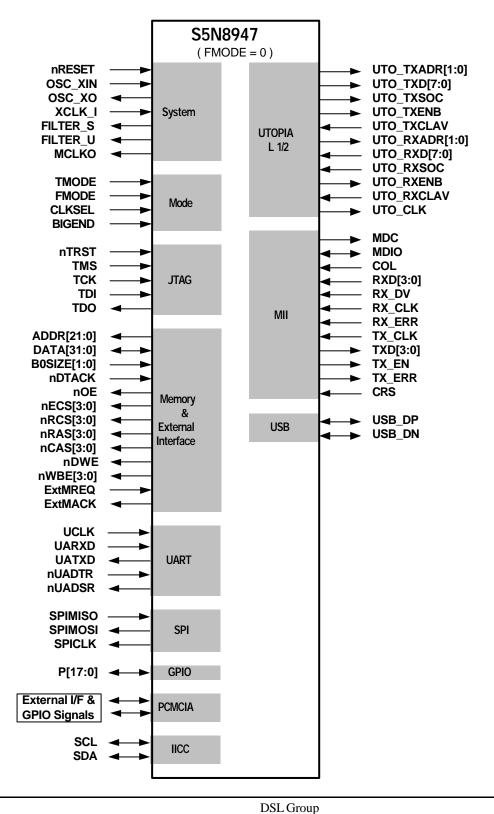

#### 4.2.1 Mode 1 (1 SAR + 1 MII + 1 USB)

Page : 13

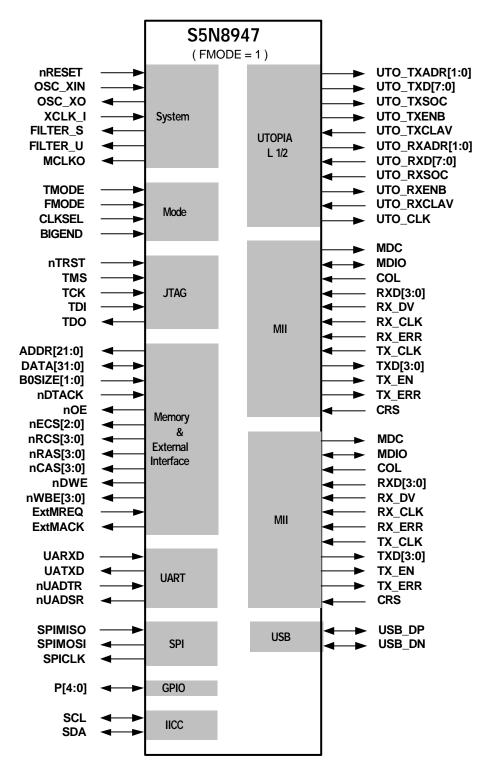

Figure 4 S5N8947 Logic Symbol Diagram (Mode 1)

#### 4.2.2 Mode 2 (1 SAR + 2 MII + 1 USB)

Figure 5 S5N8947 Logic Symbol Diagram (Mode 2)

### 4.3 Pin Descriptions with the Pin number and Pad type

| Pin<br>No | Pin Name     | I/O<br>Type | Pad type       | Descriptions        |

|-----------|--------------|-------------|----------------|---------------------|

| 1         | B0SIZE[0]    | I           | Phic           |                     |

| 2         | B0SIZE[1]    | Ι           | Phic           |                     |

| *3        | unconnection | Ι           | Phic           | Muxing with sRX_CLK |

| 4         | nRESET       | Ι           | Phtis          |                     |

| 5         | OSC_XIN      | Ι           | Phsoscm2       |                     |

| 6         | OSC_XO       | 0           | Phsoscm2       |                     |

| 7         | GND36        | Р           | Vss3o          |                     |

| 8         | XCLK_I       | Ι           | phic           |                     |

| 9         | GND1         | Р           | Vbb1_abb       |                     |

| 10        | FILTER_S     | 0           | Poar50_abb     |                     |

| 11        | FILTER_U     | 0           | Poar50_abb     |                     |

| 12        | VDD3/4       | Р           | Vdd1t_abb      | 1.8V                |

| 13        | GND3/4       | Р           | Vss1t_abb      |                     |

| 14        | ExtMREQ      | Ι           | Phic           |                     |

| 15        | ExtMACK      | 0           | Phob1          |                     |

| 16        | BIGEND       | Ι           | Phicd          |                     |

| 17        | MCLKO        | 0           | Phob4          |                     |

| 18        | GND5         | Р           | Vss3p          |                     |

| *19       | Unconnection | В           | Phbcut4        | Muxing with sMDIO   |

| 20        | VDD5         | Р           | Vdd3p          | 3.3V                |

| 21        | nTRST        | Ι           | Phicu          |                     |

| 22        | TMS          | Ι           | Phicu          |                     |

| 23        | TCK          | Ι           | phic           |                     |

| 24        | TDI          | Ι           | Phicu          |                     |

| 25        | TDO          | 0           | Phtot2         |                     |

| 26        | NDACK        | Ι           | Phicu          |                     |

| 27        | NOE          | 0           | Phot4          |                     |

| 28        | NECS[0]      | 0           | Phot4          |                     |

| 29        | NECS[1]      | 0           | Phot4          |                     |

| *30       | NECS[2]      | Ο           | Phot4          | Muxing with sTXD[3] |

| *31       | NECS[3]      | 0           | Phot4          | Muxing with sMDC    |

| 32        | nRCS[0]      | 0           | Phot4          |                     |

| 33        | nRCS[1]      | 0           | Phot4          |                     |

| 34        | nRCS[2]      | 0<br>D      | Phot4          |                     |

| 35        | VDD7/8       | P           | Vdd3o          | 3.3V                |

| 36        | GND7/8       | P           | Vss3o          | N-4 DCMCIA14        |

| 37        | nRCS[3]      | 0           | Phot4          | Not PCMCIA select   |

| 38        | nRAS[0]      | 0           | Phot4          |                     |

| 39        | nRAS[1]      | 0           | Phot4          |                     |

| 40        | nRAS[2]      | 0           | Phot4          |                     |

| 41        | nRAS[3]      | 0           | Phot4          |                     |

| 42<br>43  | nCAS[0]      | 0           | Phot4          |                     |

| 43        | nCAS[1]      | 0           | Phot4<br>Phot4 |                     |

| 44        | nCAS[2]      | 0           |                |                     |

| -         | nCAS[3]      |             | Phot4          |                     |

| 46        | nDWE         | 0           | Phot4          |                     |

Page : 15

| 48     VDD2     P     Vad1h     1.8V       49     CND9     P     Vss3     nWBE[1]     O     Phot4     nWBE[2]/ORD(PCMCIA only)       51     nWBE[3]     O     Phot4     nWBE[2]/OWR(PCMCIA only)       53     state     O     Phot4     nWBE[2]/OWR(PCMCIA only)       53     VDD11     P     Vss3     Image: State                                                                                                                                                                                                                                                                                         | 47    | nWBE[0]        | 0   | Phot4    |                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------|-----|----------|---------------------------|

| 49     CND9     P     Vs3i       50     nWBE[1]     O     Phot4     nWBE[1/IORD(PCMCIA only)       51     nWBE[2]     O     Phot4     nWBE[1/IORD(PCMCIA only)       52     nWBE[3]     O     Phot4     nWBE[1/IORD(PCMCIA only)       53     ADDR(1)     P     Vs3i     Image: State of the state                                                                                                                                                                                                                                     |       |                |     |          | 1.8V                      |

| 50     nWBE[1]     0     Phot4     nWBE[1/IORD(PCMCIA only)       51     nWBE[3]     0     Phot4     nWBE[2](JOWR(PCMCIA only)       53     58     ADDR(0:3]     0     Phot4       53     65     ADDR(0:3]     0     Phot4       57     GND11     P     Vss3i     -       58     VDD11     P     Vsd3i     3.3V       58     VDD1324     P     Vdd3o     3.3V       73     GND1344     P     Vsd3o     3.3V       74.78     ADDR[7:21]     0     Phot4     -       79.80     DATA[6:7]     B     Phot44     -       79.80     DATA[6:7]     B     Phot44     -       700     VDD17     P     Vd30     3.3V     -       701     CND17     P     Vsc33     -     -       7100     GND17     P     Vsc31     -     -       7101     DATA[2:25]     B     Phbcut4     -     -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |                |     |          |                           |

| 51     nWBE[2]     O     Phot4     nWBE[2]/IOWR(PCMCIA only)       52     nWBE[3]     O     Phot4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |                |     |          | nWBE[1]/IORD(PCMCIA only) |

| 52   nWBE[3]   O   Phot4     53-56   ADDR[0:3]   O   Phot4     57   GND11   P   Vsc31     58   VDD11   P   Vdd1h   L8V     59-71   ADDR[4:16]   O   Phot4     72   VDD1334   P   Vdd30   3.3V     73   GND1344   P   Vsc30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |                |     |          |                           |

| S3:56   ADDR $[0.3]$ O   Phot4     57   CND11   P   Vst31     58   VDD11   P   Vst31     59:71   ADDR $[4:16]$ O   Phot4     72   VDD1334   P   Vdd30   3.3V     73   GND1324   P   Vdd30   3.3V     74:78   ADDR $[17:21]$ O   Phot4     79:78   DATA[0:7]   B   Pbbcut4     87   VDD15716   P   Vst30     786   DATA[8:18]   B   Pbbcut4     80   GND17   P   Vst30     80   GND17   P   Vst31     100   GND17   P   Vst31     101   GND19   P   Vst31     102   DATA[19-25]   B   Phbcut4     111   DATA[26-31]   B   Phbcut4     111-   DATA[26-31]   B   Phbcut4     1120   P(0.3]   B   Phbcut4     1121   P[4]   B   Phbcut4     1122   P[6]   B   P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |                |     |          |                           |

| 57   GRD11   P   Vss3i     58   VDD11   P   Vddih   1.8V     72   VDD354   P   Vdd30   33V     73   GRND1334   P   Vss3o   1.8V     7478   ADDR[1721]   O   Phot4   1.8V     79-86   DATA[0:7]   B   Pbcut4   1.8V     87   VDD1516   P   Vdd30   3.3V     88   GND1516   P   Vdd30   3.3V     89:99   DATA[8:8]   B   Pbcut4   1.8V     100   VDD17   P   Vdd1h   1.8V     101   GND17   P   Vss3i   1.8V     101   GND19   P   Vss3i   1.8V     101   GND19   P   Vss3i   1.8V     111-   DATA[26-31]   B   Phbcut4   1.8V     112   P[0.3]   B   Phbcut4   1.8V     1121   P[4]   B   Phbcut4   1.8V     1121   P[4]   B   Phbcut4   1.8V     1121 <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |                |     |          |                           |

| 58     VDD11     P     Vddih     1.8V       59-71     ADDR[4:16]     O     Phot4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |                |     |          |                           |

| 59-71   ADDR[4:16]   O   Phot4     72   VDD13/34   P   Vd3/3     73   GND13/34   P   Vd3/3     74-78   ADDR[17:21]   O   Phot4     74-78   ADDR[17:21]   O   Phot4     74-78   ADDR[17:21]   O   Phot4     79-86   DATA[0:7]   B   Phocut4     78   VDD15/16   P   Vd3/3   3.3V     89-99   DATA[8:18]   B   Phocut4   1.8V     100   VDD17   P   Vd1/1   1.8V     101   GND19   P   Vs33   -     102   DATA[19-25]   B   Phocut4   -     110   VDD19   P   Vd3/1   1.8V   -     111   DATA[26-31]   B   Phocut4   -   -     111-   DATA[26-31]   B   Phocut4   Muxing with sTXD[0]   -     1122   Pf5   B   Phocut4   Muxing with sTXD[2]   -     124   VDD21   P   Vd3/2   3.4V   - <td></td> <td></td> <td></td> <td></td> <td>1.8V</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |                |     |          | 1.8V                      |

| 72   VDD13/34   P   Vsd30   3.3V     73   GRD13/34   P   Vss30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |                |     |          |                           |

| 73     GND1334     P     Vss3o       74-78     ADDR[17:21]     O     Phot4       79-86     DATA[0:7]     B     Photu4       87     VDD15/16     P     Vsd3o     3.3V       88     GND15/16     P     Vsd3o     3.3V       88     GND15/16     P     Vss3o     8999       999     DATA[8:18]     B     Phbcut4     100       100-     VDD17     P     Vsd3i     111       102-     DATA[19-25]     B     Phbcut4     18V       110     VDD19     P     Vsd3i     1.8V     111       DATA[26-31]     B     Phbcut4     111     1.8V     111       110     VDD19     P     Vd3in     1.8V     111       120     P(0:3]     B     Phbcut4     Muxing with \$TXD[0]     112       121     P(1]     B     Phbcut4     Muxing with \$TXD[2]     112       122     P(5]     B     Phbcut4     Muxing with \$TXD[2]     112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |                |     |          | 3.3V                      |

| 74-78   ADDR[17:21]   O   Phot4     79-86   DATA[0:7]   B   Phocut4     7   VDD15/16   P   Vd30   3.3V     88   GND15/16   P   Vd30   3.3V     89   DATA[8:18]   B   Phocut4      100   VD17   P   Vd31h   1.8V     101   GND17   P   Vd31h   1.8V     102   DATA[19-25]   B   Phocut4      108   GND19   P   Vd31h   1.8V     109   GND19   P   Vd31h   1.8V     110   VD19   P   Vd31h   1.8V     111   DATA[26-31]   B   Phocut4      120   P(0.3]   B   Phocut4   Muxing with sTXD[0]     *121   P(4]   B   Phocut4   Muxing with sTXD[1]     *122   P(5]   B   Phocut4   Muxing with sTXD[2]     123   P(6]   B   Phocut4   Muxing with sTXD[2]     124   VDD21   P   Vd329   3.3V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 73    |                | Р   |          |                           |

| 79-86   DATA[0.7]   B   Phbcut4     87   VDD[5/16   P   Vd330   3.3V     88   GND[5/16   P   Vs330     89-99   DATA[8:18]   B   Phbcut4     100   VDD17   P   Vdd1ih   1.8V     101   GND17   P   Vs3i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |                |     |          |                           |

| 87     VDD15/16     P     Vdd3o $3.3V$ 88     GND15/16     P     Vss3o       99-9D     DATA[8:18]     B     Phbcut4       100     VDD17     P     Vss3i       101     GND17     P     Vss3i       102-     DATA[19-25]     B     Phbcut4       100     VDD19     P     Vss3i       101     VDD19     P     Vss3i       111-     DATA[26-31]     B     Phbcut4       111-     DATA[26-31]     B     Phbcut4       111-     DATA[26-31]     B     Phbcut4       111-     DATA[26-31]     B     Phbcut4       111-     P(0.5]     B     Phbcut4       112     P(1     B     Phbcut4       112     P(1     B     Phbcut4       1123     P(6]     B     Phbcut4       1124     VDD21     P     Vsd3p       125     GND21     P     Vsd3p       126     P(7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |                |     |          |                           |

| 89-99     DATA[8:18]     B     Phbcut4       100     VDD17     P     Vddlih     1.8V       101     GND17     P     Vs3i     -       102-<br>108     DATA[19-25]     B     Phbcut4     -       100     GND19     P     Vddlih     1.8V       111     DATA[26-31]     B     Phbcut4     -       111-<br>116     DATA[26-31]     B     Phbcut4     Muxing with sTXD[0]       *121     P(4)     B     Phbcut4     Muxing with sTXD[1]       *122     P(5]     B     Phbcut4     Muxing with sTXD[2]       124     VDD21     P     Vd3p     3.3V       125     GND21     P     Vd3p     3.3V       125     GND21     P     Vs3p     -       *126     P(7]     B     Phbcut4     Muxing with sRX_DV       127-<br>129     P(8-10)     B     Phbcut4     Muxing with sRXD[1]       *131     P[12]     B     Phbcut4     Muxing with sRXD[2]       *13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |                |     |          | 3.3V                      |

| 100     VDD17     P     Vddlih     1.8V       101     GND17     P     Vss3i        102-<br>108     DATA[19-25]     B     Phbcut4        109     GND19     P     Vss3i        100     VDD19     P     Vsd1ih     1.8V       110     VDD19     P     Vdd1ih     1.8V       111-<br>116     DATA[26-31]     B     Phbcut4     Muxing with sTXD[0]       *121     P[4]     B     Phbcut4     Muxing with sTXD[1]       *122     P[5]     B     Phbcut4     Muxing with sTXD[2]       *123     P[6]     B     Phbcut4     Muxing with sTXD[2]       124     VDD21     P     Vd3p     3.3V       125     GND1     B     Phbcut4     Muxing with sRX_DV       127.     P[8-10]     B     Phbcut4     Muxing with sRXD[0]       *130     P[13]     B     Phbcut4     Muxing with sRXD[1]       *133     P[14]     B     Phbcut4     Muxing with sRXD[2]<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 88    | GND15/16       | Р   | Vss3o    |                           |

| 100     VDD17     P     Vddlih     1.8V       101     GND17     P     Vss3i        102-<br>108     DATA[19-25]     B     Phbcut4        109     GND19     P     Vss3i        100     VDD19     P     Vsd1ih     1.8V       111-<br>116     DATA[26-31]     B     Phbcut4        *110     VD19     B     Phbcut4     Muxing with sTXD[0]       *111-<br>120     P(0.3]     B     Phbcut4     Muxing with sTXD[0]       *121     P[4]     B     Phbcut4     Muxing with sTXD[1]       *122     P[5     B     Phbcut4     Muxing with sTXD[2]       124     VD21     P     Vd3p     3.3V       125     GND21     P     Vd3p     3.3V       126     P[7]     B     Phbcut4     Muxing with sRX_DV       127-<br>129     P[8-10]     B     Phbcut4     Muxing with sRXD[0]       *133     P[12]     B     Phbcut4     Muxing with sRXD[1] <td>89-99</td> <td></td> <td>В</td> <td>Phbcut4</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 89-99 |                | В   | Phbcut4  |                           |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 100   |                | Р   | Vdd1ih   | 1.8V                      |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 101   | GND17          | Р   | Vss3i    |                           |

| 109     GND19     P     Vss31       110     VDD19     P     Vdd1ih     1.8V       111-     DATA[26-31]     B     Phbcut4     1.8V       117-     P[0:3]     B     Phbcut4     1.8V       **121     P[4]     B     Phbcut4     Muxing with sTXD[0]       **122     P[5]     B     Phbcut4     Muxing with sTXD[2]       **122     P[6]     B     Phbcut4     Muxing with sTXD[2]       **123     P[6]     B     Phbcut4     Muxing with sTXD[2]       **124     VDD21     P     Vd3p     3.3V       125     GND21     P     Vss3p     ************************************                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 102-  |                | р   | Dhhart 4 |                           |

| 110   VDD19   P   Vdd1ih   1.8V     111-<br>116   DATA[26-31]   B   Phbcut4   Image: constraint of the state of the | 108   |                |     | rndcut4  |                           |

| 111-<br>116   DATA[26-31]   B   Phbcut4     117-<br>120   P[0:3]   B   Phbcut4     *121   P[4]   B   Phbcut4   Muxing with sTXD[0]     *122   P[5]   B   Phbcut4   Muxing with sTXD[1]     *123   P[6]   B   Phbcut4   Muxing with sTXD[2]     124   VDD21   P   Vd3p   3.3V     125   GND21   P   Vss3p     *126   P[7]   B   Phbcut4   Muxing with sRX_DV     127-<br>127-<br>128   P[8-10]   B   Phbcut4   Muxing with sRX_DV     *130   P[11]   B   Phbcut4   Muxing with sRXD[0]     *133   P[14]   B   Phbcut4   Muxing with sRXD[1]     *134   P[15]   B   Phbcut4   Muxing with sRXD[2]     *135   P[16]   B   Phbcut4   Muxing with sRXD[3]     135   P[16]   B   Phbcut4   Muxing with sRX_ERR     136   P[17]   B   Phbcut4   Muxing with sRX_ERR     137   UT0_TXADR[0:1]   O   Phob4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 109   | GND19          | Р   | Vss3I    |                           |

| 116     DATA[26-31]     B     Phbcut4       117-<br>120     P[0:3]     B     Phbcut4     Muxing with sTXD[0]       *121     P[4]     B     Phbcut4     Muxing with sTXD[1]       *122     P[5]     B     Phbcut4     Muxing with sTXD[2]       *123     P[6]     B     Phbcut4     Muxing with sTXD[2]       124     VDD21     P     Vd3p $3.3V$ 125     GND21     P     Vs3p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 110   | VDD19          | Р   | Vdd1ih   | 1.8V                      |

| 117-<br>120   P[0:3]   B   Phbcut4   Muxing with sTXD[0]     *121   P[4]   B   Phbcut4   Muxing with sTXD[1]     *122   P[5]   B   Phbcut4   Muxing with sTXD[2]     124   VDD21   P   Vd3p $3.3V$ 125   GND21   P   Vs3p      *126   P[7]   B   Phbcut4   Muxing with sRX_DV     127-   P[8-10]   B   Phbcut4   Muxing with sRXD[0]     *130   P[11]   B   Phbcut4   Muxing with sRXD[0]     *131   P[12]   B   Phbcut4   Muxing with sRXD[0]     *133   P[14]   B   Phbcut4   Muxing with sRXD[1]     *134   P[15]   B   Phbcut4   Muxing with sRXD[2]     *135   P[16]   B   Phbcut4   Muxing with sRXD[3]     135   P[16]   B   Phbcut4   Muxing with sRX ERR     137-<br>138   VD23/24   P   Vd3o   3.3V     140   GND23/24   P   Vd3o   3.3V     140   GND23/24   P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       | DATA[26-31]    | В   | Phbcut4  |                           |

| 120PitPitPit*121P[4]BPhbcut4Muxing with $STXD[0]$ *122P[5]BPhbcut4Muxing with $STXD[1]$ *123P[6]BPhbcut4Muxing with $STXD[2]$ 124VDD21PVdd3p $3.3V$ 125GND21PVss3p*126P[7]BPhbcut4Muxing with $sRX_DV$ 127-P[8-10]BPhbcut4Muxing with $sRXD[0]$ *130P[11]BPhbcut4Muxing with $sRXD[0]$ *131P[12]BPhbcut4Muxing with $sRXD[0]$ *132P[13]BPhbcut4Muxing with $sRXD[1]$ *133P[14]BPhbcut4Muxing with $sRXD[3]$ *134P[15]BPhbcut4Muxing with $sRXD[3]$ *135P[16]BPhbcut4Muxing with $sRXD[3]$ *136P[17]BPhbcut4Muxing with $sRXD[3]$ *137-UTO_TXADR[0:1]OPhob4*138UTO_TXD[6]OPhob4*1414UTO_TXD[0:4]OPhob4*145UTO_TXD[0:4]OPhob4*146UTO_TXD[5]OPhob4*147UTO_TXD[6]OPhob4*148UTO_TXSOCOPhob4*150UTO_TXCLAVIPhob4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 117-  | P[():3]        | В   | Phbcut4  |                           |

| *122P[5]BPhbcut4Muxing with sTXD[1]*123P[6]BPhbcut4Muxing with sTXD[2]124VDD21PVdd3p $3.3V$ 125GND21PVss3p*126P[7]BPhbcut4*127-P[8-10]BPhbcut4*130P[11]BPhbcut4*131P[12]BPhbcut4*132P[13]BPhbcut4*133P[14]BPhbcut4*134P[15]BPhbcut4*135P[16]BPhbcut4*136P[17]BPhbcut4*137IUTO_TXADR[0:1]OPhob4*138UTO_TXADR[0:1]OPhob4*141-UTO_TXD[0:4]OPhob4*144UTO_TXD[0:4]OPhob4*144UTO_TXD[0:1]OPhob4*144UTO_TXD[0:1]OPhob4*145UTO_TXD[0:1]OPhob4*146UTO_TXD[7]OPhob4*147UTO_TXD[7]OPhob4*148UTO_TXD[7]OPhob4*149UTO_TXD[6]OPhob4*141UTO_TXD[6]OPhob4*145UTO_TXD[7]OPhob4*146UTO_TXD[7]OPhob4*147UTO_TXD[7]OPhob4*149UTO_TXD[7]OPhob4*141UTO_TXSOCOPhob4*151UTO_TXCLAVI<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |                |     |          |                           |

| *123P[6]BPhbcut4Muxing with sTXD[2]124VDD21PVdd3p $3.3V$ 125GND21PVss3p*126P[7]BPhbcut4Muxing with sRX_DV127-<br>129P[8-10]BPhbcut4Muxing with sCRS*130P[11]BPhbcut4Muxing with sXD[0]*131P[12]BPhbcut4Muxing with sXD[0]*132P[13]BPhbcut4Muxing with sXD[1]*133P[14]BPhbcut4Muxing with sXD[2]*134P[15]BPhbcut4Muxing with sRXD[3]135P[16]BPhbcut4Muxing with sRXD[3]136P[17]BPhbcut4Muxing with sRX_ERR137-<br>138UTO_TXADR[0:1]OPhob4139VDD23/24PVss3o140GND23/24PVss3o141-<br>145UTO_TXD[0:4]OPhob4*146UTO_TXD[5]OPhob4*147UTO_TXD[6]OPhob4*148UTO_TXD[7]OPhob4150UTO_TXENBOPhob4150UTO_TXCLAVIPhis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |                |     |          |                           |

| 124     VDD21     P     Vdd3p     3.3V       125     GND21     P     Vss3p       *126     P[7]     B     Phbcut4     Muxing with sRX_DV       127-<br>129     P[8-10]     B     Phbcut4     Muxing with sCRS       *130     P[11]     B     Phbcut4     Muxing with sRXD[0]       *131     P[12]     B     Phbcut4     Muxing with sRXD[0]       *132     P[13]     B     Phbcut4     Muxing with sRXD[1]       *133     P[14]     B     Phbcut4     Muxing with sRXD[2]       *134     P[15]     B     Phbcut4     Muxing with sRXD[3]       135     P[16]     B     Phbcut4     Muxing with sRX_ERR       *136     P[17]     B     Phbcut4     Muxing with sRX_ERR       137-<br>138     UTO_TXADR[0:1]     O     Phob4        140     GND23/24     P     Vs30     3.3V       140     GND23/24     P     Vs30        *146     UTO_TXD[6]     O     Phob4     Mux                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |                |     |          |                           |

| 125GND21PVss3p*126P[7]BPhbcut4Muxing with sRX_DV $127$ -<br>129P[8-10]BPhbcut4Muxing with sCRS*130P[11]BPhbcut4Muxing with sCRS*131P[12]BPhbcut4Muxing with sRXD[0]*132P[13]BPhbcut4Muxing with sRXD[1]*133P[14]BPhbcut4Muxing with sRXD[2]*134P[15]BPhbcut4Muxing with sRXD[3]135P[16]BPhbcut4Muxing with sRXD[3]135P[16]BPhbcut4Muxing with sRX_ERR137-<br>138UTO_TXADR[0:1]OPhob4140GND23/24PVs3o141-<br>145UTO_TXD[0:4]OPhob4*146UTO_TXD[5]OPhob4*147UTO_TXD[6]OPhob4*148UTO_TXD[7]OPhob4*149UTO_TXD[7]OPhob4*141UTO_TXD[6]OPhob4*145UTO_TXD[7]OPhob4*146UTO_TXD[5]OPhob4*148UTO_TXD[7]OPhob4*149UTO_TXD[7]OPhob4*141UTO_TXD[6]OPhob4*145UTO_TXENBOPhob4150UTO_TXCLAVIPhis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |                |     |          |                           |

| *126P[7]BPhbcut4Muxing with $sRX_DV$ 127-<br>129P[8-10]BPhbcut4Muxing with $sRX_DV$ *130P[11]BPhbcut4Muxing with $sRXD[0]$ *131P[12]BPhbcut4Muxing with $sRXD[1]$ *132P[13]BPhbcut4Muxing with $sRXD[1]$ *133P[14]BPhbcut4Muxing with $sRXD[2]$ *134P[15]BPhbcut4Muxing with $sRXD[3]$ *135P[16]BPhbcut4Muxing with $sRXD[3]$ *136P[17]BPhbcut4Muxing with $sRX_ERR$ *137138UTO_TXADR[0:1]OPhob4139VDD23/24PVd3o $3.3V$ 140GND23/24PVss3o141-<br>145UTO_TXD[0:4]OPhob4*146UTO_TXD[5]OPhob4*148UTO_TXD[7]OPhob4*149UTO_TXSOCOPhob4150UTO_TXCLAVIPhios                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |                |     |          | 3.3V                      |

| 127-<br>129P[8-10]BPhbcut4*130P[11]BPhbcut4Muxing with sCRS*131P[12]BPhbcut4Muxing with sRXD[0]*132P[13]BPhbcut4Muxing with sRXD[1]*133P[14]BPhbcut4Muxing with sRXD[2]*134P[15]BPhbcut4Muxing with sRXD[3]135P[16]BPhbcut4Muxing with sRXD[3]136P[17]BPhbcut4Muxing with sRX_ERR137-<br>138UTO_TXADR[0:1]OPhob4140GND23/24PVss3o141-<br>145UTO_TXD[0:4]OPhob4*146UTO_TXD[5]OPhob4*148UTO_TXD[6]OPhob4*148UTO_TXSOCOPhob4150UTO_TXENBOPhob4151UTO_TXCLAVIPhis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |                |     |          |                           |

| 129     P[8-10]     B     Phbcut4       *130     P[11]     B     Phbcut4     Muxing with sCRS       *131     P[12]     B     Phbcut4     Muxing with sRXD[0]       *132     P[13]     B     Phbcut4     Muxing with sRXD[1]       *133     P[14]     B     Phbcut4     Muxing with sRXD[2]       *134     P[15]     B     Phbcut4     Muxing with sRXD[3]       135     P[16]     B     Phbcut4     Muxing with sRX_ERR       *136     P[17]     B     Phbb4     Muxing with sRX_ERR       137-<br>138     UT0_TXADR[0:1]     O     Phob4     Muxing with sRX_ERR       139     VDD23/24     P     Vss3o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       | P[7]           | В   | Phbcut4  | Muxing with sRX_DV        |