# S5N8947X

## MCU for ADSL/Cable Modem

(Revision 0.1)

May. 23, 2000

SAMSUNG ELECTRONICS PROPRIETARY

Copyright @1999-2000 Samsung Electronics, Inc. All Rights Reserved

## CONTENTS

| 1.           | GENERAL DESCRIPTION                               | 4  |

|--------------|---------------------------------------------------|----|

| 2.           | FEATURES                                          | 5  |

| 3.           | FUNCTIONAL BLOCK DESCRIPTIONS                     | 6  |

| 3.1.         | BLOCK DIAGRAM                                     | 6  |

| 3.2.         | ARCHITECTURE                                      |    |

| 3.3.         | System Manager                                    |    |

| 3.4.         | UNIFIED INSTRUCTION/DATA CACHE                    |    |

| 3.5.         | SAR/UTOPIA INTERFACE                              |    |

| 3.6.         | Ethernet MAC                                      |    |

| 3.7.         | USB Controller                                    |    |

| 3.8.         | DMA Controller                                    |    |

| 3.9.         | UART (Serial I/O)                                 |    |

| 3.9.<br>3.10 |                                                   |    |

| 3.10         |                                                   |    |

|              |                                                   |    |

| 3.12         |                                                   |    |

| 3.13         |                                                   |    |

| 3.14         | PLL (FOR SYSTEM/USB)                              | 9  |

| 4.           | PIN DESCRIPTIONS                                  | 10 |

| 4.1.         | PIN CONFIGURATION                                 | 10 |

| 4.2.         | PIN DESCRIPTIONS                                  |    |

| 4.3.         | PIN DESCRIPTIONS WITH THE PIN NUMBER AND PAD TYPE |    |

| 5.           | OPERATION DESCRIPTION                             |    |

| 5.1          | CPU Core Overview                                 |    |

| 5.1.         |                                                   |    |

| 5.2.         | INSTRUCTION SET                                   |    |

| 5.3.         | OPERATING STATES                                  |    |

| 5.4.         | OPERATING MODES                                   |    |

| 5.5.         | REGISTERS                                         |    |

| 5.6.         | EXCEPTIONS                                        | 18 |

| 6.           | HARDWARE STRUCTURE                                | 20 |

| 6.1.         | System Manager                                    | 20 |

| 6.           | 1.3. Overview                                     | 20 |

| 6.           | 1.4. System Manager Registers                     |    |

|              | 1.5. System Memory Map                            |    |

| 6.2.         | INSTRUCTION / DATA CACHE                          |    |

| 6.3.         | I <sup>2</sup> C Bus Controller                   |    |

| 6.4.         | Ethernet Controller                               |    |

|              | 4.1. Block Diagram                                |    |

|              | 4.2. Features and Benefits                        |    |

| 6.5.         | SAR AND UTOPIA INTERFACE                          |    |

|              |                                                   |    |

|              |                                                   |    |

|              |                                                   | 27 |

| 6.6.         | USB CONTROLLER                                    |    |

|              | 0                                                 | 28 |

| 6.7.         | DMA CONTROLLER                                    |    |

| 6.8.         | UART(Serial I/O)                                  |    |

| 6.9.         | TIMERS                                            | 31 |

| 6.10 | ). I/O Ports                     |  |

|------|----------------------------------|--|

| 6.11 | . INTERRUPT CONTROLLER           |  |

| 7.   | SPECIAL FUNCTION REGISTERS       |  |

| 8.   | ELECTRIC CHARACTERISTICS         |  |

| 8.1. | ABSOLUTE MAXIMUM RATINGS         |  |

| 8.2. | RECOMMENDED OPERATING CONDITIONS |  |

| 8.3. | DC ELECTRICAL CHARACTERISTICS    |  |

| 8.4. | A.C ELECTRICAL CHARACTERISTICS   |  |

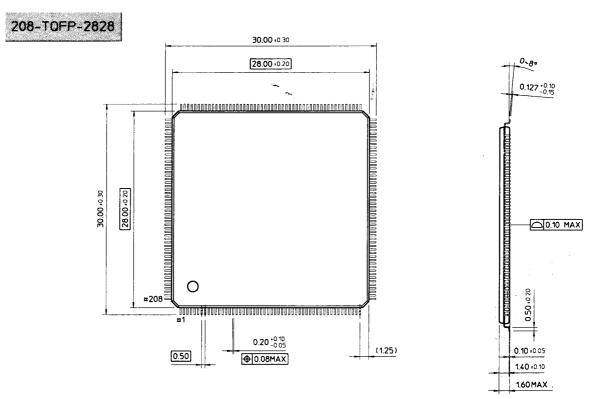

| 9.   | PACKAGE DIMENSION                |  |

## **1. GENERAL DESCRIPTION**

Samsung's S5N8947 16/32-bit RISC microcontroller is a cost-effective, high-performance microcontroller solution. The S5N8947 is designed as an integrated Ethernet controller for use in managed communication hubs and routers. The S5N8947 also provides ATM Layer SAR (Segmentation and Reassembly) function with UTOPIA interface and the full-rate USB (Universal Serial Bus) function.

The S5N8947 is built around an outstanding CPU core: the 16/32-bit ARM7TDMI RISC processor designed by Advanced RISC Machines, Ltd. The ARM7TDMI core is a low-power, general purpose, microprocessor macro-cell that was developed for use in application-specific and custom-specific integrated circuits. Its simple, elegant, and fully static design is particularly suitable for cost-sensitive and power-sensitive applications.

Important peripheral functions including an UART channel, 2-channel GDMA, two 32-bit timers, I<sup>2</sup>C bus controller, and programmable I/O ports are supported. Built-in logic including an interrupt controller, DRAM controller, and a controller for ROM/SRAM and flash memory are also supported. The S5N8947's System Manager includes an internal 32-bit system bus arbiter and an external memory controller.

To reduce total system cost, the S5N8947 offers a unified cache, Ethernet controller, SAR and USB. Most of the on-chip function blocks have been designed using an HDL synthesizer and the S5N8947 has been fully verified in Samsung's state-of-the-art ASIC test environment.

## 2. FEATURES

- ✓ 4-Kbyte unified cache

- ✓ SAR (Segmentation and Reassembly)

- ✓ UTOPIA (the Universal Test & Operations PHY Interface for ATM) Level 2 Interface

- ✓ Ethernet MAC

- ✓ Full-rate USB controller

- ✓ 2-CH GDMA (General Purpose Direct Memory Access)

- ✓ UART (Universal Asynchronous Receiver and Transmtter)

- ✓ 2 programmable 32bits Timers

- ✓ 18 Programmable I/O ports

- ✓ Interrupt controller

- ✓  $I^2C$  controller

- ✓ Built-in PLLs for System/USB

- ✓ Cost effective JTAG-based debug solution

- ✓ Boundary scan

- ✓ Operating Voltage Range(2.5V + 0.2V)

- ✓ Operating Frequency Up to 50MHz

- ✓ 208 TQFP Package

## **3. FUNCTIONAL BLOCK DESCRIPTIONS**

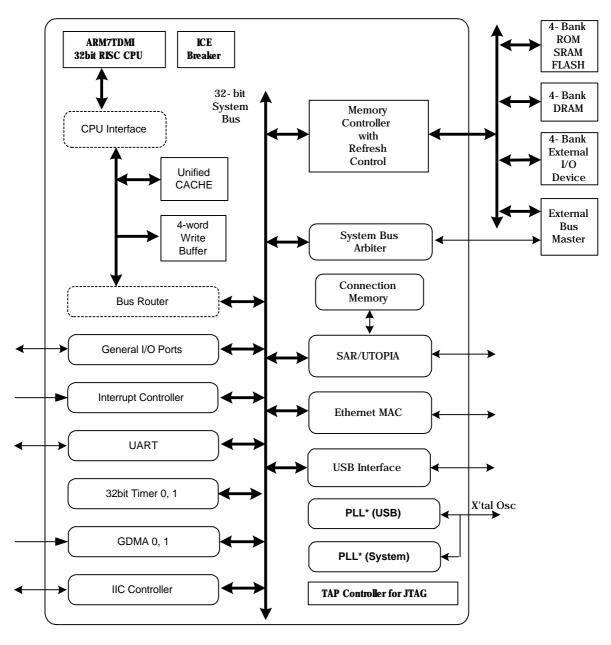

#### 3.1. Block Diagram

Figure 1 Top Block Diagram

#### 3.2. Architecture

Integrated system for embedded Ethernet / USB / SAR Fully 16/32-bit RISC architecture Efficient and powerful ARM7TDMI core Little/Big-Endian mode is supported basically, but the internal architecture is big-endian. Cost-effective JTAG-based debug solution Supports Boundary Scan

#### 3.3. System Manager

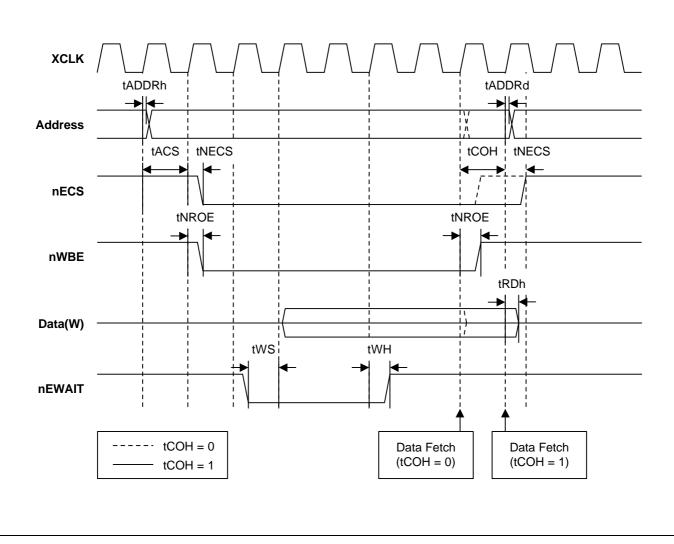

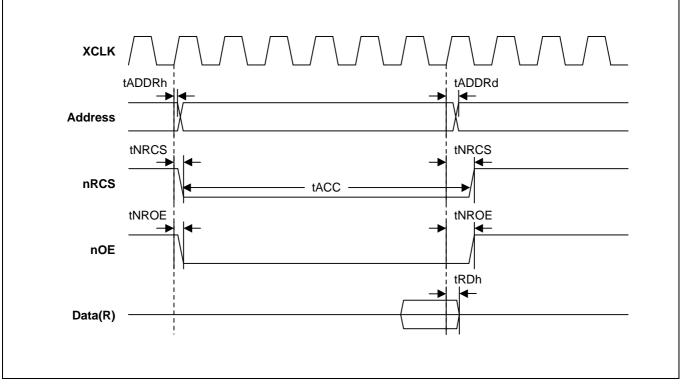

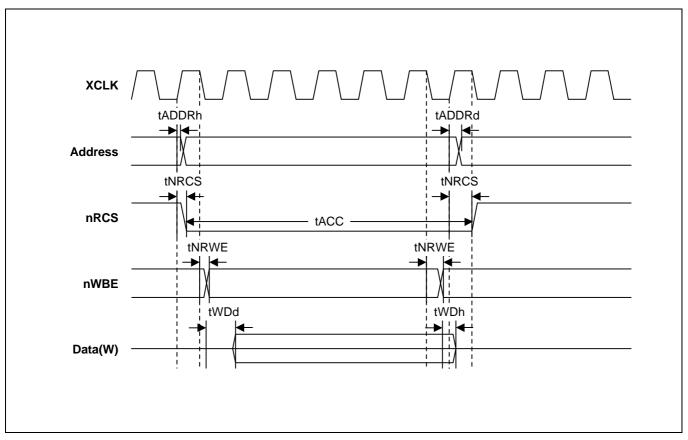

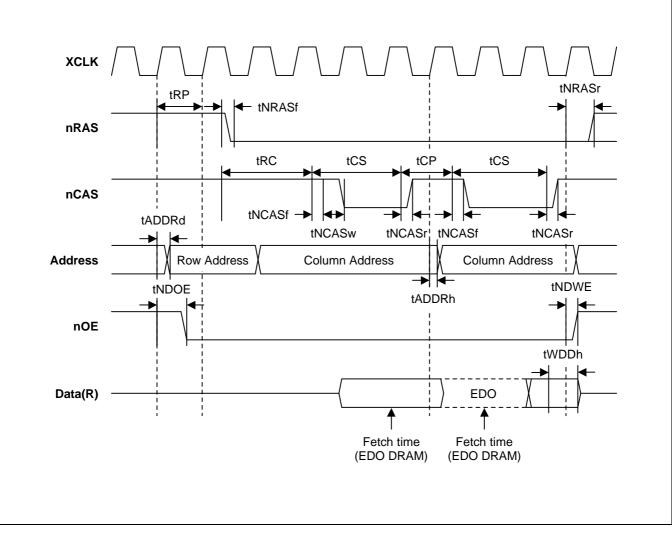

8/16/32-bit external bus support for ROM/SRAM, flash memory, DRAM and external I/O One external bus master with bus request/acknowledge pins Supports for EDO/normal or SDRAM Programmable access cycle Four-word depth write buffer Cost-effective memory-to-peripheral DMA interface

### 3.4. Unified Instruction/Data Cache

Two-way set-associative unified cache (4Kbytes) Supports for LRU (least recently used) Protocol Cache is configurable as internal SRAM

### 3.5. SAR/Utopia Interface

Directly supports ATM Adaptation Layer Five (AAL5) Segmentation And Reassembly Segments and reassembles data up to 70Mbps A glueless UTOPIA level 2 interface is supprted (for receiving and transmitting ATM cells with SAR, it is a standard ATM interface between ATM link and physical layer).

### 3.6. Ethernet MAC

2 DMA engines with burst mode Full compliance with IEEE standard 802.3 Supports MII interface (7-wire 10-Mbps interface is also supported).

#### 3.7. USB Controller

Supports 12Mbps full rate function for universal serial bus

#### 3.8. DMA Controller

2-channel general purpose DMA (for memory-to-memory, memory-to-USB, USB-to-memory, UARTto-memory, memory-to-UART data transfers without CPU intervention) Initiated by a software or a external DMA request Increments or decrements source or destination address in 8-bit, 16-bit or 32-bit data transfers

### 3.9. UART (Serial I/O)

UART (Serial I/O) block with DMA-based or interrupt-based operation Supports for 5-bit, 6-bit, 7-bit, or 8-bit serial data transmit and receive Programmable baud rates Infra-red (IR) TX/RX support (IrDA)

#### 3.10. Timers

Two programmable 32-bit timers Interval mode or toggle mode operation Supports a watchdog timer.

#### 3.11. Programmable I/O

18 programmable I/O ports Pins individually configurable to input, output, or I/O mode for dedicated signals

### 3.12. Interrupt Controller

18 interrupt sources, including 4 external interrupt sources Normal or fast interrupt mode (IRQ, FIQ) Prioritized interrupt handling

## 3.13. I<sup>2</sup>C Serial Interface

Single Master mode operation only

### 3.14. PLL (for System/USB)

The external clock can be multiplied by on-chip PLLs to provide high frequency System/USB clock The input frequency is fixed to 12 MHz

The output frequency is 4.167 times the input clock for System.

The output frequency is 4 times the input clock for USB.

## 4. PIN DESCRIPTIONS

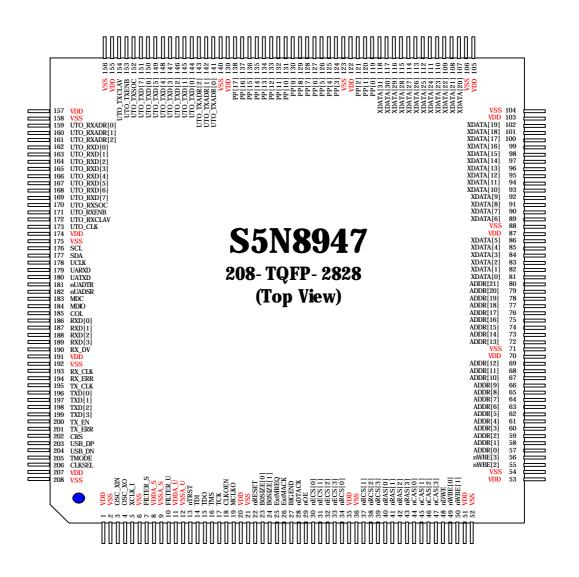

#### 4.1. Pin Configuration

Figure 2 S5N8947 Pin Configuration

## 4.2. Pin Descriptions

| Group          | Pin Name    | Pin    | I/O  | Description                                       |

|----------------|-------------|--------|------|---------------------------------------------------|

| T              |             | Counts | Туре | •                                                 |

|                | XCLK_I      | 1      | I    | External System Clock Source Input.               |

|                | MCLKO       | 1      | 0    | System Clock Out.                                 |

| ~              | CLKSEL      | 1      | I    | Clock Frequency Select from the internal PLL.     |

| System         | nRESET      | 1      | I    | System Reset, Low Active.                         |

| Configurations | CLKOEN      | 1      | I    | System Clock Out Enable.                          |

| (9)            | BIGEND      | 1      | I    | Big endian mode select pin.                       |

|                | FILTER_S    | 1      | 0    | PLL filter pin for System Clock Generation.       |

|                | OSC_XIN     | 1      | I    | 12MHz Reference Clock.                            |

|                | OSC_XO      | 1      | 0    | Crystal Clock Output.                             |

|                | TMODE       | 1      | I    | Test Mode Enable.                                 |

| TAP            | TCK         | 1      | I    | JTAG Test Clock Input.                            |

| Control        | TMS         | 1      | I    | JTAG Test Mode Select.                            |

| (5)            | TDI         | 1      | Ι    | JTAG Test Data Input.                             |

|                | TDO         | 1      | 0    | JTAG Test Data Output.                            |

|                | nTRST       | 1      | Ι    | JTAG Reset Signal, Low Active.                    |

|                | ADDR[21:0]  | 22     | 0    | Address Bus.                                      |

|                | XDATA[31:0] | 32     | I/O  | External Bidirectional 32bit Data Bus.            |

|                | nRAS[3:0]   | 4      | 0    | Row AddressSstrobe for DRAM, Low Active.          |

|                | nCAS[3:0]   | 4      | 0    | Column Address Strobe for DRAM, Low Active.       |

|                | nDWE        | 1      | 0    | Write Enable, Low Active.                         |

| Memory         | nECS[3:0]   | 4      | I/O  | External I/O Select, Low Active.                  |

| Interface      | nDTACK      | 1      | Ι    | External Data Acknowledge Signal.                 |

| (81)           | nRCS[3:0]   | 4      | 0    | ROM/SRAM/Flash Chip Select, Low Active.           |

|                | B0SIZE[1:0] | 2      | I    | Bank 0 Data Bus Size for Boot ROM.                |

|                | nOE         | 1      | 0    | Output Enable, Low Active.                        |

|                | nWBE[3:0]   | 4      | 0    | Write Byte Enable, Low Active.                    |

|                | ExtMREQ     | 1      | Ι    | External Master Bus Request.                      |

|                | ExtMACK     | 1      | 0    | External Bus Acknowledge.                         |

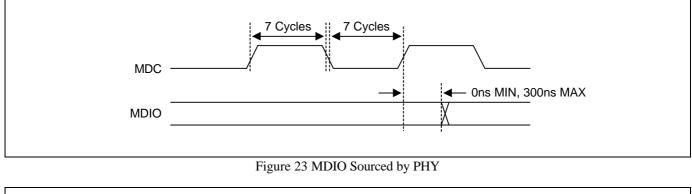

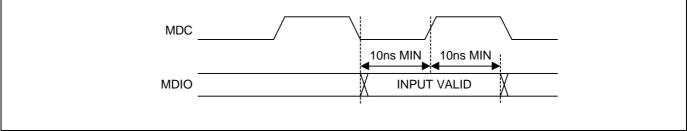

|                | MCD         | 1      | 0    | Management data clock.                            |

|                | MDIO        | 1      | I/O  | Management data I/O.                              |

|                | COL/COL_10M | 1      | I    | Collision detected/Collision detected for 10M.    |

|                | TX_CLK/     | 1      | Ι    | Transmit clk/Transmit clk for 10M.                |

|                | TX_CLK_10M  | -      | -    |                                                   |

|                | TXD[3:0]/   |        | _    |                                                   |

|                | TXD_10M/    | 4      | 0    | Transmit data/Transmit data for 10M.              |

|                | LOOP_10M    |        |      |                                                   |

| Ethernet       | TX_EN/      | 1      | 0    | Transmit enable/Transmit enable for 10M.          |

| Controller     | TXEN_10M    |        |      |                                                   |

| (18)           | TX_ERR/     | 1      | 0    | Transmit error/Packet compression enable for 10M. |

|                | PCOMP_10M   | 1      | T    | -                                                 |

|                | CRS/CRS_10M | 1      | Ι    | Carrier sense/Carrier sense for 10M.              |

|                | RX_CLK/     | 1      | Ι    | Receive clock/Receive clock for 10M.              |

|                | RXCLK_10M   |        |      |                                                   |

|                | RXD[3:0]/   | 4      | Ι    | Receive data/Receive data for 10M.                |

|                | RXD_10M     |        |      |                                                   |

|                | RX_DV/      | 1      | Ι    | Receive data valid.                               |

|                | LINK_10M    | 1      | т    |                                                   |

| LIADT          | RX_ERR      | 1      | I    | Receive error.                                    |

| UART           | UCLK        | 1      | I    | External Clock Input for UART.                    |

| (5)            | UARXD       | 1      | I    | UART Receive Data.                                |

| l              | UATXD       | 1      | 0    | UART Transmit Data.                               |

### S5N8947 (ADSL/Cable Modem MCU)

|                            | nUADTR                   | 1 | Ι   | UART Data Terminal Ready, Low Active.                 |

|----------------------------|--------------------------|---|-----|-------------------------------------------------------|

|                            | nUADSR                   | 1 | 0   | UART Data Set Ready, Low Active.                      |

| General                    | P[7:0]                   | 8 | I/O | General I/O ports for Bi-directional Data Only.       |

| Purpose<br>In/Out<br>Ports | xINTREQ[3:0]<br>/P[11:8] | 4 | I/O | External Interrupt Requests/General I/O Ports.        |

| (including<br>xINTREQ      | XDREQ[1:0]/<br>P[13:12]  | 2 | I/O | External DMA Requests for GDMA/General I/O Ports.     |

| nXDREQ<br>nXDACK           | nXDACK[1:0]/<br>P[15:14] | 2 | I/O | External DMA Acknowledge from GDMA/General I/O Ports. |

| TIMER0,1)<br>(18)          | TIMER0/<br>P[16]         | 1 | I/O | TIMER0 Out/General I/O Port.                          |

| (10)                       | TIMER1/<br>P[17]         | 1 | I/O | TIMER1 Out /General I/O Port.                         |

| I <sup>2</sup> C           | SCL                      | 1 | I/O | I <sup>2</sup> C Serial Clock.                        |

| (2)                        | SDA                      | 1 | I/O | I <sup>2</sup> C Seral Data.                          |

|                            | UTO_TXADR[2:0]           | 3 | 0   | Transmit Address Bus.                                 |

|                            | UTO_TXD[7:0]             | 8 | 0   | Transmit Data Bus to the ATM PHY.                     |

|                            | UTO_TXSOC                | 1 | 0   | Start Of Cell Indicator for Transmit Data.            |

|                            | UTO_TXENB                | 1 | 0   | Transmit Data Transfer Enable, Low Active.            |

| Utopia                     | UTO_TXCLAV               | 1 | Ι   | Cell Buffer Available for Transmit Data.              |

| (Level 2)                  | UTO_TXADR[2:0]           | 3 | 0   | Receive Address Bus.                                  |

| (30)                       | UTO_RXD[7:0]             | 8 | Ι   | Receive Data Bus from the ATM PHY.                    |

|                            | UTO_RXSOC                | 1 | Ι   | Start Of Cell Indicator for Receive Data.             |

|                            | UTO_RXENB                | 1 | 0   | Receive Data Transfer Enable, Low Active.             |

|                            | UTO_RXCLAV               | 1 | Ι   | Cell Buffer Available for Receive Data.               |

|                            | UTO_CLK                  | 1 | 0   | Transfer/Receive interface byte clock.                |

| LICD                       | USB_DP                   | 1 | I/O | USB data D+                                           |

| USB                        | USB_DN                   | 1 | I/O | USB data D-                                           |

| (3)                        | FILTER_U                 | 1 | 0   | USB PLL filter pin.                                   |

Table 1 Signal Pin Descriptions for Each Group

### 4.3. Pin Descriptions with the Pin number and Pad type

| Pin<br>No   | Pin Name          | I/O<br>Type | Pad type | Descriptions                       |

|-------------|-------------------|-------------|----------|------------------------------------|

| 1           | VDD               |             |          |                                    |

| 2           | VSS               |             |          |                                    |

| 3           | OSC_XIN           | Ι           | D 0      | 12MHz reference clock              |

| 4           | OSC_XO            | 0           | Psoscm2  | USB crystal clock out              |

| 5           | XCLK_I            | Ι           | ptic     | S5N8947 System Source Clock        |

| 6           | VSS               |             | •        |                                    |

| 7           | FILTER_S          | 0           | Poa_bb   | System PLL filter pin              |

| 8           | VDDA_S            | PWR         | vdda     | Analog power for PLL               |

| 9           | VSSA/VBBA_S       | GND         | vbba     | Analog / bulk ground for PLL       |

| 10          | FILTER_U          | 0           | poa_bb   | USB PLL filter pin                 |

| 11          | VDDA_U            | PWR         | vdda     | Analog power for PLL               |

| 12          | VSSA/VBBA_U       | GND         | vssa     | Analog / bulk ground for PLL       |

| 13          | nTRST             | Ι           | pticu    | JTAG Not Reset                     |

| 14          | TDI               | Ι           | pticu    | JTAG Test Data In                  |

| 15          | TDO               | 0           | ptot2    | JTAG Test Data Out                 |

| 16          | TMS               | Ι           | pticu    | JTAG Test Mode Select              |

| 17          | TCK               | Ι           | ptic     | JTAG Test Clock                    |

| 18          | CLKOEN            | Ι           | ptic     | Clock Out Enable/Disable           |

| 19          | MCLKO             | 0           | pob8     | System Clock Out                   |

| 20          | VDD               | PWR         |          |                                    |

| 21          | VSS               | GND         |          |                                    |

| 22          | nRESET            | Ι           | ptis     | Not Reset                          |

| 23-24       | B0SIZE[0:1]       | Ι           | ptic     | Bank 0 Data Bus Access Size        |

| 25          | ExtMREQ           | Ι           | ptic     | External Master bus request        |

| 26          | ExtMACK           | 0           | pob1     | External bus Acknowledge           |

| 27          | BIGEND            | Ι           | pticd    | Big endian mode select pin         |

| 28          | nDACK             | Ι           | ptic     | Not external acknowledge signal    |

| 29          | nOE               | 0           | ptot4    | Not output enable                  |

| 30-33       | nECS[0:3]         | В           | pbct4    | Not external I/O select            |

| 34-39       | nRCS[0:3]         | 0           | ptot4    | Not ROM/SRAM/Flash Chip select     |

| 40-43       | nRAS[0:3]         | 0           | ptot4    | Not Row address strobe for DRAM    |

| 44-47       | nCAS[0:3]         | 0           | ptot4    | Not Column address strobe for DRAM |

| 48          | nDWE              | 0           | ptot4    | Not Write Enable                   |

| 49-50       | NWBE[0:1]         | 0           | ptot4    | Not Write Byte Enable              |

| 51          | VDD               | PWR         |          |                                    |

| 52          | VSS               | GND         |          |                                    |

| 53          | VDD               | PWR         |          |                                    |

| 54          | VSS               | GND         |          | Net Welte Dete Details             |

| 55-56       | NWBE[2:3]         | 0           | ptot4    | Not Write Byte Enable              |

| 57-69       | ADDR[0:12]        | O<br>DWD    | ptot6    | Address bus                        |

| 70          | VDD               | PWR         |          |                                    |

| 71          | VSS               | GND         | ntate    | Address bus                        |

| 72-80       | ADDR[13:21]       | O<br>B      | ptot6    | Address bus                        |

| 81-86<br>87 | XDATA[0:5]<br>VDD | PWR         | ptbsut6  | External bidirectional data bus    |

| 87<br>88    | VDD<br>VSS        | GND         |          |                                    |

| 88-<br>89-  | v 33              | UND         |          |                                    |

| 102         | XDATA[6:19]       | В           | ptbsut6  | External bidirectional data bus    |

| 102         | VDD               | PWR         |          |                                    |

| 103         | VSS               | GND         |          |                                    |

| 104         | v 33              | UND         |          |                                    |

| 107-<br>118 | XDATA[20:31]          | В   | ptbsut6  | External bidirectional data bus                  |

|-------------|-----------------------|-----|----------|--------------------------------------------------|

| 119-<br>121 | P[0:2]                | В   | ptbst4sm | General I/O ports                                |

| 121         | VDD P                 | PWR |          |                                                  |

| 122         | VSS_P                 | GND |          |                                                  |

| 123         |                       |     |          |                                                  |

| 138         | P[3:17]               | В   | ptbst4sm | General I/O ports                                |

| 139         | VDD_P                 | PWR |          |                                                  |

| 140         | VDD_S                 | GND |          |                                                  |

| 141-<br>143 | UTO_TXADR[0:2]        | О   |          | Address bus for TX                               |

| 144-<br>151 | UTO_TXD[0:7]          | О   | pob4     | Data bus for TX                                  |

| 152         | UTO_TXSOC             | 0   | pob4     | Start Of Cell for TX                             |

| 153         | UTO_TXENB             | 0   | pob4     | Enable data transfers (active low)               |

| 154         | UTO_TXCLAV            | Ι   | ptis     | Cell Buffer Available                            |

| 155         | VDD_P                 | PWR | vdd3op   | I/O pad power                                    |

| 156         | VSS_P                 | GND | vssop    | I/O pad ground                                   |

| 157         | VDD_P                 | PWR | vdd3op   | I/O pad power                                    |

| 158         | VSS_P                 | GND | vssop    | I/O pad ground                                   |

| 159-<br>161 | UTOP_RXADR[0:2]       | 0   |          | Address bus for RX                               |

| 162-<br>169 | UTO_RXD[0:7]          | Ι   | ptis     | Data bus for RX                                  |

| 170         | UTO_RXSOC             | Ι   | ptic     | Start Of Cell for RX                             |

| 171         | UTO_RXENB             | 0   | pob4     | Enable data transfers (active low)               |

| 172         | UTO_RXCLAV            | Ι   | ptis     | Cell Buffer available                            |

| 173         | UTO_CLK               | 0   | pob4     | Transfer/Receive interface byte clock            |

| 174         | VDD_I                 | PWR |          |                                                  |

| 175         | VSS_I                 | GND |          |                                                  |

| 176         | SCL                   | В   | ptbcd4   | I <sup>2</sup> C serial clock                    |

| 177         | SDA                   | В   | ptbcd4   | I <sup>2</sup> C serial data                     |

| 178         | UCLK                  | Ι   | ptis     | UART external clock for UART                     |

| 179         | UARXD                 | Ι   | ptic     | UART receive data                                |

| 180         | UATXD                 | 0   | pob4     | UART transmit data                               |

| 181         | nUADTR                | Ι   | ptic     | Not UART0 data terminal ready                    |

| 182         | nUADSR                | 0   | pob4     | Not UART0 data set ready                         |

| 183         | MDC                   | 0   | pob4     | Management data clock                            |

| 184         | MDIO                  | 0   | ptbbcut4 | Management data I/O                              |

| 185         | COL/COL_10M           | I   | ptis     | Collision detected/Collision detected for 10M    |

| 186-<br>189 | RXD[0:3]/RXD_10M      | Ι   | ptis     | Receive data/Receive data for 10M                |

| 190         | RX_DV/LINK_10M        | Ι   | ptis     | Receive data valid                               |

| 191         | VDD                   | PWR |          |                                                  |

| 192         | VSS                   | GND |          |                                                  |

| 193         | RX_CLK/RXCLK_10<br>M  | Ι   | ptis     | Receive clock/Receive clock for 10M              |

| 194         | RX_ERR                | Ι   | ptis     | Receive error                                    |

| 195         | TX_CLK/TX_CLK_10<br>M | Ι   | ptis     | Transmit clock/Transmit clock for 10M            |

| 196-        | TXD[0:3]/TXD_10M/     | 0   | pob4     | Transmit data/Transmit data for 10M              |

| 199         | LOOP_10M              |     | -        |                                                  |

| 200         | TX_EN/TXEN_10M        | 0   | pob4     | Transmit enable/Transmit enable for 10M          |

| 201         | TX_ERR/PCOMP_10<br>M  | 0   | pob4     | Transmit error/Packet compression enable for 10M |

| 202         | CRS/CRS_10M           | Ι   | ptis     | Carrier sense/Carrier sense for 10M              |

#### S5N8947 (ADSL/Cable Modem MCU)

| 203 | USB_DP | В   | mhuah 1 | USB data D+              |

|-----|--------|-----|---------|--------------------------|

| 204 | USB_DN | В   | pbusb1  | USB data D-              |

| 205 | TMODE  | Ι   | ptic    | Test Mode                |

| 206 | CLKSEL | Ι   | ptic    | Clock Out Enable/Disable |

| 207 | VDD    | PWR |         |                          |

| 208 | VSS    | GND |         |                          |

## **5. OPERATION DESCRIPTION**

#### 5.1. CPU Core Overview

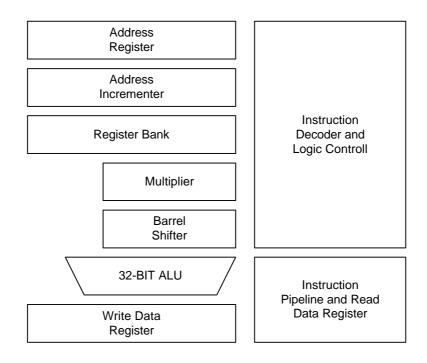

The S5N8947 CPU core is the ARM7TDMI processor, a general purpose, 32-bit microprocessor developed by Advanced RISC Machines, Ltd. (ARM). The core's architecture is based on Reduced Instruction Set Computer (RISC) principles. The RISC architecture makes the instruction set and its related decoding mechanisms simpler and more efficient than those with microprogrammed Complex Instruction Set Computer (CISC) systems. The resulting benefit is high instruction throughput and impressive real-time interrupt response. Pipelining is also employed so that all components of the processing and memory systems can operate continuously. The ARM7TDMI has a 32-bit address bus. An important feature of the ARM7TDMI processor, and one which differentiates it from the ARM7 processor, is a unique architectural strategy called THUMB. The THUMB strategy is an extension of the basic ARM architecture and consists of 36 instruction formats. These formats are based on the standard 32-bit ARM instruction set, but have been re-coded using 16-bit wide opcodes.

#### Figure 3 ARM7TDMI Core Block Diagram

Because THUMB instructions are one-half the bit width of normal ARM instructions, they produce very high-density code. When a THUMB instruction is executed, its 16-bit opcode is decoded by the processor into its equivalent instruction in the standard ARM instruction set. The ARM core then processes the 16-bit instruction as it would a normal 32-bit instruction. In other words, the THUMB architecture gives 16-bit systems a way to access the 32-bit performance of the ARM core without incurring the full overhead of 32-bit processing. Because the ARM7TDMI core can execute both standard 32-bit ARM instructions and 16-bit THUMB instructions, it lets you mix routines of THUMB instructions and ARM code in the same address space. In this way, you can adjust code size and performance, routine by routine, to find the best programming solution for a specific application.

#### 5.2. Instruction Set

The S5N8947 instruction set is divided into two subsets: a standard 32-bit ARM instruction set and a *16-bit THUMB instruction set*.

The 32-bit ARM instruction set is comprised of thirteen basic instruction types which can be divided into four broad classes:

- Four types of branch instructions which control program execution flow, instruction privilege levels, and switching between ARM code and THUMB code.

- Three types of data processing instructions which use the on-chip ALU, barrel shifter, and multiplier to perform high-speed data operations in a bank of 31 registers (all with 32-bit register widths).

- Three types of load and store instructions which control data transfer between memory locations and the registers. One type is optimized for flexible addressing, another for rapid context switching, and the third for swapping data.

- Three types of co-processor instructions which are dedicated to controlling external co-processors. These instructions extend the off-chip functionality of the instruction set in an open and uniform way.

**NOTE :** All 32-bit ARM instructions can be executed conditionally.

The 16-bit THUMB instruction set contains 36 instruction formats drawn from the standard 32-bit ARM instruction set. The THUMB instructions can be divided into four functional groups:

- Four branch instructions.

- Twelve data processing instructions, which are a subset of the standard ARM data processing instructions.

- Eight load and store register instructions.

- Four load and store multiple instructions.

**NOTE :** Each 16-bit THUMB instruction has a corresponding 32-bit ARM instruction with the identical processing model.

The 32-bit ARM instruction set and the 16-bit THUMB instruction sets are good targets for compilers of many different high-level languages. When assembly code is required for critical code segments, the ARM programming technique is straightforward, unlike that of some RISC processors which depend on sophisticated compiler technology to manage complicated instruction interdependencies.

Pipelining is employed so that all parts of the processor and memory systems can operate continuously. Typically, while one instruction is being executed, its successor is being decoded, and a third instruction is being fetched from memory.

### **5.3. OPERATING STATES**

From a programmer's point of view, the ARM7TDMI core is always in one of two operating states. These states, which can be switched by software or by exception processing, are:

- ARM state (when executing 32-bit, word-aligned, ARM instructions), and

- *THUMB state* (when executing 16-bit, half-word aligned THUMB instructions).

#### **5.4. OPERATING MODES**

The ARM7TDMI core supports seven operating modes:

- User mode: the normal program execution state

- FIQ (Fast Interrupt Request) mode: for supporting a specific data transfer or channel process

- IRQ (Interrupt ReQuest) mode: for general purpose interrupt handling

- Supervisor mode: a protected mode for the operating system

- Abort mode: entered when a data or instruction pre-fetch is aborted

- System mode: a privileged user mode for the operating system

- Undefined mode: entered when an undefined instruction is executed

Operating mode changes can be controlled by software, or they can be caused by external interrupts or exception processing. Most application programs execute in User mode. Privileged modes (that is, all modes other than User mode) are entered to service interrupts or exceptions, or to access protected resources.

#### 5.5. REGISTERS

The S5N8947 CPU core has a total of 37 registers: 31 general-purpose 32-bit registers, and 6 status registers. Not all of these registers are always available. Which registers are available to the programmer at any given time depends on the current processor operating state and mode.

**NOTE :** When the S5N8947 is operating in ARM state, 16 general registers and one or two status registers can be accessed at any time. In privileged mode, mode-specific banked registers are switched in.

Two register sets, or banks, can also be accessed, depending on the core's current state: the ARM state register set and the *THUMB state register* set:

- The ARM state register set contains 16 directly accessible registers: R0-R15. All of these registers, except for R15, are for general-purpose use, and can hold either data or address values. An additional (seventeenth) register, the CPSR (Current Program Status Register), is used to store status information.

- The THUMB state register set is a subset of the ARM state set. You can access eight general registers, R0-R7, as well as the program counter (PC), a stack pointer register (SP), a link register (LR), and the CPSR. Each privileged mode has a corresponding banked stack pointer, link register, and saved process status register (SPSR).

The THUMB state registers are related to the ARM state registers as follows:

- THUMB state R0-R7 registers and ARM state R0-R7 registers are identical

- THUMB state CPSR and SPSRs and ARM state CPSR and SPSRs are identical

- THUMB state SP, LR, and PC map directly to ARM state registers R13, R14, and R15, respectively

In THUMB state, registers R8-R15 are not part of the standard register set. However, you can access them for assembly language programming and use them for fast temporary storage, if necessary.

### 5.6. EXCEPTIONS

An exception arises whenever the normal flow of program execution is interrupted. For example, when processing must be diverted to handle an interrupt from a peripheral. The processor's state just prior to handling the exception must be preserved so that the program flow can be resumed when the exception routine is completed. Multiple exceptions may arise simultaneously.

To process exceptions, the S5N8947 uses the banked core registers to save the current state. The old PC value and the CPSR contents are copied into the appropriate R14 (LR) and SPSR register. The PC and mode bits in the CPSR are forced to a value which corresponds to the type of exception being processed.

The S5N8947 core supports seven types of exceptions. Each exception has a fixed priority and a corresponding privileged processor mode, as shown in following Table

| Exception             | Mode on Entry   | Priority    |

|-----------------------|-----------------|-------------|

| Reset                 | Supervisor mode | 1 (highest) |

| Data abort            | Abort mode      | 2           |

| FIQ                   | FIQ mode        | 3           |

| IRQ                   | IRQ mode        | 4           |

| Prefetch abort        | Abort mode      | 5           |

| Undefined instruction | Undefined mode  | 6           |

| SWI                   | Supervisor mode | 6 (lowest)  |

Table 2 S5N8947 CPU Exceptions

## 6. HARDWARE STRUCTURE

#### 6.1. System Manager

#### 6.1.3. Overview

The S5N8947 microcontroller's System Manager has the following functions.

- To arbitrate system bus access requests from several master blocks, based on fixed priorities.

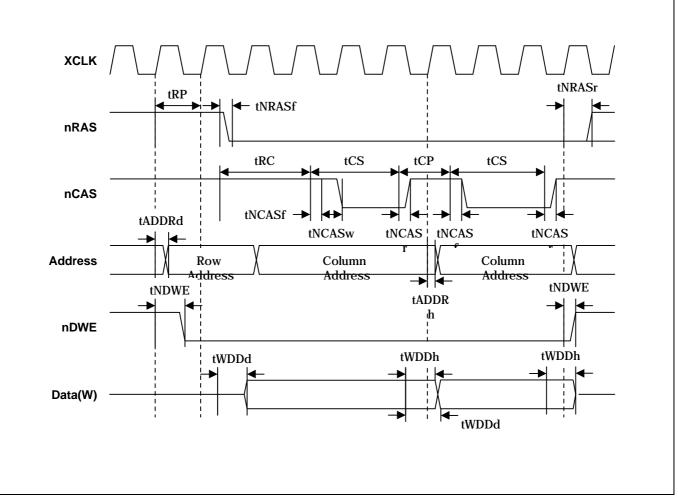

- To provide the required memory control signals for external memory accesses. For example, if a master block such as the DMA controller or the CPU generates an address which corresponds to a DRAM bank, the System Manager's DRAM controller generates the required normal/EDO or SDRAM access signals. The interface signals for normal/EDO or SDRAM can be switched by SYSCFG[31].

- To provide the required signals for bus traffic between the S5N8947 and ROM/SRAM and the external I/O banks.

- To compensate for differences in bus width for data flowing between the external memory bus and the internal data bus.

- To support both little and big endian for external memory or I/O devices. Internal registers, however, operate under big-endian mode.

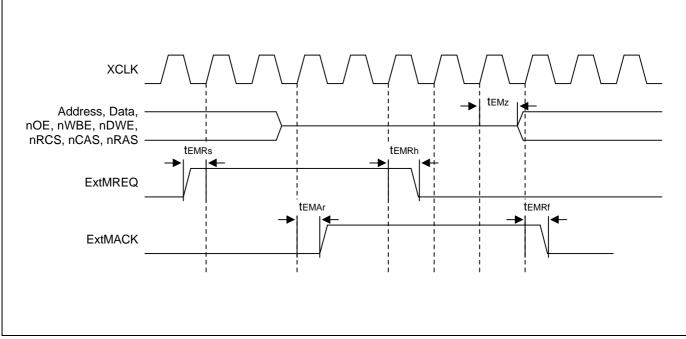

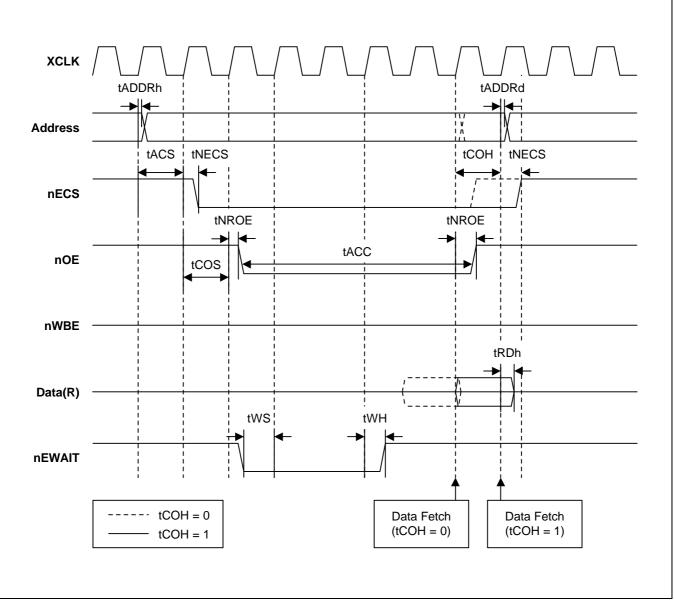

**Note** : By generating an external bus request (ExtMREQ), an external device can access the S5N8947's external memory. The S5N8947 can access slow external devices using a nDTACK signal. The DTACK signal, which is generated by the external device, extends the duration of the CPU's memory access cycle beyond its programmable value.

#### 6.1.4. System Manager Registers

To control external memory operations, the System Manager uses a dedicated set of special registers. By programming the values in the System Manager special registers, you can specify such things as :

- Memory type

- External bus width access cycle

- Control signal timing (RAS and CAS, for example)

- Memory bank locations

- Size of each memory bank to be used for arbitrary address spacing

The System Manager uses special register setting to control the generation and processing of the control signals, addresses, and data that are required by external devices in a standard system configuration. Special registers are also used to control access to ROM/SRAM/Flash banks, up to four DRAM banks and four external I/O banks, and a special register mapping area.

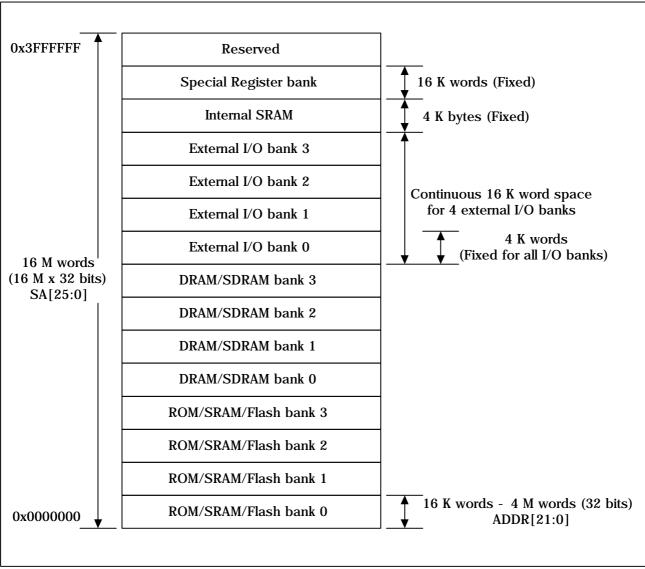

The address resolution for each memory bank base pointer is 64 Kbytes (16 bits). The base address pointer is 10 bits. This gives a total addressable memory bank space of 16 M words.

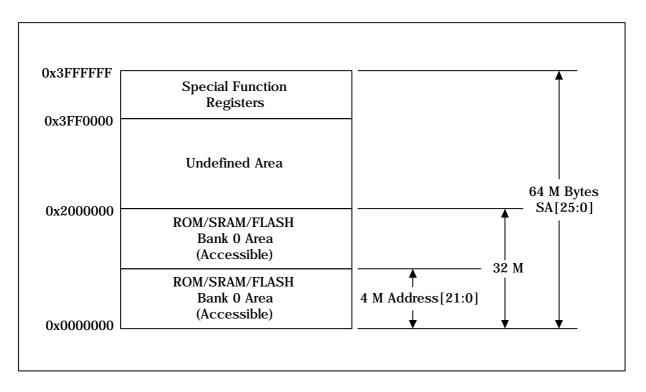

Figure 4 S5N8947 System Memory Map

#### 6.1.5. System Memory Map

Followings are several important features to note about the S5N8947 system memory map :

• The size and location of each memory bank is determined by the register settings for "current bank base pointer" and "current bank end pointer". You can use this base/next bank pointer concept to set up a consecutive memory map. To do this, you set the base pointer of the "next bank" to the same address as the next pointer of the "current bank". Please note that when setting the bank control registers, the address boundaries of consecutive banks must not overlap. This can be applied even if one or more banks are disabled.

- Four external I/O banks are defined in a continuous address space. A programmer can only set the base pointer for external I/O bank 0. The start address of external I/O bank 1 is then calculated as the external I/O bank 0 start address +16 K. Similary, the start address for external I/O bank 2 is the external I/O bank 0 start address + 32 K, and the start address for external I/O bank 3 is the external I/O bank 0 start address + 48 K. Therefore, the total consecutive addressable space of the four external banks is defined as the start address of external I/O bank 0 + 64 K bytes.

- Within the addressable space, the start address of each I/O bank is not fixed. You can use bank control registers to assign a specific bank start address by setting the bank's base pointer. The address resolution is 64 K bytes. The bank's start address is defined as "base pointer << 16" and the bank's end address (except for external I/O banks) is "next pointer << 16 1".

After a power-on or system reset, all bank address pointer registers are initialized to their default values. In this means that a system reset automatically defines ROM bank 0 as a 32-Mbyte space with a start address of zero. This means that, except for ROM bank 0, all banks are undefined following a system startup.

The reset value for the next pointer and base pointer of ROM bank 0 are 0x200 and 0x000, respectively. This means that a system reset automatically defines ROM bank 0 as a 32-Mbyte space with a start address of zero. This initial definition of ROM bank 0 lets the system power-on or reset operation pass control to the user-supplied boot code that is stored in external ROM. (This code is located at address 0 in the system memory map.) When the boot code (i.e. ROM program) executes, it performs various system initialization tasks and reconfigures the system memory map according to the application's actual external memory and device configuration.

The initial system memory map following system startup is shown in following :

Figure 5 Initial system memory map (After reset)

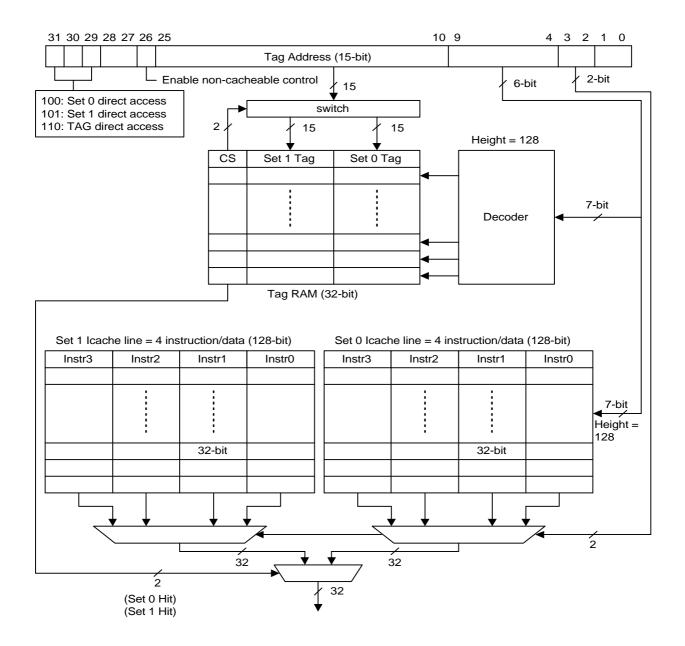

#### 6.2. Instruction / Data Cache

The S5N8947 CPU has a unified internal 4-Kbyte instruction/data cache. The cache is configured using two-way, set-associative addressing. The replacement algorithm is pseudo-LRU (Least Recently Used). The cache line size is four words (16 bytes). When a miss occurs, four word must be fetched consecutively from external memory. Typically, RISC processors take advantage of unified instruction/data caches to improve performance.

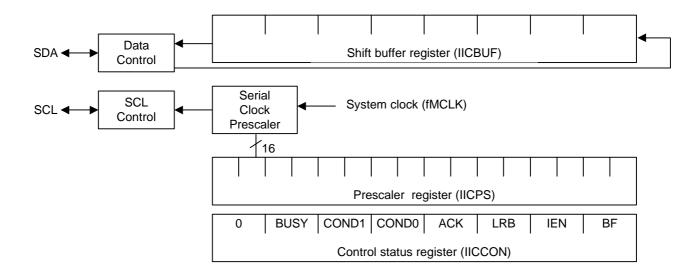

### 6.3. I<sup>2</sup>C Bus Controller

The S5N8947's Internal IC bus ( $I^2$ C-bus) controller has the following important features :

- It requires only two bus lines, a serial data line (SDA) and a serial clock line (SCL). When the I<sup>2</sup>C-bus is free, both lines are High level.

- Each device that is connected to the bus is software-addressable by a unique address. Slave relationships on the bus are constant. The bus master can be either a master-transmitter or a master-receiver. The I<sup>2</sup>C bus controller supports only single master mode.

- It supports 8-bit, bi-directional, serial data transfers.

- The number of ICs that you can connect to the same I<sup>2</sup>C-bus is limited only by the maximum bus capacitance of 400 pF.

Following figure shows a block diagram of the S5N8947's I<sup>2</sup>C-bus controller.

Figure 6 I<sup>2</sup>C-Bus block diagram

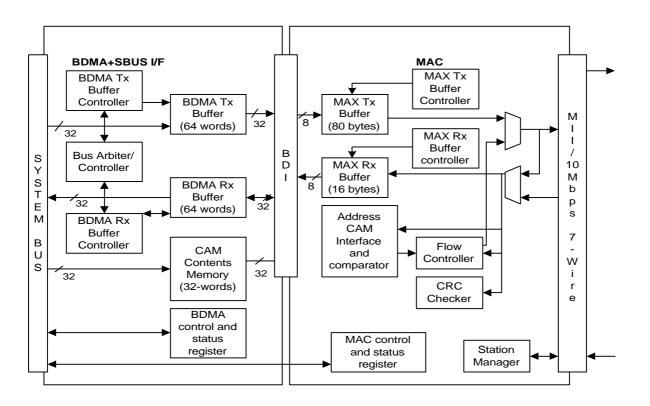

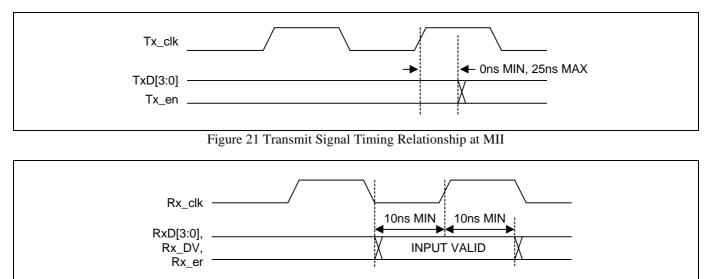

#### 6.4. Ethernet Controller

The S5N8947 has an Ethernet controller which operates at either 100/10-Mbits per second in halfduplex or full-duplex mode. In half-duplex mode, the controller supports the IEEE 802.3 Carrier Sense Multiple Access with Collision Detection (CSMA/CD) protocol. In full-duplex mode, it supports the IEEE 802.3 MAC Control Layer, including the Pause operation for flow control.

#### 6.4.1. Block Diagram

Figure 7 Ethernet controller block diagram

#### 6.4.2. Features and Benefits

The most important features and benefits of the S5N8947 Ethernet controller are follows :

- Cost-effective connection to an external Repeater Interface Controller(RIC)/Ethernet backbone

- Buffered DMA (BDMA) engine using Burst mode

- BDMA Tx/Rx buffers (256 bytes/256 bytes)

- MAC Tx/Rx FIFOs (80 bytes/16 bytes) to support re-transmit after collision without DMA request and to handle DMA latency

- Data alignment logic

- Supports for old and new media (compatible with existing 10-Mbit/s networks)

- Full IEEE 802.3 compatibility for existing applications

- Provides a standard Media Independent Interface (MII)

- Provides an external 7-wire interface, also.

- Station Management (STA) signaling for external physical layer configuration and link negotiation

- On-chip CAM (21 addresses)

- Full-duplex mode for doubled bandwidth

- Pause operation hardware support for full-duplex flow control

- Long packet mode for specialized environments

- Short packet mode for fast testing

- PAD generation for ease of processing and reduced processing time

- Support for old and new media : Compatible with existing 100/10Mbit/s networks.

- Full IEEE 802.3 compatibility : Compatible with existing hardware and software.

- Standard CSMA/CD,Full duplex capability at 100/10 Mbit/s : Increase in data throughput performance.

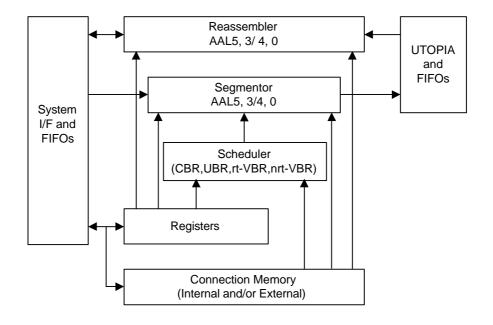

#### 6.5. SAR and Utopia Interface

The S5N8947 provides ATM layer Segmentation and Reassembly (SAR) function over a 8bit UTOPIA interface. The S5N8947 delivers an integrated solution for performing the SAR tasks required to communicate over an ATM network. The device translates packet-based data into 53-byte ATM cells that are asynchronously mapped into various physical media. The S5N8947 can be effectively applied for equipment requiring an interface between packet-based data and ATM-based networks.

#### 6.5.1. Block Diagram

Figure 8 SAR function block diagram

#### 6.5.2. Features and Benefits

- Supports CBR, UBR, rt-VBR and nrt-VBR traffic with rates set on a per-VC or per-VP basis.

- Supports AAL0 (raw cells) and AAL5 segmentation and reassembly.

- Segments and reassembles data up to about 70M bps via UTOPIA interface.

- Generates and verifies CRC-10 for OAM cells and AAL3/4 cells.

- Supports concurrent OAM cells and AAL5 cells on each active connection.

- Supports simultaneous segmentation and reassembly of up to 32 connections with internal memory and up to 4K connections with external memory.

- On chip 8K bytes SRAM for internal connection memory.

- Supports Contents Addressable Memory (CAM) for channel mapping (up to 32 connections).

- Supports packet sizes up to 64K bytes.

- Supports scatter and gather packet capability for large packets

- Start of Packet offset available for ease of implementing bridging and routing between different protocols.

- Provides glue-less UTOPIA level 2 interface (up to 7 PHYs).

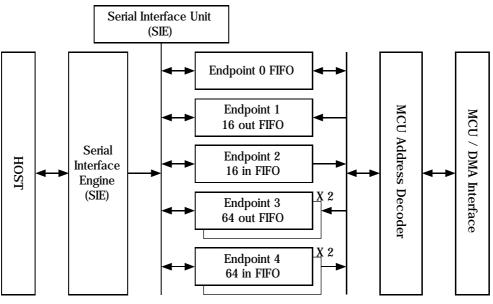

#### 6.6. USB Controller

The Universal Serial Bus (USB) is an industry standard bus architecture for computer peripheral attachment. The USB provides a single interface for easy, plug-and-play, hot-plug attachment of peripherals such as keyboard, mouse, speakers, printers, scanners, and communication devices. The USB allows simultaneous use of many different peripherals with a combined transfer rate of up to 12 Mbit/s.

The S5N8497 controller includes a highly flexible integrated USB peripheral controller that lets designers implement a variety of microcontroller-based USB peripheral devices for telephony, audio, or other high-end applications. The S5N8947 controller is intended for USB peripherals that use the full-speed signalling rate of 12 Mbit/s. The USB low-speed rate (1.5 Mbit/s) is not supported. An integrated USB transceiver is provided to minimize system device count and cost, but an external transceiver can be used instead, if required. The USB peripheral controller's features meet or exceed all of the USB device class resource requirements defined by the USB specification Version 1.0 and 1.1. Consult the USB specification for details about overall USB system design. The integrated USB peripheral controller provides a very efficient and easy-to-use interface, so that device software (or firmware) does not incur the overhead of managing low-level USB protocol requirements.

The USB peripheral controller hardware implements a number of USB standard commands directly; the rest can be implemented in device software. In addition, the USB peripheral controller provides a high degree of flexibility to help designers accommodate vendor- or device-class-specific commands, as well as any new features that might be added in future USB specifications.

Specialized hardware is provided to support Bulk data transfers. Using the Microcontroller's DMA features, large size of bulk transfers from an off-chip peripheral, can be automatically synchronized to the USB data rate with little or no CPU overhead.

Robust error detection and management features are provided so the device software can manage transfers in any number of ways as required by the application. The USB suspend/ resume, reset, and remote wake up features are also supported.

#### 6.6.1. Block Diagram

Figure 9 USB Module Block Diagram

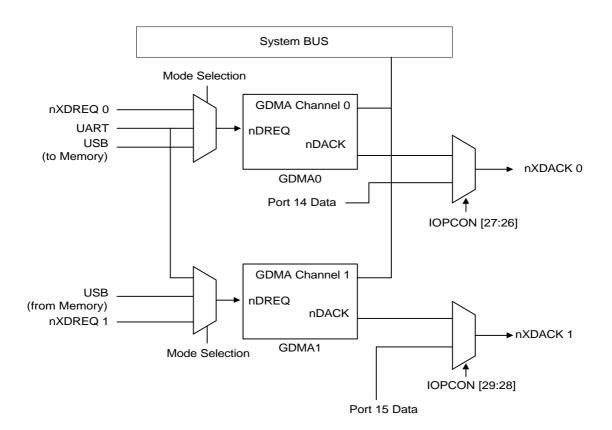

#### 6.7. DMA Controller

The S5N8947 has a two-channel general DMA controller, called the GDMA. The two-channel GDMA performs the following data transfers without CPU intervention:

- Memory-to-memory (memory to/from memory)

- UART-to-memory (serial port to/from memory)

- USB-to-memory (USB port to/from memory)

The on-chip GDMA can be started by software and/or by an external DMA request (nXDREQ). Software can also be used to restart a GDMA operation after it has been stopped.

The CPU can recognize when a GDMA operation has been completed by software polling and/or when it receives an appropriate internally generated GDMA interrupt. The S5N8947 GDMA controller can increment or decrement source or destination addresses and conduct 8-bit (byte), 16-bit (half-word), or 32-bit (word) data transfers.

Figure 10 GDMA controller block diagram

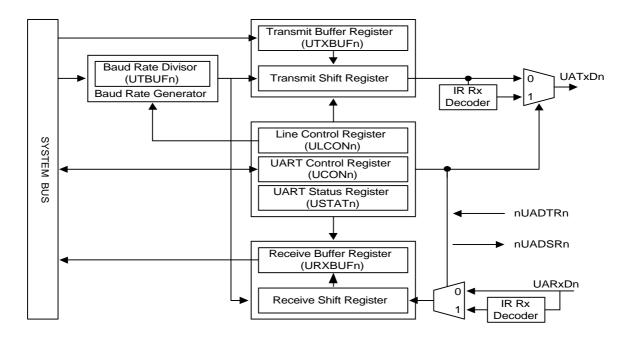

### 6.8. UART(Serial I/O)

The S5N8947 UART (Universal Asynchronous Receiver/Transmitter) unit provides an asynchronous serial I/O (SIO) port. This can operate in interrupt-based or DMA-based mode. That is, the UART can generate internal interrupts or DMA requests to transfer data between the CPU and the serial I/O port.

The most important features of the S5N8947 UART include:

- Programmable baud rates

- Infra-red (IR) transmit/receive

- Insertion of one or two Stop bits per frame

- Selectable 5-bit, 6-bit, 7-bit, or 8-bit data transfers

- Parity checking

This unit has a baud rate generator, transmitter, receiver, and a control unit, as shown in next figure. The baud-rate generator can be driven by the internal system clock, MCLK. The transmitter and receiver block use this baud rate clock and have independent data buffer registers and data shifters.

Transmit data is written first to the transmit buffer register. From there, it is copied to the transmit shifter and then shifted out by the transmit data pin, UATXDn. Receive data is shifted in by the receive data pin, UARXDn. It is then copied from the shifter to the receive buffer register when one data byte has been received.

This unit provides software controls for mode selection, and for status and interrupt generation.

Figure 11 UART block diagram

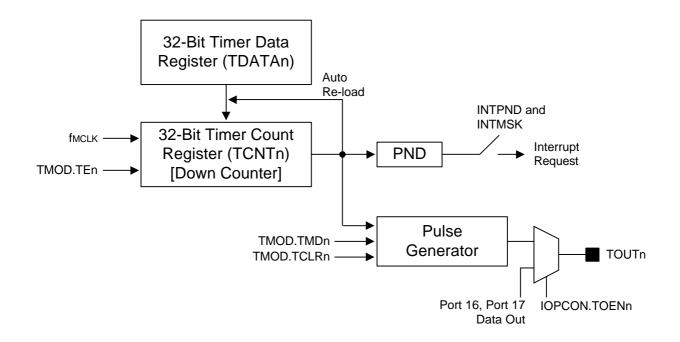

#### 6.9. Timers

The S5N8947 has two 32-bit timers. These timers can operate in interval mode or in toggle mode. The output signals are TOUT0 and TOUT1, respectively.

You enable or disable the timers by setting control bits in the timer mode register, TMOD. An interrupt request is generated whenever a timer count-out (down count) occurs.

Watchdog timer is also implemented in the S5N8947. The following guidelines apply to watchdog timer functions:

- When a watchdog timer is enabled, it loads a data value to its count register and begins decrementing the count register value by the system clock.

- If the reset from the watchdog timer (WDRESET) reaches to zero, the Watchdog will start its reset sequence. The reset value is then reloaded and the watchdog timer is disabled.

- The WDRESET performs the same function as the External Reset (System Reset) to each block.

Figure 12 32-bit timer block diagram

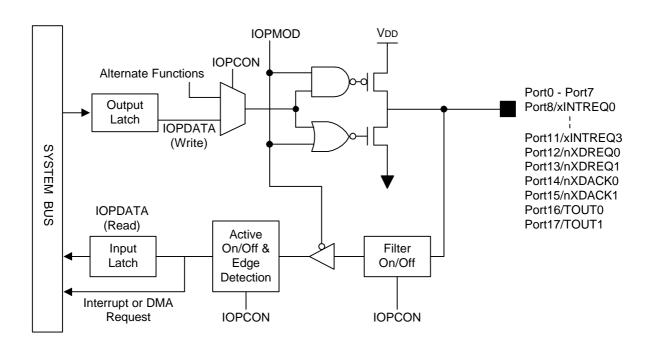

#### 6.10. I/O Ports

The S5N8947 has 18 programmable I/O ports. You can configure each I/O port to input mode, output mode, or special function mode. To do this, you write the appropriate settings to the IOPMOD and IOPCON registers. User can set filtering for the input ports using IOPCON register.

The modes of the ports from port0 to port7 are determined only by the IOPMOD register. But port[11:8] can be used as xINTREQ[3:0], port[13:12] as nXDREQ[1:0], port[15:14] as nXDACK[1:0], port[16] as TOUT0, or port[17] as TOUT1 depending on the settings in IOPCON register.

Figure 13 I/O port function diagram

#### 6.11. Interrupt Controller

The S5N8947 interrupt controller has a total of 18 interrupt sources. Interrupt requests can be generated by internal function blocks and external pins.

The ARM7TDMI core recongnizes two kinds of interrupts: a normal interrupt request (IRQ), and a fast interrupt request (FIQ). Therefore all S5N8947 interrupts can be categorized as either IRQ or FIQ. The S5N8947 interrupt controller has an interrupt pending bit for each interrupt source.

Four special registers are used to control interrupt generation and handling:

- Interrupt priority registers. The index number of each interrupt source is written to the pre-defined interrupt priority register field to obtain that priority. The interrupt priorities are pre-defined from 0 to 17.

- Interrupt mode register. Defines the interrupt mode, IRQ or FIQ, for each interrupt source.

- Interrupt pending register. Indicates that an interrupt request is pending. If the pending bit is set, the interrupt pending status is maintained until the CPU clears it by writing a "1" to the appropriate pending register. When the pending bit is set, the interrupt service routine starts whenever the interrupt mask register is "0". The service routine must clear the pending condition by writing a "1" to the appropriate pending bit. This avoids the possibility of continuous interrupt requests from the same interrupt pending bit.

- Interrupt mask register. Indicates that the current interrupt has been disabled if the corresponding mask bit is "1". If an interrupt mask bit is "0" the interrupt will be serviced normally. If the global mask bit (bit 18) is set to "1", no interrupts are serviced. However, the source's pending bit is set if the interrupt is generated. When the global mask bit has been set to "0", the interrupt is serviced.

| Index Values | Interrupt Sources                     |

|--------------|---------------------------------------|

| [17]         | I <sup>2</sup> C-bus interrupt        |

| [16]         | Ethernet controller MAC Rx interrupt  |

| [15]         | Ethernet controller MAC Tx interrupt  |

| [14]         | Ethernet controller BDMA Rx interrupt |

| [13]         | Ethernet controller BDMA Tx interrupt |

| [12]         | SAR Tx/Rx done interrupt              |

| [11]         | SAR Tx/Rx error interrupt             |

| [10]         | USB interrupt                         |

| [9]          | GDMA channel 1 interrupt              |

| [8]          | GDMA channel 0 interrupt              |

| [7]          | Timer 1 interrupt                     |

| [6]          | Timer 0 interrupt                     |

| [5]          | UART receive and error interrupt      |

| [4]          | UART transmit interrupt               |

| [3]          | External interrupt 3                  |

| [2]          | External interrupt 2                  |

| [1]          | External interrupt 1                  |

| [0]          | External interrupt 0                  |

Table 3 S5N8947 Interrupt Sources

## 7. SPECIAL FUNCTION REGISTERS

| Group    | Registers | Offset  | R/W | Description                               | Reset/Value |

|----------|-----------|---------|-----|-------------------------------------------|-------------|

| System   | SYSCFG    | 0x0000  | R/W | System configuration register             | 0x23FF0000  |

| Manager  | SYSCON    | 0x3000  | R/W | System control register                   | 0x0000000   |

|          | EXTACON0  | 0x3008  | R/W | External I/O timing register 1            | 0x00000000  |

|          | EXTACON1  | 0x300C  | R/W | External I/O timing register 2            | 0x00000000  |

|          | EXTDBWTH  | 0x3010  | R/W | Data bus width for each memory bank       | 0x00000000  |

|          | ROMCON0   | 0x3014  | R/W | ROM/SRAM/Flash bank 0 control register    | 0x20000060  |

|          | ROMCON1   | 0x3018  | R/W | ROM/SRAM/Flash bank 1 control register    | 0x0000060   |

|          | ROMCON2   | 0x301C  | R/W | ROM/SRAM/Flash bank 2 control register    | 0x0000060   |

|          | ROMCON3   | 0x3020  | R/W | ROM/SRAM/Flash bank 3 control register    | 0x0000060   |

|          | DRAMCON0  | 0x3024  | R/W | DRAM bank 0 control register              | 0x00000000  |

|          | DRAMCON1  | 0x3028  | R/W | DRAM bank 1 control register              | 0x00000000  |

|          | DRAMCON2  | 0x302C  | R/W | DRAM bank 2 control register              | 0x00000000  |

|          | DRAMCON3  | 0x3030  | R/W | DRAM bank 3 control register              | 0x00000000  |

|          | REFEXTCON | 0x3034  | R/W | Refresh and external I/O control register | 0x83FD0000  |

| Ethernet | BDMATXCON | 0x9000  | R/W | Buffered DMA receive control register     | 0x00000000  |

| (BDMA)   | BDMARXCON | 0x9004  | R/W | Buffered DMA transmit control register    | 0x00000000  |

|          | BDMATXPTR | 0x9008  | R/W | Transmit trame descriptor start address   | 0x00000000  |

|          | BDMARXPTR | 0x900C  | R/W | Receive frame descriptor start address    | 0x00000000  |

|          | BDMARXLSZ | 0x9010  | R/W | Receive frame maximum size                | Undefined   |

|          | BDMASTAT  | 0x9014  | R/W | Buffered DMA status                       | 0x00000000  |

|          | CAM       | 0x9100- | R/W | CAM content (32 words)                    | Undefined   |

|          |           | 0x917C  |     |                                           |             |

|          | BDMATXBUF | 0x9200- | R/W | BDMA Tx buffer (64 words) for test mode   | Undefined   |

|          |           | 0x92FC  |     | addressing                                |             |

|          | BDMARXBUF | 0x9800- | R/W | BDMA Rx buffer (64 words) for test mode   | Undefined   |

|          |           | 0x99FC  |     | addressing                                |             |

| Ethernet | MACON     | 0xA000  | R/W | Ethernet MAC control register             | 0x00000000  |

| (MAC)    | CAMCON    | 0xA004  | R/W | CAM control register                      | 0x00000000  |

|          | MACTXCON  | 0xA008  | R/W | MAC transmit control register             | 0x00000000  |

|          | MACTXSTAT | 0xA00C  | R/W | MAC transmit status register              | 0x0000000   |

|          | MACRXCON  | 0xA010  | R/W | MAC receive control register              | 0x00000000  |

|          | MACRXSTAT | 0xA014  | R/W | MAC receive status register               | 0x00000000  |

|          | STADATA   | 0xA018  | R/W | Station management data                   | 0x00000000  |

|          | STACON    | 0xA01C  | R/W | Station management control and address    | 0x00006000  |

|          | CAMEN     | 0xA028  | R/W | CAM enable register                       | 0x00000000  |

|          | EMISSCNT  | 0xA03C  | R/W | Missed error count register               | 0x00000000  |

|          | EPZCNT    | 0xA040  | R   | Pause count register                      | 0x00000000  |

|          | ERMPZCNT  | 0xA044  | R   | Remote pause count register               | 0x0000000   |

|          | ETXSTAT   | 0x9040  | R   | Transmit control frame status             | 0x0000000   |

| USB      | FA        | 0x7000  | R/W | Function address register                 | 0x0000000   |

|          | РМ        | 0x7004  | R/W | Power management register                 | 0x0000000   |

|          | EI        | 0x7008  | R/W | Endpoint interrupt register               | 0x0000000   |

|          | UI        | 0x700C  | R/W | USB interrupt register                    | 0x0000000   |

|          | EIE       | 0x7010  | R/W | Endpoint interrupt enable register        | 0x000001F   |

|          | UIE       | 0x7014  | R/W | USB interrupt enable register             | 0x00000004  |

|          |           |         |     |                                           |             |

|    | HBFN        | 0x70                       | 01C  | R   | Frome number? register                            | 0x00000000                |

|----|-------------|----------------------------|------|-----|---------------------------------------------------|---------------------------|

|    | IEOM        | 0x70                       |      | R/W | Frame number2 register<br>Input EP0 MAXP register | 0x00000000<br>0x00000000  |

|    | *EOC        | 0x70                       |      | R/W | EP0 Control register                              | 0x00000000<br>0x00000000  |

|    | *E0BC       | 0x70                       |      | R/W |                                                   | 0x00000000<br>0x00000000  |

|    | *E0BC       | 0x70                       |      | R/W | EP0 Write Byte Counter<br>EP1 OUT MAXP register   | 0x00000000<br>0x000000001 |

|    |             |                            |      |     | Č                                                 | 0x00000001<br>0x00000000  |

|    | *0101       | 0x70                       |      | R/W | EP1 OUT Control register 1                        |                           |

|    | *01C2       | 0x70                       |      | R/W | EP1 OUT Control register 2                        | 0x00000000                |

|    | *E1BC       | 0x70                       |      | R/W | EP1 Write Byte Counter                            | 0x0000000                 |

|    | *I2M        | 0x70                       |      | R/W | EP2 IN MAXP register                              | 0x00000001                |

|    | *I2C1       | 0x70                       |      | R/W | EP2 IN Control register 1                         | 0x0000000                 |

|    | *I2C2       | 0x70                       |      | R/W | EP2 IN Control register 2                         | 0x00000000                |

|    | *03M        | 0x70                       | )50  | R/W | EP3 OUT MAXP register                             | 0x00000004                |

|    | *03C1       | 0x70                       | )54  | R/W | EP3 OUT Control register 1                        | 0x00000000                |

|    | *O3C2       | 0x70                       | )58  | R/W | EP3 OUT Control register 2                        | 0x00000000                |

|    | *E3BC       | 0x70                       | )5C  | R/W | EP3 Write Byte Counter                            | 0x00000000                |

|    | *I4M        | 0x70                       | )60  | R/W | EP4 IN MAXP register                              | 0x0000004                 |

|    | *I4C1       | 0x70                       | )64  | R/W | EP4 IN Control register 1                         | 0x0000000                 |

|    | *I4C2       | 0x70                       | )6C  | R/W | EP4 IN Control register 2                         | 0x0000000                 |

|    | *PDC        | 0x7070<br>0x7100<br>0x7104 |      | R/W | Power-down Counter Register                       | 0x00000000                |

|    | *EP0D       |                            |      | R/W | EP0 FIFO data register                            | 0x00000000                |

|    | *EP1D       |                            |      | R/W | EP1 FIFO data register                            | 0x0000000                 |

|    | *EP2D       | 0x71                       | 108  | R/W | EP2 FIFO data register                            | 0x00000000                |

|    | *EP3D       | 0x71                       | l0C  | R/W | EP3 FIFO data register                            | 0x00000000                |

|    | *EP4D       | 0x71                       | 10   | R/W | EP4 FIFO data register                            | 0x00000000                |

| AR | SW_RESET    |                            | 0x00 | R/W | Software reset register                           | 0x00000000                |

|    | GLOBAL_MODE |                            | 0x08 | R/W | Global mode register                              | 0x00000000                |

|    |             |                            | 0x0C | R/W | Base multiple for receive packet timeout register | 0x00FF7FFF                |

|    | TX_READY1   |                            | 0x10 | R/W | Transmit ready first packet or subpacket address  | 0x00000000                |

|    | TX_READY2   |                            | 0x14 | R/W | Transmit ready last packet or subpacket address   | 0x00000000                |

|    | TX_DONE_AD  | DDR                        | 0x18 | R/W | Transmit packet done queue base address register  | 0x00000000                |

|    | TX_DONE_SIZ | ZE                         | 0x1C | R/W | Transmit packet done queue size register          | 0x00C00000                |

|    | RX_POOL0_A  | DDR                        | 0x20 | R/W | Receive queue 0 base address register             | 0x00000000                |

|    | RX_POOL0_SI | ZE                         | 0x24 | R/W | Receive queue 0 size register                     | 0x00C00000                |

|    | RX_POOL1_A  | DDR                        | 0x28 | R/W | Receive queue 1 base address register             | 0x00000000                |

|    | RX_POOL1_SI |                            | 0x2C | R/W | Receive queue 1 size register                     | 0x00C00000                |

|    | RX_POOL2_A  |                            | 0x30 | R/W | Receive queue 2 base address register             | 0x0000000                 |

|    | RX_POOL2_SI |                            | 0x34 | R/W | Receive queue 2 size register                     | 0x00C00000                |

|    | RX_POOL3_A  |                            | 0x38 | R/W | Receive queue 3 base address register             | 0x0000000                 |

|    | RX_POOL3_SI |                            | 0x3C | R/W | Receive queue 3 size register                     | 0x00C00000                |

|    | RX_DONE0_A  |                            | 0x40 | R/W | Receive packet done queue 0 base address register | 0x0000000                 |

|    | RX_DONE0_S  |                            | 0x44 | R/W | Receive packet done queue 0 size register         | 0x00C00000                |

|    | RX_DONE1_A  |                            | 0x48 | R/W | Receive packet done queue 1 base address register | 0x0000000                 |

|    | RX_DONE1_S  |                            | 0x4C | R/W | Receive packet done queue 1 size register         | 0x00C00000                |

|    | UTOPIA_CON  |                            | 0x50 | R/W | UTOPIA interface configuration register           | 0x00000000                |

|    | UTOPIA_TIME |                            | 0x54 | R/W | UTOPIA interface timeout register                 | 0xFFFFFFFF                |

|    | CLOCK_RATI  |                            | 0x64 | R/W | Ratio of SAR clock freq toUNI interface speed     | 0x000008E                 |

|    | DONE_INT_M  |                            | 0x70 | R/W | Interrupt mask for done interrupt register        | 0xFFFFFFFF                |

|    | ERR_INT_MA  |                            | 0x74 | R/W | Interrupt mask for error interrupt register       | 0xFFFFFFFF                |

|    | DONE_INT_ST |                            | 0x78 | R/W | Interrupt status for done interrupt register      | 0x0000000                 |

|    | ERR_INT_STA |                            | 0x7C | R/W | Interrupt status for error interrupt register     | 0x00000000                |

|    | 1/R_LOOKUP_ |                            | 0x80 | R/W | Base address of 1/Rate lookup table               | 0x00000000                |

|    | VP_LOOKUP_  |                            | 0x84 | R/W | Base address of VP lookup table                   | 0x00000200                |

|    | UBR_SCH_TB  |                            | 0x88 | R/W | Base address and entry number of UBR schedule     | 0x00000300                |

|    | CBR_SCH_TB  |                            | 0x8C | R/W | Base address and entry number of CBR schedule     | 0x00000380                |

|                      | CELL_BUFF                    |               | 0x90     | R/W                                                   | Base address and entry number of cell buffer                               | 0x00000400               |

|----------------------|------------------------------|---------------|----------|-------------------------------------------------------|----------------------------------------------------------------------------|--------------------------|

|                      | SCH_CONN_TH                  | 3L            | 0x94     | R/W                                                   | Base address and entry number of scheduler                                 | 0x00000500               |

|                      |                              |               |          |                                                       | connection table                                                           |                          |

|                      |                              |               | R/W      | Base address and entry number of AAL connection table | 0x00000600                                                                 |                          |

|                      | SAR_CONN_TH                  | 3L            | 0x9C     | R/W                                                   | Base address and entry number of SAR                                       | 0x00000700               |

|                      | CAM VPVC/CM                  | N O           | x100-1F0 | C R/W                                                 | connection table<br>CAM VPCI, VCI and connection number register           | 0x0000000                |

|                      | CONFIGURATI                  |               | 0x200    | R/W                                                   | Clock control and connection memory                                        | 0x000000044              |

|                      | EXT_CMBASE                   |               | 0x204    | R/W                                                   | configuration register<br>External connection memory base address register | 0x00000000               |

| I/O Ports            | IOPMOD                       | 0x50          | 000      | R/W                                                   | I/O port mode register                                                     | 0x00000000               |

|                      | IOPCON                       | 0x50          | 004      | R/W                                                   | I/O port control register                                                  | 0x0000000                |

|                      | IOPDATA                      | 0x50          | 008      | R/W                                                   | Input port data register                                                   | Undefined                |

| Interrupt            | INTMOD                       | 0x40          |          | R/W                                                   | Interrupt mode register                                                    | 0x0000000                |

| Controller           | INTPND                       | 0x40          |          | R/W                                                   | Interrupt pending register                                                 | 0x0000000                |

|                      | INTMSK                       | 0x40          |          | R/W                                                   | Interrupt mask register                                                    | 0x003FFFFF               |

|                      | INTPRIO                      | 0x40          |          | R/W                                                   | Interrupt priority register 0                                              | 0x03020100               |

|                      | INTPRI0 0x40<br>INTPRI1 0x40 |               |          | R/W                                                   | Interrupt priority register 1                                              | 0x07060504               |

|                      | INTPRI2                      |               |          | R/W                                                   | Interrupt priority register 2                                              | 0x07000504               |

|                      | INTPRI3                      | 0x4014        |          | R/W                                                   | Interrupt priority register 3                                              | 0x0F0E0D0C               |

|                      |                              | 0x4018        |          |                                                       |                                                                            |                          |

|                      | INTPRI4<br>INTPRI5           | 0x401C        |          | R/W<br>R/W                                            | Interrupt priority register 4                                              | 0x00001110<br>0x00000000 |

|                      |                              | 0x4020        |          |                                                       | Interrupt priority register 5                                              |                          |

|                      | INTOFFSET                    | 0x4024        |          | R                                                     | Interrupt offset address register                                          | 0x00000054               |

|                      |                              | NTPNDPRI 0x40 |          | R                                                     | Interrupt pending priority register                                        | 0x0000000                |

|                      | INTPNDTST 0x40               |               |          | W                                                     | Interrupt pending test register                                            | 0x00000000               |

|                      | INTOSET_FIQ 0x40             |               |          | R                                                     | FIQ interrupt offset register                                              | 0x00000054               |

|                      | INTOSET_IRQ                  | -             |          | R                                                     | IRQ interrupt offset register                                              | 0x0000054                |

| I <sup>2</sup> C Bus | IICCON                       | 0XF           |          | R/W                                                   | I <sup>2</sup> C bus control status register                               | 0x0000000                |