# STC4130 Synchronous Clock for SETS Data Sheet

# Description

The STC4130 is a ROHS compatible, integrated, single chip solution for the synchronous clock in SDH and SONET network elements. The device is fully compliant with ITU-T G.812 Type III, G.813, and Telcordia GR1244, and GR253.

The STC4130 accepts 12 reference inputs and generates 8 independent synchronized output clocks. Reference input frequencies are automatically detected, and inputs are individually monitored for quality. Active reference selection may be manual or automatic. All reference switches are hitless. Synchronized outputs may be programmed for a wide variety of SONET and SDH frequencies.

Two independent clock generators provide the standardized T0 and T4 functions. Each clock generator includes a DPLL (Digital Phase-Locked Loop), which may operate in the Freerun, Synchronized, and Holdover modes. Both clock generators support master/ slave operation for redundant applications. Connor-Winfield's proprietary **SyncLink**<sup>TM</sup> Cross-couple data link provides master/slave phase information and state data to ensure seamless side switches.

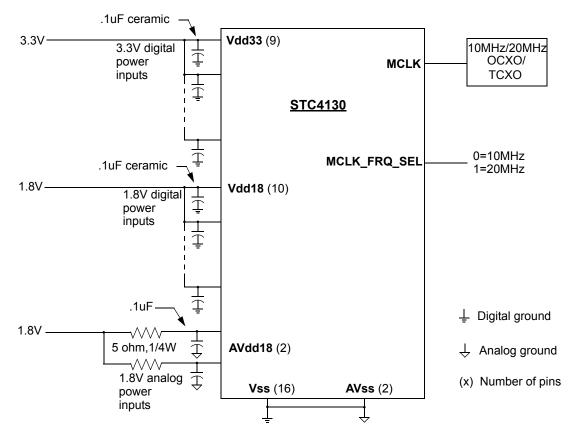

A standard SPI serial bus interface or parallel bus provide access to the STC4130's comprehensive, yet simple to use internal control and status registers. The device operates with an external OCXO or TCXO as its MCLK at either 10 or 20 MHz.

### Features

- For SDH SETS and SSU

- For SONET Stratum 3E, 3, 4E, 4 and SMC

- Complies with ITU-T G.812 Type III , G.813, Telcordia GR1244, and GR253

- Supports Master/Slave operation with the SyncLink<sup>TM</sup> cross-couple data link for master/ slave redundant applications

- Accepts 12 individual clock reference inputs

- Reference clock inputs are automatically frequency detected

- Supports manual or automatic reference selection

- T0 and T4 have independent reference lists and priority tables for automatic reference selection

- 8 synchronized output clocks

- Output/input phase skew is adjustable in slave mode, in 0.1nS steps up to 200nS

- · Hit-less reference and master/slave switching

- · Phase rebuild on re-lock and reference switches

- Better than 0.1 ppb holdover accuracy

- Programmable bandwidth, from 90mHz to 107Hz, for both T0 and T4 DPLL

- Supports SPI or parallel bus interface

- IEEE 1149.1 JTAG boundary scan

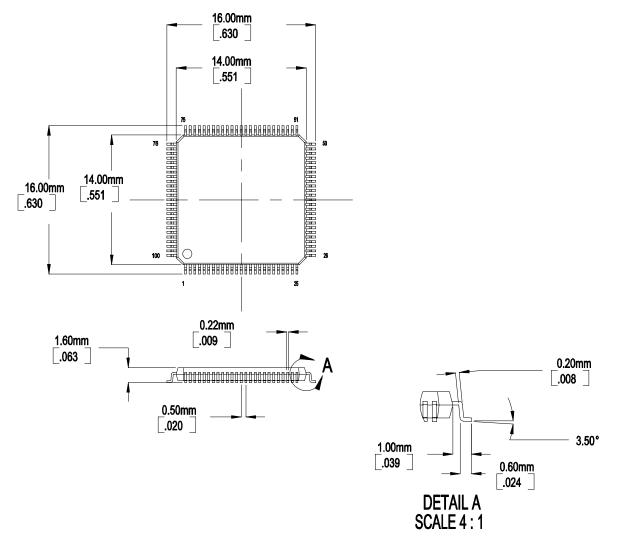

- Available in TQ100 ROHS package

#### Table of Contents

Description 1 Features 1 STC4130 Pin Diagram (Top View) 3 STC4130 Pin Description 4 Absolute Maximum Ratings 6 **Operating Conditions and Electrical Characteristics 6** Register Map 7 **General Description 9 Detailed Description 10** Chip Master Clock Input 10 Reference Input Monitoring and Qualification 10 **DPLL Active Reference Selection 11** Manual Reference Selection Mode 11 Automatic Reference Selection Mode 11 Digital Phase Locked Loop General Description 11 Free Run 12 Synchronized 12 Holdover 12 DPLL Operating Mode Details 12 Free Run Mode 12 Holdover Mode 13 **Output Clocks 14** Master/Slave Operation 15 Processor Interface Descriptions 17 SPI Bus Mode 17 Serial Bus Timing 18 Motorola Bus 19 Intel Bus 21 Multiplex Bus Mode 24 Register Descriptions and Operation 26 General Register Operation 26 Multibyte register reads 26 Multibyte register writes 26 Clearing bits in the Interrupt Status Register 26 Default Register Settings 26 Application Notes 40 Mechanical Dimensions 42 Ordering Information 42

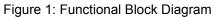

STC4130 Pin Diagram (Top View)

COMPLIANT

Note: Pins labeled "Test Pin" must be grounded.

# STC4130 Synchronous Clock for SETS Data Sheet

# **STC4130 Pin Description**

### Table 1: Pin Description

| Pin Name     | Pin #                                                              | I/O <sup>1</sup> | Description                                                         |

|--------------|--------------------------------------------------------------------|------------------|---------------------------------------------------------------------|

| Vdd33        | 6,22,31,<br>44,59,<br>69,80,<br>89,97                              | I                | 3.3V power input                                                    |

| Vdd18        | 9,18,27,<br>38,47,53,<br>65,73,84,<br>92                           | I                | 1.8V power input                                                    |

| Vss          | 3,13,15,<br>20,29,35,<br>41,49,56,<br>62,67,71,<br>78,82,87,<br>95 |                  | Digital ground                                                      |

| AVdd18       | 1, 76                                                              |                  | 1.8V analog power input                                             |

| Avss         | 75, 100                                                            |                  | Analog ground                                                       |

| TRST         | 94                                                                 | I                | JTAG reset                                                          |

| тск          | 93                                                                 | I                | JTAG clock                                                          |

| TMS          | 91                                                                 | Ι                | JTAG mode selection                                                 |

| TDI          | 90                                                                 | I                | JTAG data input                                                     |

| TDO          | 88                                                                 | 0                | JTAG data output                                                    |

| RESET        | 30                                                                 | I                | Active low to reset the chip                                        |

| MCLK         | 99                                                                 | I                | Master clock input, 10 MHZ or 20 MHz                                |

| MCLK_FRQ_SEL | 98                                                                 | Ι                | Master clock frequency select, 0 = 10 MHz or 1 = 20 MHz             |

| BUS_MODE0    | 63                                                                 | I                | Bus mode selection, 00: SPI, 01: Motorola, 10: Intel, 11: Multiplex |

| BUS_MODE1    | 64                                                                 | I                | Bus mode selection, 00: SPI, 01: Motorola, 10: Intel, 11: Multiplex |

| BUS_CS       | 45                                                                 | I                | Parallel bus or SPI Chip select                                     |

| BUS_ALE      | 46                                                                 | Ι                | Parallel bus address latch or SPI clock input                       |

| BUS_WRB      | 48                                                                 | I                | Parallel bus write or SPI data input                                |

| BUS_RDB      | 50                                                                 | Ι                | Parallel bus read or read/write input                               |

| BUS_RDY      | 51                                                                 | 0                | Parallel bus ready output or SPI data output                        |

| BUS_A6       | 61                                                                 | Ι                | Bus Address bit 6                                                   |

| BUS_A5       | 60                                                                 | I                | Bus Address bit 5                                                   |

| BUS_A4       | 58                                                                 | I                | Bus Address bit 4                                                   |

| BUS_A3       | 57                                                                 | I                | Bus Address bit 3                                                   |

| BUS_A2       | 55                                                                 | I                | Bus Address bit 2                                                   |

| BUS_A1       | 54                                                                 | I                | Bus Address bit 1                                                   |

| BUS_A0       | 52                                                                 | I                | Bus Address bit 0                                                   |

| BUS_AD7      | 43                                                                 | I/O              | Parallel bus address/data bit7                                      |

# STC4130 Synchronous Clock for SETS Data Sheet

### Table 1: Pin Description

| Pin Name     | Pin #   | I/O <sup>1</sup> | Description                                                                                         |

|--------------|---------|------------------|-----------------------------------------------------------------------------------------------------|

| BUS_AD6      | 42      | I/O              | Parallel bus address/data bit6                                                                      |

| BUS_AD5      | 40      | I/O              | Parallel bus address/data bit5                                                                      |

| BUS_AD4      | 39      | I/O              | Parallel bus address/data bit4                                                                      |

| BUS_AD3      | 37      | I/O              | Parallel bus address/data bit3                                                                      |

| BUS_AD2      | 36      | I/O              | Parallel bus address/data bit2                                                                      |

| BUS_AD1      | 34      | I/O              | Parallel bus address/data bit1                                                                      |

| BUS_AD0      | 33      | I/O              | Parallel bus address/data bit0                                                                      |

| BUS_INTR     | 32      | 0                | Interrupt                                                                                           |

| REF1         | 2       | I                | Reference input 1                                                                                   |

| REF2         | 4       | I                | Reference input 2                                                                                   |

| REF3         | 5       | I                | Reference input 3                                                                                   |

| REF4         | 8       | I                | Reference input 4                                                                                   |

| REF5         | 10      | I                | Reference input 5                                                                                   |

| REF6         | 12      | I                | Reference input 6                                                                                   |

| REF7         | 14      | I                | Reference input 7                                                                                   |

| REF8         | 16      | I                | Reference input 8                                                                                   |

| REF9         | 17      | I                | Reference input 9                                                                                   |

| REF10        | 19      | I                | Reference input 10                                                                                  |

| REF11        | 21      | I                | Reference input 11                                                                                  |

| REF12        | 23      | I                | Reference input 12                                                                                  |

| T0_M/S       | 24      | I                | Select master or slave mode for T0, 1: Master, 0: Slave                                             |

| T4_M/S       | 28      | Ι                | Select master or slave mode for T4, 1: Master, 0: Slave                                             |

| T0_XSYNC_IN  | 25      | I                | Cross-couple SyncLink <sup>TM</sup> data link input fot T0 for master/slave redundant applications  |

| T0_XSYNC_OUT | 70      | 0                | Cross-couple SyncLink <sup>TM</sup> data link output fot T0 for master/slave redundant applications |

| T4_XSYNC_IN  | 26      | Ι                | Cross-couple SyncLink <sup>TM</sup> data link input fot T4 for master/slave redundant applications  |

| T4_XSYNC_OUT | 66      | 0                | Cross-couple SyncLink <sup>TM</sup> data link output fot T4 for master/slave redundant applications |

| CLK0_P       | 85      | 0                | 155.52 MHz LVDS output                                                                              |

| CLK0_N       | 86      | 0                | 155.52 MHz LVDS output                                                                              |

| CLK1         | 83      | 0                | 19.44/38.88/77.76 MHz                                                                               |

| CLK2         | 81      | 0                | 19.44/38.88/77.76 MHz                                                                               |

| CLK3         | 79      | 0                | 8 KHz frame pulse or 50% duty cycle clock                                                           |

| CLK4         | 77      | 0                | 2 KHz frame pulse or 50% duty cycle clock                                                           |

| CLK5         | 74      | 0                | 44.736/34.368 MHz                                                                                   |

| CLK6         | 72      | 0                | 1.544/3.088/6.176/12.352/24.704/2.048/4.098/8.192/16.384/32.768 MHZ                                 |

| CLK7         | 68      | 0                | 1.544/2.048 MHz                                                                                     |

| Test_Pin     | 7,11,96 | I                | Test pin, must be grounded for normal operation                                                     |

## **Absolute Maximum Ratings**

| Symbol | Parameter                        | Min. | Max | Units | Notes |

|--------|----------------------------------|------|-----|-------|-------|

| Vdd33  | Logic power supply voltage, 3.3V | -0.5 | 4.5 | volts | 1     |

| Vdd18  | Logic power supply voltage, 1.8V | -0.5 | 2.5 | volts | 1     |

| VIN    | Logic input voltage, rel. to GND | -0.5 | 5.5 | volts | 1     |

| TSTG   | Storage Temperature              | -65  | 150 | С     | 1     |

### Table 2: Absolute Maximum Ratings

Note 1: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. Devices should not be operated outside the Recommended Operating Conditions.

# **Operating Conditions and Electrical Characteristics**

| Symbol     | Parameter                                   | Min.      | Nominal | Max. | Units | Notes |

|------------|---------------------------------------------|-----------|---------|------|-------|-------|

| Vdd33      | 3.3V digital power supply voltage           | 3.0       | 3.3     | 3.6  | Volts |       |

| Vdd18      | 1.8V digital power supply voltage           | 1.65      | 1.8     | 1.95 | Volts |       |

| VIH (3.3V) | High level input voltage                    | 2.0       |         | 5.5  | Volts | 2     |

| VIL (3.3V) | Low level input voltage                     | -0.3      |         | 0.8  | Volts | 2     |

| Voh (3.3V) | High level output voltage (IOH = -12mA)     | Vcc - 0.4 |         | Vcc  | Volts | 2     |

| VOL (3.3V) | Low level output voltage (IOL =12mA)        | 0         |         | 0.4  | Volts | 2     |

| CIN        | Input capacitance                           |           | 8       |      | pF    |       |

| TRIP       | Input reference signal positive pulse width | 10        |         |      | nS    |       |

| TRIN       | Input reference signal negative pulse width | 10        |         |      | nS    |       |

| ТА         | Operating Ambient Temperature Range         | 0         |         | 70   | °C    | 3     |

| Icc (Vcc)  | 3.3V digital supply current                 |           |         | 80   | mA    |       |

| Icc (Vcc)  | 1.8V supply current                         |           |         | 240  | mA    |       |

| Pd         | Device power dissipation                    |           |         |      | W     |       |

### **Table 3: Recommended Operating Conditions and Electrical Characteristics**

Note 2: LVCMOS 3.3 compatible

Note 3: For Industrial Temperature Range (-40° to 85), Use part number STC4130-I

# STC4130 Synchronous Clock for SETS Data Sheet

# **Register Map**

### Table 4: Register Map

| Addr | Reg Name                   | Bits | Туре | Description                                                                                                                                                                                                           |

|------|----------------------------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00 | Chip_ID                    | 15-0 | R    | Chip ID, 0x4130                                                                                                                                                                                                       |

| 0x02 | Chip_Rev                   | 7-0  | R    | Chip revision number 0x01                                                                                                                                                                                             |

| 0x03 | Chip_Sub_Rev               | 7-0  | R    | Chip sub-revision 0x01                                                                                                                                                                                                |

| 0x04 | T0_T4_MS_Sts               | 1-0  | R    | Indicates master/slave state                                                                                                                                                                                          |

| 0x05 | T0_Slave_Phase_Adj         | 11-0 | R/W  | Adjust T0 slave phase from 0 ~ 409.5 nS in 0.1 nS steps                                                                                                                                                               |

| 0x07 | T4_Slave_Phase_Adj         | 11-0 | R/W  | Adjust T4 slave phase from 0 ~ 409.5 nS in 0.1 nS steps                                                                                                                                                               |

| 0x09 | Fill_Rate                  | 3-0  | R/W  | Leaky bucket fill rate, 1 ~ 16 mS                                                                                                                                                                                     |

| 0x0a | Leak_Rate                  | 3-0  | R/W  | Leaky bucket leak rate, 1/n <sup>th</sup> of fill rate, n = 1 ~ 16                                                                                                                                                    |

| 0x0b | Bucket_Size                | 5-0  | R/W  | Leaky bucket size, 0 ~ 63                                                                                                                                                                                             |

| 0x0c | Assert_Threshold           | 5-0  | R/W  | Leaky bucket alarm assert threshold, 0 ~ 63                                                                                                                                                                           |

| 0x0d | De_Assert_Threshold        | 5-0  | R/W  | Leaky bucket alarm de-assert threshold, 0 ~ 63                                                                                                                                                                        |

| 0x0e | Freerun_Cal                | 10-0 | R/W  | Freerun calibration of the TCXO, - 102.4 ~ + 102.3 ppm                                                                                                                                                                |

| 0x10 | Disqualification_Range     | 9-0  | R/W  | Reference disqualification range, 0 ~ 102.3 ppm                                                                                                                                                                       |

| 0x12 | Qualification_Range        | 9-0  | R/W  | Reference qualification range, 0 ~ 102.3 ppm                                                                                                                                                                          |

| 0x14 | Qualification_Timer        | 5-0  | R/W  | Reference qualification timer, 0 ~ 63 S                                                                                                                                                                               |

| 0x15 | Ref_Selector               | 3-0  | R/W  | Determines which reference data is shown in register 0x16                                                                                                                                                             |

| 0x16 | Ref_Frq_Offset             | 14-0 | R    | Reference frequency and frequency offset are shown in bits 14-12 and 11-0                                                                                                                                             |

| 0x18 | Refs_Activity              | 13-0 | R    | Reference and cross reference activity                                                                                                                                                                                |

| 0x1a | Refs_Qual                  | 11-0 | R    | Reference 1 ~ 12 qualification                                                                                                                                                                                        |

| 0x1c | T0_Control_Mode            | 5-0  | R/W  | OOP -Follow/Don't Follow, Manual/Auto, Revertive, HO_Usage, PhaseAlignMode                                                                                                                                            |

| 0x1d | T0_Bandwidth               | 4-0  | R/W  | Bandwidth selection                                                                                                                                                                                                   |

| 0x1e | T0_Auto_Active_Ref         | 3-0  | R    | Indicates automatically selected reference                                                                                                                                                                            |

| 0x1f | T0_Manual_Active_Ref       | 3-0  | R/W  | Selects the active reference in manual mode                                                                                                                                                                           |

| 0x20 | Reserved                   | 31-0 | R    | Reserved                                                                                                                                                                                                              |

| 0x24 | T0_Long_Term_Accu_History  | 31-0 | R    | Long term Accumulated History for T0 relative to the TCXO                                                                                                                                                             |

| 0x28 | T0_Short_Term_Accu_History | 31-0 | R    | Short term Accumulated History for T0 relative to the TCXO                                                                                                                                                            |

| 0x2c | T0_User_Accu_History       | 31-0 | R/W  | User Holdover data for T0 relative to the TCXO                                                                                                                                                                        |

| 0x30 | T0_HO_BW_Ramp              | 7-0  | R/W  | Bits7-4, Long term history accumuation bandwidth: 9.7, 4.9, 2.4, 1.2, 0.61, 0.03 mHz<br>Bits3-2, Short term history accumulation bandwidth: 2.5, 1.24, 0.62, 0.31 mHz<br>Bit21:0, Ramp control: none, 1, 1.5, 2 ppm/S |

| 0x31 | T0_Priority_Table          | 47-0 | R/W  | REF1-12 selection priority for automatic mode, 4 bits/reference                                                                                                                                                       |

| 0x37 | T0_PLL_Status              | 7-0  | R    | LTH Avail, LTH Complete, OOP, LOL, LOS, Sync                                                                                                                                                                          |

| 0x38 | T0_Accu_Flush              | 0-0  | W    | 0: Flush current history, 1: Flush all histories                                                                                                                                                                      |

| 0x39 | T4_Control_Mode            | 5-0  | R/W  | OOP -Follow/Don't Follow, Manual/Auto, Revertive, HO_Usage, PhaseAlignMode                                                                                                                                            |

| 0x3a | T4_Bandwidth               | 4-0  | R/W  | Bandwidth selection                                                                                                                                                                                                   |

| 0x3b | T4_Auto_Active_Ref         | 3-0  | R    | Indicates automatically selected reference                                                                                                                                                                            |

| 0x3c | T4_Manual_Active_Ref       | 3-0  | R/W  | Selects the active reference in manual mode                                                                                                                                                                           |

| 0x3d | Reserved                   | 31-0 | R    | Reserved                                                                                                                                                                                                              |

| 0x41 | T4_Long_Term_Accu_History  | 31-0 | R    | Long term Accumulated History for T4 relative to the TCXO                                                                                                                                                             |

### Table 4: Register Map

| Addr | Reg Name                   | Bits | Туре | Description                                                                                                                                                                                                           |

|------|----------------------------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x45 | T4_Short_Term_Accu_History | 31-0 | R    | Short term Accumulated History for T4 relative to the TCXO                                                                                                                                                            |

| 0x49 | T4_User_Accu_History       | 31-0 | R/W  | User Holdover data for T4 relative to the TCXO                                                                                                                                                                        |

| 0x4d | T4_HO_BW_Ramp              | 7-0  | R/W  | Bits7-4, Long term history accumuation bandwidth: 9.7, 4.9, 2.4, 1.2, 0.61, 0.03 mHz<br>Bits3-2, Short term history accumulation bandwidth: 2.5, 1.24, 0.62, 0.31 mHz<br>Bit21:0, Ramp control: none, 1, 1.5, 2 ppm/S |

| 0x4e | T4_Priority_Table          | 47-0 | R/W  | REF1-12 selection priority for automatic mode, 4 bits/reference                                                                                                                                                       |

| 0x54 | T4_PLL_Status              | 7-0  | R    | LTH Avail, LTH Complete, OOP, LOL, LOS, Sync                                                                                                                                                                          |

| 0x55 | T4_Accu_Flush              | 0-0  | W    | 0: Flush current history, 1: Flush all histories                                                                                                                                                                      |

| 0x56 | CLK0_Sel                   | 0-0  | R/W  | 155.52 MHz clock enable/disable for CLK0                                                                                                                                                                              |

| 0x57 | CLK1_Sel                   | 1-0  | R/W  | 19.44MHz/38.88MHz/77.76MHz or disable select for CLK1                                                                                                                                                                 |

| 0x58 | CLK2_Sel                   | 1-0  | R/W  | 19.44MHz/38.88MHz/77.76MHz or disable select for CLK2                                                                                                                                                                 |

| 0x59 | CLK3_Sel                   | 5-0  | R/W  | 8KHz output 50% duty cycle or pulse width selection for CLK3                                                                                                                                                          |

| 0x5a | CLK4_Sel                   | 5-0  | R/W  | 2KHz output 50% duty cycle or pulse width selection for CLK4                                                                                                                                                          |

| 0x5b | CLK5_Sel                   | 1-0  | R/W  | DS3/E3 select for CLK5                                                                                                                                                                                                |

| 0x5c | CLK6_Sel                   | 3-0  | R/W  | DS1 x n / E1 x n selector for CLK6                                                                                                                                                                                    |

| 0x5d | CLK7_Sel                   | 1-0  | R/W  | Ds1/E1 selector for CLK7                                                                                                                                                                                              |

| 0x5e | Intr_Event                 | 9-0  | R/W  | Interrupt event                                                                                                                                                                                                       |

| 0x60 | Intr_Enable                | 9-0  | R/W  | Interrupt enable                                                                                                                                                                                                      |

# **General Description**

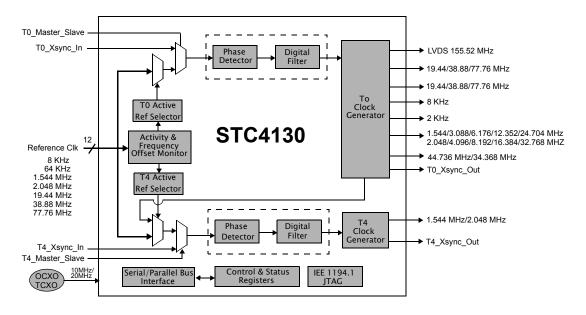

The STC4130 is an integrated single chip solution for the synchronous clock in SDH and SONET network elements. It's highly integrated design implements all of the necessary reference selection, monitoring, digital filtering, synthesis, and control functions. An external OCXO or TCXO at either 10 or 20 MHz completes a system level solution (see Functional Block Diagram, Figure 1).

The STC4130 includes two independent DPLLs (Digital Phase-Locked Loop) implementing the timing functions of T0 and T4. Each may select one of 12 reference inputs as its active reference. T0 provides 7 of the chip's 8 clock outputs while T4 provides one clock output. Both T0 and T4 provide a cross reference output for master/slave applications.

Reference frequencies are autodected and may each be 8KHz, 64KHz, 1.544MHz, 2.048MHz, 19.44MHz, 38.88MHz, or 77.76MHz. Each reference input is continuously monitored for activity and frequency offset. Activity monitoring is implemented with a leaky bucket accumulator with programmable fill and leak rates. Frequency offset is determined relative to the digitally calibrated external OCXO/TCXO. A reference is designated as "qualified" if it is active and its frequency is within the programmed frequency offset range for a pre-programmed time.

Active references may be selected manually or automatically, individually selectable for T0 and T4. In manual mode, the active reference is selected under application control, independant of it's qualification status.

In automatic mode, the active reference is selected according to revertivity status, and each reference's priority and qualification. Reference priorities are individually programmable. To and T4 each have their own priority tables. While a current active reference is qualified, revertivity determines whether a higher priority qualified reference should be selected as the new active reference. If revertivity is enabled, the highest priority qualified reference will always be selected as the active reference. If revertivity is not enabled, a new or returning qualified reference of higher priority will not be selected until the current active reference is disqualified.

The two independent clock generators, T0 and T4,

# STC4130 Synchronous Clock for SETS Data Sheet

each include a DPLL, which may operate in the Freerun, Synchronized, and Holdover modes. Both clock generators support master/slave operation for redundant applications. T0 generates Connor-Winfield's proprietary **SyncLink<sup>TM</sup>** Cross-couple data link, which provides master/slave phase information and state data to ensure seamless side switches. T4 provides an 8KHz cross-couple signal. The slave output clock phase is user adjustable.

The T0 and T4 clock generators may each be in freerun, synchronized, or holdover modes. In freerun, the clock outputs are simply determined by the accuracy of the digitally calibrated OCXO/TCXO. In synchronized mode, the chip phase locks to the selected input reference. Phase lock may be selected as arbitrary or zero phase offset between the reference and clock outputs. All reference switches are performed in a hitless manner, and frequency ramp controls ensure smooth output signal transitions. When references are switched, the device will minimize phase transitions in the output clocks. While synchronized, a frequency history is accumulated. In holdover mode, the chip outputs are synthesized according to this or a user supplied history.

The Digital Phase Locked Loop which provides the critical filtering and frequency/phase control functions is implemented with Connor-Winfield's NOVA Kernel - a set of well-proven algorithms and control that meet or exceed all requirements and lead the industry in critical jitter and accuracy performance parameters. Filter bandwidth may be user configured.

The device generates 8 independent synchronized output clocks. The first is at 155.52MHZ. The second and third clocks may be programmed at 19.44/38.88/77.76MHZ. The fourth and fifth are at 8kHz and 2kHz. The sixth is programmable at 1, 2, 4, 8, or 16 x T1 or E1. The seventh is programmable at either DS3 or E3. The eighth is programmable at either T1 or E1.

Control functions are provided either via a standard SPI serial bus interface or 8-bit parallel bus register interfaces. These provide access to the STC4130's comprehensive, yet simple to use internal control and status registers. Parallel bus operation is supported in the Motorola mode, Intel mode, or Multiplex bus mode.

## **Detailed Description**

### Chip Master Clock Input

The device operates with an external OCXO or TCXO as its master clock, connected to the **MCLK** input, pin 99. This may be at either 10 MHz or 20 MHz, **MCLK\_FRQ\_SEL** pin 98 = 0 for 10 MHZ, 1 for 20 MHZ.

The external TCXO or OCXO may be calibrated, (thus calibrating the freerun output frequency of the chip) by writing an offset to the **Freerun\_Cal** register, (0x0e/0f), from -102.4 to +102.3 ppm, in .1ppm steps, in two's complement form. (See **Register Descriptions** section for details regarding register references in this section.)

# Reference Input Monitoring and Qualification

The STC4130 accepts 12 external reference inputs at 8kHz, 64kHz, 1.544MHz, 2.048MHz, 19.44MHz, 38.88MHz, or 77.76MHz. Input frequencies are detected automatically. The autodetected frequency of any reference may be read by selecting the reference in the **Ref\_Selector** register (0x15) and then reading the frequency from bits 4 - 6 of register **Ref\_Frq\_Offset** (0x17).

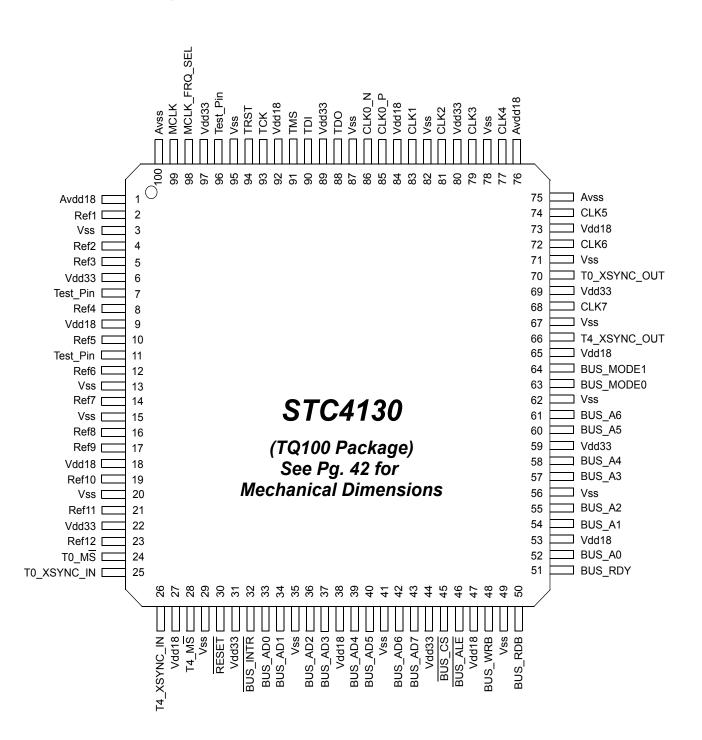

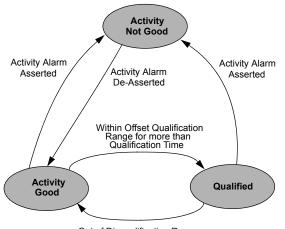

Each input is monitored and gualified for activity and frequency offset. Activity monitoring is accomplished with a leaky bucket accumulation algorithm, as shown in figure 2. The "leaky bucket" accumulator has a fill rate window that may be set from 1 to 16 ms, where any hit of signal abnormality (or multiple hits) during the window increments the bucket count by one. The leak rate is 1/n<sup>th</sup> of the fill rate, where n may be set from 1 to 16, corresponding to a leak rate window n x the fill rate window size. The leaky bucket accumulator decrements by one for each leak rate window that passes with no signal abnormality. Both windows operate in a consecutive, non-overlapping manner. The bucket accumulator has alarm assert and alarm de-assert thresholds that can each be programmed from 0 to 63.

The fill rate is written to the **Fill\_Rate** register, 0x09, and the leak rate is written to register **Leak\_Rate**, 0x0a. The bucket size is written to register **Bucket\_Size** (0x0b). The alarm assert threshold is written to register **Assert\_Threshold** (0x0c), and the

de-assert threshold is written to register **De\_Assert\_Threshold** (0x0d).

Bucket size must be greater than or equal to the alarm assert threshold value, and the alarm assert threshold value must be greater than the alarm deassert value.

Alarms appear in the **Refs\_Activity** register (0x18/ 19). A "1" indicates activity, and a "0" indicates an alarm, no activity. Note that if a reference is active and returns at a different autodetected frequency, it will be become inactive immediately.

Figure 2: Activity Monitor

Reference inputs are also monitored and qualified for frequency offset.

A PLL qualification range may be programmed up to +/-102.3 ppm by writina to register Qualification Range (0x12/13), and a disgualification range set up to +/-102.3 ppm, by writing to regis-Disqualification\_Range ter (0x10/11). The qualification range must be set less than the disqualification range. Additionally, a qualification timer may be programmed from 0 to 63 seconds by writing to register Qualification Timer (0x14). The PLL pull-in range is the same as the disqualification range.

The actual frequency offset (relative to the calibrated OCXO/TCXO) of any reference may be read by selecting the reference in the **Ref\_Selector** register (0x15) and then reading the offset value in bits 7 - 0/3 - 0 of register **Ref\_Frq\_Offset** (0x16/17).

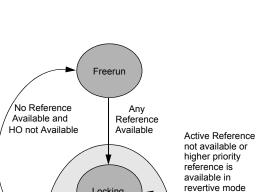

Figure 3 shows the reference qualification scheme. A reference is qualified if it has no activity alarm and is within the qualification range for more than the qualification time. An activity alarm or frequency offset

beyond the disqualification range will disqualify the reference. It may then be re-qualified and the activity alarm is de-asserted, if it is within the qualification range for more than the qualification time.

The reference qualification status of each reference may then be read from register **Refs\_Qual** (0x1a/ 1b).

Out of Disqualification Range

#### Figure 3: Reference Qualification and Disqualification

### **DPLL Active Reference Selection**

The T0 and T4 clock generators may be individually operated in either manual or automatic input reference selection mode. The mode is selected via the **T0(4)\_Control\_Mode** registers.

#### Manual Reference Selection Mode

In manual reference selection mode, the user may select the reference. Manual reference selection mode is selected by setting bit 4 of the **T0\_Control\_Mode** (0x1c) or **T4\_Control\_Mode** (0x39) register (for T0 or T4, respectively) to 0. The reference is selected by writing to bits 0 - 3 of the **T0\_Manual\_Active\_Ref** (0x1f) and **T4\_Manual\_Active\_Ref** (0x3c) registers.

#### Automatic Reference Selection Mode

In automatic reference selection mode, the device will select one pre-qualified reference as the active reference. Automatic reference selection mode is set

# Synchronous Clock for SETS Data Sheet

by writing bit 4 of the **T0\_Control\_Mode** (0x1c) or **T4\_Control\_Mode** (0x39) register (for T0 or T4, respectively) to 1.

The reference is picked according to its indicated priority in the reference priority table, Registers **T0\_Priority\_Table** (0x31~0x36) or **T4\_Priority\_Table** (0x4e ~ 0x0x53). Each reference has one entry in the table, which may be set to a value from 0 to 15. '0' masks-out the reference, while 1 to 15 set the priority, where '1' has the highest, and '15' has the lowest priority. The highest priority prequalified reference is chosen as the active reference.

The automatically selected reference for each DPLL may be read from registers **T0\_Auto\_Active\_Ref** (0x1e) and **T4\_Auto\_Active\_Ref** (0x3b).

The pre-qualification scheme is described in the **Reference Inputs Monitoring and Qualification** section. When a selected active reference is disqualified, the highest priority qualified remaining reference is chosen. If multiple references share the same priority, they are ordered according to the duration of their qualification. The longer the duration, the higher the priority is set.

When a reference is disqualified, and subsequently re-qualified as the highest priority candidate, it may or may not be re-selected as the active reference. This is determined by either enabling or disabling "reversion" by writing bit 3 of the **T0\_Control\_Mode** (0x1c) or **T4\_Control\_Mode** (0x39) register (for T0 or T4, respectively) to "1" for revertive or to "0" for non-revertive operation.

If reversion is enabled, a qualified/re-qualified reference will be selected as the new active reference, if it is the highest priority qualified reference at that time. If reversion is disabled, the active reference will not be pre-empted by a higher priority reference until it is disqualified.

# Digital Phase Locked Loop General Description

The STC4130 includes both a T0 and T4 clock generator. Each clock generator has a DPLL, including a phase detector and a digital filter.

Each DPLL may select any of the 12 input reference clocks in master mode. In slave mode, they will

select the (T0/T4)\_XSYNC\_IN cross-couple SyncLink<sup>TM</sup> data link(s) as the source of phase information.

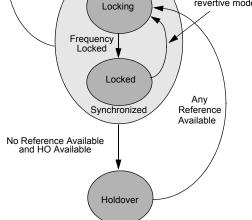

In master mode, the T0 and T4 clock generators may each operate in the Freerun, Synchronized, or Holdover modes:

#### 1. Free Run

In freerun mode, the **CLK(0-7)** clock outputs are determined directly from and have the accuracy of the digitally calibrated free running OCXO/TCXO. Reference inputs continue to be monitored for signal presence and frequency offset, but are not used to synchronize the outputs.

#### 2. Synchronized

The **CLK(0-7)** clock outputs are phase locked to and track the selected input reference. Upon entering the Locking mode, the device begins an acquisition process that includes reference qualification and frequency slew rate limiting, if needed. Once satisfactory lock is achieved, the "Locked" state is entered, and the "SYNC" bit is set in the **T(0/4)\_DPLL\_Status** register.

Each DPLL's loop bandwidth may be set independently. Loop bandwidth is selectable from 90mHz to 107Hz, by writing to the T0/4\_Bandwidth registers (0x1d/0x3a).

#### 3. Holdover

Upon entering holdover mode, the **CLK(0-7)** clock outputs are determined from the holdover history established for the last selected reference, or from a user supplied holdover history. Output frequency is determined by a weighted average of the holdover history, and accuracy is determined by the OCXO/ TCXO. Holdover mode may be entered manually or automatically. Automatic entry into holdover mode occurs when operating in the automatic mode, the reference is lost, and no other valid reference exists. The transfer into and out of holdover mode is designed to be smooth and free of hits.

Figure 4 shows the phase lock loop states and transitions for operation with automatic reference selection in Master mode.

Synchronous Clock for SETS

**STC4130**

**Data Sheet**

Figure 4: Device phase lock operational mode transition in Automatic Reference Selection/Master Mode

### **DPLL Operating Mode Details**

The T0 and T4 clock generators may operate in the Freerun, Synchronized, or Holdover modes, including some variants thereof:

#### Freerun Mode

The **CLK(0-7)** clock outputs are synthesized using the free running OCXO/TCXO, calibrated with the freerun frequency offset. The calibration offset may be programmed by the application by writing to the **Freerun\_Cal** register, (0x0e/0f). The calibration offset may be programmed from -102.4 to +102.3 ppm, in .1ppm steps, in two's complement form.

The Freerun mode may be entered automatically, when in the Automatic Reference Selection mode (as shown in figure 4), or manually, by writing to the **T(0/4)\_Manual\_Active\_Ref** registers.

#### Synchronized Mode

The Synchronized mode may be entered automatically, when in the Automatic Reference Selection mode (as shown in figure 4), or manually, by writing to the **T(0/4)\_Manual\_Active\_Ref** registers (0x1f/ 0x3c), selecting a reference as well as the operating mode.

Each DPLL's loop bandwidth may be set independently. Loop bandwidth is selectable from 90mHz to 107Hz by writing to the **T(0/4)\_Bandwidth** registers (0x1d/ 0x3a).

In the "Synchronized" mode, bit 0 of the **T(0/ 4)\_Control\_Mode** registers (0x1c, 0x39) determines the output clock to input reference phase alignment mode. In "Arbitrary" mode, the clock output phase relationship relative to the reference input phase is according to the initial start-up phase. In "Phase Align" mode, the output clocks are phase aligned to the selected reference. (It should be noted that output-to-reference phase alignment is meaningfull only in those cases where the output frequency and reference are the same or related by a factor of  $2^{n}$ .)

When locked on an external reference, two holdover histories are built, for use in Holdover mode:

- 1) Long-Term History This is a long-term averaged frequency of the selected external reference, accumulated according to a single-pole low pass filtering algorithm. The -3dB point of the algorithm may be application programmed for 9.7, 4.9, 2.4, 1.2, 0.61, or 0.30 mHz, by writing to the T(0/ 4)\_HO\_Ramp registers (0x30/ 0x4d). Internally, an express mode is used initially to apply a lower time-constant to speed up the history accumulation process. When a long term history has been built, it is indicated as available by the LHA bit 7 of the T(0/ 4)\_DPLL\_Status registers (0x37/0x54). Additionally, the application may flush/rebuild this long-term history, by writing to the T(0/ 4)\_Accu\_Flush registers (0x38, 0x55). The long-term history is used when operating in Holdover Mode, and may be read from the T(0/4)\_Long\_Term\_Accu\_History registers (0x24-0x27/ 0x41-0x44).

- 2) Short-Term History The short term history may be programmed for a -3dB point of 2.5,

# STC4130 Synchronous Clock for SETS Data Sheet

1.24, 0.62, or 0.31 mHz by writing to the **T(0/ 4)\_HO\_Ramp** registers (0x30/ 0x4d). The short-term history is used, in the event of a reference loss in manual reference selection mode, and may be read from the

T(0/4)\_Short\_Term\_Accu\_History registers (0x28-0x2b/ 0x45-ox48)

In manual mode selection, there are two special cases of the Synchronized mode:

**a)** "**Zombie**" **Mode** – If the selected active reference signal is lost, the DPLL output is generated according to a short-term history.

**b)** Out of Pull-in Range Mode - If the selected reference exceeds the pull-in range as programmed by the application, the DPLL output may be programmed to stay at the pull-in range limit, or to follow the reference. This is programmed by writing to bit 5 of the T(0/4)\_Control\_Mode registers (0x1c/ 0x39), specifying whether to follow or not follow a reference that has exceeded the pull-in range.

Additionally, when a device is operated as <u>a</u> slave in a master/slave pair (by tying the  $T(0/4)_M/S$  pin low), the device locks and phase align on the cross-coupled **SyncLink<sup>TM</sup>** data link signal on the **(T0/ T4)\_XSYNC\_IN** input.

When the device has locked on a reference, the "SYNC" bit 0 is set in the  $T(0/4)_DPLL_Status$  register (0x37/ 0x54). If synchronization is lost, the "LOL" bit 2 is set in the  $T(0/4)_DPLL_Status$  register.

#### Holdover Mode

The application may select either of two sources of frequency offset in Holdover mode, as determined by writing bit 2 of the T(0/4)\_Control\_Mode registers (0x1c/ 0x39):

a) Device Accumulated History Holdover Mode – uses the long-term history accumulated by the device to synthesize the DPLL output This is analogous to the Freerun mode, except that the Holdover algorithms effectively supply the "frequency offset" from the holdover history.

b) User Supplied History Mode – The DPLL output is synthesized according to an application supplied frequency offset, as provided in the T(0/ 4)\_User\_Accu\_History registers (0x2c/ 0x49). To facilitate the user's accumulation of a holdover history, the user may read the short term history of the active reference from the T(0/ 4)\_Shor\_Term\_Accu\_History registers (0x28-0x2b/

0x45-0x48).

On either transition, from Synchronized to Holdover, or back from Holdover to Synchronized, an application programmable maximum slew rate of 1, 1.5, or 2 ppm/second (or no slew rate limit) is applied, as written to the **T(0/4)\_HO\_Ramp** registers (0x30/ 0x4d).

### **Output Clocks**

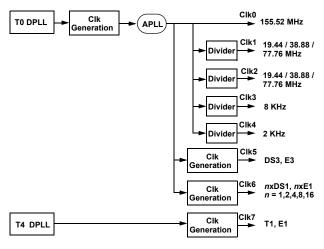

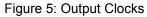

The clock output section includes 4 clock generations, an APLL, and four dividers, and generates nine synchronized clocks, as shown in figure 5.

The first synthesizer drives an analog PLL and generates five output clocks. It is driven from the T0 DPLL:

- CLK0: 155.52 MHz (LVPECL), enabled/disabled by writing the CLK0\_Sel register (0x56), bit 0.

- CLK1: Programmable at 19.44MHz, 38.88MHz, 77.76 MHz, and "disabled", by writing to the CLK1\_Sel register (0x57), bits 0 - 1.

- CLK2: Programmable at 19.44MHz, 38.88MHz, 77.76 MHz, and "disabled", by writing to the CLK2\_Sel register (0x58), bits 0 - 1.

- CLK3: 8kHz, 50% duty cycle or programmable pulse width, and may be disabled by writing to the CLK3\_Sel register (0x59), bits 0 -5.

- CLK4: 2kHz, 50% duty cycle or programma-

# STC4130 Synchronous Clock for SETS Data Sheet

ble pulse width, and may be disabled by writing to the **CLK4\_Sel** register (0x5a), bits 0 -5.

Two synthesizers generate additional clocks from the T0 clock generator:

- CLK5: Either DS3 or E3 rate, or "disabled", programmed by writing to the CLK5\_Sel register (0x5b), bits 0 - 1.

- CLK6: Programmable at nxDS1 or nxE1 where n=1,2,4,8,16, or may be disabled, by writing to the CLK6\_Sel register (0x5c), bits 0 - 3.

One synthesizer is driven by the T4 clock generator:

CLK7: Either DS1 or E1 rate, or "disabled", programmed by writing to the CLK7\_Sel register (0x5d), bits 0 - 1.

When a clock output is disabled, the pin is tri-stated. In addition, the **T0\_Xsync\_OUT** and **T4\_Xsync\_OUT** outputs provide phase information and state data for master/slave operation of the T0 and T4 clock generators.

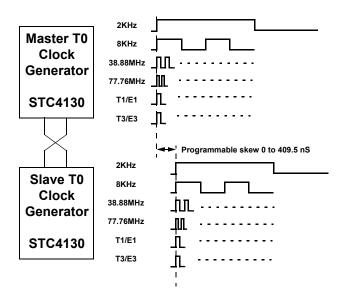

Note that the **CLK1**, **2**, **5** and **6** are phase aligned with the **CLK3** (8KHz) as shown in Figure 7. **CLk3** is phase aligned with **CLK4** (2KHz).

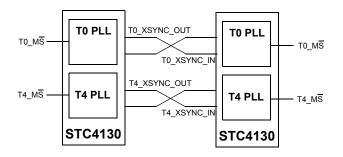

### Master/Slave Configuration

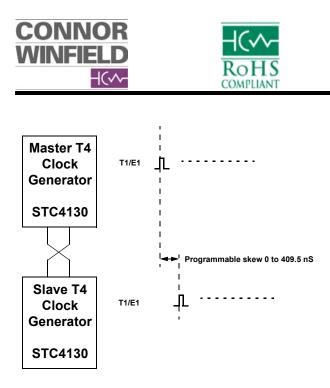

Pairs of STC4130 devices may be operated in a master/slave configuration for added reliability, as shown in Figure 6.

Figure 6: Master/Slave Configuration

Devices are configured for master/slave operation by cross-connecting their respective

T(0/4)\_Xsync\_Out and/or T(0/4)\_Xsync\_In pins.

The **T(0/4)\_MS** pins determine the master or slave mode for each clock generator. 1=Master, 0=Slave. Thus, master/slave state is always manually controlled by the application. The master synchronizes to the selected input reference, while the slave synchronizes and phase-aligns according to data received over the **T(0/4)\_Xsync\_Out** / **T(0/ 4)\_Xsync\_In** data link from the unit in master mode.

The T0 and T4 PLL's may be operated completely independent of each other – either or both may be cross-connected as master/slave pairs across two STC4130 devices, and master/slave states may be set the same or opposite within a given device.

In slave mode, the operational mode is "Synchronized" and the **T(0/4)\_Xsync\_Out** data links provide phase and state information. Bits 0 and 1 of the **T0\_T4\_MS\_Sts** register reflect the states of the **T(0/4)\_MS** pins.

### Master/Slave Operation

Perfect phase alignment of the **Clk(x)** output clocks (between the clock generators in two devices) would require no delay on the cross-couple data link connection. To accommodate path length delays, the STC4130 provides a programmable phase skew feature. See figures 7 and 8. The slave's **Clk(x)** outputs

# STC4130 Synchronous Clock for SETS Data Sheet

may be phase shifted from 0 to +409.5nS, in 100pS increments according to the contents of the **T(0/ 4)\_Slave\_Phase\_Adj** (0x05/06, 0x07/08) registers to compensate for the path length of the **T(0/ 4)\_Xsync\_Out** to **T(0/4)\_Xsync\_In** connections. This offset may therefore be programmed to exactly compensate for the actual path length delay associated with the particular application's cross-couple traces. Thus, master/slave switches with the STC4130 devices may be accomplished with nearzero phase hits.

The first time a clock generator becomes a slave, such as immediately after power-up, its output clock phase starts out arbitrary, and will quickly phasealign to the master unit. The phase skew will be eliminated (or converged to the programmed phase offset) step by step. The whole pull-in-and-lock process will complete in about 16 seconds. There is no frequency slew protection in slave mode. In slave mode, the unit's mission is to lock to and follow the master.

Note the phase alignment of all clock outputs from the T0 clock generator with the 2KHz output.

Figure 8: T4 CLK7 Master/Slave Skew Control

Once a pair of clock generators has been operating in aligned master/slave mode, and a master/slave switch occurs, the clock generator that becomes master will maintain its output clock phase and frequency while a phase rebuild (to the current output clock phase) is performed on its selected reference input. Therefore, as master mode operation commences, there will be no phase or frequency hits on the clock output. Assuming the phase offset is programmed for the actual propagation delay of this cross-couple path, there will again be no phase hits on the output clock of the clock generator that has transitioned from master to slave. The data link will also provide state information that will allow the new master to lock on the same reference as the old master.

STC4130

**Data Sheet**

Synchronous Clock for SETS

### **Processor Interface Descriptions**

The STC4130 supports four common microprocessor control interfaces: SPI, Motorola, Intel, and multiplex parallel. The control interface mode is selected with the **Bus\_Mode(0/1)** pins:

| Bus_Mode1,<br>Bus_Mode0 | Bus Mode           |

|-------------------------|--------------------|

| 00                      | SPI                |

| 01                      | Motorola           |

| 10                      | Intel              |

| 11                      | Multiplex parallel |

The following sections describe each bus mode's interface timing:

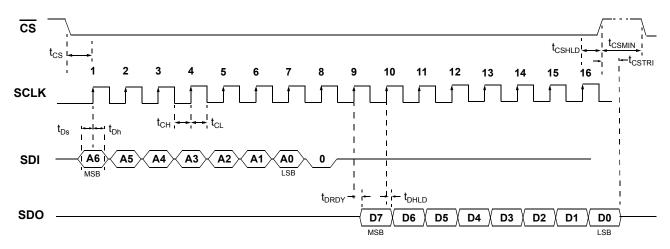

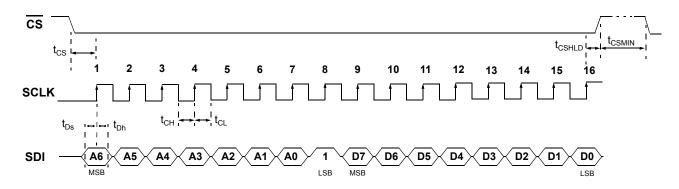

#### SPI Bus Mode

The SPI interface bus mode uses the BUS\_CS, BUS\_ALE, BUS\_WRB, and BUS\_RDY pins, corresponding to CS, SCLK, SDI, and SDO respectively, with timing as shown in figures 9 and 10:

#### Serial Bus Timing

#### Figure 9: Serial Bus Timing, Read access

# STC4130 Synchronous Clock for SETS Data Sheet

### Table 5: Serial Bus Timing

| Symbol             | Description                               | Min | Max | Unit |

|--------------------|-------------------------------------------|-----|-----|------|

| t <sub>CS</sub>    | CS low to SCLK high                       | 10  |     | nS   |

| t <sub>CH</sub>    | SCLK high time                            | 25  |     | nS   |

| t <sub>CL</sub>    | SCLK low time                             | 25  |     | nS   |

| t <sub>Ds</sub>    | Data setup time                           | 10  |     | nS   |

| t <sub>Dh</sub>    | Data hold time                            | 10  |     | nS   |

| t <sub>DRDY</sub>  | Data ready                                |     | 7   | nS   |

| t <sub>DHLD</sub>  | Data hold                                 | 5   |     | nS   |

| t <sub>CSHLD</sub> | Chip select hold                          | 30  |     | nS   |

| t <sub>CSTRI</sub> | Chip select to data tri-state             |     | 5   | nS   |

| t <sub>CSMIN</sub> | Minimum delay between successive accesses | 50  |     | nS   |

#### Motorola Bus

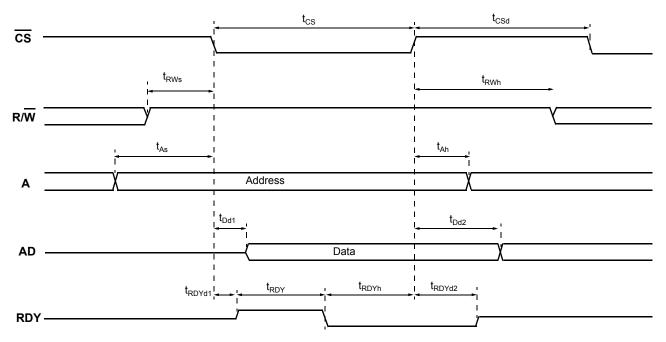

In Motorola mode, the device will interface to 680xx type processors. The BUS\_CS, BUS\_RDB, BUS\_A(6-0), BUS\_AD(7-0), and BUS\_RDY pins are used, corresponding to CS, R/W, A, AD, and RDY, respectively. Timing is as follows:

#### Motorola Bus Timing

Figure 11: Motorola Bus Read Timing

### Table 6: Motorola Bus Read Timing

| Symbol            | Description                                      | Min | Max | Unit |

|-------------------|--------------------------------------------------|-----|-----|------|

| t <sub>CS</sub>   | CS low time                                      | 50  |     | nS   |

| t <sub>CSd</sub>  | CS minimum high time between reads/writes        | 50  |     | nS   |

| t <sub>RWs</sub>  | Read/write setup time                            | 0   |     | nS   |

| t <sub>RWh</sub>  | Read/write hold time                             | 0   |     | nS   |

| t <sub>As</sub>   | Address setup                                    | 10  |     | nS   |

| t <sub>Ah</sub>   | Address hold                                     | 0   |     | nS   |

| t <sub>Dd1</sub>  | Data valid delay from $\overline{\text{CS}}$ low |     | 50  | nS   |

| t <sub>Dd2</sub>  | Data high-z delay from $\overline{CS}$ low       |     | 10  | nS   |

| t <sub>RDY1</sub> | CS low to RDY high delay                         |     | 13  | nS   |

| t <sub>RDY</sub>  | RDY high time                                    | 37  | 50  | nS   |

| t <sub>RDYh</sub> | CS hold after RDY low                            | 0   |     | nS   |

| Symbol            | Description                    | Min | Max | Unit |

|-------------------|--------------------------------|-----|-----|------|

| t <sub>RDY2</sub> | RDY high-z delay after CS high |     | 9   | nS   |

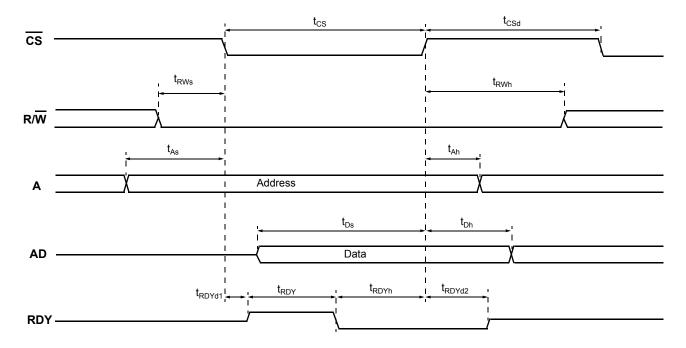

Figure 12: Motorola Bus Write timing

### Table 7: Motorola Bus Read Timing

| Symbol             | Description                                 | Min | Max | Unit |

|--------------------|---------------------------------------------|-----|-----|------|

| t <sub>CS</sub>    | CS low time                                 | 50  |     | nS   |

| t <sub>CSd</sub>   | CS minimum high time between writes/reads   | 50  |     | nS   |

| t <sub>RWs</sub>   | Read/write setup time                       | 0   |     | nS   |

| t <sub>RWh</sub>   | Read/write hold time                        | 0   |     | nS   |

| t <sub>As</sub>    | Address setup                               | 10  |     | nS   |

| t <sub>Ah</sub>    | Address hold                                | 0   |     | nS   |

| t <sub>Ds</sub>    | Data setup time before $\overline{CS}$ high | 10  |     | nS   |

| t <sub>Dh</sub>    | Data hold time after $\overline{CS}$ high   | 10  |     | nS   |

| t <sub>RDYd1</sub> | CS low to RDY high delay                    |     | 13  | nS   |

| t <sub>RDY</sub>   | RDY high time                               | 37  |     | nS   |

| t <sub>RDYh</sub>  | CS hold after RDY low                       | 0   |     | nS   |

| Symbol             | Description                                 | Min | Max | Unit |

|--------------------|---------------------------------------------|-----|-----|------|

| t <sub>RDYd2</sub> | RDY high-z delay after $\overline{CS}$ high |     | 7   | nS   |

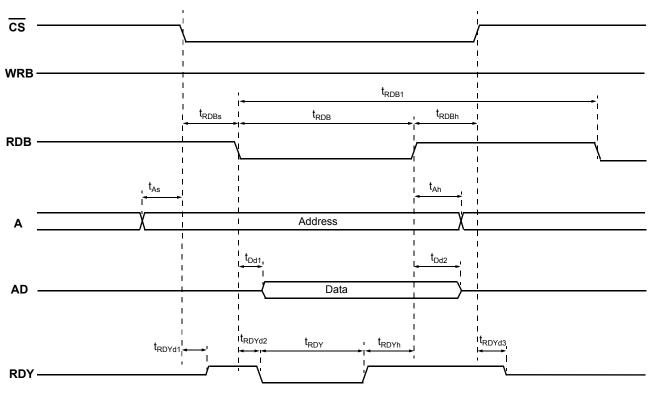

#### Intel Bus

In Intel mode, the device will interface to 80x86 type processors. The BUS\_CS, BUS\_WRB, BUS\_RDB, BUS\_A(6-0), BUS\_AD(7-0), and BUS\_RDY pins are used, corresponding to CS, WRB, RDB, A, AD, and RDY, respectively. Timing is as follows:

#### Figure 13: Intel Bus Read Timing

### Table 8: Intel Bus Read Timing

| Symbol             | Description                     | Min | Max | Unit |

|--------------------|---------------------------------|-----|-----|------|

| t <sub>RDBs</sub>  | Read setup time                 | 0   |     | nS   |

| t <sub>RDB</sub>   | Read low time                   | 40  |     | nS   |

| t <sub>RDBh</sub>  | Read hold time                  | 0   |     | nS   |

| t <sub>RDB1</sub>  | Time between consecutive reads  | 50  |     | nS   |

| t <sub>As</sub>    | Address setup                   | 10  |     | nS   |

| t <sub>Ah</sub>    | Address hold                    | 0   |     | nS   |

| t <sub>Dd1</sub>   | Data valid delay from RDB high  |     | 50  | nS   |

| t <sub>Dd2</sub>   | Data high-z delay from RDB high |     | 10  | nS   |

| t <sub>RDYd1</sub> | CS low to RDY high delay        |     | 13  | nS   |

# STC4130 Synchronous Clock for SETS Data Sheet

| Symbol             | Description                    | Min | Max | Unit |

|--------------------|--------------------------------|-----|-----|------|

| t <sub>RDYd2</sub> | RDB low to RDY low             |     | 40  | nS   |

| t <sub>RDY</sub>   | RDY low time                   | 50  |     | nS   |

| t <sub>RDYh</sub>  | RDB hold after RDY high        | 0   |     | nS   |

| t <sub>RDY3</sub>  | RDY high-z delay after CS high |     | 11  | nS   |

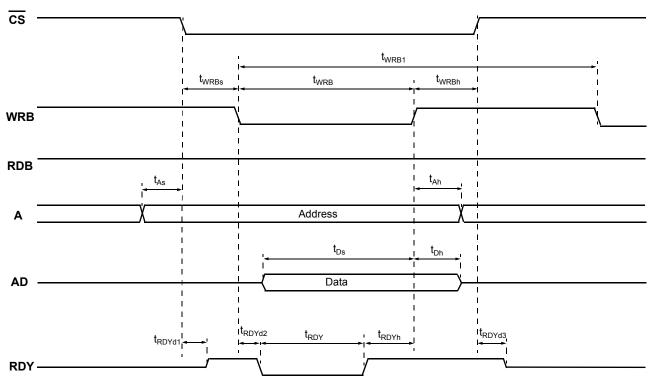

Figure 14: Intel Write Read Timing

### Table 9: Intel Bus Write Timing

| Symbol             | Description                                 | Min | Max | Unit |

|--------------------|---------------------------------------------|-----|-----|------|

| t <sub>WRBs</sub>  | Write setup time                            | 0   |     | nS   |

| t <sub>WRB</sub>   | Write low time                              | 40  |     | nS   |

| t <sub>WRBh</sub>  | Write hold time                             | 0   |     | nS   |

| t <sub>WRB1</sub>  | Time between consecutive writes             | 50  |     | nS   |

| t <sub>As</sub>    | Address setup                               | 10  |     | nS   |

| t <sub>Ah</sub>    | Address hold                                | 0   |     | nS   |

| t <sub>Ds</sub>    | Data setup time before $\overline{CS}$ high | 10  |     | nS   |

| t <sub>Dh</sub>    | Data hold time after $\overline{CS}$ high   | 10  |     | nS   |

| t <sub>RDYd1</sub> | CS low to RDY high delay                    |     | 13  | nS   |

| t <sub>RDYd2</sub> | RDB low to RDY low                          |     | 40  | nS   |

| t <sub>RDY</sub>   | RDY low time                                | 50  |     | nS   |

| t <sub>RDYh</sub>  | RDB hold after RDY high                     | 0   |     | nS   |

| t <sub>RDY3</sub>  | RDY high-z delay after $\overline{CS}$ high |     | 10  | nS   |

#### Multiplex Bus Mode

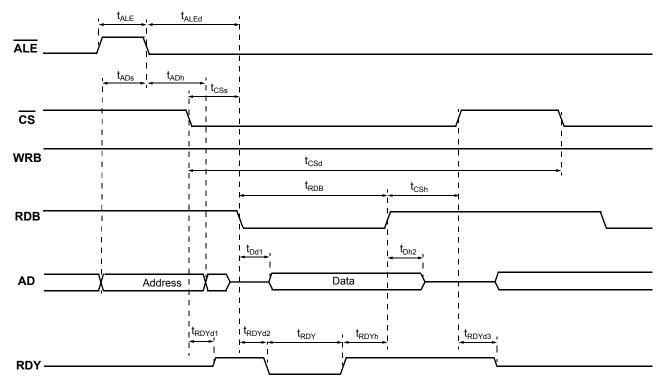

In multiplex bus mode, the device can interface with microprocessors which share the address and data on the same bus signals. The <u>BUS\_ALE</u>, <u>BUS\_CS</u>, <u>BUS\_WRB</u>, <u>BUS\_RDB</u>, <u>BUS\_AD</u>(7-0), and <u>BUS\_RDY</u> pins are used, corresponding to <u>ALE</u>, <u>CS</u>, <u>WRB</u>, <u>RDB</u>, <u>AD</u>, and <u>RDY</u>, respectively.

#### **Multiplex Bus Timing**

#### Figure 15: Multiplex Bus Read Timing

| Symbol             | Description                       | Min | Max | Unit |

|--------------------|-----------------------------------|-----|-----|------|

| t <sub>ALE</sub>   | ALE high time                     | 10  |     | nS   |

| t <sub>ALEd</sub>  | ALE falling edge to RDB low       | 0   |     | nS   |

| t <sub>ADs</sub>   | Address setup time                | 10  |     | nS   |

| t <sub>ADh</sub>   | Address hold time                 | 10  |     | nS   |

| t <sub>CSs</sub>   | Read setup time                   | 0   |     | nS   |

| t <sub>RDB</sub>   | Read time                         | 40  |     | nS   |

| t <sub>CSh</sub>   | CS hold time                      | 0   |     | nS   |

| t <sub>CSd</sub>   | CS delay for multiple read/writes | 50  |     | nS   |

| t <sub>Dd1</sub>   | Data valid delay from RDB low     |     | 50  | nS   |

| t <sub>Dh2</sub>   | Data high-z from RDB high         |     | 10  | nS   |

| t <sub>RDYd1</sub> | CS low to RDY active              |     | 13  | nS   |

| t <sub>RDYd2</sub> | RDB low to RDY low                |     | 40  | nS   |

| t <sub>RDY</sub>   | RDY low time                      | 50  |     | nS   |

| t <sub>RDYh</sub>  | Read hold after RDY high          | 0   |     | nS   |

#### Table 10: Multiplex Bus Read Timing

RDY

t<sub>RDYd1</sub>

f

I t<sub>RDYd2</sub>

# STC4130 Synchronous Clock for SETS Data Sheet

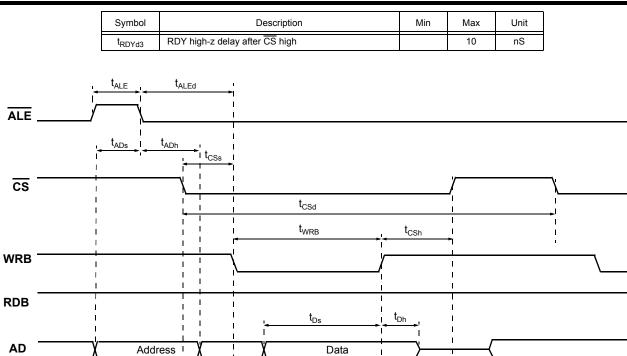

| Figure | 16: Multiplex | Bus Write | Timing |

|--------|---------------|-----------|--------|

t<sub>WRBh</sub>

t<sub>RDYd3</sub>

t<sub>RDY</sub>

| Symbol             | Description                       | Min | Max | Unit |

|--------------------|-----------------------------------|-----|-----|------|

| t <sub>ALE</sub>   | ALE high time                     | 10  |     | nS   |

| t <sub>ALEd</sub>  | ALE falling edge to RDB low       | 0   |     | nS   |

| t <sub>ADs</sub>   | Address setup time                | 10  |     | nS   |

| t <sub>ADh</sub>   | Address hold time                 | 10  |     | nS   |

| t <sub>CSs</sub>   | Write CS setup time               | 0   |     | nS   |

| t <sub>WRB</sub>   | Write time                        | 40  |     | nS   |

| t <sub>CSh</sub>   | CS hold time                      | 10  |     | nS   |

| t <sub>CSd</sub>   | CS delay for multiple write/reads | 50  |     | nS   |

| t <sub>Ds</sub>    | Data setup time                   | 10  |     | nS   |

| t <sub>Dh</sub>    | Data hold time                    | 10  |     | nS   |

| t <sub>RDYd1</sub> | CS low to RDY active              |     | 13  | nS   |

| t <sub>RDYd2</sub> | WRB low to RDY low                |     | 40  | nS   |

| t <sub>RDY</sub>   | RDY low time                      | 50  |     | nS   |

| t <sub>WRBh</sub>  | WRB hold after RDY high           | 0   | İ   | nS   |

| t <sub>RDYd3</sub> | RDY high-z delay after CS high    |     | 9   | nS   |

#### Table 11: Multiplex Bus Write Timing

### **Register Descriptions and Operation**

### **General Register Operation**

The STC4130 device has 1, 2, and 4 byte registers. One byte registers are read and written directly. Two and four byte registers must be read and written in a specific manner and order, as follows:

#### Multibyte register reads

A multibyte register read must commence with a read of the least significant byte first. This triggers a transfer of the remaining byte(s) to a holding resgister, ensuring that the remaining data will not change with the continuing operation of the device. The remaining byte(s) may then be read in any order, and with no timing restrictions.

#### Multibyte register writes

A multibyte register write must commence with a write to the least significant byte first. Subsequent writes to the remaining byte(s)must be performed in ascending byte order, but with no timing restrictions. Multibyte register writes are temporarily stored in a holding register, and are transferred to the target register when the most significant byte is written.

#### **Clearing bits in the Interrupt Status Register**

Interrupt event register (**Intr\_Event**, 0x5e~0x5f) bits are cleared by writing a "1" to the bit position to be cleared. Interrupt bit positions to be left as is are written with a "0".

#### **Default Register Settings**

#### Chip\_ID, 0x00 (R)

| Address | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |  |

|---------|------|------|------|------|------|------|------|------|--|--|

| 0x00    |      | 0x30 |      |      |      |      |      |      |  |  |

| 0x01    |      | 0x41 |      |      |      |      |      |      |  |  |

#### Chip\_Rev, 0x02 (R)

|   | Address | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |

|---|---------|------|------|------|------|------|------|------|------|--|

| ſ | 0x02    |      | 0x01 |      |      |      |      |      |      |  |

#### Chip\_Sub\_Rev, 0x03 (R)

| Address | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |  |

|---------|------|------|------|------|------|------|------|------|--|

| 0x03    |      | 0x01 |      |      |      |      |      |      |  |

#### T0\_T4\_MS\_Sts, 0x04 (R/W)

| Address | Bit7 | Bit6     | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0   |

|---------|------|----------|------|------|------|------|------|--------|

| 0x04    |      | Not used |      |      |      |      |      | T0 M/S |

Reflects the states of the **T0/T4\_Master\_Slave** select pins. 1 = Master, 0 = slave

#### T0\_Slave\_Phase\_Adj, 0x05 (R/W)

| Address | Bit7 | Bit6                                                                  | Bit5 | Bit4 | Bit3           | Bit2 | Bit1                       | Bit0          |  |  |  |

|---------|------|-----------------------------------------------------------------------|------|------|----------------|------|----------------------------|---------------|--|--|--|

| 0x05    |      | Adjust T0 slave phase from 0 ~ 409.5 nS in 0.1 nS steps, lower 8 bits |      |      |                |      |                            |               |  |  |  |

| 0x06    |      | Not                                                                   | used |      | Adjust T0 slav | •    | 0 ~ 409.5 nS in<br>`4 bits | 0.1 nS steps, |  |  |  |

The T0 slave phase may be adjusted 0 to 409.5 nS relative to the cross couple input with 0.1 nS resolution. This is a 12 bit register, split across address 0x05 and 0x06. Default value: 0.

#### T4\_Slave\_Phase\_Adj, 0x07 (R/W)

| Address | Bit7 | Bit6                                                                  | Bit5 | Bit4 | Bit3          | Bit2 | Bit1                      | Bit0          |  |  |  |

|---------|------|-----------------------------------------------------------------------|------|------|---------------|------|---------------------------|---------------|--|--|--|

| 0x07    |      | Adjust T4 slave phase from 0 ~ 409.5 nS in 0.1 nS steps, lower 8 bits |      |      |               |      |                           |               |  |  |  |

| 0x08    |      | Not                                                                   | used |      | Adjust T4 sla |      | 0 ~ 409.5 nS in<br>4 bits | 0.1 nS steps, |  |  |  |

The T4 slave phase may be adjusted 0 to 409.5 nS relative to the cross couple input with 0.1 nS resolution. This is a 12 bit register, split across address 0x07 and 0x08. Default value: 0.

#### Fill\_Rate, 0x09 (R/W)

| Address | Bit7 | Bit6 | Bit5 | Bit4 | Bit3         | Bit2             | Bit1             | Bit0  |

|---------|------|------|------|------|--------------|------------------|------------------|-------|

| 0x09    | Not  | used |      |      | Leaky bucket | fill rate window | , 0 ~ 15, Defaul | t = 0 |

Sets the fill rate window size for the reference activity monitor. The value can be set from 0 to 15, corresponding to 1mS to 16mS.

Default value: 1.

#### Leak\_Rate, 0x0a (R/W)

| Address | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2                          | Bit1                | Bit0 |

|---------|------|------|------|------|------|-------------------------------|---------------------|------|

| 0x0a    |      | Not  | used |      | L    | eak rate, 1/n <sup>th</sup> . | of fill rate, 0 ~ 1 | 5    |

Sets the leak rate for the reference activity monitor to 1/nth of the fill rate, corresponding to n x the fill rate window size. Valid values from 0 to 15, corresponding to n = 1 to 16. For example, if the fill rate is set to 4mS and the leak rate is set to 3 (n = 4), the leak rate window size will be 16mS. Default value: 3.

#### Bucket\_Size, 0x0b (R/W)

| Address | Bit7 | Bit6 | Bit5                      | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|---------|------|------|---------------------------|------|------|------|------|------|

| 0x0b    | Not  | used | Leaky bucket size, 0 ~ 63 |      |      |      |      |      |

Sets the leaky bucket size for the reference activity monitor. Bucket size must be greater than or equal to the alarm assert value. Invalid values will not be written to the register. Default value: 20.

#### Assert\_Threshold, 0x0c (R/W)

| Address | Bit7  | Bit6 | Bit5                                        | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|---------|-------|------|---------------------------------------------|------|------|------|------|------|

| 0x0c    | Not i | used | Leaky bucket alarm assert threshold, 0 ~ 63 |      |      |      |      |      |

Sets the leaky bucket alarm assert threshold for the reference activity monitor. The alarm assert threshold value must be greater than the de-assert threshold value and less than or equal to the bucket size value. Invalid values will not be written to the register. Default value: 15.

#### De\_Assert\_Threshold, 0x0d (R/W)

|   | Address | Bit7 | Bit6 | Bit5                                           | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|---|---------|------|------|------------------------------------------------|------|------|------|------|------|

| ſ | 0x0d    | Not  | used | Leaky bucket alarm de-assert threshold, 0 ~ 63 |      |      |      |      |      |

Sets the leaky bucket alarm de-assert threshold for the reference activity monitor. The de-assert threshold value must be less than the assert threshold value. Invalid values will not be written to the register. Default value: 10.

#### Freerun\_Cal, 0x0e (R/.W)

| Address | Bit7                  | Bit6         | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|---------|-----------------------|--------------|------|------|------|------|------|------|

| 0x0e    |                       | Lower 8 bits |      |      |      |      |      |      |

| 0x0f    | Not used Upper 3 bits |              |      |      |      |      |      |      |

Freerun TCXO/OCXO calibration, from -102.4 to +102.3 ppm, in .1ppm steps, two's complement. Default value: 0.

#### Disqualification\_Range, 0x10 (R/W)

| Address | Bit7                  | Bit6         | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|---------|-----------------------|--------------|------|------|------|------|------|------|

| 0x10    |                       | Lower 8 bits |      |      |      |      |      |      |

| 0x11    | Not used Upper 3 bits |              |      |      |      |      |      |      |