| • | Inputs | are | TTL- | Voltage | Compatible |

|---|--------|-----|------|---------|------------|

- Internal Look-Ahead for Fast Counting

- Carry Output for n-Bit Cascading

- Fully Synchronous Operation for Counting

- Synchronously Programmable

- Flow-Through Architecture to Optimize PCB Layout

- Center-Pin V<sub>CC</sub> and GND Configurations to Minimize High-Speed Switching Noise

- EPIC™ (Enhanced-Performance Implanted CMOS) 1-μm Process

- 500-mA Typical Latch-Up Immunity at 125°C

- Package Options Include Plastic "Small Outline" Packages, Ceramic Chip Carriers, and Standard Plastic and Ceramic 300-mil DIPs

#### description

This synchronous, presettable 4-bit binary counter features an internal carry look-ahead for application in high-speed counting designs. Synchronous operation is provided by having all flip-flops clocked simultaneously so that the outputs change coincident with each other when so instructed by the count-enable inputs and internal gating.

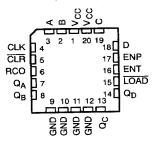

#### 54ACT11161 ... J PACKAGE 74ACT11161 ... DW OR N PACKAGE (TOP VIEW)

RCO [ 20 CLR 19 CLK QA [] 2 Ов 🛛 з 18 🛮 A GND 4 17 B GND [ 5 16 VCC GND 6 15 🛮 VCC GND 7 14 C 13 🛛 D Q<sub>C</sub> [] 8 12 ENP QD [] a 11 ENT LOAD [

#### 54ACT11161 ... FK PACKAGE (TOP VIEW)

This mode of operation eliminates the output counting spikes that are normally associated with asynchronous (ripple clock) counters. A buffered clock input triggers the four flip-flops on the rising (positive-going) edge of the clock input waveform.

This counter is fully programmable; that is, it may be preset to any number between 0 and 5. As presetting is synchronous, setting up a low level at the load input disables the counter and causes the outputs to agree with the setup data after the next clock pulse regardless of the levels of the enable inputs.

The clear function for the 'ACT11161 is synchronous and a low level at the clear input sets all four of the flip-flop outputs low regardless of the levels of the clock, load, or enable inputs. This synchronous clear allows the count length to be modified easily by decoding the Q outputs for the maximum count desired. The active-low output of the gate used for decoding is connected to the clear input to synchronously clear the counter to 0000 (LLLL).

The carry look-ahead circuitry provides for cascading counters for n-bit synchronous applications without additional gating. Instrumental in accomplishing this function are two count-enable inputs and a ripple carry output. Both count-enable inputs (ENP and ENT) must be high to count, and ENT is fed forward to enable the ripple carry output (RCO). RCO thus enabled will produce a high-level pulse while the count is 15 (HHHH). This high-level overflow ripple carry pulse can be used to enable successive cascaded stages. Transitions at the ENP or ENT are allowed regardless of the level of the clock input.

EPIC is a trademark of Texas Instruments Incorporated.

PRODUCT PREVIEW documents contain information on products in the formative or design phase of development. Characteristic data and other specifications are design goals. Texas instruments reserves the right to change or discontinue these products without notice.

Copyright © 1990, Texas Instruments Incorporated

2-176

POST OFFICE BOX 655303 - DALLAS, TEXAS 75265

Ti0159--- D3452, MARCH 1990

#### description (continued)

This counter features a fully independent clock circuit. Changes at control inputs (ENP, ENT, or  $\overline{\text{LOAD}}$ ) that will modify the operating mode have no effect on the contents of the counter until clocking occurs. The function of the counter (whether enabled, disabled, loading, or counting) will be dictated solely by the conditions meeting the setup and hold times.

The 54ACT11161 is characterized for operation over the full military temperature range of  $-55^{\circ}$ C to 125°C. The 74ACT11161 is characterized for operation from  $-40^{\circ}$ C to 85°C.

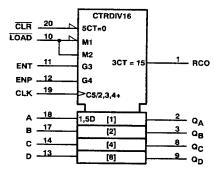

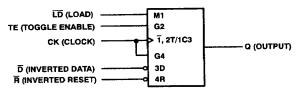

#### logic symbol†

<sup>&</sup>lt;sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12. Pin numbers shown are for DW, J, and N packages.

PRODUCT PREVIEW

# 54ACT11161, 74ACT11161 SYNCHRONOUS 4-BIT BINARY COUNTERS

D3452, MARCH 1990-TI0159

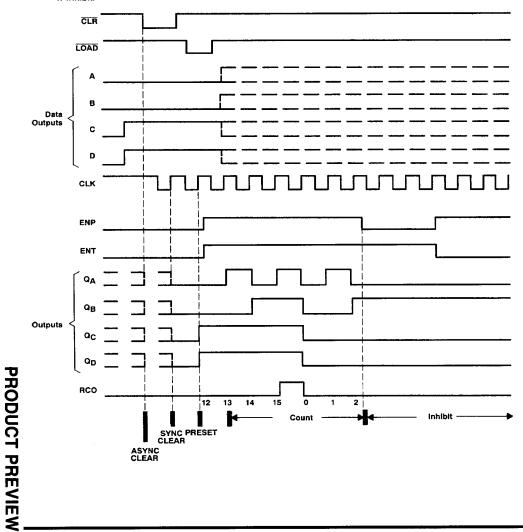

#### output sequence

Illustrated below is the following sequence:

- 1. Synchronously clear outputs to zero

- 2. Preset to binary twelve

- 3. Count to thirteen, fourteen, zero, one, and two

- 4. Inhibit.

POST OFFICE BOX 655303 - DALLAS, TEXAS 75265

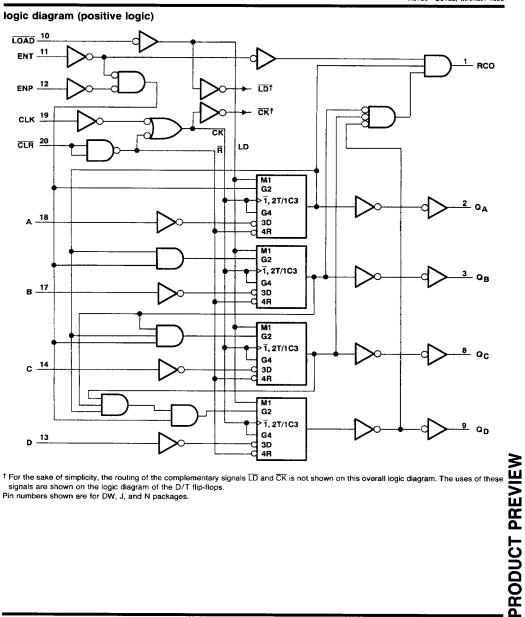

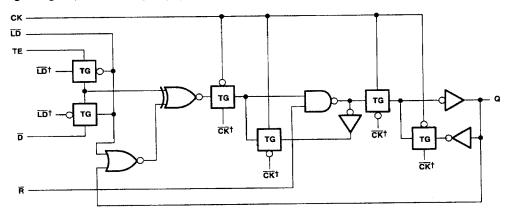

† For the sake of simplicity, the routing of the complementary signals  $\overline{\mathsf{LD}}$  and  $\overline{\mathsf{CK}}$  is not shown on this overall logic diagram. The uses of these signals are shown on the logic diagram of the D/T flip-flops.

Pin numbers shown are for DW, J, and N packages.

2-179

D3452, MARCH 1990-TI0159

## logic symbol, each D/T flip-flop (positive logic)

### logic diagram, each D/T flip-flop (positive logic)

<sup>†</sup> The origins of the signals  $\overline{\text{LD}}$  and CK are shown in the logic diagrams of the overall devices.

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)‡

| and not | Supply voltage range, V <sub>C</sub> C  Input voltage range, V <sub>I</sub> (see Note 1) | ± 20 mA<br>± 50 mA<br>± 50 mA<br>± 50 mA<br>± 125 mA<br>to 150°C |

|---------|------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| EVIEW   |                                                                                          |                                                                  |

2-180

POST OFFICE BOX 655303 - DALLAS, TEXAS 75265

TI0159-D3452, MARCH 1990

## recommended operating conditions

|       |                                    | 54ACT | 54ACT11161 |      | 74ACT11161 |      |

|-------|------------------------------------|-------|------------|------|------------|------|

|       |                                    | MIN   | MAX        | MIN  | MAX        | UNIT |

| VCC   | Supply voltage                     | 4.5   | 5.5        | 4.5  | 5.5        | ٧    |

| VIH   | High-level input voltage           | 2     |            | 2    |            | ٧    |

| VIL   | Low-level input voltage            |       | 0.8        |      | 0.8        | ٧    |

| VI    | Input voltage                      | 0     | Vcc        | 0    | Vcc        | ٧    |

| Vo    | Output voltage                     | 0     | Vcc        | 0    | Vcc        | ٧    |

| ЮН    | High-level output current          |       | -24        |      | -24        | mA   |

| lOL   | Low-level output current           |       | 24         |      | 24         | mA   |

| Δt/Δv | Input transition rise or fall rate | 0     | 10         | 0    | 10         | ns/V |

| TA    | Operating free-air temperature     | -55   | 125        | - 40 | 85         | °C   |

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER         | TEST SOURITIONS                                             | vcc   | T <sub>A</sub> = 25°C |         | 54AC | 54AC11161 |      | 74AC11161    |      |

|-------------------|-------------------------------------------------------------|-------|-----------------------|---------|------|-----------|------|--------------|------|

| PARAMETER         | TEST CONDITIONS                                             |       | MIN                   | TYP MAX | MIN  | MAX       | MIN  | MAX          | UNIT |

|                   | I <sub>OH</sub> = -50 μA                                    | 4.5 V | 4.4                   |         | 4.4  |           | 4.4  |              | v    |

|                   |                                                             | 5.5 V | 5.4                   |         | 5.4  |           | 5.4  |              |      |

| V+                | J 04 A                                                      | 4.5 V | 3.94                  |         | 3.7  |           | 3.8  |              |      |

| VOH               | IOH = -24 mA                                                | 5.5 V | 4.94                  |         | 4.7  |           | 4.8  |              |      |

|                   | I <sub>OH</sub> = -50 mA <sup>†</sup>                       | 5.5 V |                       |         | 3.85 |           |      |              |      |

|                   | $I_{OH} = -75 \text{ mA}^{\dagger}$                         | 5.5 V |                       |         |      |           | 3.85 |              |      |

|                   | In 50 A                                                     | 4.5 V | T                     | 0.1     |      | 0.1       |      | 0.1          | ٧    |

|                   | I <sub>OL</sub> = 50 μA                                     | 5.5 V |                       | 0.1     |      | 0.1       |      | 0.1          |      |

| Va                | I <sub>OL</sub> = 24 mA                                     | 4.5 V |                       | 0.36    |      | 0.5       |      | 0.44         |      |

| VOL               |                                                             | 5.5 V |                       | 0.36    |      | 0.5       |      | 0.44         |      |

|                   | IOL = 50 mA <sup>†</sup>                                    | 5.5 V |                       |         |      | 1.65      |      |              |      |

|                   | I <sub>OL</sub> = 75 mA <sup>†</sup>                        | 5.5 V |                       |         |      |           |      | 0.44<br>1.65 |      |

| 4                 | Vt = VCC or GND                                             | 5.5 V | 1                     | ± 0.1   |      | ±1        |      | ±1           | μΑ   |

| ICC               | V <sub>I</sub> = V <sub>CC</sub> or GND, I <sub>O</sub> = 0 | 5.5 V |                       | 8       |      | 160       |      | 80           | μΑ   |

| 41+               | One input at 3.4 V,                                         | 5.5 V | T                     |         |      |           |      | . 1          | mA   |

| ΔICC <sup>‡</sup> | Other inputs at GND or VCC                                  |       |                       | 0.9     |      | 1         |      |              |      |

| Ci                | V <sub>1</sub> = V <sub>CC</sub> or GND                     | 5 V   | 1                     | 3.5     |      |           | -    |              | pF   |

<sup>†</sup> Not more than one output should be tested at one time, and the duration of the test should not exceed 10 ms.

PRODUCT PREVIEW

2-181

<sup>\*</sup> This is the increase in supply current for each input that is at one of the specified TTL voltage levels rather than 0 V to VCC.