# **Balanced Modulators/ Demodulators**

These devices were designed for use where the output voltage is a product of an input voltage (signal) and a switching function (carrier). Typical applications include suppressed carrier and amplitude modulation, synchronous detection, FM detection, phase detection, and chopper applications. See ON Semiconductor Application Note AN531 for additional design information.

# Features

- Excellent Carrier Suppression -65 dB typ @ 0.5 MHz

- -50 dB typ @ 10 MHz

- Adjustable Gain and Signal Handling

- Balanced Inputs and Outputs

- High Common Mode Rejection -85 dB Typical

- This Device Contains 8 Active Transistors

- Pb-Free Package is Available\*

# **ON Semiconductor®**

http://onsemi.com

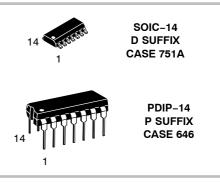

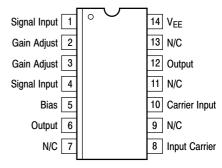

# **PIN CONNECTIONS**

# **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 12 of this data sheet.

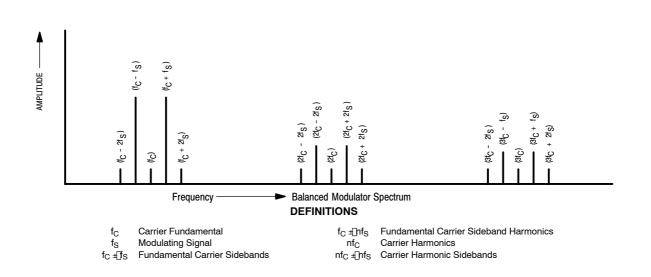

# **DEVICE MARKING INFORMATION**

See general marking information in the device marking section on page 12 of this data sheet.

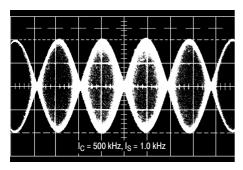

Figure 1. Suppressed Carrier Output Waveform

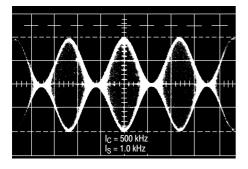

Figure 3. Amplitude Modulation Output Waveform

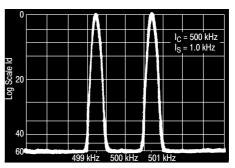

Figure 2. Suppressed Carrier Spectrum

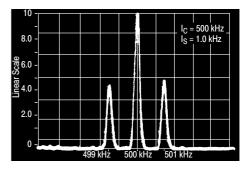

Figure 4. Amplitude-Modulation Spectrum

| <b>MAXIMUM RATINGS</b> ( $T_A = 25^{\circ}C$ , unless otherwise noted.)                         |                     |                                |      |  |  |

|-------------------------------------------------------------------------------------------------|---------------------|--------------------------------|------|--|--|

| Rating                                                                                          | Symbol              | Value                          | Unit |  |  |

| Applied Voltage<br>(V6-V8, V10-V1, V12-V8, V12-V10, V8-V4, V8-V1, V10-V4, V6-V10, V2-V5, V3-V5) | ΔV                  | 30                             | Vdc  |  |  |

| Differential Input Signal                                                                       | V8 – V10<br>V4 – V1 | +5.0<br>±(5+I5R <sub>e</sub> ) | Vdc  |  |  |

| Maximum Bias Current                                                                            | I <sub>5</sub>      | 10                             | mA   |  |  |

| Thermal Resistance, Junction-to-Air<br>Plastic Dual In-Line Package                             | $R_{	hetaJA}$       | 100                            | °C/W |  |  |

| Operating Ambient Temperature Range MC1496<br>MC1496B                                           | T <sub>A</sub>      | 0 to +70<br>-40 to +125        | °C   |  |  |

| Storage Temperature Range                                                                       | T <sub>stg</sub>    | -65 to +150                    | °C   |  |  |

| Electrostatic Discharge Sensitivity (ESD)<br>Human Body Model (HBM)<br>Machine Model (MM)       | ESD                 | 2000<br>400                    | V    |  |  |

# Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

| <b>ELECTRICAL CHARACTERISTICS</b> (V <sub>CC</sub> = 12 Vdc, V <sub>EE</sub> = $-8.0$ Vdc, I5 = $1.0$ mAdc, R <sub>L</sub> = $3.9$ k $\Omega$ , R <sub>e</sub> = $1.0$ k $\Omega$ , T <sub>A</sub> = T <sub>low</sub> to T <sub>high</sub> , |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| all input and output characteristics are single-ended, unless otherwise noted.) (Note 1)                                                                                                                                                     |

| Characteristic                                                                                                                                                                                                                                                                   | Fig. | Note | Symbol                                    | Min              | Тур                     | Max                  | Unit           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------------------------------------------|------------------|-------------------------|----------------------|----------------|

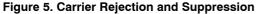

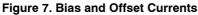

| $ \begin{array}{lll} Carrier Feedthrough & & f_C = 1.0 \ \text{kHz} \\ offset adjusted to zero & f_C = 10 \ \text{MHz} \\ V_C = 300 \ \text{mVpp square wave:} \\ offset adjusted to zero & f_C = 1.0 \ \text{kHz} \\ offset not adjusted & f_C = 1.0 \ \text{kHz} \end{array} $ | 5    | 1    | V <sub>CFT</sub>                          | _<br>_<br>_<br>_ | 40<br>140<br>0.04<br>20 | -<br>-<br>0.4<br>200 | μVrms<br>mVrms |

| Carrier Suppression                                                                                                                                                                                                                                                              | 5    | 2    | V <sub>CS</sub>                           |                  |                         |                      | dB             |

| $f_S = 10 \text{ kHz}$ , 300 mVrms<br>$f_C = 500 \text{ kHz}$ , 60 mVrms sine wave<br>$f_C = 10 \text{ MHz}$ , 60 mVrms sine wave                                                                                                                                                | 0    | _    | · CS                                      | 40<br>-          | 65<br>50                |                      | k              |

| Transadmittance Bandwidth (Magnitude) ( $R_L = 50 \Omega$ )<br>Carrier Input Port, $V_C = 60 \text{ mVrms}$ sine wave<br>$f_S = 1.0 \text{ kHz}$ , 300 mVrms sine wave<br>Signal Input Port, $V_S = 300 \text{ mVrms}$ sine wave                                                 | 8    | 8    | BW <sub>3dB</sub>                         | _                | 300<br>80               | -                    | MHz            |

| $ V_C  = 0.5 \text{ Vdc}$<br>Signal Gain (V <sub>S</sub> = 100 mVrms, f = 1.0 kHz;  V <sub>C</sub>  = 0.5 Vdc)                                                                                                                                                                   | 10   | 3    | A <sub>VS</sub>                           | 2.5              | 3.5                     | _                    | V/V            |

| Single-Ended Input Impedance, Signal Port, f = 5.0 MHz                                                                                                                                                                                                                           | 6    | -    | 7475                                      | 2.0              | 0.0                     |                      | •,•            |

| Parallel Input Resistance<br>Parallel Input Capacitance                                                                                                                                                                                                                          | 0    |      | r <sub>ip</sub><br>C <sub>ip</sub>        |                  | 200<br>2.0              | -                    | kΩ<br>pF       |

| Single-Ended Output Impedance, f = 10 MHz<br>Parallel Output Resistance<br>Parallel Output Capacitance                                                                                                                                                                           | 6    | -    | r <sub>op</sub><br>c <sub>oo</sub>        |                  | 40<br>5.0               |                      | kΩ<br>pF       |

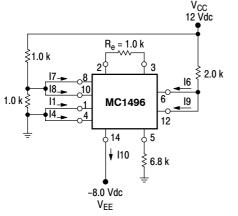

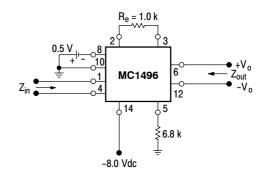

| Input Bias Current<br>$I_{bS} = \frac{I1 + I4}{2}; I_{bC} = \frac{I8 + I10}{2}$                                                                                                                                                                                                  | 7    | -    | I <sub>bS</sub><br>I <sub>bC</sub>        |                  | 12<br>12                | 30<br>30             | μΑ             |

| Input Offset Current<br>I <sub>ioS</sub> = I1–I4; I <sub>ioC</sub> = I8–I10                                                                                                                                                                                                      | 7    | -    | ∣I <sub>ioS</sub> ∣<br>I <sub>ioC</sub> ∣ |                  | 0.7<br>0.7              | 7.0<br>7.0           | μΑ             |

| Average Temperature Coefficient of Input Offset Current $(T_A = -55^{\circ}C \text{ to } +125^{\circ}C)$                                                                                                                                                                         |      | -    | TC <sub>lio</sub>                         | -                | 2.0                     | -                    | nA/°C          |

| Output Offset Current (I6–I9)                                                                                                                                                                                                                                                    | 7    | -    | I <sub>oo</sub>                           | -                | 14                      | 80                   | μΑ             |

| Average Temperature Coefficient of Output Offset Current<br>( $T_A = -55^{\circ}C$ to +125°C)                                                                                                                                                                                    |      | -    | TC <sub>loo</sub>                         | -                | 90                      | -                    | nA/°C          |

| Common-Mode Input Swing, Signal Port, f <sub>S</sub> = 1.0 kHz                                                                                                                                                                                                                   |      | 4    | CMV                                       | -                | 5.0                     | -                    | Vpp            |

| Common–Mode Gain, Signal Port, $f_S = 1.0 \text{ kHz}$ , $ V_C = 0.5 \text{ Vdc}$                                                                                                                                                                                                |      | -    | ACM                                       | -                | -85                     | -                    | dB             |

| Common-Mode Quiescent Output Voltage (Pin 6 or Pin 9)                                                                                                                                                                                                                            |      | -    | V <sub>out</sub>                          | -                | 8.0                     | -                    | Vpp            |

| Differential Output Voltage Swing Capability                                                                                                                                                                                                                                     |      | -    | V <sub>out</sub>                          | -                | 8.0                     | -                    | Vpp            |

| Power Supply Current I6 +I12<br>I14                                                                                                                                                                                                                                              |      | 6    | I <sub>CC</sub><br>I <sub>EE</sub>        | _<br>_           | 2.0<br>3.0              | 4.0<br>5.0           | mAdc           |

| DC Power Dissipation                                                                                                                                                                                                                                                             | 7    | 5    | PD                                        | -                | 33                      | -                    | mW             |

1.  $T_{low} = 0^{\circ}C$  for MC1496  $T_{high} = +70^{\circ}C$  for MC1496  $= +125^{\circ}C$  for MC1496B

# **GENERAL OPERATING INFORMATION**

# **Carrier Feedthrough**

Carrier feedthrough is defined as the output voltage at carrier frequency with only the carrier applied (signal voltage = 0).

Carrier null is achieved by balancing the currents in the differential amplifier by means of a bias trim potentiometer (R1 of Figure 5).

# **Carrier Suppression**

Carrier suppression is defined as the ratio of each sideband output to carrier output for the carrier and signal voltage levels specified.

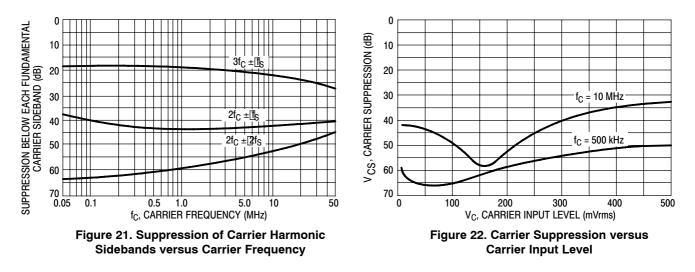

Carrier suppression is very dependent on carrier input level, as shown in Figure 22. A low value of the carrier does not fully switch the upper switching devices, and results in lower signal gain, hence lower carrier suppression. A higher than optimum carrier level results in unnecessary device and circuit carrier feedthrough, which again degenerates the suppression figure. The MC1496 has been characterized with a 60 mVrms sinewave carrier input signal. This level provides optimum carrier suppression at carrier frequencies in the vicinity of 500 kHz, and is generally recommended for balanced modulator applications.

Carrier feedthrough is independent of signal level,  $V_S$ . Thus carrier suppression can be maximized by operating with large signal levels. However, a linear operating mode must be maintained in the signal-input transistor pair  $-[] \phi r$ harmonics of the modulating signal will be generated and appear in the device output as spurious sidebands of the suppressed carrier. This requirement places an upper limit on input-signal amplitude (see Figure 20). Note also that an optimum carrier level is recommended in Figure 22 for good carrier suppression and minimum spurious sideband generation.

At higher frequencies circuit layout is very important in order to minimize carrier feedthrough. Shielding may be necessary in order to prevent capacitive coupling between the carrier input leads and the output leads.

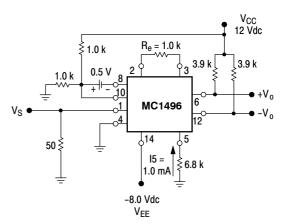

# Signal Gain and Maximum Input Level

Signal gain (single-ended) at low frequencies is defined as the voltage gain,

$$A_{VS} = \frac{V_o}{V_S} = \frac{R_L}{R_e + 2r_e} \text{ where } r_e = \frac{26 \text{ mV}}{15(\text{mA})}$$

A constant dc potential is applied to the carrier input terminals to fully switch two of the upper transistors "on" and two transistors "off" ( $V_C = 0.5$  Vdc). This in effect forms a cascode differential amplifier.

Linear operation requires that the signal input be below a critical value determined by  $R_E$  and the bias current I5.

$$V_S \leq I5 R_E$$

(Volts peak)

Note that in the test circuit of Figure 10,  $V_S$  corresponds to a maximum value of 1.0 V peak.

# **Common Mode Swing**

The common-mode swing is the voltage which may be applied to both bases of the signal differential amplifier, without saturating the current sources or without saturating the differential amplifier itself by swinging it into the upper switching devices. This swing is variable depending on the particular circuit and biasing conditions chosen.

# **Power Dissipation**

Power dissipation,  $P_D$ , within the integrated circuit package should be calculated as the summation of the voltage-current products at each port, i.e. assuming V12 = V6, I5 = I6 = I12 and ignoring base current,  $P_D = 2$  I5 (V6 - V14) + I5)V5 - V14 where subscripts refer to pin numbers.

# **Design Equations**

The following is a partial list of design equations needed to operate the circuit with other supply voltages and input conditions.

# A. Operating Current

The internal bias currents are set by the conditions at Pin 5. Assume:

$$I5 = I6 = I12,$$

$I_B < < I_C$  for all transistors

then :

$$R5 = \frac{V - -\varphi}{I5} - 500 \ \Omega \qquad \mbox{where:} R5 \ \mbox{is the resistor between} \\ Pin \ 5 \ \mbox{and ground} \\ \varphi = 0.75 \ \mbox{at} \ T_A = +25^{\circ}C$$

The MC1496 has been characterized for the condition  $I_5 = 1.0$  mA and is the generally recommended value.

B. Common–Mode Quiescent Output Voltage V6 = V12 = V+ – I5 R<sub>I</sub>

# Biasing

The MC1496 requires three dc bias voltage levels which must be set externally. Guidelines for setting up these three levels include maintaining at least 2.0 V collector–base bias on all transistors while not exceeding the voltages given in the absolute maximum rating table;

$$\begin{array}{l} 30 \ \text{Vdc} \geq [(\text{V6}, \text{V12}) - (\text{V8}, \text{V10})] \geq \fbox{2} \ \text{Vdc} \\ 30 \ \text{Vdc} \geq [(\text{V8}, \text{V10}) - (\text{V1}, \text{V4})] \geq \fbox{2}.7 \ \text{Vdc} \\ 30 \ \text{Vdc} \geq [(\text{V1}, \text{V4}) - (\text{V5})] \geq \fbox{2}.7 \ \text{Vdc} \end{array}$$

The foregoing conditions are based on the following approximations:

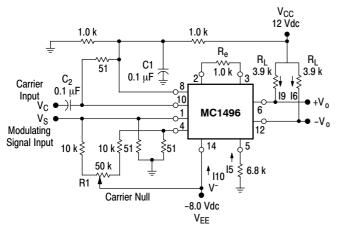

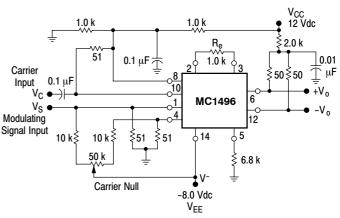

**TEST CIRCUITS**

Bias currents flowing into Pins 1, 4, 8 and 10 are transistor base currents and can normally be neglected if external bias dividers are designed to carry 1.0 mA or more.

# **Transadmittance Bandwidth**

Carrier transadmittance bandwidth is the 3.0 dB bandwidth of the device forward transadmittance as defined by:

$$v_{21C} = \frac{i_0 \text{ (each sideband)}}{v_s \text{ (signal)}} \quad V_0 = 0$$

Signal transadmittance bandwidth is the 3.0 dB bandwidth of the device forward transadmittance as defined by:

$$V_{21S} = \frac{i_0 \text{ (signal)}}{v_s \text{ (signal)}} V_c = 0.5 \text{ Vdc}, V_0 = 0$$

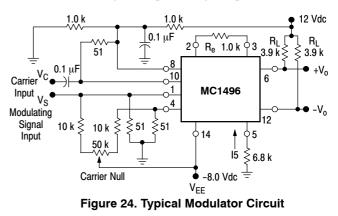

#### **Coupling and Bypass Capacitors**

Capacitors C1 and C2 (Figure 5) should be selected for a reactance of less than 5.0  $\Omega$  at the carrier frequency.

# **Output Signal**

,

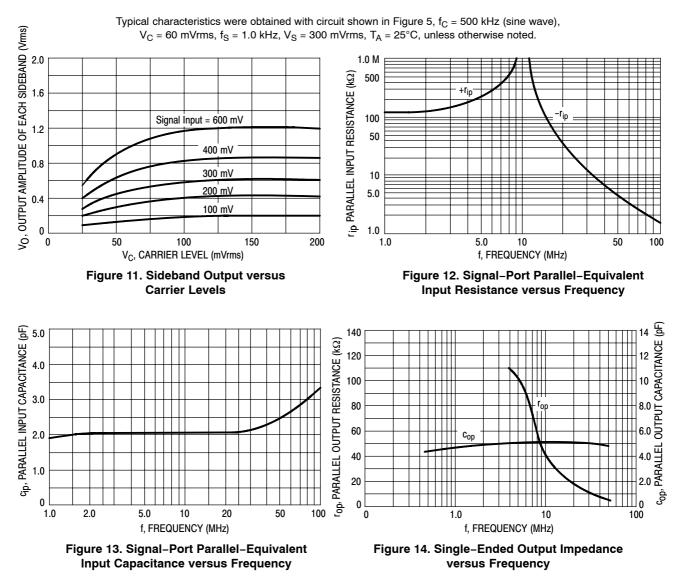

The output signal is taken from Pins 6 and 12 either balanced or single–ended. Figure 11 shows the output levels of each of the two output sidebands resulting from variations in both the carrier and modulating signal inputs with a single–ended output connection.

#### **Negative Supply**

$V_{EE}$  should be dc only. The insertion of an RF choke in series with  $V_{EE}$  can enhance the stability of the internal current sources.

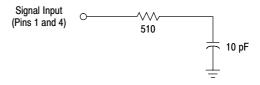

# **Signal Port Stability**

Under certain values of driving source impedance, oscillation may occur. In this event, an RC suppression network should be connected directly to each input using short leads. This will reduce the Q of the source-tuned circuits that cause the oscillation.

An alternate method for low-frequency applications is to insert a 1.0 k $\Omega$  resistor in series with the input (Pins 1, 4). In this case input current drift may cause serious degradation of carrier suppression.

**NOTE:** Shielding of input and output leads may be needed to properly perform these tests.

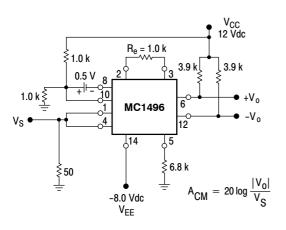

#### Figure 6. Input–Output Impedance

Figure 8. Transconductance Bandwidth

Figure 9. Common Mode Gain

Figure 10. Signal Gain and Output Swing

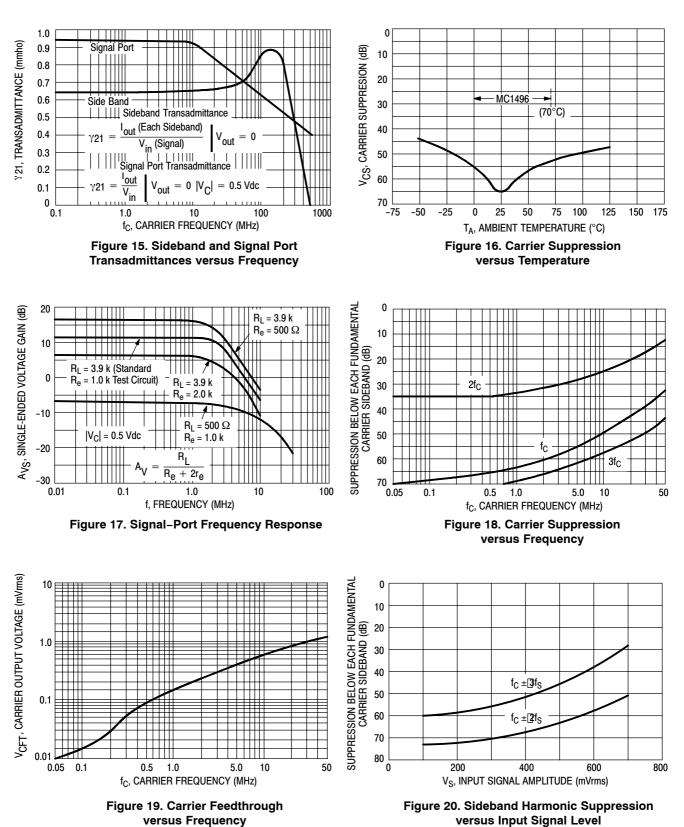

# **TYPICAL CHARACTERISTICS**

# TYPICAL CHARACTERISTICS (continued)

Typical characteristics were obtained with circuit shown in Figure 5,  $f_C$  = 500 kHz (sine wave),  $V_C$  = 60 mVrms,  $f_S$  = 1.0 kHz,  $V_S$  = 300 mVrms,  $T_A$  = 25°C, unless otherwise noted.

# **OPERATIONS INFORMATION**

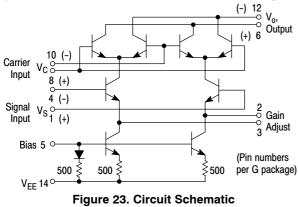

The MC1496, a monolithic balanced modulator circuit, is shown in Figure 23.

This circuit consists of an upper quad differential amplifier driven by a standard differential amplifier with dual current sources. The output collectors are cross-coupled so that full-wave balanced multiplication of the two input voltages occurs. That is, the output signal is a constant times the product of the two input signals.

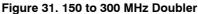

Mathematical analysis of linear ac signal multiplication indicates that the output spectrum will consist of only the sum and difference of the two input frequencies. Thus, the device may be used as a balanced modulator, doubly balanced mixer, product detector, frequency doubler, and other applications requiring these particular output signal characteristics.

The lower differential amplifier has its emitters connected to the package pins so that an external emitter resistance may be used. Also, external load resistors are employed at the device output.

# **Signal Levels**

The upper quad differential amplifier may be operated either in a linear or a saturated mode. The lower differential amplifier is operated in a linear mode for most applications.

For low-level operation at both input ports, the output signal will contain sum and difference frequency

components and have an amplitude which is a function of the product of the input signal amplitudes.

For high-level operation at the carrier input port and linear operation at the modulating signal port, the output signal will contain sum and difference frequency components of the modulating signal frequency and the fundamental and odd harmonics of the carrier frequency. The output amplitude will be a constant times the modulating signal amplitude. Any amplitude variations in the carrier signal will not appear in the output.

The linear signal handling capabilities of a differential amplifier are well defined. With no emitter degeneration, the maximum input voltage for linear operation is approximately 25 mV peak. Since the upper differential amplifier has its emitters internally connected, this voltage applies to the carrier input port for all conditions.

Since the lower differential amplifier has provisions for an external emitter resistance, its linear signal handling range may be adjusted by the user. The maximum input voltage for linear operation may be approximated from the following expression:

#### $V = (I5) (R_E)$ volts peak.

This expression may be used to compute the minimum value of  $R_E$  for a given input voltage amplitude.

| Carrier Input Signal (V <sub>C</sub> ) | Approximate Voltage Gain                                                          | Output Signal Frequency(s)                                                              |

|----------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Low-level dc                           | $\frac{R_{L}V_{C}}{2(R_{E}+2r_{e})\left(\frac{KT}{q}\right)}$                     | f <sub>M</sub>                                                                          |

| High-level dc                          | $\frac{R_{L}}{R_{E} + 2r_{e}}$                                                    | f <sub>M</sub>                                                                          |

| Low-level ac                           | $\frac{R_{L} V_{C}(rms)}{2\sqrt{2}  \left(\frac{K T}{q}\right) (R_{E} + 2r_{e})}$ | $f_{\rm C} \pm \Xi_{\rm M}$                                                             |

| High-level ac                          | $\frac{0.637 \text{ R}_{\text{L}}}{\text{R}_{\text{E}} + 2\text{r}_{\text{e}}}$   | $f_{C} \pm \mathbb{I}_{M}, 3f_{C} \pm \mathbb{I}_{M}, 5f_{C} \pm \mathbb{I}_{M}, \dots$ |

#### Table 1. Voltage Gain and Output Frequencies

2. Low-level Modulating Signal, V<sub>M</sub>, assumed in all cases. V<sub>C</sub> is Carrier Input Voltage.

3. When the output signal contains multiple frequencies, the gain expression given is for the output amplitude ofeach of the two desired outputs,  $f_{C} + f_{M}$  and  $f_{C} - f_{M}$ .

4. All gain expressions are for a single-ended output. For a differential output connection, multiply each expression by two.

5. R<sub>L</sub> = Load resistance.

6.  $R_E = Emitter resistance between Pins 2 and 3.$

re  $\approx \frac{10 \text{ mV}}{\text{I}_5 \text{ (mA)}}$

8. K = Boltzmann's Constant, T = temperature in degrees Kelvin, q = the charge on an electron.

The gain from the modulating signal input port to the output is the MC1496 gain parameter which is most often of interest to the designer. This gain has significance only when the lower differential amplifier is operated in a linear mode, but this includes most applications of the device.

As previously mentioned, the upper quad differential amplifier may be operated either in a linear or a saturated mode. Approximate gain expressions have been developed for the MC1496 for a low-level modulating signal input and the following carrier input conditions:

1) Low-level dc

2) High-level dc

3) Low-level ac

4) High-level ac

These gains are summarized in Table 1, along with the frequency components contained in the output signal.

# **APPLICATIONS INFORMATION**

Double sideband suppressed carrier modulation is the basic application of the MC1496. The suggested circuit for this application is shown on the front page of this data sheet.

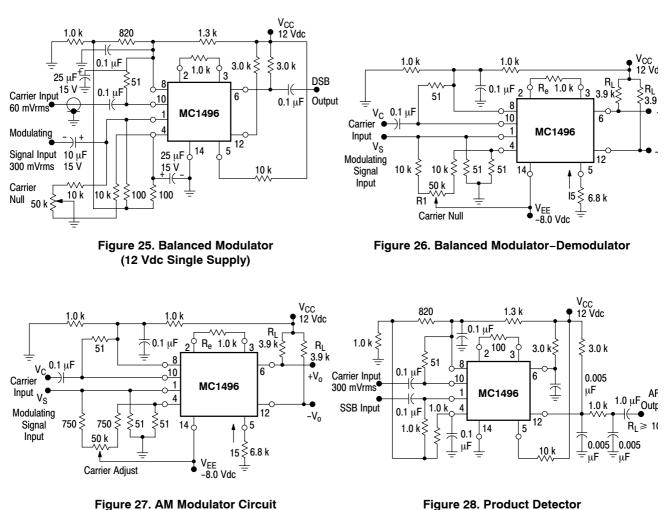

In some applications, it may be necessary to operate the MC1496 with a single dc supply voltage instead of dual supplies. Figure 25 shows a balanced modulator designed for operation with a single 12 Vdc supply. Performance of this circuit is similar to that of the dual supply modulator.

#### AM Modulator

The circuit shown in Figure 26 may be used as an amplitude modulator with a minor modification.

All that is required to shift from suppressed carrier to AM operation is to adjust the carrier null potentiometer for the proper amount of carrier insertion in the output signal.

However, the suppressed carrier null circuitry as shown in Figure 26 does not have sufficient adjustment range. Therefore, the modulator may be modified for AM operation by changing two resistor values in the null circuit as shown in Figure 27.

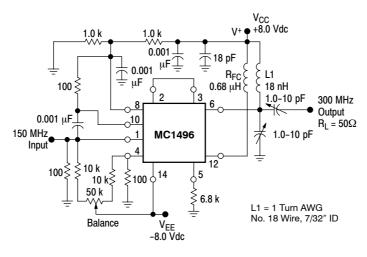

#### **Product Detector**

The MC1496 makes an excellent SSB product detector (see Figure 28).

This product detector has a sensitivity of  $3.0 \ \mu V$  and a dynamic range of 90 dB when operating at an intermediate frequency of 9.0 MHz.

The detector is broadband for the entire high frequency range. For operation at very low intermediate frequencies down to 50 kHz the 0.1  $\mu$ F capacitors on Pins 8 and 10 should be increased to 1.0  $\mu$ F. Also, the output filter at Pin 12 can be tailored to a specific intermediate frequency and audio amplifier input impedance.

As in all applications of the MC1496, the emitter resistance between Pins 2 and 3 may be increased or decreased to adjust circuit gain, sensitivity, and dynamic range.

This circuit may also be used as an AM detector by introducing carrier signal at the carrier input and an AM signal at the SSB input.

The carrier signal may be derived from the intermediate frequency signal or generated locally. The carrier signal may

be introduced with or without modulation, provided its level is sufficiently high to saturate the upper quad differential amplifier. If the carrier signal is modulated, a 300 mVrms input level is recommended.

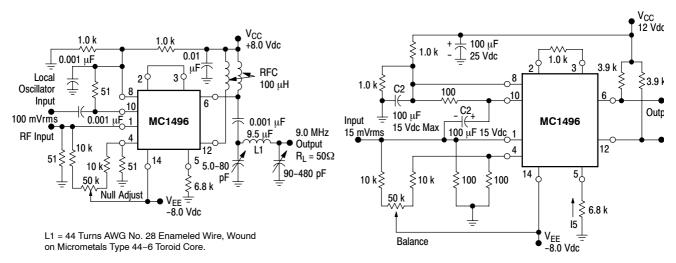

#### **Doubly Balanced Mixer**

The MC1496 may be used as a doubly balanced mixer with either broadband or tuned narrow band input and output networks.

The local oscillator signal is introduced at the carrier input port with a recommended amplitude of 100 mVrms.

Figure 29 shows a mixer with a broadband input and a tuned output.

#### **Frequency Doubler**

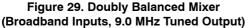

The MC1496 will operate as a frequency doubler by introducing the same frequency at both input ports.

Figures 30 and 31 show a broadband frequency doubler and a tuned output very high frequency (VHF) doubler, respectively.

#### **Phase Detection and FM Detection**

The MC1496 will function as a phase detector. High–level input signals are introduced at both inputs. When both inputs are at the same frequency the MC1496 will deliver an output which is a function of the phase difference between the two input signals.

An FM detector may be constructed by using the phase detector principle. A tuned circuit is added at one of the inputs to cause the two input signals to vary in phase as a function of frequency. The MC1496 will then provide an output which is a function of the input signal frequency.

(12 Vdc Single Supply)

# **TYPICAL APPLICATIONS**

# **ORDERING INFORMATION**

| Device      | Package              | Shipping <sup>†</sup> |  |

|-------------|----------------------|-----------------------|--|

| MC1496D     | SOIC-14              |                       |  |

| MC1496DG    | SOIC-14<br>(Pb-Free) | 55 Units/Rail         |  |

| MC1496DR2   | SOIC-14              |                       |  |

| MC1496DR2G  | SOIC-14<br>(Pb-Free) | 2500 Tape & Reel      |  |

| MC1496P     | PDIP-14              |                       |  |

| MC1496PG    | PDIP-14<br>(Pb-Free) |                       |  |

| MC1496P1    | PDIP-14              | 25 Units/Rail         |  |

| MC1496P1G   | PDIP-14<br>(Pb-Free) |                       |  |

| MC1496BD    | SOIC-14              |                       |  |

| MC1496BDG   | SOIC-14<br>(Pb-Free) | 55 Units/Rail         |  |

| MC1496BDR2  | SOIC-14              |                       |  |

| MC1496BDR2G | SOIC-14<br>(Pb-Free) | 2500 Tape & Reel      |  |

| MC1496BP    | PDIP-14              |                       |  |

| MC1496BPG   | PDIP-14<br>(Pb-Free) | 25 Units/Rail         |  |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

#### **MARKING DIAGRAMS**

# **PACKAGE DIMENSIONS**

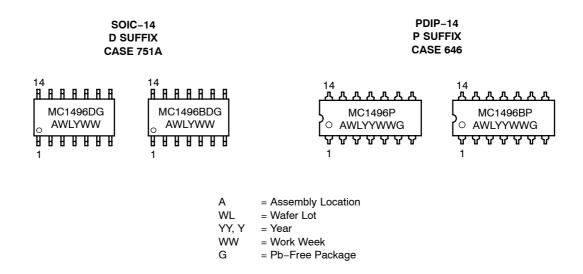

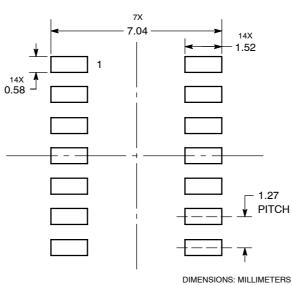

SOIC-14 CASE 751A-03 ISSUE H

- NOTES: 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. 2. CONTROLLING DIMENSION: MILLIMETER. 3. DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION. 4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) DEG SIDE

- MAXIMUM MOLD PROTRUSION 0.15 (0.0) PER SIDE.

DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |      | INCHES    |       |

|-----|-------------|------|-----------|-------|

| DIM | MIN         | MAX  | MIN       | MAX   |

| Α   | 8.55        | 8.75 | 0.337     | 0.344 |

| В   | 3.80        | 4.00 | 0.150     | 0.157 |

| С   | 1.35        | 1.75 | 0.054     | 0.068 |

| D   | 0.35        | 0.49 | 0.014     | 0.019 |

| F   | 0.40        | 1.25 | 0.016     | 0.049 |

| G   | 1.27 BSC    |      | 0.050 BSC |       |

| J   | 0.19        | 0.25 | 0.008     | 0.009 |

| к   | 0.10        | 0.25 | 0.004     | 0.009 |

| Μ   | 0 °         | 7 °  | 0 °       | 7 °   |

| Р   | 5.80        | 6.20 | 0.228     | 0.244 |

| R   | 0.25        | 0.50 | 0.010     | 0.019 |

# SOLDERING FOOTPRINT\*

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and

Mounting Techniques Reference Manual, SOLDERRM/D.

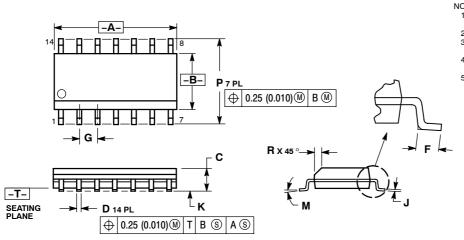

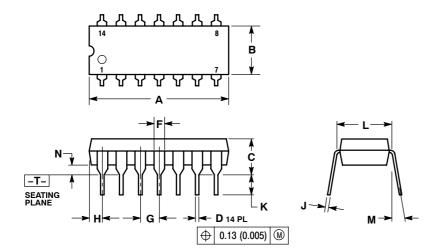

PDIP-14 CASE 646-06 ISSUE P

NOTES:

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: INCH.

- CONTROLLING DIMENSION: INCH.

DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL.

- PORIMED PARALLEL.

DIMENSION B DOES NOT INCLUDE MOLD FLASH.

ROUNDED CORNERS OPTIONAL.

|     | INCHES    |       | MILLIN   | IETERS |

|-----|-----------|-------|----------|--------|

| DIM | MIN       | MAX   | MIN      | MAX    |

| Α   | 0.715     | 0.770 | 18.16    | 19.56  |

| В   | 0.240     | 0.260 | 6.10     | 6.60   |

| С   | 0.145     | 0.185 | 3.69     | 4.69   |

| D   | 0.015     | 0.021 | 0.38     | 0.53   |

| F   | 0.040     | 0.070 | 1.02     | 1.78   |

| G   | 0.100 BSC |       | 2.54 BSC |        |

| н   | 0.052     | 0.095 | 1.32     | 2.41   |

| J   | 0.008     | 0.015 | 0.20     | 0.38   |

| ĸ   | 0.115     | 0.135 | 2.92     | 3.43   |

| L   | 0.290     | 0.310 | 7.37     | 7.87   |

| М   |           | 10 °  |          | 10 °   |

| Ν   | 0.015     | 0.039 | 0.38     | 1.01   |

ON Semiconductor and use registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use personal and solut to wars and is not for resale in any manner.

# PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Japan: ON Semiconductor, Japan Customer Focus Center 2–9–1 Kamimeguro, Meguro-ku, Tokyo, Japan 153–0051 Phone: 81–3–5773–3850 ON Semiconductor Website: http://onsemi.com

Order Literature: http://www.onsemi.com/litorder

For additional information, please contact your local Sales Representative.