|                                                                                                                                                                                                                                                                                                                                                              | REVISIONS                                                                 | •  |                 |                    |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----|-----------------|--------------------|--|--|--|--|

| LTR                                                                                                                                                                                                                                                                                                                                                          | DESCRIPTION                                                               |    | DATE (YR-MO-DA) | APPROVED           |  |  |  |  |

| B Change case 2 to case X. Changes to recommended operating conditions, table I, and table II. Convert to military drawing format. Editorial changes throughout. Add vendor CAGE 34649.                                                                                                                                                                      |                                                                           |    |                 |                    |  |  |  |  |

| C                                                                                                                                                                                                                                                                                                                                                            | Add device type 02. Change drawing CAGE code. Editori changes throughout. | al | 89 OCT 25       | Weekman<br>Weekman |  |  |  |  |

| D CLK rise time ( $t_{CH1CH2}$ ) device type 01 and 02 changed from 15 ns maximum to 10 ns maximum. CLK fall time ( $t_{CL2CL1}$ ) device type 01 and 02 changed from 15 ns maximum to 10 ns maximum. Table I: RD inactive to next address active ( $t_{RHAV}$ ) device type 02 changed from -45 ns minimum to -40 ns minimum. Editorial changes throughout. |                                                                           |    |                 |                    |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                              |                                                                           |    |                 |                    |  |  |  |  |

| CL                                                                                                                                                                                                                                                                                                                                                           | JRRENT CAGE CODE 67268                                                    |    |                 |                    |  |  |  |  |

| REV                                                                                                                                                                                                                                                                                                                                                          |                                                                           |    |                 |                    |  |  |  |  |

| SHEE                                                                                                                                                                                                                                                                                                                                                         | <del>,                                    </del>                          | 11 | 1               |                    |  |  |  |  |

SHEET 23 24 26 27 С С C **REV** C С С С С С С С D D **REV STATUS OF SHEETS** SHEET 8 9 10 PMIC N/A **DEFENSE ELECTRONICS SUPPLY CENTER** DAYTON, OHIO 45444 STANDARDIZED **MILITARY** MICROCIRCUITS, DIGITAL, CMOS, 16 BIT **DRAWING** MICROPROCESSOR, MONOLITHIC SILICON THIS DRAWING IS AVAILABLE CAGE CODE DRAWING APPROVAL DATE SIZE FOR USE BY ALL DEPARTMENTS 14933 AND AGENCIES OF THE Α 29 NOVEMBER 1984

DESC FORM 193-1

AMSC N/A

SEP 87

DEPARTMENT OF DEFENSE

REV

D

С

+ U.S. GOVERNMENT PRINTING OFFICE: 1987 - 748-129/60912

SHEET

1

С

С С C С

21

20

84052

D

**REVISION LEVEL**

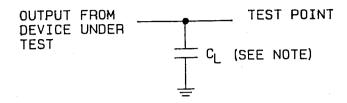

1/ These device design parameters were characterized using  $C_L = 100$  pF, clock rise/fall time are driven at 1 ns/V, and input rise/fall time are driven at 1 ns/V. 2/ Minimum and maximum mode.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br><b>A</b> |      |                 | 84052 |   |

|------------------------------------------------------|------------------|------|-----------------|-------|---|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 | -                | REVI | SION LEVEL<br>C | SHEET | 2 |

```

Data hold time after WR (t_{WHDX})

t_{CLCH} -30 ns minimum 1/3/

System design characteristics:

RDY setup time into clock generator (tRIVCL) - -

35 ns minimum 4/

RDY hold time into clock generator (t_{CLR1X}) - -

0 ns minimum 47

Command active delay (t<sub>CLML</sub>):

5 ns to 45 ns maximum

Device type 01 - - - - - - - -

Device type 02 - - - - - - -

5 ns to 35 ns maximum 5/

Command inactive delay (tclMH):

Device type 01 - - - - - -

5 ns to 45 ns maximum

Device type 02 - - - - - - -

5 ns to 35 ns maximum \frac{5}{}

Status valid to ALE high (t<sub>SVLH</sub>):

35 ns maximum

20 ns maximum

Status valid to MCE high (t<sub>SVMCH</sub>):

35 ns maximum

Device type 01 - - - - - - - - - -

30 ns maximum

Device type 02 - - - - - -

CLK low to MCE high (t<sub>CLMCH</sub>):

35 ns maximum 5/

25 ns maximum 5/

Control active delay (tcvny) - - - - - -

5 ns minimum to 45 ns maximum 5/

Control inactive delay (t_{CYNX}) - - - - -

5 ns minimum to 45 ns maximum 5/

Direction control active delay (t_{CHDTL}) - - -

50 ns maximum 5/

Direction control inactive delay (t<sub>CHDTH</sub>):

Device type 01 - - - - - - -

35 ns maximum 5/

Device type 02 - - - - - - - - - - - -

30 ns maximum 5/

CLK low to ALE valid (t<sub>CLLH</sub>) - - - - - - -

20 ns maximum 5/

ALE inactive delay (t<sub>CHLL</sub>):

4 ns minimum to 35 ns maximum

4 ns minimum to 25 ns maximum

CLK rise time (t<sub>CH1CH2</sub>):

Device type 01 - - - - - - - - -

10 ns maximum

Device type 02 - - - - - - - - - CLK fall time (tcL2cL1):

10 ns maximum

Device type 01 - - - - -

10 ns maximum

Device type 02 - - - - - - - - - - - - - - -

10 ns maximum

Input rise time (except CLK) (tILIH) - - - - - -

15 ns maximum

Input fall time (except CLK) (t_{IHIL}) - - - - - -

15 ns maximum

```

Minimum and maximum mode.

3/ Minimum complexity system timing responses.

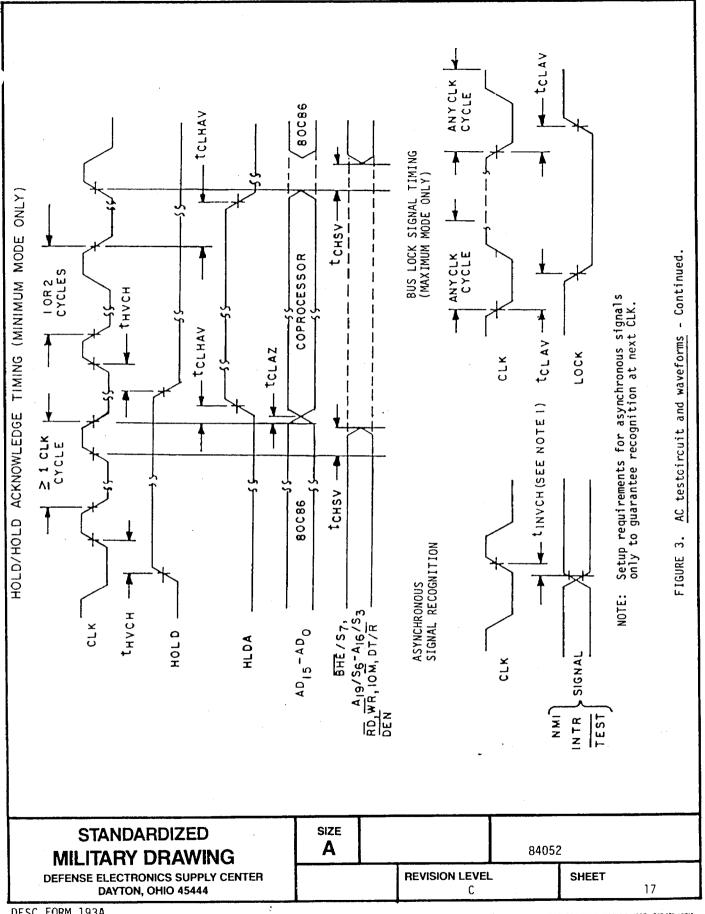

4/ Setup requirement for asynchronous signal only to guarantee recognition at next clock.

5/ Design reference limits when the device is used in conjunction with a bus controller in maximum mode.

| STANDARDIZED MILITARY DRAWING | SIZE<br><b>A</b> | 84052 |

|-------------------------------|------------------|-------|

|                               |                  |       |

DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444

|                | 84052 |   |  |

|----------------|-------|---|--|

| REVISION LEVEL | SHEET |   |  |

| D              |       | 3 |  |

<sup>1/</sup> These device design parameters were characterized using  $C_L = 100$  pF, clock rise/fall time are driven at 1 ns/V, and input rise/fall time are driven at 1 ns/V.

#### 2. APPLICABLE DOCUMENTS

2.1 Government specification, standard, and bulletin. Unless otherwise specified, the following specification, standard, and bulletin of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

**SPECIFICATION**

MILITARY

MIL-M-38510 - Microcircuits, General Specification for

STANDARD

MILITARY

MIL-STD-883 - Test Methods and Procedures for Microelectronics

BULLETIN

**MILITARY**

MIL-BUL-103 - List of Standardized Military Drawings (SMD's).

(Copies of the specification, standard, and bulletin required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

2.2 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

#### REQUIREMENTS

- 3.1 Item requirements. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein.

- 3.2 Design, construction, and physical dimensions. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 and herein.

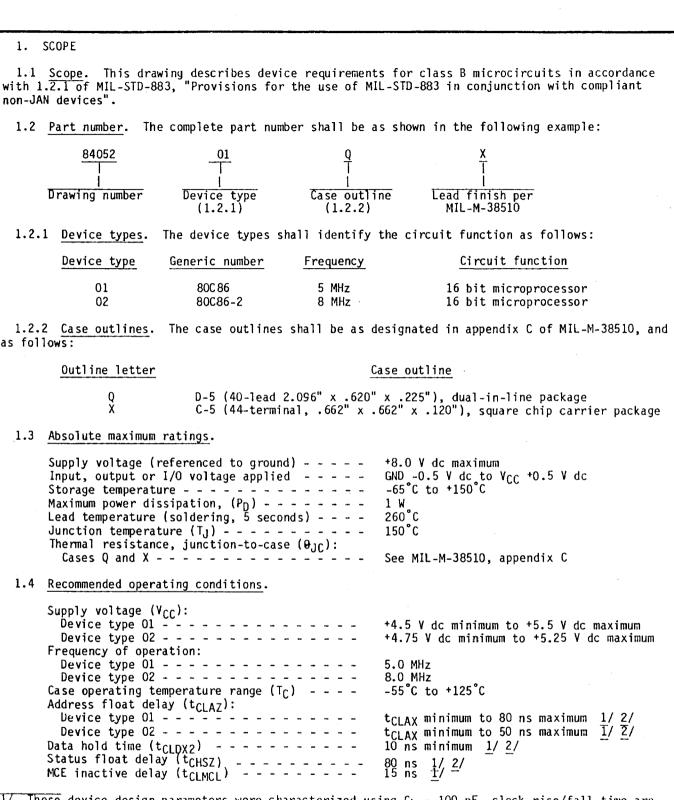

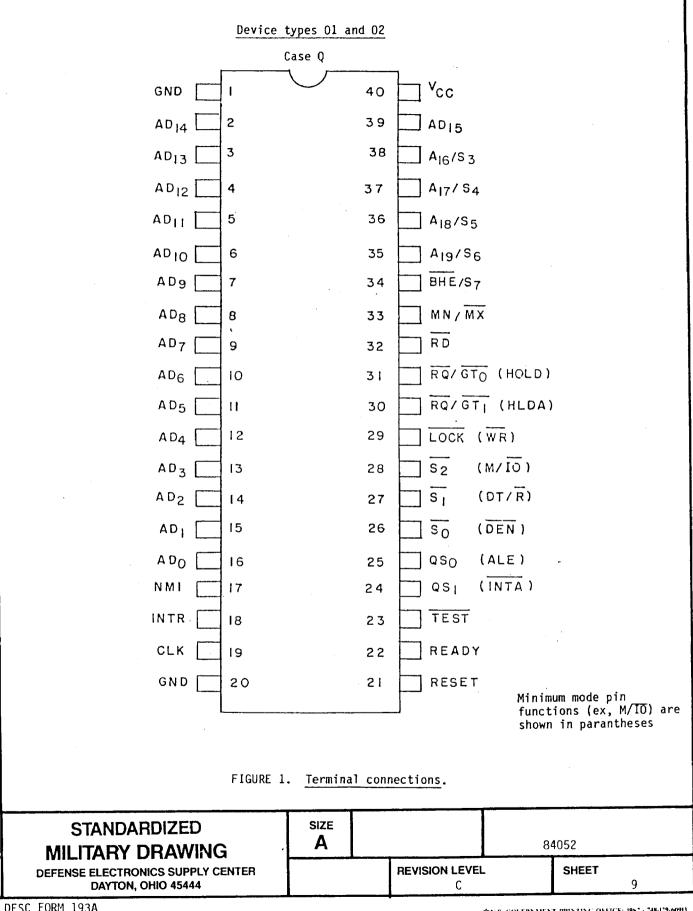

- 3.2.1 Terminal connections. The terminal connnections shall be as specified on figure 1.

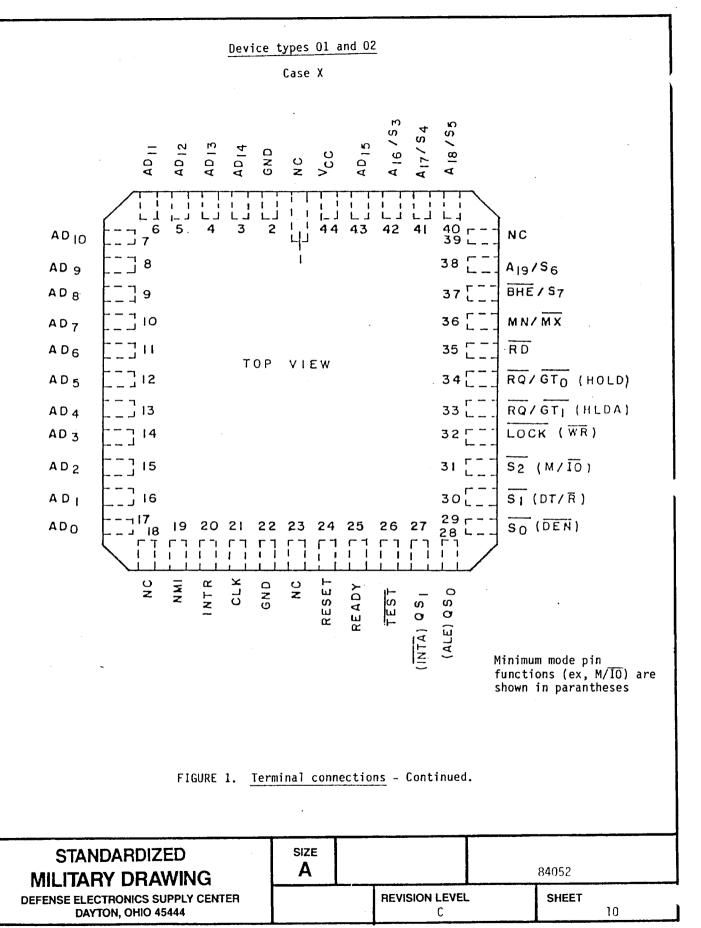

- 3.2.2 Functional diagram. The functional diagram shall be as specified on figure 2.

- 3.2.3 Case outlines. The case outlines shall be in accordance with 1.2.2 herein.

- 3.3 Electrical performance characteristics. Unless otherwise specified herein, the electrical performance characteristics are as specified in table I and shall apply over the full case operating temperature range.

- 3.4 Electrical test requirements. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are described in table I.

| STANDARDIZED<br>MILITARY DRAWING                        | SIZE<br><b>A</b> |                |   | 84052 |   |

|---------------------------------------------------------|------------------|----------------|---|-------|---|

| DEFENSE ELECTRONICS SUPPLY CENTER<br>DAYTON, OHIO 45444 |                  | REVISION LEVEL | • | SHEET | 4 |

| Parameter                                 | Symbol                                                         | Conditions                                                                                             | Group A   | Limits                  |                  | Unit                |

|-------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------|-------------------------|------------------|---------------------|

|                                           |                                                                | -55°C < T <sub>C</sub> < +125°C,<br>unless otherwise specified<br>V <sub>CC</sub> = minimum <u>1</u> / | subgroups |                         | Max              | .<br> <br>          |

| Clock input<br>low voltage                | V <sub>IL1</sub>                                               |                                                                                                        | 1, 2, 3   | <br> <br> <br>          | 0.8              | V                   |

| Clock input l<br>high voltage             | V <sub>IH1</sub>                                               | V <sub>CC</sub> = maximum                                                                              | 1, 2, 3   | V <sub>CC</sub>         |                  | <br>  V<br>         |

| Input low voltage                         | V <sub>IL2</sub>                                               | 2/                                                                                                     | 1, 2, 3   |                         | 0.8              | V                   |

| Input high voltage                        | V <sub>IH2</sub>                                               | $V_{CC} = \text{maximum}  2/$                                                                          | 1, 2, 3   | 2.2                     |                  | V                   |

| High level  <br>output voltage            | v <sub>OH</sub>                                                | I <sub>OH</sub> = -100 μA <u>3</u> /                                                                   | 1, 2, 3   | V <sub>CC</sub><br>-0.4 |                  | 1<br>1<br>1 V       |

|                                           |                                                                | $I_{OH} = -2.5 \text{ mA}  3/$                                                                         | 1, 2, 3   | 3.0                     |                  | <br>                |

| Low level<br>output voltage               | I<br>V <sub>OL</sub>                                           | $I_{OL} = 2.5 \text{ mA} \frac{3}{}$                                                                   | 1, 2, 3   | <br>                    | 0.4              | !<br>  V<br>!       |

| Input leakage<br>current                  | <br>  I <sub>I L</sub><br>                                     | V <sub>IN</sub> = 0 V or V <sub>CC</sub><br>  V <sub>CC</sub> = maximum                                | 1, 2, 3   | -1.0                    | 1.0              | <br>  μΑ<br>        |

| Input leakage<br>current-bus hold<br>high | <br>  IBHH<br>                                                 |                                                                                                        | 1, 2, 3   | -40<br>                 | - 400            | <br>  μΑ<br>        |

| Input leakage<br>current-bus hold<br>low  | <br> IBHL<br>                                                  | $V_{IN} = 0.8 V \frac{3}{5}$<br>$V_{CC} = minimum and maximum$                                         | 1, 2, 3   | <br>  +40<br>           | 400              | l<br>  μΑ<br>       |

| Output leakage current                    | 1 <sub>0</sub>                                                 | $V_0 = 0  V  V_{CC} = \text{maximum}$                                                                  | 1, 2, 3   |                         | -10.0            | <br>  μΑ<br>        |

| Standby power supply current              | ICCSB                                                          | V <sub>CC</sub> = maximum, V <sub>IN</sub> = V <sub>CC</sub> or GND <u>6</u> /<br> Outputs unloaded    | 1, 2, 3   |                         | 500              | <br>  μΑ<br>        |

| Operating power supply current            | ICCOP                                                          | V <sub>CC</sub> = 5.0 V, V <sub>IH</sub> = V <sub>CC</sub> ,                                           | 1, 2, 3   | <br> <br>               | 10               | <br> mA/MH<br> <br> |

| Pin capacitance                           | IC <sub>IN</sub> ,<br>IC <sub>I/O</sub> ,<br>IC <sub>OUT</sub> |                                                                                                        | 4         |                         | 25<br> <br> <br> | <br>  pF<br> <br>   |

| Functional tests<br>See footnotes at en   | l<br>l<br>nd of tab                                            | <br> See 4.3.1d<br> le.                                                                                | 7, 8      | <u> </u>                | İ<br>İ           | İ                   |

| STANDA                                    | ARDIZE                                                         |                                                                                                        | T         |                         |                  | <del>,</del>        |

| MILITARY                                  | DRAV                                                           | VING A                                                                                                 | <u> </u>  | 84052                   |                  |                     |

| MILITARY DEFENSE ELECTR               |                             |                                     |                                              | REVISION LE       | VEL                      | SHEE                                  |                |                 |

|---------------------------------------|-----------------------------|-------------------------------------|----------------------------------------------|-------------------|--------------------------|---------------------------------------|----------------|-----------------|

| STANDA                                |                             | _                                   | SIZE .                                       |                   |                          | 84052                                 | <b>)</b>       |                 |

| See footnotes at er                   | nd of tab                   | le.                                 |                                              |                   |                          | ··· · · · · · · · · · · · · · · · · · |                |                 |

| RD inactive delay                     | tCLRH                       |                                     | t                                            | 01 02             | 9, 10, 11                | 10<br>10                              | 150<br>80      | ns              |

| RD active delay                       | tCLRL                       |                                     |                                              | 01                | 9, 10, 11                | <br>  10<br>  10                      | 165<br>100     | ns              |

| Address float to<br>READ active       | tAZRL                       | <br> <br>                           |                                              | 01<br>02          | 9, 10, 11                | 0                                     | <br> <br>      | l ns            |

| Data valid delay                      | t <sub>CLDV</sub>           | <br> <br><u> </u>                   |                                              | 01                | 9, 10, 11                | 10                                    | 110            | l ns            |

| Address hold time                     | tCLAX                       |                                     |                                              | 01                | 9, 10, 11                | 10<br>10                              |                | l ns            |

| Address valid delay                   | tCLAV                       | <del> </del><br> <br>               |                                              | 01 02             | 9, 10, 11                | 10<br>10                              | 110            | ns              |

| INTR, NMI, TEST setup time <u>8</u> / | tINVCH                      | T<br> <br>                          |                                              | 01                | <br>  9, 10, 11<br>      | <br>  30<br>  15                      |                | l ns            |

| READY inactive<br>to CLK <u>7</u> /   | <br> t <sub>RYLCL</sub><br> | <br> <br> <br>                      |                                              | 01 02             | <br>  9, 10, 11<br> <br> | -5<br>  -5<br>                        | <br> <br> <br> | ns<br>ns        |

| READY hold time<br>into device        | tCHRYX                      | <br>                                |                                              | 01                | 9, 10, 11                | 30                                    | <br> <br>      | l ns            |

| READY setup time<br>into device       | t <sub>RYHCH</sub>          | T<br> <br>                          |                                              | 01                | 9, 10, 11                | <br>  118<br>  68                     |                | l<br>  ns       |

| Oata in hold time                     | t <sub>CLDX1</sub>          | T<br>!<br>!                         |                                              | 01<br>02          | <br>  9, 10, 11<br>      | l<br>  10<br>  10                     | 1<br>1<br>1    | l ns            |

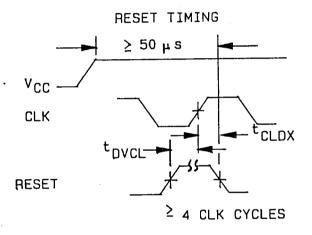

| ata in setup time                     | t <sub>DVCL</sub>           | T<br>!<br>!                         |                                              | <br>  01<br>  02  | 9, 10, 11                | <br>  30<br>  20                      | <br>           | l<br>l ns<br>l  |

| CLK high time                         | 1<br>1t <sub>CHCL</sub>     | Ť<br>!<br>!                         |                                              | 01                | 9, 10, 11                | 69<br>44                              | !<br>!         | l<br>i ns<br>l  |

| CLK low time                          | l<br>lt <sub>CLCH</sub>     | T<br>1                              |                                              | 1<br>1 01<br>1 02 | 9, 10, 11                | <br>  118<br>  68                     | <br> <br>      | l<br>l ns<br>l  |

| CLK Cycle period                      | lt <sub>CLCL</sub>          | <br> Minimum and m<br> See figure 3 | aximum mode                                  | 01                | 9, 10, 11                | 200<br>125                            |                | ns              |

| T d T dille be T                      |                             | -55°C < T<br>  unless othe          | $C \le +125$ °C, rwise specified inimum $1/$ | types             | subgroups                | Min                                   | Max            | Γ<br> <br> <br> |

| Parameter                             | <br> Symbol                 | Con                                 | ditions                                      |                   | Group A                  | Lim                                   | its            | <br>  Unit      |

| Parameter                             | Symbol                           | Conditions                                                                                     | Device             | Group A                  | Limi                                                             | its               | l Unit         |

|---------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------|--------------------|--------------------------|------------------------------------------------------------------|-------------------|----------------|

|                                       | <br> <br> <br>                   | -55°C < T <sub>C</sub> < +125°C,<br>unless otherwise specified<br>V <sub>CC</sub> = minimum 1/ | type<br> <br> <br> | subgroups                | Min                                                              | Max               | <br> <br> <br> |

| RD inactive to next<br>address active | <br> t <sub>RHAY</sub><br> <br>  | See figure 3<br> <br>                                                                          | 01                 | <br>  9, 10, 11<br> <br> | <br> t <sub>CLCL</sub><br>  -45  <br> t <sub>CLCL</sub><br>  -40 |                   | ns             |

| Output rise time                      | t <sub>OLOH</sub>                | <br> From 0.8 V to 2.0 V<br> See figure 3                                                      | 01 02              | 9, 10, 11                |                                                                  | 20<br>15          | ns             |

| Output fall time                      | t <sub>OHOL</sub>                | From 2.0 V to 0.8 V<br> See figure 3                                                           | 01 02              | 9, 10, 11                | <br> <br>                                                        | 20<br>15          | ns             |

| Status active delay                   | tchsv                            | See figure 3                                                                                   | 01 02              | 9, 10, 11                | 10<br>10                                                         | 110<br>60         | ns             |

| HOLD setup time                       | thvch                            | <br> Minimum mode<br> See figure 3<br>                                                         | 01 02              | 9, 10, 11                | 35                                                               |                   | ns             |

| ALE width                             | <br>  t <sub>LHLL</sub><br> <br> |                                                                                                | 01                 | 9, 10, 11                | t <sub>CLCH</sub><br>  -20<br>  t <sub>CLCH</sub><br>  -10       |                   | ns             |

| ALE active delay                      | t <sub>CLLH</sub>                | <u> </u>                                                                                       | 01 02              | 9, 10, 11                |                                                                  | 80<br>50          | l ns           |

| ALE inactive delay                    | t <sub>CHLL</sub>                | <br>                                                                                           | 01 02              | 9, 10, 11                |                                                                  | 85<br>55          | ns             |

| Address hold time<br>to ALE inactive  | <br> t <sub>LLAX</sub><br>       | <br>                                                                                           | 01                 | 9, 10, 11                | tcHCL<br>  -10<br>  tcHCL<br>  -10                               | <br> <br> <br>  · | ns             |

| Control active<br>delay 1             | t <sub>CVCTV</sub>               |                                                                                                | 01                 | 9, 10, 11                | 10                                                               | 110<br>70         | l ns           |

| Control active<br>delay 2             | l<br>I <sup>t</sup> снстv        | <br>                                                                                           | 01                 | 9, 10, 11                | <br>  10<br>  10                                                 | 110<br>60         | ns             |

| Control inactive<br>delay             | t <sub>CVCTX</sub>               | <br> <br>                                                                                      | 01 02              | 9, 10, 11                | 10                                                               | 110<br>70         | ns             |

| HLDA valid delay                      | l t <sub>CLHAV</sub>             | <br>                                                                                           | 01 02              | 9, 10, 11                | 10                                                               | 160<br>100        | ns             |

| RD width                              | I<br> t <sub>RLRH</sub><br>      | <br> <br>                                                                                      | 01                 | 9, 10, 11                | <br> 2t <sub>CLCL</sub><br>  -75<br> 2t <sub>CL</sub> CL         | <br> <br>         | ns             |

| See footnotes at en                   | l<br>d of tabl                   | <u>l</u>                                                                                       | 1                  | 1                        | -50°                                                             |                   | <u> </u>       |

| STANDA<br>MILITARY                    |                                  | l A i                                                                                          |                    |                          | 8405                                                             | 2                 |                |

|                                       |                    | Electrical performance chara                                    | T                         |                                   | Ţ <del></del>                                                  |                  |                        |

|---------------------------------------|--------------------|-----------------------------------------------------------------|---------------------------|-----------------------------------|----------------------------------------------------------------|------------------|------------------------|

| Parameter                             | Symbol             | Conditions $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | Device<br>  type<br> <br> | Group A<br>  subgroups  <br> <br> | Limi<br> <br>  Min  <br>                                       | Max              | Unit                   |

| WR width                              | twwwH              | Minimum mode<br> See figure 3                                   | 01 02                     | 9, 10, 11                         | 2t <sub>CLCL</sub><br>  -60<br>  2t <sub>CLCL</sub><br>  -40   |                  | ns                     |

| Address valid to<br>ALE low           | t <sub>AVAL</sub>  | T<br> <br>                                                      | 01 02                     | 9, 10, 11                         | <br> t <sub>CLCH</sub><br>  -60<br> t <sub>CLCH</sub><br>  -40 |                  | <br>  ns<br> <br>      |

| RQ/GT setup time                      | t <sub>GVCH</sub>  | <br> Maximum mode<br> See figure 3                              | 01 02                     | 9, 10, 11                         | <br>  30<br>  15                                               |                  | l ns                   |

| RQ hold time 9/<br>into device        | tcHGX              | T<br>!                                                          | 01 02                     | 9, 10, 11                         | <br>  40<br>  30                                               |                  | ns                     |

| Ready active to status passive 7/ 10/ | t <sub>RYHSH</sub> |                                                                 | 01 02                     | <br>  9, 10, 11<br>               | <br> <br> <br>                                                 | 110<br>65        | <br>  ns<br>           |

| Status inactive delay 10/             | t <sub>CLSH</sub>  | <del> </del><br> <br>                                           | 01 02                     | 9, 10, 11                         | <br>  10<br>  10                                               | 130<br>  70      | ns                     |

| GT active delay                       | tCLGL              | T<br> <br>                                                      | 01 02                     | 9, 10, 11                         | <br>  10<br>  0                                                | <br>  85<br>  50 | l ns                   |

| GT inactive delay                     | t <sub>CLGH</sub>  | T<br>                                                           | 01                        | 9, 10, 11                         | <br>  10<br>  0                                                | 85<br>50         | <br>  ns<br>           |

| RD width                              | t <sub>RLRH</sub>  |                                                                 | 01                        | 9, 10, 11                         | <br> 2tclcL<br>  -75<br> 2t <sub>CLCL</sub><br>  -50           | <br>             | <br>  ns<br> <br> <br> |

$V_{CC}$  minimum is 4.5 V for device type 01 and 4.75 V for device type 02.  $V_{CC}$  maximum is 5.5 V for device type 01 and 5.25 V for device type 02.

MN/MX pin is a strap option and should be held at  $V_{\rm CC}$  or GND. Interchanging of force and sense conditions permitted.

IBHH should be measured after raising  $V_{\rm IN}$  to  $V_{\rm CC}$  and then lowering to 3.0 V on the following pins: 2 through 16, 26 through 32, 34 through 39. IBHL should be measured after lowering  $V_{\rm IN}$  to GND and then raising to 0.8 V on the following pins: 2-16, 34-39.

ICCSB tested during clock high time after halt instruction executed. Outputs are unloaded.

Applies only to  $T_2$  state (8 ns into  $T_3$ ). Setup requirements for asynchronous signal only to guarantee recognition at next CLK. The device actively pulls the  $\overline{RQ/GT}$  pin to a logic one on the following clock low time.

TO/ Status lines return to their inactive (logic one) state after CLK goes low and READY goes high.

| STANDARDIZED<br>MILITARY DRAWING                     | SIZE<br><b>A</b> |                       |   | 84052 |   |

|------------------------------------------------------|------------------|-----------------------|---|-------|---|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | <b>REVISION LEVEL</b> | • | SHEET | 8 |

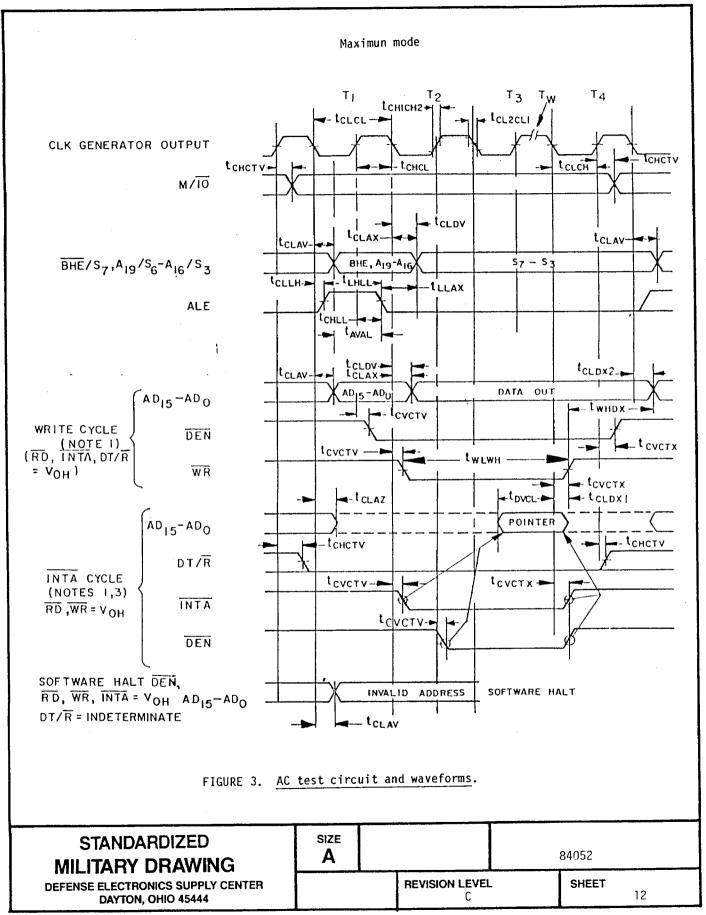

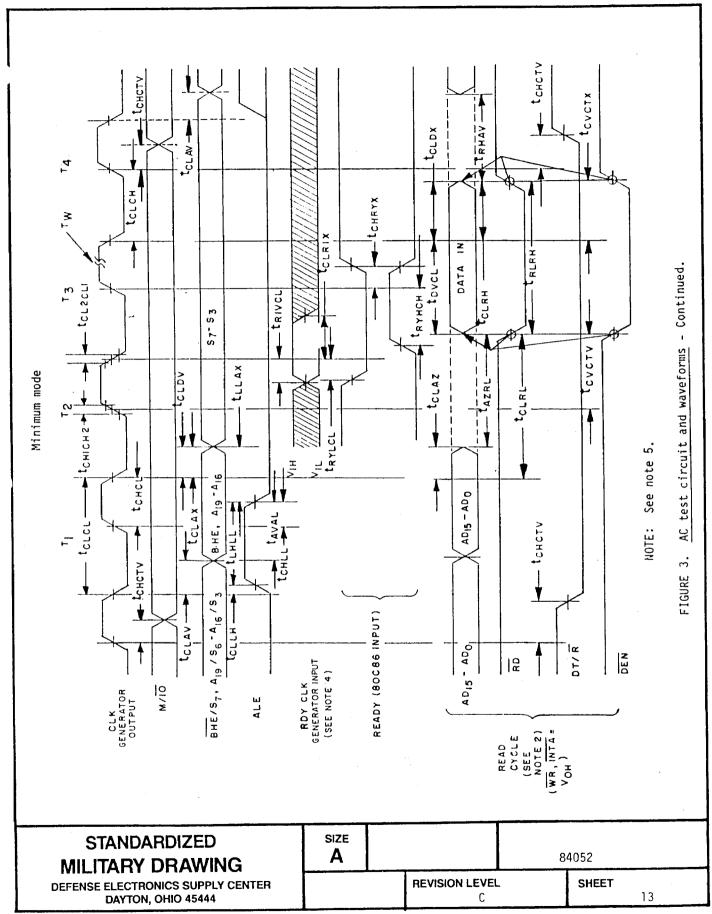

#### Minimum mode

#### NOTES:

- 1. All signals switch between  $V_{OH}$  and  $V_{OL}$  unless otherwise specified. 2. RDY is sampled near the end of  $T_2$ ,  $T_3$ , and  $T_W$  to determine if  $T_W$  machines

- states are to be inserted.

Two INTA cycles run back-to-back. The 80C86 local addr-data bus is floating during both INTA cycles. Control signals are shown for the second INTA cycle.

- Signals are shown for reference only.

- 5. All timing measurements are made at 1.5 V unless otherwise noted.

FIGURE 3. AC test circuit and waveforms - Continued.

**STANDARDIZED** SIZE Α 84052 **MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER REVISION LEVEL** SHEET **DAYTON, OHIO 45444** 14 С

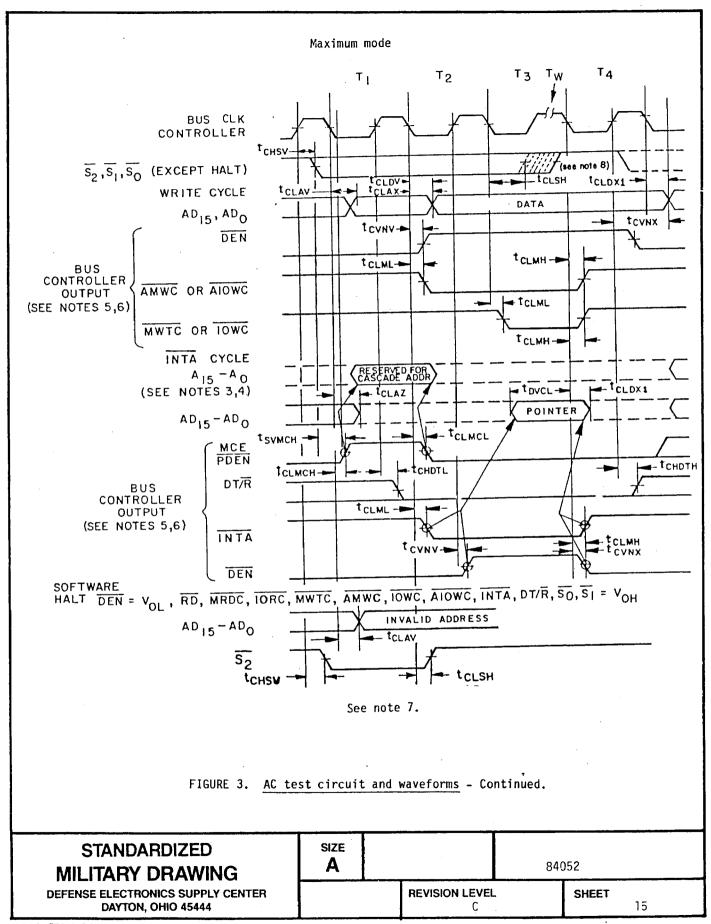

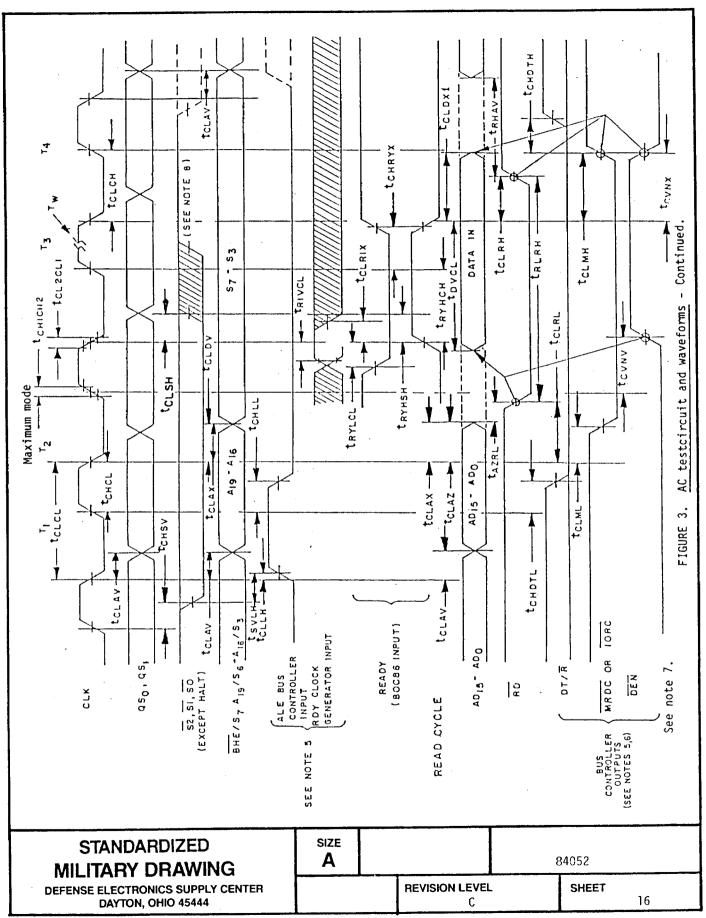

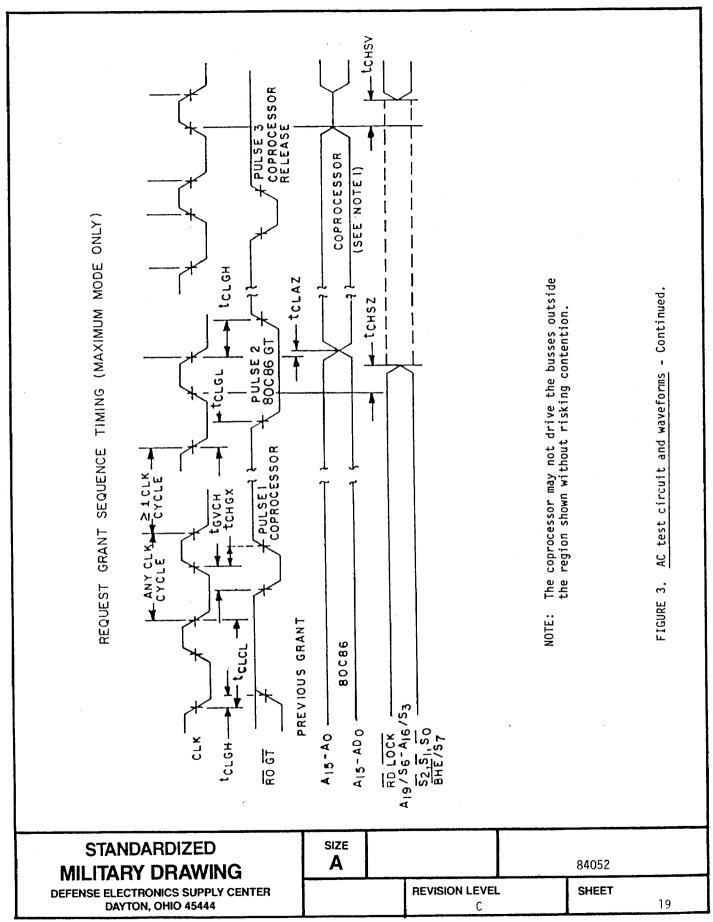

#### Maximum mode

#### NOTES:

All signals switch between  $V_{OH}$  and  $V_{OL}$  unless otherwise specified. RDY is sampled near the end of  $T_2$ ,  $T_3$ , and  $T_W$  to determine if  $T_W$  machines states are to be inserted.

Cascade address is valid between first and second INTA cycles.

Two INTA cycles run back-to-back. The 80C86 local addr-data bus is floating during both INTA cycles. Control signals are shown for the second INTA cycle.

5. Signals are shown for reference only.

- The issuance of the bus controlled command and control signals ( $\overline{MRDC}$ ,  $\overline{MWTC}$ ,  $\overline{AMWC}$ ,  $\overline{IOWC}$ ,  $\overline{AIOWC}$ ,  $\overline{INTA}$ , and  $\overline{DEN}$ ) as the active high bus controller CEN.

- 7. All timing measurements are made at 1.5  $\mbox{V}$  unless otherwise noted.

8. Status inactive in state just prior to T4.

FIGURE 3. AC test circuit and waveforms - Continued.

| } | STANDARDIZED                                         | SIZE |                |      |       |    |

|---|------------------------------------------------------|------|----------------|------|-------|----|

|   | MILITARY DRAWING                                     | Α    |                | 8405 | 2     |    |

| ١ | DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |      | REVISION LEVEL |      | SHEET | 18 |

NOTE:  $C_L = 100 \text{ pF}$  stray and jig capacitance

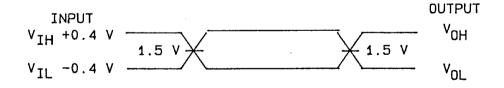

AC testing input, output waveform.

AC testing: All input signals (other than CLK) must switch between  $_{\rm VIL(max)}^{\rm ViL(max)}$  -0.4 V and VIH(min) +0.4 V. CLK must switch between 0.4 V and VCC -0.4 V.  $t_r$  and  $t_f$  are driven at 1 ns/V.

FIGURE 3. AC test circuit and waveforms - Continued.

## STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 SIZE A REVISION LEVEL C 20

- 3.5 Marking. Marking shall be in accordance with MIL-STD-883 (see 3.1 herein). The part shall be marked with the part number listed in 1.2 herein. In addition, the manufacturer's part number may also be marked as listed in MIL-BUL-103 (see 6.6 herein).

- 3.6 Certificate of compliance. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-BUL-103 (see 6.6 herein). The certificate of compliance submitted to DESC-ECC prior to listing as an approved source of supply shall affirm that the manufacturer's product meets the requirements of MIL-STD-883 (see 3.1 herein) and the requirements herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required in MIL-STD-883 (see 3.1 herein) shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 Notification of change. Notification of change to DESC-ECC shall be required in accordance with MIL-STD-883 (see 3.1 herein).

- 3.9 Verification and review. DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available on shore at the option of the reviewer.

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 Sampling and inspection. Sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein).

- 4.2 <u>Screening</u>. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition A, B, C, or D using the circuit submitted with the certificate of compliance (see 3.6 herein).

- (2)  $T_A = +125^{\circ}C$ , minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

- 4.3 Quality conformance inspection. Quality conformance inspection shall be in accordance with method  $\overline{5005}$  of MIL-STD-883 including groups A, B, C, and D inspections. The following additional criteria shall apply.

- 4.3.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. Subgroups 5 and 6 in table I, method 5005 of MIL-STD-883 shall be omitted.

- c. Subgroup 4 (C<sub>IN</sub>, C<sub>OUT</sub>, and C<sub>I/O</sub> measurements) shall be measured only for the initial test and after process or design changes which may affect capacitance. A minimum sample size of 5 devices with zero rejects shall be required.

- d. Subgroups 7 and 8 shall consist of verifying the functionality of the device. These tests form a part of the vendor's test tape and shall be maintained and available from approved source of supply.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br><b>A</b> |                | 84052    |

|------------------------------------------------------|------------------|----------------|----------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVEL | SHEET 21 |

#### TABLE II. Electrical test requirements.

| MIL-STD-883 test requirements                                          | Subgroups (per method<br>  5005, table I) |

|------------------------------------------------------------------------|-------------------------------------------|

| <br> Initial electrical parameters (method 5004)                       |                                           |

| <br> Final electrical test parameters (method 5004)                    | 1*,2,3,7,8,9,10,11                        |

| <br> Group A test requirements (method 5005)                           | 1,2,3,4,7,8,9,10,11                       |

| <br> Groups C and D end-point electrical parameters<br>  (method 5005) | <br>  2,8 (125°C),10                      |

<sup>\*</sup> PDA applies to subgroup 1.

#### 4.3.2 Groups C and D inspections.

- a. End-point electrical parameters shall be as specified in table II herein.

- b. Steady-state life test, method 1005 of MIL-STD-883 conditions.

- (1) Test condition A, B, C, or D using the circuit submitted with the certificate of compliance (see 3.6 herein).

- (2)  $T_A = +125^{\circ}C$ , minimum.

- (3) Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

#### PACKAGING

5.1 Packaging requirements. The requirements for packaging shall be in accordance with MIL-M-38510.

#### 6. NOTES

- 6.1 <u>Intended use.</u> Microcircuits conforming to this drawing are intended for use when military specifications do not exist and qualified military devices that will perform the required function are not available for OEM application. When a military specification exists and the product covered by this drawing has been qualified for listing on QPL-38510, the device specified herein will be inactivated and will not be used for new design. The QPL-38510 product shall be the preferred item for all applications.

- 6.2 Replaceability. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.3 Configuration control of SMD's. All proposed changes to existing SMD's will be coordinated with the users of record for the individual documents. This coordination will be accomplished in accordance with MIL-STD-481 using DD Form 1693, Engineering Change Proposal (Short Form).

- 6.4 Record of users. Military and industrial users shall inform Defense Electronics Supply Center when a system application requires configuration control and the applicable SMD. DESC will maintain a record of users and this list will be used for coordination and distribution of changes to the drawings. Users of drawings covering microelectronics devices (FSC 5962) should contact DESC-ECC, telephone (513) 296-6022.

- 6.5 Comments. Comments on this drawing should be directed to DESC-ECC, Dayton, Ohio 45444, or telephone (513) 296-8525.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br><b>A</b> |                | 84052    |

|------------------------------------------------------|------------------|----------------|----------|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVEL | SHEET 22 |

6.6 Symbols, definitions, and functional descriptions. The symbols, definitions, and functional description for this device shall be as follows:

Name and function (Minimum and maximum mode)

SYMBOL

$AD_{15} - AD_{0}$

ADDRESS DATA BUS: These lines constitute the time multiplexed memory/IO address ( $T_1$ ) and data ( $T_2$ ,  $T_3$ ,  $T_W$ ,  $T_4$ ) bus.  $A_0$  is analogous to BHE for the lower byte of the data bus, pins  $D_7$ - $D_0$ . It is LOW during  $T_1$  when a byte is to be transferred on the lower portion of the bus in memory or I/O operations. Eight-bit oriented devices tied to the lower half would normally use  $A_0$  to condition chip select functions (see BHE). These lines are active HIGH and are held at high impedance to the last valid logic level during interrupt acknowledge and local bus "hold acknowledge" or "grant sequence."

A<sub>19</sub>/S<sub>6</sub> A<sub>18</sub>/S<sub>5</sub> A<sub>17</sub>/S<sub>4</sub> A<sub>16</sub>/S<sub>3</sub> ADDRESS/STATUS: During  $T_1$ , these are the four most significant address lines for memory operations. During I/O operations these lines are LOW. During memory and I/O operations, status information is available on these lines during  $T_2$ ,  $T_3$ ,  $T_W$ , and  $T_4$ .  $S_6$  is always low. The status of the interrupt enable FLAG bit ( $S_5$ ) is updated at the beginning of each CLK cycle.  $S_4$  and  $S_3$  are encoded as follows:

| S <sub>4</sub>                                    | \$3 | Characteristics                                       |

|---------------------------------------------------|-----|-------------------------------------------------------|

| 0 (LOW) 0 1 1 (HIGH) 1 1S <sub>6</sub> is 0 (LOW) |     | Alternate data<br>  Stack<br>  Code or none<br>  Data |

This information indicates which segment register is presently being used for data accessing. These lines are held at high impedance to the last valid logic level during local bus "hold acknowledge" or "grant sequence".

BHE/S7

BUS HIGH ENABLE/STATUS: During  $T_1$  the bus high enable signal ( $\overline{BHE}$ ) should be used to enable data onto the most significant half of the data bus, pins  $D_{15}-D_8$ . Eight bit oriented devices tied to the upper half of the bus would normally use  $\overline{BHE}$  to condition chip select functions.  $\overline{BHE}$  is LOW during  $T_1$  for read, write, and interrupt acknowledge cycles when a byte is to be transferred on the high portion of the bus. The  $S_7$  status information is available during  $T_2$ ,  $T_3$ , and  $T_4$ . The signal is active LOW, and is held to high impedance to the last valid logic level during interrupt acknowledge and local bus "hold acknowledge". It is LOW during  $T_1$  for the first interrupt acknowledge cycle.

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

| SIZE<br><b>A</b> |                | 84052 |    |  |

|------------------|----------------|-------|----|--|

|                  | REVISION LEVEL | SHEET |    |  |

|                  | С              |       | 23 |  |

#### Name and function (Minimum and maximum mode)

SYMBOL

| BHE | A <sub>0</sub> | <br>  Characteristics<br>                                 |

|-----|----------------|-----------------------------------------------------------|

| 0   | 0 1            | Whole word   Upper byte from/                             |

| 1   | 0              | to odd address  <br>Lower byte from/  <br>to even address |

| j 1 | 1 1            | None                                                      |

RD

READ: Read strobe indicates that the processor is performing a memory or I/O read cycle, depending on the state of the  $\overline{S_2}$  or M/IO pin. This signal is used to read devices which reside on the microprocessor local bus. RD is active LOW during  $T_2$ ,  $T_3$ , and  $T_W$  of any read cycle, and remains HIGH in  $T_2$  until the microprocessor local bus has floated. This line is held at a high impedance logic one state during "hold acknowledge" or "grant sequence."

READY

READY: Is the acknowledgement from the addressed memory or I/O device that will complete the data transfer. The RDY signal from memory or I/O is synchronized by the Clock Generator to form READY. This signal is active HIGH. The microprocessor READY input is not synchronized. Correct operation is not guaranteed if the setup and hold times are not met.

INTR

INTERRUPT REQUEST: A level triggered input which is sampled during the last clock cycle of each instruction to determine if the processor should enter into an interrupt acknowledge operation. A subroutine is vectored to via an interrupt vector lookup table located in system memory. It can be internally masked by software resetting the interrupt enable bit. INTR is internally synchronized. This signal is active HIGH.

TEST

TEST: Input is examined by the "Wait" instruction. If the TEST input is LOW execution continues, otherwise the processor waits in an "Idle" state. This input is synchronized internally during each clock cycle on the leading edge of CLK.

NMI

NON-MASKABLE INTERRUPT: An edge triggered input which causes a type 2 interrupt. A subroutine is vectored to via an interrupt vector lookup table located in system memory. NMI is not maskable internally by software. A transition from a LOW to HIGH initiates the interrupt at the end of the current instruction. This input is internally synchronized.

RESET

RESET: Causes the processor to immediately terminate its present activity. The signal must transition LOW to HIGH and must remain active HIGH for at least four clock cycles. It restarts execution when RESET returns LOW. RESET is internally synchronized.

### STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER SIZE A 84052 REVISION LEVEL SHEET

DAYTON, OHIO 45444

24

| Name and function<br>(πinimum mode)<br>MN/MX = VCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                    |                                     |                           |                                                                    |                                                               |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------|--------------------------------------------------------------------|---------------------------------------------------------------|--|

| SYMBOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                    |                                     |                           |                                                                    |                                                               |  |

| CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CLOCK: Provides the basic timing for the processor and bus controller. It is asymmetric with a 33 percent duty cycle to provide optimized internal timing.                                                                                                                                                                                                                         |                                     |                           |                                                                    |                                                               |  |

| v <sub>cc</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $V_{CC}$ power supply pin. A 0.1 $_{\mu}F$ capacitor between pins 20 and 40 is recommended for decoupling. Reference pin numbers are for case Q. A 0.1 $_{\mu}F$ capacitor should be connected between pins 2z and 4a for case X.                                                                                                                                                  |                                     |                           |                                                                    |                                                               |  |

| GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | GND: Ground.                                                                                                                                                                                                                                                                                                                                                                       |                                     |                           |                                                                    |                                                               |  |

| MN/ <del>MX</del>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | MINIMUM/MAXIMUM: Indica                                                                                                                                                                                                                                                                                                                                                            | tes what n                          | node t                    | ne processor is to op                                              | erate in.                                                     |  |

| M/I0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | STATUS LINE: Logically equivalent to $\overline{S_2}$ in the maximum mode. It is used to distinguish a memory access from an I/O access. M/IO becomes valid in the T <sub>4</sub> preceding a bus cycle and remains valid until the final T <sub>4</sub> of the cycle (M = HIGH, IO = LOW). M/IO is held high impedance logic zero internally during local bus "hold acknowledge". |                                     |                           |                                                                    |                                                               |  |

| <b>ਅ</b> ਲ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | WRITE: Indicates that the processor is performing a write memory or write I/O cycle, depending on the state of the M/ $\overline{10}$ signal. $\overline{WR}$ is active for $T_2$ , $T_3$ , and $T_W$ of any write cycle. It is active LOW, and is held to high impedance logic one internally during local bus "hold acknowledge."                                                |                                     |                           |                                                                    |                                                               |  |

| TNTA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | INTERRUPT ACKNOWLEDGE: Is used as a read strobe for interrupt acknowledge cycles. It is active LOW during $T_2$ , $T_3$ , and $T_W$ of each interrupt acknowledge cycle. Note that INTA is never floated.                                                                                                                                                                          |                                     |                           |                                                                    |                                                               |  |

| ALE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ADDRESS LATCH ENABLE: Provided by the processor to latch the address into the external address latch. It is a HIGH pulse active during clock low of $T_1$ of any bus cycle. Note that ALE is never floated.                                                                                                                                                                        |                                     |                           |                                                                    |                                                               |  |

| DT/R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DATA TRANSMIT/RECEIVE: bus transceiver. It is transceiver. Logically, timing is the same as fo impedance logic one inte                                                                                                                                                                                                                                                            | used to co<br>DT/R is or<br>IO/M (T | ontrol<br>equiva<br>= HIG | the direction of dat lent to $S_1$ in maximum H, R = LOW). This si | a flow through the<br>mode, and its<br>gnal is held to a high |  |

| DEN DATA ENABLE: Is provided as an output enable for the bus transceiver in a minimum system which uses the transceiver. DEN is active LOW during each memory and I/O access, and for $\overline{\text{INTA}}$ cycles. For a read or $\overline{\text{INTA}}$ cycle, it is active from the middle of $T_2$ until the middle of $T_4$ , while for a write cycle, it is active from the beginning of $T_2$ until the middle of $T_4$ . DEN is held to high impedance logic one internally during local bus "hold acknowledge." |                                                                                                                                                                                                                                                                                                                                                                                    |                                     |                           |                                                                    |                                                               |  |

| STAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DARDIZED                                                                                                                                                                                                                                                                                                                                                                           | SIZE                                |                           |                                                                    |                                                               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | RY DRAWING                                                                                                                                                                                                                                                                                                                                                                         | Α                                   |                           |                                                                    | 84052                                                         |  |

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                    |                                     |                           | REVISION LEVEL                                                     | <b>SHEET</b> 25                                               |  |

### Name and function (maximum mode) MN/MX = GND

SYMBOL

HOLD HLDA HOLD: Indicates that another master is requesting a local bus "hold." To be acknowledged, HOLD must be active HIGH. The processor receiving the "hold" will issue a "hold acknowledge" (HLDA) in the middle of a T4 or T1 clock cycle. Simultaneous with the issuance of HLDA, the processor will float the local bus and control lines. After HOLD is detected as being LOW, the processor will lower HLDA, and when the processor needs to run another cycle, it will again drive the local bus and control lines.

HOLD is not an asynchronous input. External synchronization should be provided if the system cannot otherwise guarantee the setup time.

$\overline{s_0}$ ,  $\overline{s_1}$ ,  $\overline{s_2}$

STATUS: active during  $T_4$ ,  $T_1$ , and  $T_2$  and is returned to the passive state (1, 1, 1) during  $T_3$  or during  $T_W$  when READY is HIGH. This status is used by the Bus Controller to generate all memory and I/O access control signals. Any change by  $\overline{S_2}$ ,  $\overline{S_1}$ , or  $\overline{S_0}$  during  $T_4$  is used to indicate the beginning of a bus cycle and the return to the passive state in  $T_3$  or  $T_W$  is used to indicate the end of a bus cycle. These signals are held internally to a high impedance logic one state during "grant sequence."

These status lines are encoded as follows:

| 0   0   1   Read I/O Port<br>  0   1   0   Write I/O Port<br>  0   1   1   Halt | 52                                                               | 52 51                   | 20                                   | Characteristics                                                  |

|---------------------------------------------------------------------------------|------------------------------------------------------------------|-------------------------|--------------------------------------|------------------------------------------------------------------|

| 1                                                                               | O (LOW)<br>  O  <br>  O  <br>  O  <br>  O  <br>  1 (HIGH)<br>  1 | 0   0<br>0   1<br>0   1 | 0<br>  1<br>  0<br>  1<br>  0<br>  1 | Write I/O Port  <br>  Halt  <br>  Code Access  <br>  Read Memory |

RQ/GTO

REQUEST/GRANT: Pins are used by other local bus masters to force the RQ/GT1 processor to release the local bus at the end of the processor's current bus cycle. Each pin is bidirectional with  $RQ/GT_0$  having higher priority than  $RQ/GT_1$ . RQ/GT has internal bus-hold high circuitry and, if unused, may be left unconnected. The request/grant sequence is as follows (see figure 3):

- 1. A pulse of one CLK wide from another local bus master indicates a local bus request ("hold") to the device (pulse 1).

- 2. During a T<sub>4</sub> or T<sub>1</sub> clock cycle, a pulse one clock wide from the device to the requesting master (pulse 2), indicates that the device has allowed the local bus to float and that it will enter the "grant sequence" state at the next CLK. The CPU's bus interface unit is disconnected logically from the local bus during "grant sequence." The same rules as for HOLD/HOLDA apply as for when the bus is released.

# STANDARDIZED MILITARY DRAWING DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 SIZE A 84052 REVISION LEVEL C 26

#### Name and function (maximum mode) MN/MX = GND

SYMBOL

3. A pulse one CLK wide from the requesting master indicates to the device (pulse 3) that the "hold" request is about to end and that the device can reclaim the local bus at the next CLK. The CPU then enters  $T_4$ .

Each master-master exchange of the local bus is a sequence of three pulses. There must be one idle CLK cycle after each bus exchange. Pulses are active LOW.

If the request is made while the CPU is performing a memory cycle, it will release the local bus during T4 of the cycle when all the following conditions are met:

- 1. Request occurs on or before T2.

- 2. Current cycle is not the low bit of a word.

- Current cycle is not the first acknowledge of an interrupt acknowledge sequence.

- 4. A locked instruction is not currently executing.

If the local bus is idle when the request is made, the two possible events will follow:

- 1. Local bus will be released during the next clock.

- 2. A memory cycle will start within 3 clocks. Now the four rules for a currently active memory cycle apply with condition number 1 already satisfied.

LOCK

$\overline{\text{LOCK}}$ : Indicates that other system bus masters are not go gain control of the system bus while  $\overline{\text{LOCK}}$  is active (LOW). The  $\overline{\text{LOCK}}$  signal is activated by the "LOCK" prefix instruction and remains active until the completion of the next instruction. This signal is active LOW, and is held high internally during "grant sequence."

$QS_1, QS_0$

QUEUE STATUS: The queue status is valid during the CLK cycle after which the queue  $QS_0$ 051 operation is performed. O (LOW) O No Operation 1 First Byte of QS<sub>1</sub> and QS<sub>0</sub> provide status to allow external tracking of the internal Op Code from Queue instruction queue. Note that QS1, 1 (HIGH) O Empty the Queue 1 Subsequent Byte QSo never become high impedance. from Queue

| STANDARDIZED MILITARY DRAWING                        | SIZE<br><b>A</b> |                |   | 84052 |    |

|------------------------------------------------------|------------------|----------------|---|-------|----|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVEL | _ | SHEET | 27 |

6.6 Approved sources of supply. Approved sources of supply are listed in MIL-BUL-103. Additional sources will be added to MIL-BUL-103 as they become available. The vendors listed in MIL-BUL-103 have agreed to this drawing and a certificate of compliance (see 3.6 herein) has been submitted to and accepted by DESC-ECC. The approved sources of supply listed below are for information purposes only and are current only to the date of the last action of this document.

| Military drawing<br>  part number<br> | Vendor<br>  CAGE<br>  number | Vendor<br>  similar part<br>  number |

|---------------------------------------|------------------------------|--------------------------------------|

| 8405201QX                             | 34371<br>34649               | MD80C86/883  <br>  MD80C86/B         |

| 8405201XX                             | 34371                        | MR80C86/883                          |

| 8405202QX                             | <br>  34371<br>  34649       | MD80C86-2/883                        |

| 8405202XX                             | 34371                        | MR80C86-2/883                        |

1/ <u>Caution</u>: Do not use this number for item acquisition. Items acquired to this number may not satisfy the performance requirements of this drawing.

| Vendor CAGE<br>number | Vendor name<br>and address                                                                                          |

|-----------------------|---------------------------------------------------------------------------------------------------------------------|

| 34371                 | Harris Semiconductor<br>200 Palm Bay Boulevard<br>P. O. Box 883<br>Melbourne, FL 32901                              |

| 34649                 | Intel Corporation<br>3065 Bowers Avenue<br>Santa Clara, CA 95051<br>Point of contact: 5000 West Williams Field Road |

Chandler, AZ 85224

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

84052

REVISION LEVEL

D

28