# mos integrated circuit $\mu$ PD784224, 784225, 784224Y, 784225Y

#### 16/8-BIT SINGLE-CHIP MICROCONTROLLERS

www.datasheet4u.com

The  $\mu$ PD784224 and 784225 are products of the  $\mu$ PD784225 Subseries in the 78K/IV Series. Besides a high-speed and high performance CPU, these controllers have ROM, RAM, I/O ports, 8-bit resolution A/D and D/A converters, timers, serial interfaces, a real-time output port, interrupt functions, and various other peripheral hardware.

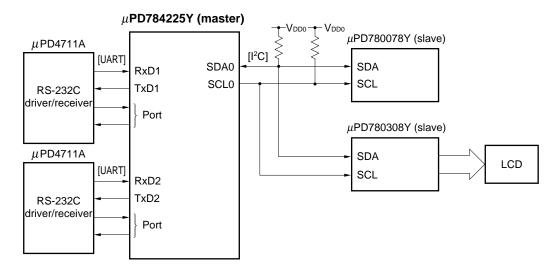

The  $\mu$ PD784224Y and 784225Y are based on the  $\mu$ PD784225 Subseries with the addition of a multimaster-supporting I<sup>2</sup>C bus interface.

Flash memory versions, the  $\mu$ PD78F4225 and 78F4225Y, which replace the internal ROM of the mask ROM version with flash memory, and various development tools are also available.

The functions are explained in detail in the following user's manuals. Be sure to read this manual when designing your system.

$\mu$ PD784225, 784225Y Subseries User's Manual - Hardware : U12697E 78K/IV Series User's Manual - Instruction : U10905E

#### **FEATURES**

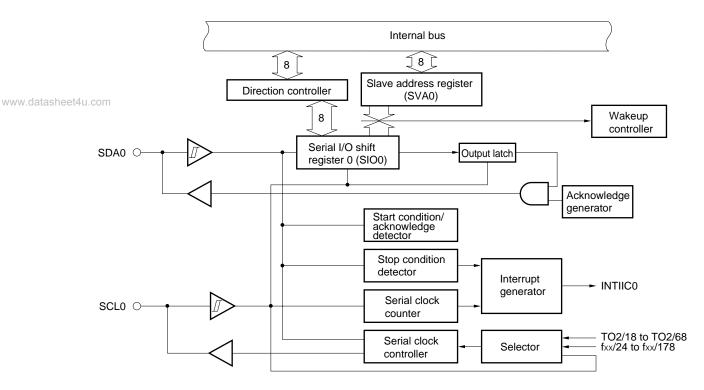

- I<sup>2</sup>C bus

- ROM correction

- Inherits peripheral functions of  $\mu$ PD780058Y Subseries

- Minimum instruction execution time

160 ns (main system clock fxx = 12.5 MHz)

61 μs (subsystem clock fxτ = 32.768 kHz)

- I/O port: 67 pins

- Timer/counter: 16-bit timer/counter × 1 unit

8-bit timer/counter × 4 units

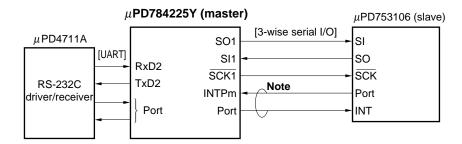

- Serial interface: 3 channels

UART/IOE (3-wire serial I/O): 2 channels

CSI (3-wire serial I/O, multi-master supporting I<sup>2</sup>C bus<sup>Note</sup>): 1 channel

**Note** μPD784225Y Subseries only

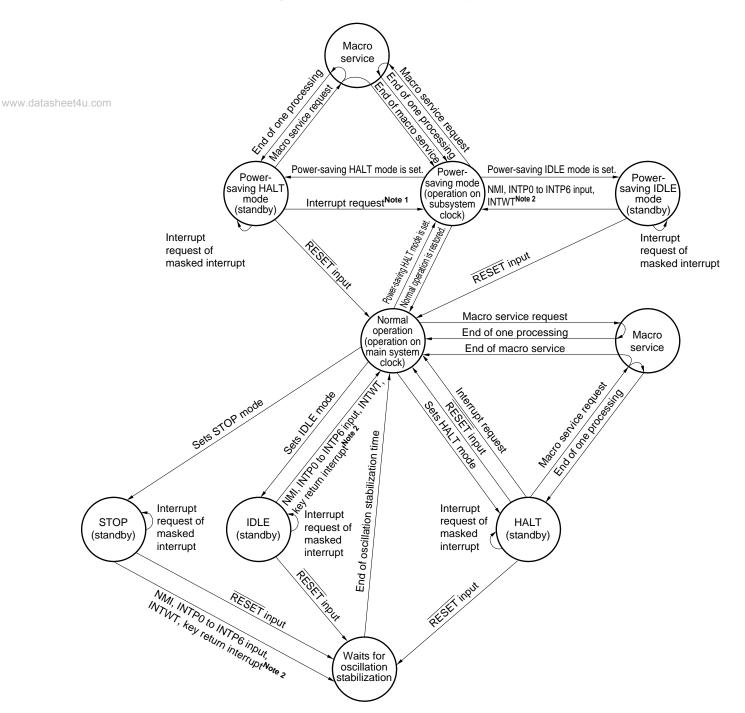

- Standby function HALT/STOP/IDLE mode

- In power-saving mode: HALT/IDLE mode (with subsystem clock)

- · Clock division function

- Watch timer: 1 channel

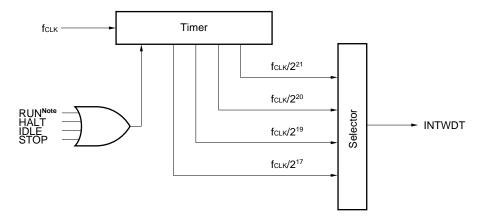

- · Watchdog timer: 1 channel

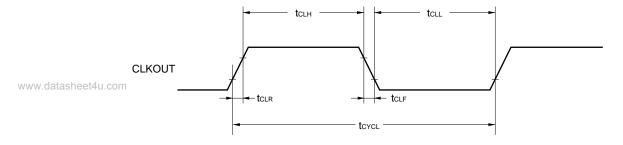

- Clock output function fxx, fxx/2, fxx/2<sup>2</sup>, fxx/2<sup>3</sup>, fxx/2<sup>4</sup>, fxx/2<sup>5</sup>, fxx/2<sup>6</sup>, fxx/2<sup>7</sup>, fxx selectable

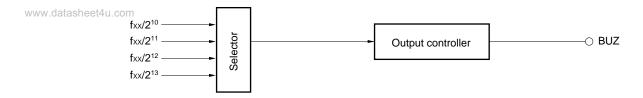

- Buzzer output function fxx/2<sup>10</sup>, fxx/2<sup>11</sup>, fxx/2<sup>12</sup>, fxx/2<sup>13</sup> selectable

- A/D converter: 8-bit resolution × 8 channels

D/A converter: 8-bit resolution × 2 channels

- Supply voltage: VDD = 1.8 to 5.5 V

#### APPLICATION FIELD

Car audio, portable audio, telephones, etc.

Unless contextually excluded, references in this document to  $\mu$ PD784225 mean  $\mu$ PD784224, 784225, 784224Y, and 784225Y.

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.

#### \* ORDERING INFORMATION

|        | Part Number                                               | Package                                              | Internal ROM (Bytes) | Internal RAM (Bytes) |

|--------|-----------------------------------------------------------|------------------------------------------------------|----------------------|----------------------|

|        | $\mu$ PD784224GC- $\times$ $\times$ -8BT                  | 80-pin plastic QFP (14 × 14 mm)                      | 96 K                 | 3,584                |

|        | $\mu$ PD784224GK- $\times$ $\times$ -9EU <sup>Note</sup>  | 80-pin plastic TQFP (fine pitch) (14 $\times$ 20 mm) | 96 K                 | 3,584                |

|        | $\mu$ PD784225GC- $\times$ $\times$ -8BT                  | 80-pin plastic QFP (14 × 14 mm)                      | 128 K                | 4,352                |

| www.da | μPD784225GK-×××-9EU                                       | 80-pin plastic TQFP (fine pitch) (14 $\times$ 20 mm) | 128 K                | 4,352                |

|        | $\mu$ PD784224YGC- $\times$ $\times$ -8BT                 | 80-pin plastic QFP (14 × 14 mm)                      | 96 K                 | 3,584                |

|        | $\mu$ PD784224YGK- $\times$ $\times$ -9EU                 | 80-pin plastic TQFP (fine pitch) (14 $\times$ 20 mm) | 96 K                 | 3,584                |

|        | $\mu$ PD784225YGC- $\times\times$ -8BT $^{\mathbf{Note}}$ | 80-pin plastic QFP (14 × 14 mm)                      | 128 K                | 4,352                |

|        | $\mu$ PD784225YGK- $\times\times$ -9EU <sup>Note</sup>    | 80-pin plastic TQFP (fine pitch) (14 $\times$ 20 mm) | 128 K                | 4,352                |

Note Under development

Remark xxx indicates a ROM code suffix.

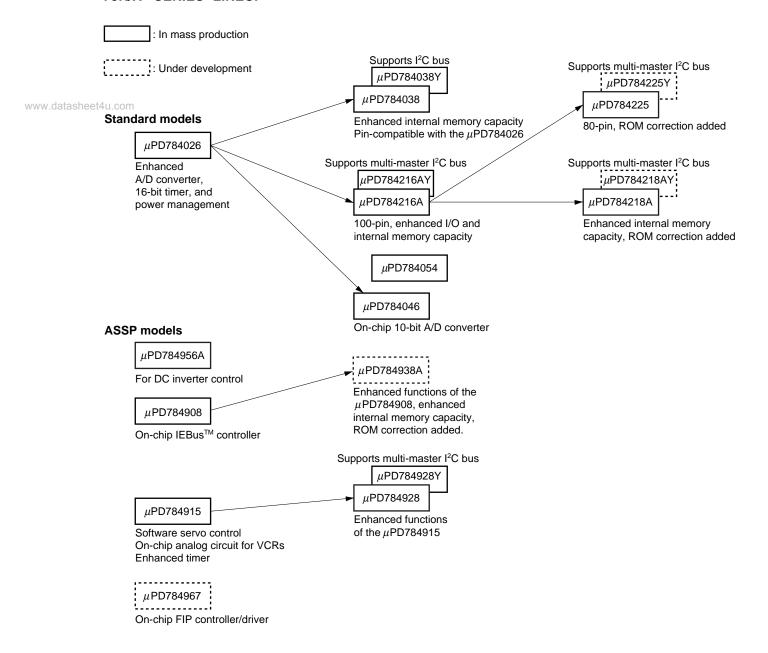

#### **★ 78K/IV SERIES LINEUP**

#### **FUNCTIONS**

|                             | Part Number                           | μPD784224,                                                                                                                                                                    | μPD784225,                                                                               |  |  |  |  |

|-----------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|--|--|--|

| Item                        |                                       | μPD784224Y                                                                                                                                                                    | μPD784225Y                                                                               |  |  |  |  |

| Number of basic (mnemonics) | instructions                          | 113                                                                                                                                                                           |                                                                                          |  |  |  |  |

| General-purpos              | e register                            | 8 bits $\times$ 16 registers $\times$ 8 banks, or 16 bits $\times$                                                                                                            | 8 registers × 8 banks (memory mapping                                                    |  |  |  |  |

| Minimum instruc             | tion execution                        | <ul> <li>160 ns/320 ns/640 ns/1,280 ns/2,560 ns (main system clock: fxx = 12.5 MHz)</li> <li>61 μs (subsystem clock: fxτ = 32.768 kHz)</li> </ul>                             |                                                                                          |  |  |  |  |

| Internal                    | ROM                                   | 96 Kbytes                                                                                                                                                                     | 128 Kbytes                                                                               |  |  |  |  |

| memory                      | RAM                                   | 3,584 bytes                                                                                                                                                                   | 4,352 bytes                                                                              |  |  |  |  |

| Memory space                |                                       | 1 MB with program and data spaces combir                                                                                                                                      | ned                                                                                      |  |  |  |  |

| I/O port                    | Total                                 | 67                                                                                                                                                                            |                                                                                          |  |  |  |  |

|                             | CMOS Input                            | 8                                                                                                                                                                             |                                                                                          |  |  |  |  |

|                             | CMOS I/O                              | 59                                                                                                                                                                            |                                                                                          |  |  |  |  |

| Pins with ancillary         | Pins with pull-up resistor            | 57                                                                                                                                                                            |                                                                                          |  |  |  |  |

| functions Note 1            | LEDs direct drive output              | 16                                                                                                                                                                            |                                                                                          |  |  |  |  |

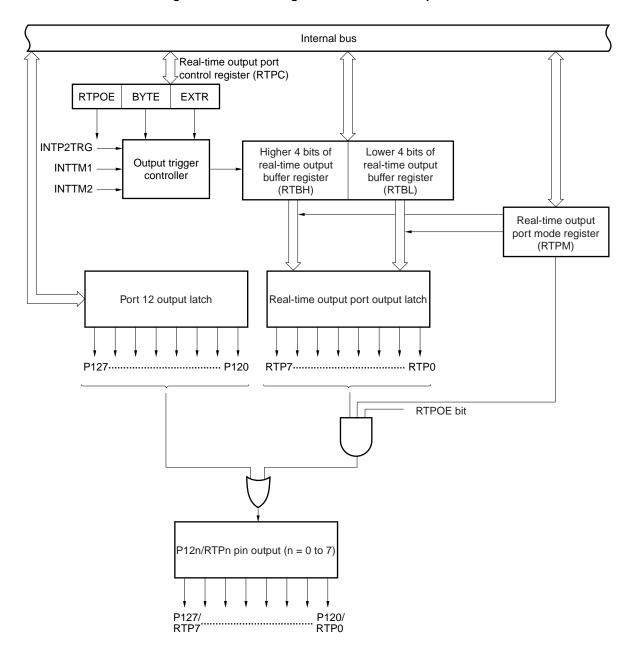

| Real-time outpu             | ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' ' | 4 bits × 2, or 8 bits × 1                                                                                                                                                     |                                                                                          |  |  |  |  |

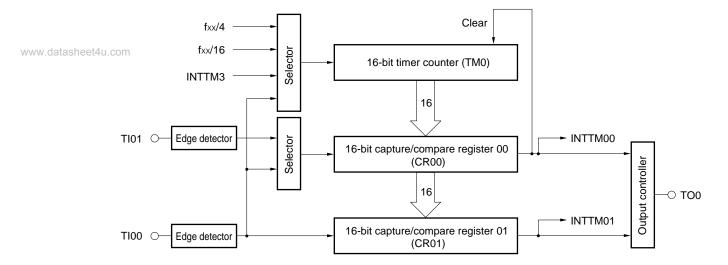

| Timer                       |                                       | Timer/event counter : Timer counter × 1 (16-bit) Capture/compare                                                                                                              | Pulse output register × 2  • PWM/PPG output • Square wave output • One-shot pulse output |  |  |  |  |

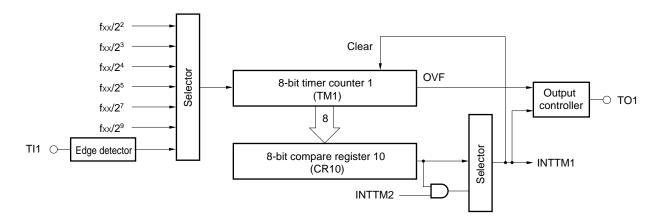

|                             |                                       | Timer/event counter 1 : Timer counter × 1 (8-bit) Compare register                                                                                                            | Pulse output  • PWM output  • Square wave output                                         |  |  |  |  |

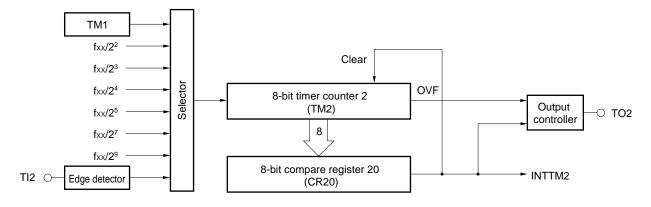

|                             |                                       | Timer/event counter 2 : Timer counter × 1 (8-bit) Compare register                                                                                                            | Pulse output  • PWM output  • Square wave output                                         |  |  |  |  |

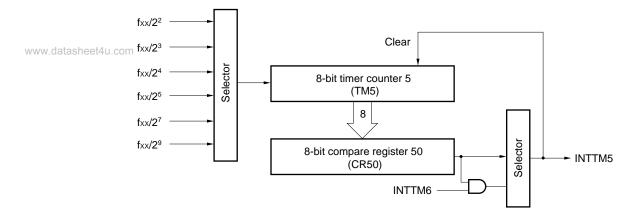

|                             |                                       | Timer 5 : Timer counter $\times$ 1 (8-bit) Compare register                                                                                                                   | × 1                                                                                      |  |  |  |  |

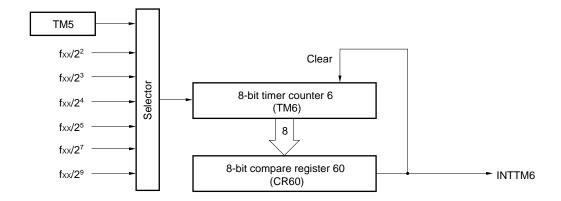

|                             |                                       | Timer 6 : Timer counter × 1 (8-bit) Compare register × 1                                                                                                                      |                                                                                          |  |  |  |  |

| Serial interface            |                                       | UART/IOE (3-wire serial I/O): 2 channels (on-chip baud rate generator)     CSI (3-wire serial I/O, I <sup>2</sup> C bus <sup>Note 2</sup> supporting multi master): 1 channel |                                                                                          |  |  |  |  |

| A/D converter               |                                       | 8-bit resolution × 8 channels                                                                                                                                                 |                                                                                          |  |  |  |  |

| D/A converter               |                                       | 8-bit resolution × 2 channels                                                                                                                                                 |                                                                                          |  |  |  |  |

| Clock output                |                                       | Selectable from fxx, fxx/2, fxx/2 <sup>2</sup> , fxx/2 <sup>3</sup> , fxx/2 <sup>4</sup> , fxx/2 <sup>5</sup> , fxx/2 <sup>6</sup> , fxx/2 <sup>7</sup> , fxt                 |                                                                                          |  |  |  |  |

| Buzzer output               |                                       | Selectable from fxx/2 <sup>10</sup> , fxx/2 <sup>11</sup> , fxx/2 <sup>12</sup> , fxx/2 <sup>13</sup>                                                                         |                                                                                          |  |  |  |  |

| Watch timer                 |                                       | 1 channel                                                                                                                                                                     |                                                                                          |  |  |  |  |

| Watchdog timer              |                                       | 1 channel                                                                                                                                                                     |                                                                                          |  |  |  |  |

| Standby                     |                                       | HALT/STOP/IDLE mode                                                                                                                                                           |                                                                                          |  |  |  |  |

|                             |                                       | In power-saving mode (with subsystem clock): HALT/IDLE mode                                                                                                                   |                                                                                          |  |  |  |  |

| Interrupt                   | Hardware                              | 25 (internal: 18, external: 7)                                                                                                                                                |                                                                                          |  |  |  |  |

|                             | Software                              | BRK instruction, BRKCS instruction, operar                                                                                                                                    | d error                                                                                  |  |  |  |  |

|                             | Non-maskable                          | Internal: 1, external: 1                                                                                                                                                      |                                                                                          |  |  |  |  |

|                             | Maskable                              | Internal: 17, external: 6                                                                                                                                                     |                                                                                          |  |  |  |  |

|                             |                                       | <ul><li>4 programmable priority levels</li><li>3 service modes: vectored interrupt/macro</li></ul>                                                                            | o service/context switching                                                              |  |  |  |  |

| Supply voltage              |                                       | V <sub>DD</sub> = 1.8 to 5.5 V                                                                                                                                                |                                                                                          |  |  |  |  |

| - · · · · · · - ·           |                                       | 80-pin plastic QFP(14 × 14 mm)                                                                                                                                                |                                                                                          |  |  |  |  |

| -                           |                                       | • 80-pin plastic TQFP (fine pitch) (12 × 12 mm)                                                                                                                               |                                                                                          |  |  |  |  |

**Notes 1.** The pins with ancillary functions are included in the I/O pins.

**2.**  $\mu$ PD784225Y Subseries only

#### **CONTENTS**

|              | 1.              | DIFF     | ERENCES AMONG MODELS IN $\mu$ PD784225, 784225Y SUBSERIES                      | . 7  |

|--------------|-----------------|----------|--------------------------------------------------------------------------------|------|

| /ww.datashee | t4 <u>2.</u> cc |          | OR DIFFERENCES BETWEEN $\mu$ PD784216Y SUBSERIES AND                           |      |

|              |                 | $\mu$ PD | 780058Y SUBSERIES                                                              | . 8  |

|              | 3.              | PIN (    | CONFIGURATION (Top View)                                                       | . 9  |

|              | 4.              | BLO      | CK DIAGRAM                                                                     | . 11 |

|              | 5.              | PIN I    | FUNCTION                                                                       | . 12 |

|              |                 | 5.1      | Port Pins                                                                      |      |

|              |                 | 5.2      | Pins Other Than Port Pins                                                      | . 14 |

|              |                 | 5.3      | I/O Circuit Type of Respective Pins and Recommended Connections of Unused Pins |      |

|              | 6.              | CPU      | ARCHITECTURE                                                                   | . 20 |

|              |                 | 6.1      | Memory Space                                                                   | . 20 |

|              |                 | 6.2      | CPU Registers                                                                  | . 23 |

|              |                 |          | 6.2.1 General-purpose registers                                                | . 23 |

|              |                 |          | 6.2.2 Control registers                                                        | . 24 |

|              |                 |          | 6.2.3 Special function registers (SFRs)                                        | . 25 |

|              | 7.              | PER      | PHERAL HARDWARE FUNCTIONS                                                      | . 30 |

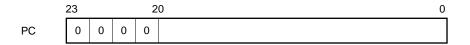

|              |                 | 7.1      | Ports                                                                          | . 30 |

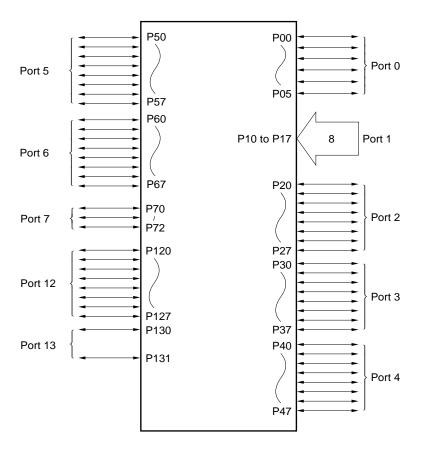

|              |                 | 7.2      | Clock Generator                                                                | . 31 |

|              |                 | 7.3      | Real-Time Output Port                                                          | . 33 |

|              |                 | 7.4      | Timer                                                                          | . 34 |

|              |                 | 7.5      | A/D Converter                                                                  | . 37 |

|              |                 | 7.6      | D/A Converter                                                                  | . 38 |

|              |                 | 7.7      | Serial Interface                                                               | . 39 |

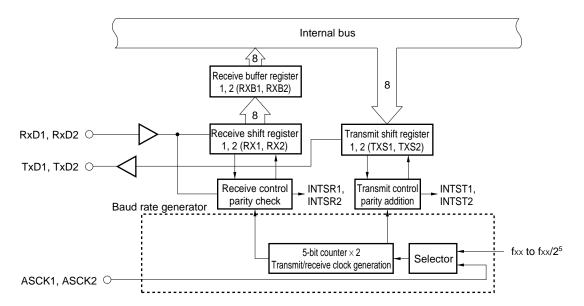

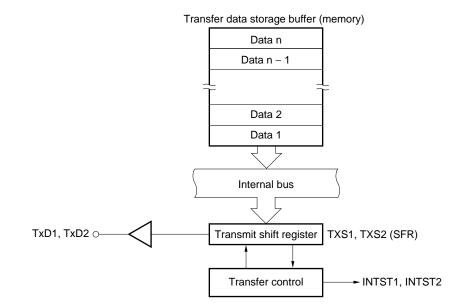

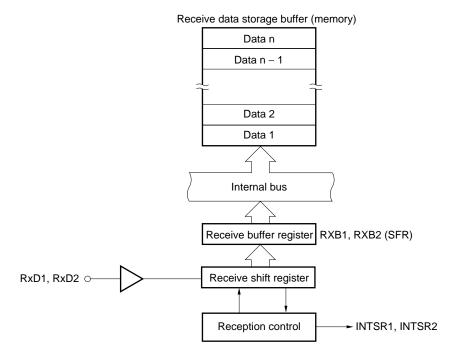

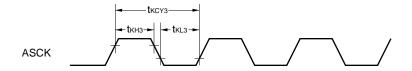

|              |                 |          | 7.7.1 Asynchronous serial interface/3-wire serial I/O (UART/IOE)               | . 40 |

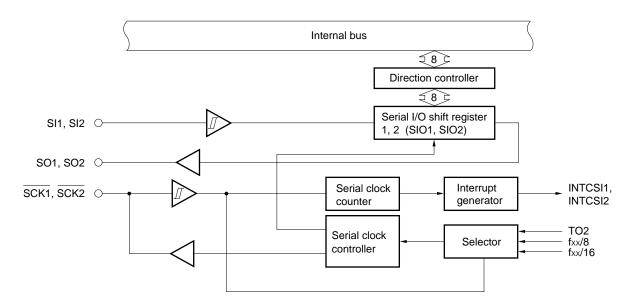

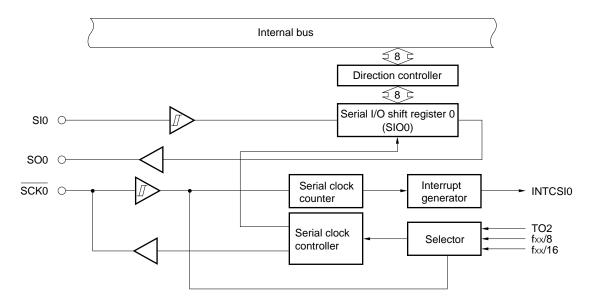

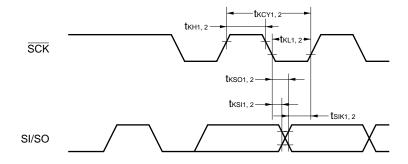

|              |                 |          | 7.7.2 Clocked serial interface (CSI)                                           | . 42 |

|              |                 | 7.8      | Clock Output Function                                                          | . 43 |

|              |                 | 7.9      | Buzzer Output Function                                                         | . 44 |

|              |                 | 7.10     | Edge Detection Function                                                        | . 44 |

|              |                 | 7.11     | Watch Timer                                                                    | . 44 |

|              |                 | 7.12     | Watchdog Timer                                                                 | . 45 |

|              | 8.              | INTE     | RRUPT FUNCTION                                                                 | . 46 |

|              |                 | 8.1      | Interrupt Sources                                                              | . 46 |

|              |                 | 8.2      | Vectored Interrupt                                                             | . 48 |

|              |                 | 8.3      | Context Switching                                                              | . 49 |

|              |                 | 8.4      | Macro Service                                                                  | . 49 |

|              |                 | 8.5      | Application Example of Macro Service                                           | . 50 |

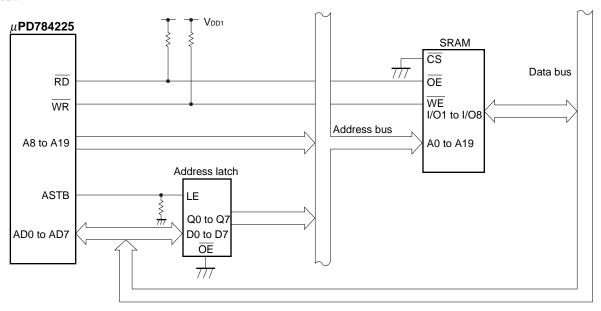

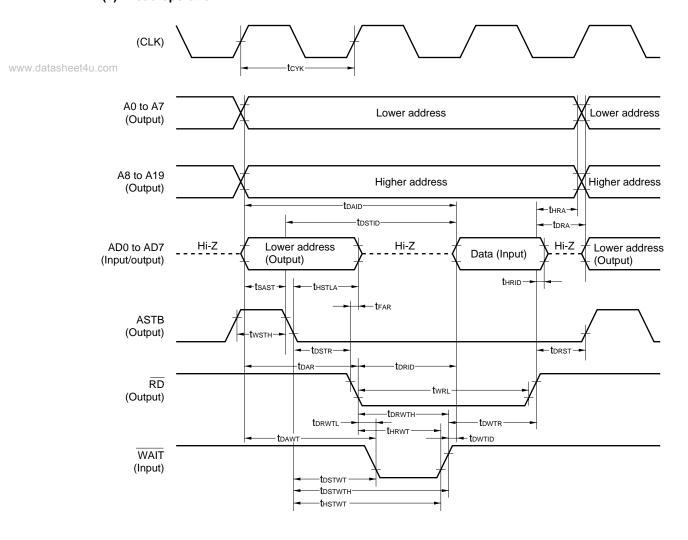

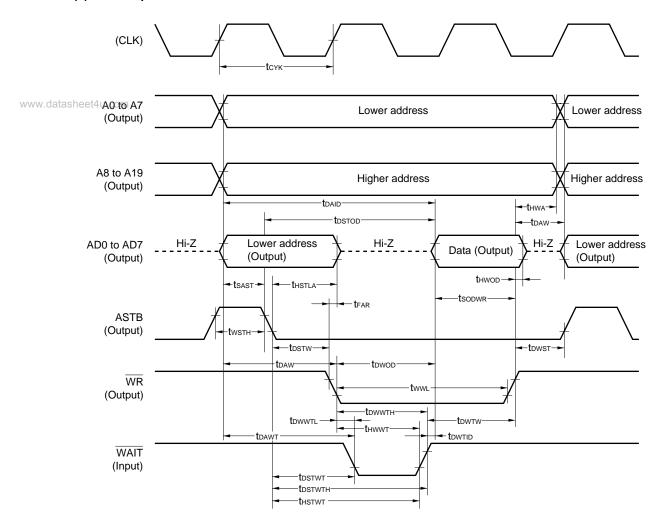

|      | 9.  | LOC            | AL BUS INTERFACE                | 51 |

|------|-----|----------------|---------------------------------|----|

|      |     | 9.1            | Memory Expansion                | 51 |

|      |     | 9.2            | Programmable Wait               | 51 |

|      |     | 9.3            | External Access Status Function | 51 |

| w d  |     | STA<br>eet4u.c | NDBY FUNCTION                   | 52 |

| W.Ca |     |                | ET FUNCTION                     | 54 |

|      | 12. | ROM            | 1 CORRECTION                    | 55 |

|      | 13. | INST           | TRUCTION SET                    | 56 |

| *    | 14. | ELE            | CTRICAL SPECIFICATIONS          | 61 |

|      | 15. | PAC            | KAGE DRAWINGS                   | 82 |

| *    | 16. | REC            | OMMENDED SOLDERING CONDITIONS   | 84 |

|      | API | PEND           | DIX A. DEVELOPMENT TOOLS        | 85 |

|      | ΔРІ | PEND           | NIX B. RELATED DOCUMENTS        | 22 |

#### $\star$ 1. DIFFERENCES AMONG MODELS IN $\mu$ PD784225, 784225Y SUBSERIES

The only difference among the  $\mu$ PD784224 and 784225 lies in the internal memory capacity.

The  $\mu$ PD784224Y and 784225Y are based on the  $\mu$ PD784224 and 784225 respectively, with the addition of an I<sup>2</sup>C bus control function.

The  $\mu$ PD78F4225 and 78F4225Y are provided with a 128-Kbyte flash memory instead of the mask ROM of the www.datasheet4above models. These differences are summarized in Table 1-1.

Table 1-1. Differences among Models in  $\mu$ PD784225, 784225Y Subseries

| Part Number Item                                                    | μPD784224,<br>μPD784224Y        | μPD784225,<br>μPD784225Y | μPD78F4225,<br>μPD78F4225Y     |  |  |

|---------------------------------------------------------------------|---------------------------------|--------------------------|--------------------------------|--|--|

| Internal ROM                                                        | 96 Kbytes<br>(mask ROM)         | 128 Kbytes<br>(mask ROM) | 128 Kbytes<br>(Flash memory)   |  |  |

| Internal RAM                                                        | 3,584 bytes                     | 4,352 bytes              |                                |  |  |

| Internal memory<br>size switching<br>register (IMS) <sup>Note</sup> | None                            |                          | Provided                       |  |  |

| Supply voltage                                                      | V <sub>DD</sub> = 1.8 to 5.5 V  |                          | V <sub>DD</sub> = 1.9 to 5.5 V |  |  |

| Electrical specifications                                           | Refer to the data sheet for eac | h device.                |                                |  |  |

| Recommended soldering conditions                                    |                                 |                          |                                |  |  |

| TEST pin                                                            | Provided                        |                          | None                           |  |  |

| V <sub>PP</sub> pin                                                 | None                            |                          | Provided                       |  |  |

**Note** The internal flash memory capacity and internal RAM capacity can be changed using the internal memory size switching register (IMS).

Caution There are differences in noise immunity and noise radiation between the flash memory and mask ROM versions. When pre-producing an application set with the flash memory version and then mass-producing it with the mask ROM version, be sure to conduct sufficient evaluations on the commercial samples (not engineering samples) of the mask ROM version.

### 2. MAJOR DIFFERENCES BETWEEN $\mu$ PD784216Y SUBSERIES AND $\mu$ PD780058Y SUBSERIES

|      |                                                                                    | Series Name                     | μPD784225, 784225Y                                                                                                   | μPD784216Y Subseries                                                                                                 | μPD780058Y Subseries                                                                                                                                                                                                                        |

|------|------------------------------------------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ite  | Item                                                                               |                                 | Subseries                                                                                                            |                                                                                                                      |                                                                                                                                                                                                                                             |

| СР   | CPU                                                                                |                                 | 16-bit CPU                                                                                                           |                                                                                                                      | 8-bit CPU                                                                                                                                                                                                                                   |

|      | nimum<br>truction                                                                  | With main system clock selected | 160 ns (at 12.5 MHz)                                                                                                 |                                                                                                                      | 400 ns (at 5.0 MHz)                                                                                                                                                                                                                         |

| exe  | ecution time                                                                       | With subsystem clock            | 61 μs (at 32.768 kHz)                                                                                                |                                                                                                                      | 122 μs (at 32.768 kHz)                                                                                                                                                                                                                      |

| Ме   | emory space                                                                        |                                 | 1 Mbytes                                                                                                             |                                                                                                                      | 64 Kbytes                                                                                                                                                                                                                                   |

| I/O  | port                                                                               | Total                           | 67 pins                                                                                                              | 86 pins                                                                                                              | 68 pins                                                                                                                                                                                                                                     |

|      |                                                                                    | CMOS input                      | 8 pins                                                                                                               | 8 pins                                                                                                               | 2 pins                                                                                                                                                                                                                                      |

|      |                                                                                    | CMOS I/O                        | 59 pins                                                                                                              | 72 pins                                                                                                              | 62 pins                                                                                                                                                                                                                                     |

|      |                                                                                    | N-ch open-drain I/O             | -                                                                                                                    | 6 pins                                                                                                               | 4 pins                                                                                                                                                                                                                                      |

| a    | Pins with ancillary                                                                | Pins with pull-up resistor      | 57 pins                                                                                                              | 70 pins                                                                                                              | 66 pins (flash memory model: 62 pins)                                                                                                                                                                                                       |

| f    | unction <sup>Note</sup> 1                                                          | LED direct drive output         | 16 pins                                                                                                              | 22 pins                                                                                                              | 12 pins                                                                                                                                                                                                                                     |

|      |                                                                                    | Medium-voltage pin              | -                                                                                                                    | 6 pins                                                                                                               | 4 pins                                                                                                                                                                                                                                      |

| Tin  | Timer/counter  Serial interface                                                    |                                 | <ul> <li>16-bit timer/event counter         × 1 unit</li> <li>8-bit timer/event counter         × 4 units</li> </ul> | <ul> <li>16-bit timer/event counter         × 1 unit</li> <li>8-bit timer/event counter         × 6 units</li> </ul> | 16-bit timer/event counte     × 1 unit     8-bit timer/event counter     × 2 units                                                                                                                                                          |

| Se   |                                                                                    |                                 | <ul> <li>UART/IOE (3-wire serial I/O)</li> <li>CSI (3-wire serial I/O), mult bus Note 2) × 1 channel</li> </ul>      |                                                                                                                      | UART (time-division transfer function)/IOE (3-wire serial I/O) × 2 channels CSI (3-wire serial I/O, 2-wire serial I/O, I <sup>2</sup> C bus) × 1 channel CSI (3-wire serial I/O with automatic transmission/reception function) × 1 channel |

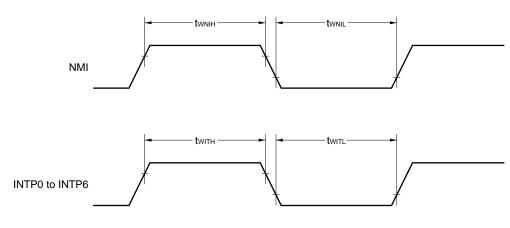

| Inte | errupt                                                                             | NMI pin                         | Provided                                                                                                             |                                                                                                                      | None                                                                                                                                                                                                                                        |

|      |                                                                                    | Macro service                   | Provided                                                                                                             | led                                                                                                                  |                                                                                                                                                                                                                                             |

|      | Context switching Programmable priority  Standby function  ROM correction  Package |                                 | Provided                                                                                                             |                                                                                                                      | None                                                                                                                                                                                                                                        |

|      |                                                                                    |                                 | 4 levels                                                                                                             |                                                                                                                      | 2 levels                                                                                                                                                                                                                                    |

| Sta  |                                                                                    |                                 | HALT/STOP/IDLE mode     Power-saving mode: HALT                                                                      | T/IDLE Mode                                                                                                          | HALT/STOP mode                                                                                                                                                                                                                              |

| RC   |                                                                                    |                                 | Provided                                                                                                             | None                                                                                                                 | Provided                                                                                                                                                                                                                                    |

| Pa   |                                                                                    |                                 | • 80-pin plastic QFP<br>(14 × 14 mm)<br>• 80-pin plastic TQFP<br>(fine pitch) (12 × 12 mm)                           | • 100-pin plastic QFP (fine pitch) (14 × 14 mm) • 100-pin plastic QFP (14 × 20 mm)                                   | 80-pin plastic QFP     (14 × 14 mm)     80-pin plastic TQFP     (fine pitch) (12 × 12 mm)                                                                                                                                                   |

Notes 1. Pins with ancillary function are included in the I/O pins.

**2.**  $\mu$ PD784225Y and 784216Y Subseries only

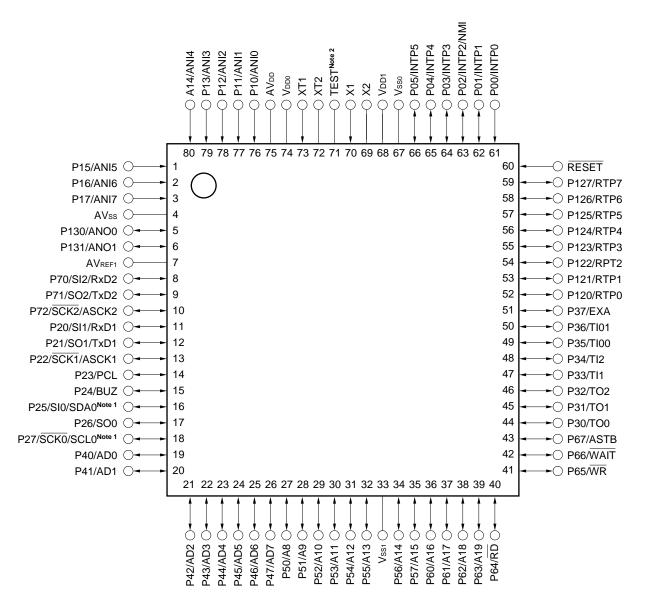

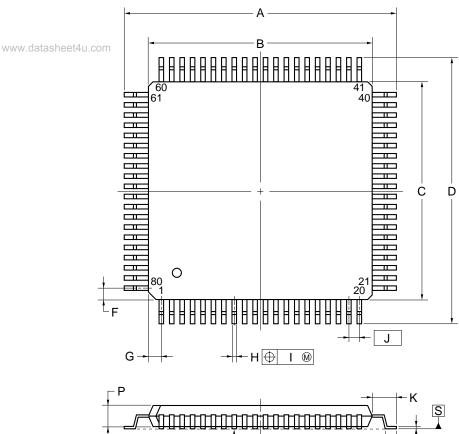

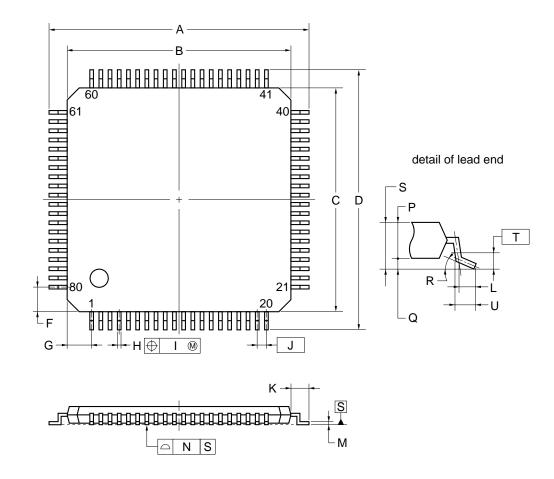

#### 3. PIN CONFIGURATION (Top View)

80-pin plastic QFP (14 × 14 mm)

μPD784224GC-×××-8BT, μPD784224YGC-×××-8BT,

μPD784225GC-×××-8BT, μPD784225YGC-×××-8BT

• 80-pin plastic TQFP (fine pitch) (12 × 12 mm)

www.datasheet4u.com $\mu$ PD784224GK-xxx-BE9,  $\mu$ PD784224YGK-xxx-BE9,  $\mu$ PD784225GK-xxx-BE9,  $\mu$ PD784225YGK-xxx-BE9

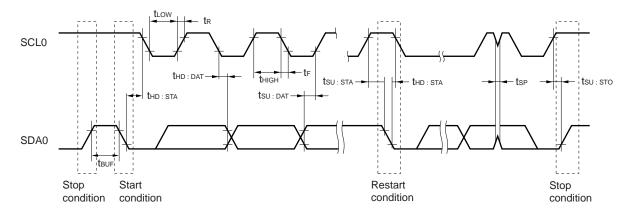

- **Notes 1.** The SCL0 and SDA0 pins are available in  $\mu$ PD784225Y Subseries only.

- 2. Connect the TEST pin to Vsso directly or via a pull-down resistor. For the pull-down connection, use of a resistor with a resistance ranging from 470  $\Omega$  to 10 k $\Omega$  is recommended.

#### Caution Connect the AVss pin to Vsso.

**Remark** When using in applications where noise from inside the microcomputer has to be reduced, it is recommended to take countermeasures against noise such as supplying power to VDD0 and VDD1 independently, and connecting Vsso and Vss1 to different ground lines.

|          | A8 to A19          | : Address Bus                   | P130, P131           | : Port13                      |

|----------|--------------------|---------------------------------|----------------------|-------------------------------|

|          | AD0 to AD7         | : Address/Data Bus              | PCL                  | : Programmable Clock          |

|          | ANI0 to ANI7       | : Analog Input                  | RD                   | : Read Strobe                 |

|          | ANO0, ANO1         | : Analog Output                 | RESET                | : Reset                       |

|          | ASCK1, ASCK2       | : Asynchronous Serial Clock     | RTP0 to RTP7         | : Real-time Output Port       |

|          | ASTB               | : Address Strobe                | RxD1, RxD2           | : Receive Data                |

| www.data | s AV bu.com        | : Analog Power Supply           | SCK0 to SCK2         | : Serial Clock                |

|          | AV <sub>REF1</sub> | : Analog Reference Voltage      | SCL0 <sup>Note</sup> | : Serial Clock                |

|          | AVss               | : Analog Ground                 | SDA0 <sup>Note</sup> | : Serial Data                 |

|          | BUZ                | : Buzzer Clock                  | SI0 to SI2           | : Serial Input                |

|          | EXA                | : External Access Status Output | SO0 to SO2           | : Serial Output               |

|          | INTP0 to INTP5     | : Interrupt from Peripherals    | TEST                 | : Test                        |

|          | NMI                | : Non-maskable Interrupt        | TI00, TI01, TI1, TI2 | 2 : Timer Input               |

|          | P00 to P05         | : Port0                         | TO0 to TO2           | : Timer Output                |

|          | P10 to P17         | : Port1                         | TxD1, TxD2           | : Transmit Data               |

|          | P20 to P27         | : Port2                         | VDD0, VDD1           | : Power Supply                |

|          | P30 to P37         | : Port3                         | Vsso, Vss1           | : Ground                      |

|          | P40 to P47         | : Port4                         | WAIT                 | : Wait                        |

|          | P50 to P57         | : Port5                         | WR                   | : Write Strobe                |

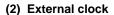

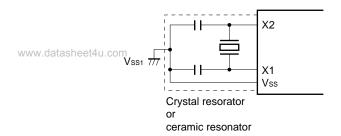

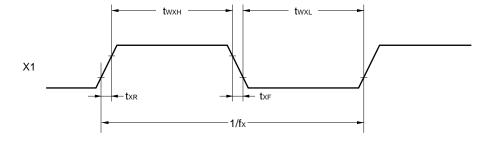

|          | P60 to P67         | : Port6                         | X1, X2               | : Crystal (Main System Clock) |

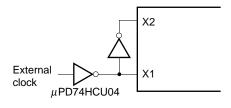

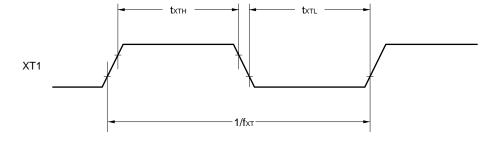

|          | P70 to P72         | : Port7                         | XT1, XT2             | : Crystal (Subsystem Clock)   |

|          | P120 to P127       | : Port12                        |                      |                               |

**Note** The SCL0 and SDA0 pins are available in  $\mu$ PD784225Y Subseries only.

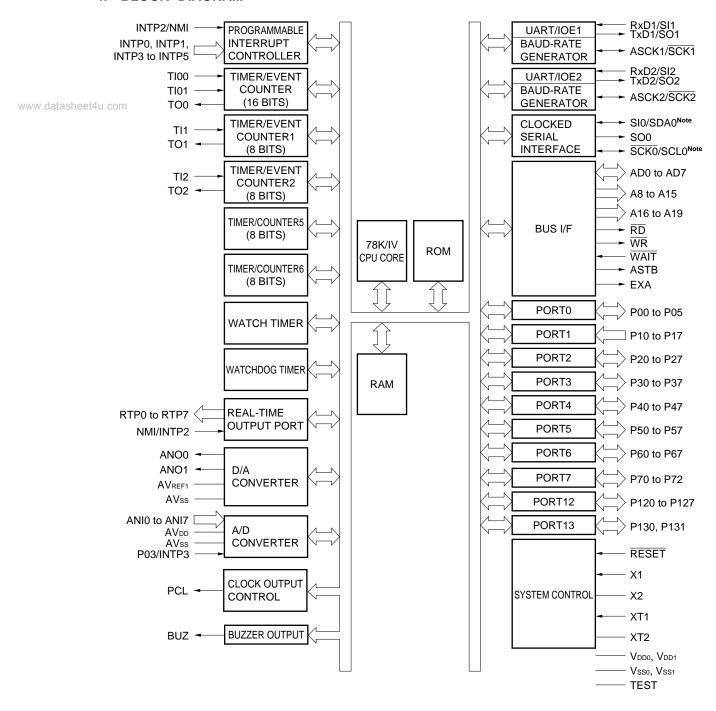

#### 4. BLOCK DIAGRAM

**Note** This function supports the I<sup>2</sup>C bus interface and is available in  $\mu$ PD784225Y Subseries only.

Remark The internal ROM and RAM capacities differ depending on the model.

#### 5. PIN FUNCTION

# 5.1 Port Pins (1/2)

www.d

| Pin Name            | I/O   | Alternate Function       | Function                                                                                                                                                                                    |

|---------------------|-------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P00                 | I/O   | INTP0                    | Port 0 (P0):                                                                                                                                                                                |

| asheet4u.com<br>P01 |       | INTP1                    | • 6-bit I/O port                                                                                                                                                                            |

| P02                 |       | INTP2/NM1                | <ul> <li>Can be set in input or output mode bit-wise.</li> <li>Pins set in input mode can be connected to internal pull-up</li> </ul>                                                       |

| P03                 |       | INTP3                    | resistors by software bit-wise.                                                                                                                                                             |

| P04                 |       | INTP4                    |                                                                                                                                                                                             |

| P05                 |       | INTP5                    |                                                                                                                                                                                             |

| P10 to P17          | Input | ANI0 to ANI7             | Port 1 (P1): • 8-bit input port                                                                                                                                                             |

| P20                 | I/O   | RxD1/SI1                 | Port 2 (P2):                                                                                                                                                                                |

| P21                 | 1     | TxD1/SO1                 | 8-bit I/O port                                                                                                                                                                              |

| P22                 | 1     | ASCK1/SCK1               | <ul> <li>Can be set in input or output mode bit-wise.</li> <li>Pins set in input mode can be connected to internal pull-up</li> </ul>                                                       |

| P23                 |       | PCL                      | resistors by software bit-wise.                                                                                                                                                             |

| P24                 |       | BUZ                      |                                                                                                                                                                                             |

| P25                 |       | SI0/SDA0 <sup>Note</sup> |                                                                                                                                                                                             |

| P26                 |       | SO0                      |                                                                                                                                                                                             |

| P27                 |       | SCK0/SCL0Note            |                                                                                                                                                                                             |

| P30                 | I/O   | TO0                      | Port 3 (P3):                                                                                                                                                                                |

| P31                 |       | TO1                      | 8-bit I/O port     Con he get in input or output mode bit wise.                                                                                                                             |

| P32                 |       | TO2                      | <ul> <li>Can be set in input or output mode bit-wise.</li> <li>Pins set in input mode can be connected to internal pull-up</li> </ul>                                                       |

| P33                 |       | TI1                      | resistors by software bit-wise.                                                                                                                                                             |

| P34                 |       | TI2                      |                                                                                                                                                                                             |

| P35                 |       | TI00                     |                                                                                                                                                                                             |

| P36                 | 1     | TI01                     |                                                                                                                                                                                             |

| P37                 | 1     | EXA                      |                                                                                                                                                                                             |

| P40 to P47          | I/O   | AD0 to AD7               | Port 4 (P4):  • 8-bit I/O port  • Can be set in input or output mode bit-wise.  • All pins set in input mode can be connected to internal pull-up resistors by software.  • Can drive LEDs. |

| P50 to P57          | I/O   | A8 to A15                | Port 5 (P5):  • 8-bit I/O port  • Can be set in input or output mode bit-wise.  • All pins set in input mode can be connected to internal pull-up resistors by software.  • Can drive LEDs. |

**Note** This function is available in  $\mu$ PD784255Y Subseries only.

# 5.1 Port Pins (2/2)

www.datasheet4

| Pin Name             | I/O | Alternate Function | Function                                                                                                                                                                       |

|----------------------|-----|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P60                  | I/O | A16                | Port 6 (P6):                                                                                                                                                                   |

| P61                  |     | A17                | 8-bit I/O port     Can be set in input or output mode bit-wise.                                                                                                                |

| <b>P62</b><br>4u.com |     | A18                | All pins set in input mode can be connected to internal pull-up                                                                                                                |

| P63                  |     | A19                | resistors by software.                                                                                                                                                         |

| P64                  |     | RD                 |                                                                                                                                                                                |

| P65                  |     | WR                 |                                                                                                                                                                                |

| P66                  |     | WAIT               |                                                                                                                                                                                |

| P67                  |     | ASTB               |                                                                                                                                                                                |

| P70                  | I/O | RxD2/SI2           | Port 7 (P7):                                                                                                                                                                   |

| P71                  |     | TxD2/SO2           | 3-bit I/O port     Can be set in input or output mode bit-wise.     Pins set in input mode can be connected to internal pull-up                                                |

| P72                  |     | ASCK2/SCK2         | resistor by software bit-wise.                                                                                                                                                 |

| P120 to P127         | I/O | RTP0 to RTP7       | Port 12 (P12):  • 8-bit I/O port  • Can be set in input or output mode bit-wise.  • Pins set in input mode can be connected to internal pull-up resistor by software bit-wise. |

| P130, P131           | I/O | ANO0, ANO1         | Port 13 (P13):  • 2-bit I/O port  • Can be set in input or output mode bit-wise.                                                                                               |

#### 5.2 Pins Other Than Port Pins (1/2)

Pin Name I/O Alternate Function **Function** TI00 Input P35 External count clock input to 16-bit timer register TI01 P36 Capture trigger signal input to capture/compare register 00 TI1 asheet4<u>u.com</u> P33 External count clock input to 8-bit timer register 1 www.da TI2 P34 External count clock input to 8-bit timer register 2 TO0 16-bit timer output (shared by 14-bit PWM output) Output P30 **TO1** P31 8-bit timer output (shared by 8-bit PWM output) TO<sub>2</sub> P32 RxD1 P20/SI1 Serial data input (UART1) Input RxD2 P70/SI2 Serial data input (UART2) TxD1 Output P21/S01 Serial data output (UART1) TxD2 P71/SO2 Serial data output (UART2) P22/SCK1 ASCK1 Intput Baud rate clock input (UART1) P72/SCK2 ASCK2 Baud rate clock input (UART2) P25/SDA0Note SI0 Serial data input (3-wire serial clock I/O0) Input SI1 P20/RxD1 Serial data input (3-wire serial clock I/O1) SI2 P70/RxD2 Serial data input (3-wire serial clock I/O2) SO<sub>0</sub> P26 Serial data output (3-wire serial I/O0) Output SO<sub>1</sub> P21/TxD1 Serial data output (3-wire serial I/O1) SO<sub>2</sub> P71/TxD2 Serial data output (3-wire serial I/O2) SDA0Note I/O P25/SI0 Serial data input/output (I<sup>2</sup>C bus) P27/SCL0Note SCK<sub>0</sub> Serial clock input/output (3-wire serial I/O0) I/O SCK<sub>1</sub> P22/ASCK1 Serial clock input/output (3-wire serial I/O1) SCK<sub>2</sub> P72/ASCK2 Serial clock input/output (3-wire serial I/O2) SCL0Note P27/SCK0 Serial clock input/output (I<sup>2</sup>C bus) P02/INTP2 NMI Input Non-maskable interrupt request input P00 INTP0 External interrupt request input INTP1 P01 INTP2 P02/NMI INTP3 P03 INTP4 P04 INTP5 P05 **PCL** Output P23 Clock output (for trimming main system clock and subsystem clock) BUZ P24 Output Buzzer output RTP0 to RTP7 P120 to P127 Output Real-time output port that outputs data in synchronization with trigger AD0 to AD7 I/O P40 to P47 Low-order address/data bus when external memory is connected P50 to P57 A8 to A15 Output Middle-order address bus when external memory is connected A16 to A19 P60 to P63 High-order address bus when external memory is connected

**Note** This function is available in  $\mu$ PD784255Y Subseries only.

# 5.2 Pins Other Than Port Pins (2/2)

www.datasheet4

| Pin Name         | I/O              | Alternate Function | Function                                                                                                                                                                                  |  |

|------------------|------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RD               | Output           | P64                | Strobe signal output for read operation of external memory                                                                                                                                |  |

| WR               |                  | P65                | Strobe signal output for write operation of external memory                                                                                                                               |  |

| WAIT             | Input            | P66                | To insert wait state(s) when external memory is accessed                                                                                                                                  |  |

| ASTB             | Output           | P67                | Strobe output to externally latch address information output to ports 4 to 6 to access external memory                                                                                    |  |

| EXA              | Output           | P37                | External access status output                                                                                                                                                             |  |

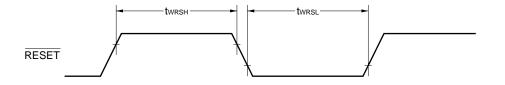

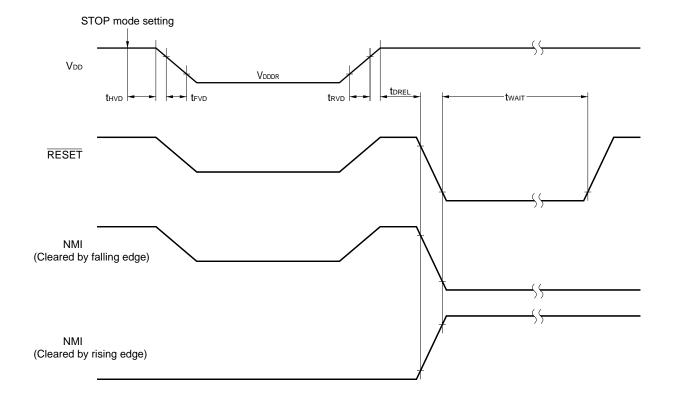

| RESET            | Input            | _                  | System reset input                                                                                                                                                                        |  |

| X1               | Input            | _                  | To connect main system clock oscillation crystal                                                                                                                                          |  |

| X2               | -                |                    |                                                                                                                                                                                           |  |

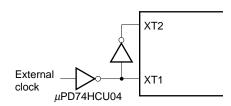

| XT1              | Input            | _                  | To connect subsystem clock oscillation crystal                                                                                                                                            |  |

| XT2              | -                |                    |                                                                                                                                                                                           |  |

| ANI0 to ANI7     | Input            | P10 to P17         | Analog voltage input for A/D converter                                                                                                                                                    |  |

| ANO0, ANO1       | Output           | P130, P131         | Analog voltage output for D/A converter                                                                                                                                                   |  |

| AVREF1           | _                | _                  | To apply reference voltage for D/A converter                                                                                                                                              |  |

| AV <sub>DD</sub> |                  |                    | Positive power supply for A/D converter. Connected to VDDO.                                                                                                                               |  |

| AVss             |                  |                    | GND for A/D converter and D/A converter. Connected to Vsso.                                                                                                                               |  |

| V <sub>DD0</sub> |                  |                    | Positive power supply for port block                                                                                                                                                      |  |

| Vsso             |                  |                    | GND potential for port block                                                                                                                                                              |  |

| V <sub>DD1</sub> | V <sub>DD1</sub> |                    | Positive power supply (except port block)                                                                                                                                                 |  |

| Vss1             |                  |                    | GND potential (except port block)                                                                                                                                                         |  |

| TEST             |                  |                    | Connect this pin to Vsso directly or via pull-down resistor. For the pull-down connection, use of a resistor with a resistance ranging from 470 $\Omega$ to 10 k $\Omega$ is recommended. |  |

\*

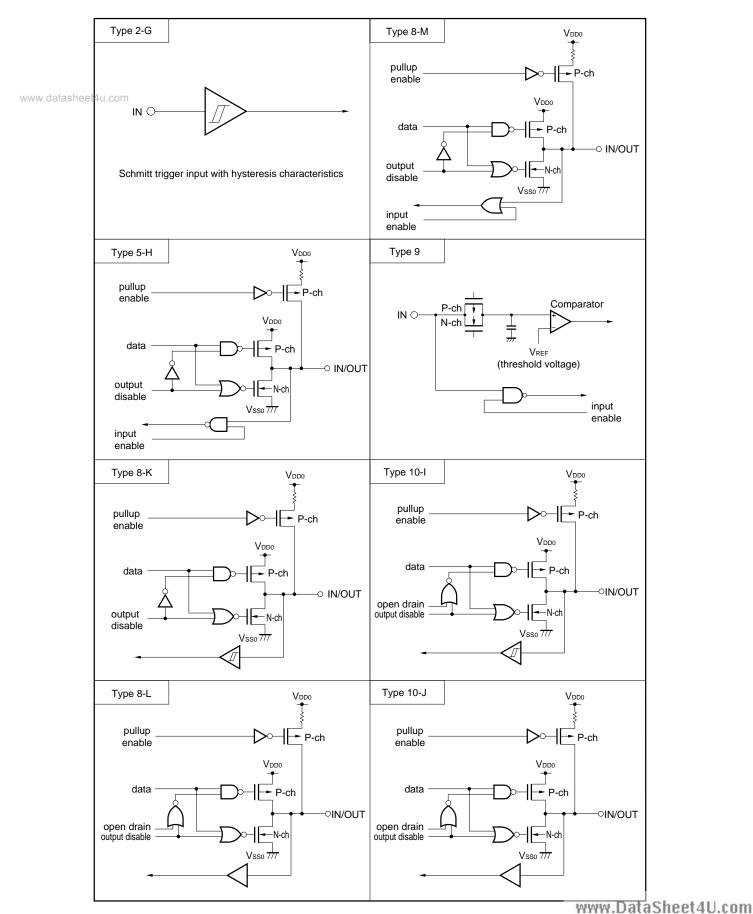

#### 5.3 I/O Circuit Type of Respective Pins and Recommended Connections of Unused Pins

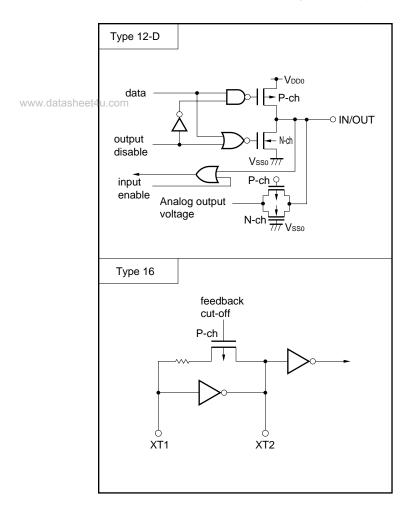

Table 5-1 shows symbols indicating the I/O circuit types of the respective pins and the recommended connection of unused pins.

For the circuit diagram of each type of I/O circuit, refer to Figure 5-1.

#### ★ Table 5-1. I/O Circuit Type of Respective Pins and Recommended Connections of Unused Pins (1/2)

www.datasheet4u.com

| Pin Name                       | I/O Circuit Type | I/O   | Recommended Connections of Unused Pins              |

|--------------------------------|------------------|-------|-----------------------------------------------------|

| P00/INTP0                      | 8-K              | I/O   | Input : Individually connected to Vsso via resistor |

| P01/INTP1                      |                  |       | Output: Open                                        |

| P02/INTP2/NMI                  |                  |       |                                                     |

| P03/INTP3 to P05/INTP5         |                  |       |                                                     |

| P10/ANI0 to P17/ANI7           | 9                | Input | Connected to Vsso or VDDO                           |

| P20/RxD1/SI1                   | 10-l             | I/O   | Input : Individually connected to Vsso via resistor |

| P21/TxD1/SO1                   | 10-J             |       | Output: Open                                        |

| P22/ASCK1/SCK1                 | 10-I             |       |                                                     |

| P23/PCL                        | 10-J             |       |                                                     |

| P24/BUZ                        |                  |       |                                                     |

| P25/SDA0 <sup>Note</sup> /SI0  | 10-I             |       |                                                     |

| P26/SO0                        | 10-J             |       |                                                     |

| P27/SCL0 <sup>Note</sup> /SCK0 | 10-I             |       |                                                     |

| P30/TO0 to P32/TO2             | 8-M              |       |                                                     |

| P33/TI1, P34/TI2               | 8-K              |       |                                                     |

| P35/TI00, P36/TI01             | 8-L              |       |                                                     |

| P37/EXA                        | 8-M              |       |                                                     |

| P40/AD0 to P47/AD7             | 5-H              |       |                                                     |

| P50/A8 to P57/A15              |                  |       |                                                     |

| P60/A16 to P63/A19             |                  |       |                                                     |

| P64/RD                         |                  |       |                                                     |

| P65/WR                         |                  |       |                                                     |

| P66/WAIT                       |                  |       |                                                     |

| P67/ASTB                       |                  |       |                                                     |

| P70/RxD2/SI2                   | 8-K              |       |                                                     |

| P71/TxD2/SO2                   | 8-L              |       |                                                     |

| P72/ASCK2/SCK2                 | 8-K              |       |                                                     |

Note This function is available in  $\mu$ PD784255Y Subseries only.

**Remark** Because the circuit type numbers are standardized among the 78K Series products, they are not sequential in some models (i.e., some circuits are not provided).

#### **★** Table 5-1. I/O Circuit Type of Respective Pins and Recommended Connections of Unused Pins (2/2)

|                | Pin Name                  | I/O Circuit Type | I/O   | Recommended Connections of Unused Pins              |

|----------------|---------------------------|------------------|-------|-----------------------------------------------------|

|                | P120/RTP0 to P127/RTP7    | 8-K              | I/O   | Input : Individually connected to Vsso via resistor |

|                | P130/ANO0, P131/ANO1      | 12-D             |       | Output: Open                                        |

| www.datasheet4 | RESET                     | 2-G              | Input | _                                                   |

|                | XT1                       | 16               |       | Connected to Vsso                                   |

|                | XT2                       |                  | -     | Open                                                |

|                | AV <sub>REF1</sub>        | -                |       | Connected to VDD0                                   |

|                | AVDD                      |                  |       |                                                     |

|                | AVss                      |                  | ,     | Connected to Vsso                                   |

|                | TEST/V <sub>PP</sub> Note |                  | ,     | Directly connected to Vsso                          |

**Note** VPP pin is available in  $\mu$ PD78F4225, 78F4255Y only.

**Remark** Because the circuit type numbers are standardized among the 78K Series products, they are not sequential in some models (i.e., some circuits are not provided).

www.DataSheet4U.com

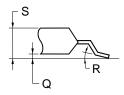

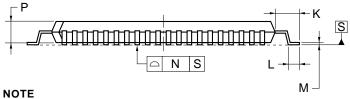

Figure 5-1. Types of Pin I/O Circuits (1/2)

Figure 5-1. Types of Pin I/O Circuits (2/2)

#### 6. CPU ARCHITECTURE

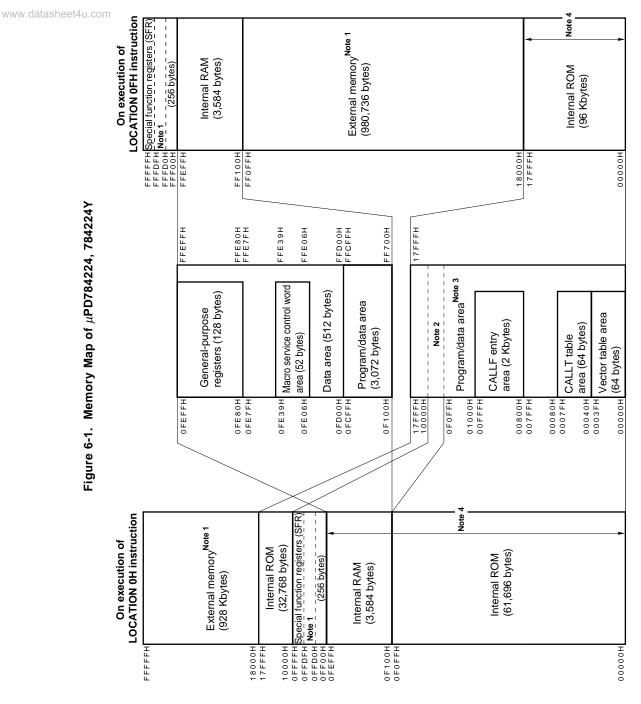

#### 6.1 Memory Space

A memory space of 1 Mbyte can be accessed. Mapping of the internal data area (special function registers and internal RAM) can be specified the LOCATION instruction. The LOCATION instruction must be always executed after RESET cancellation, and must not be used more than once.

www.datasheet4u.com

#### (1) When LOCATION 0H instruction is executed

#### Internal memory

The internal data area and internal ROM area are mapped as follows:

| Part Number              | Internal Data Area | Internal ROM Area                    |

|--------------------------|--------------------|--------------------------------------|

| μPD784224,<br>μPD784224Y | 0F100H to 0FFFFH   | 00000H to 0F0FFH<br>10000H to 17FFFH |

| μPD784225,<br>μPD784225Y | 0EE00H to 0FFFFH   | 00000H to 0EDFFH<br>10000H to 1FFFFH |

# Caution The following areas that overlap the internal data area of the internal ROM cannot be used when the LOCATION 0H instruction is executed.

| Part Number              | Unusable Area                  |

|--------------------------|--------------------------------|

| μPD784224,<br>μPD784224Y | 0F100H to 0FFFFH (3,840 bytes) |

| μPD784225,<br>μPD784225Y | 0EE00H to 0FFFFH (4,608 bytes) |

#### External memory

The external memory is accessed in external memory expansion mode.

#### (2) When LOCATION 0FH instruction is executed

#### • Internal memory

The internal data area and internal ROM area are mapped as follows:

| Part Number              | Internal Data Area | Internal ROM Area |

|--------------------------|--------------------|-------------------|

| μPD784224,<br>μPD784224Y | FF100H to FFFFFH   | 00000H to 17FFFH  |

| μPD784225,<br>μPD784225Y | FEE00H to FFFFFH   | 00000H to 1FFFFH  |

#### • External memory

The external memory is accessed in external memory expansion mode.

Figure 6-1. Memory Map of  $\mu$ PD784224, 784224Y

Accessed in external memory expansion mode. Notes

This 3,840-byte area can be used as an internal ROM only when the LOCATION 0FH instruction is executed. 6

On execution of LOCATION 0H instruction: 94,464 bytes, on execution of LOCATION 0FH instruction: 98,304 bytes რ

www.datasheet4u.com

Note 4 **LOCATION 0FH instruction** FFFFFH Special function registers (SFR) External memory Note 1 On execution of Internal RAM (4,352 bytes) \_(256 bytes) (912,896 bytes) Internal ROM (128 Kbytes) FEEOOH 20000H 1FFFFH Figure 6-2. Memory Map of  $\mu$ PD784225, 784225Y FFE80H FFE7FH FFD00H FFCFFH 1 FFFFH FFE39H FEE00H FFEFFH FE06H Program/data area Macro service control word Data area (512 bytes) registers (128 bytes) Program/data area (3,840 bytes) General-purpose Vector table area Note 2 area (2 Kbytes) area (64 bytes) CALLF entry area (52 bytes) CALLT table (64 bytes) 00040H 0003FH 0 FCFFH 1 FFFFH 1 0 0 0 0 H 01000H 00FFFH 0 FE 8 0 H 0 FE 7 FH 0 EDFFH 0 FE 0 6 H 0000H OFEFFH 0 FE39H 0EE00H 00800H 007FFH 00080H 0007FH 10000H

OFFFH Special function registers (SFR)

OFFDH Note 1 - - - - - OFFDH OFF PH

OFF PH Note 4 **LOCATION 0H instruction** External memory Note 1 (896 Kbytes) On execution of (65,536 bytes) Internal ROM (60,928 bytes) Internal ROM Internal RAM (4,352 bytes)

20000H 1FFFFH

Accessed in external memory expansion mode. <del>.</del> Notes

H00000

00000

OEE00H OEDFFH

This 4,608-byte area can be used as an internal ROM only when the LOCATION 0FH instruction is executed. 'n

On execution of LOCATION 0H instruction: 126,464 bytes, on execution of LOCATION 0FH instruction: 131,072 bytes რ

Base area and entry area for reset or interrupt. However, the internal RAM area is not used as a reset entry area. 4.

#### 6.2 CPU Registers

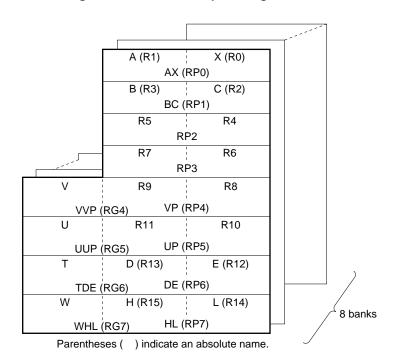

#### 6.2.1 General-purpose registers

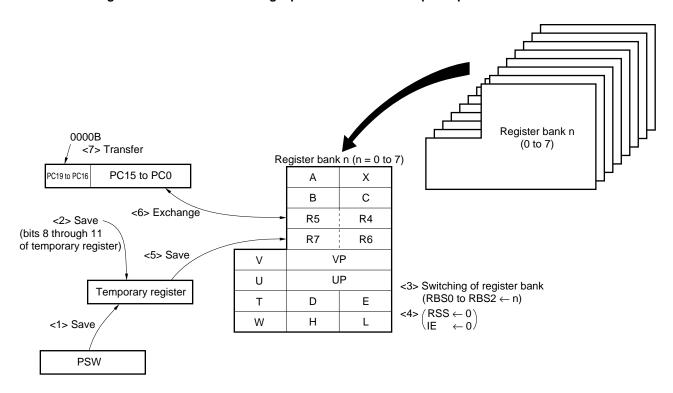

Sixteen 8-bit general-purpose registers are available. Two 8-bit registers can be also used in pairs as a 16-bit register. Of the 16-bit registers, four can be used in combination with an 8-bit register for address expansion as 24-bit address specification registers.

www.datasheet4u.cEight banks of these registers are available which can be selected by using software or the context switching function.

The general-purpose registers except V, U, T, and W registers for address expansion are mapped to the internal RAM.

Figure 6-3. General-Purpose Register Format

Caution Registers R4, R5, R6, R7, RP2, and RP3 can be used as X, A, C, B, AX, and BC registers, respectively, by setting the RSS bit of the PSW to 1. However, use this function only for recycling the program of the 78K/III Series.

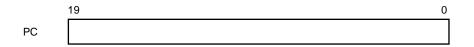

#### 6.2.2 Control registers

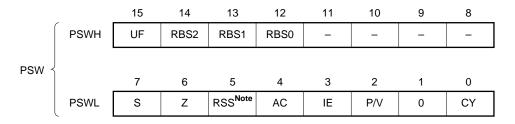

#### (1) Program counter (PC)

The program counter is a 20-bit register whose contents are automatically updated when the program is executed.

www.datasheet4u.com

Figure 6-4. Program Counter (PC) Format

#### (2) Program status word (PSW)

This register holds the statuses of the CPU. Its contents are automatically updated when the program is executed.

Figure 6-5. Program Status Word (PSW) Format

**Note** This flag is provided to maintain compatibility with the 78K/III Series. Be sure to clear this flag to 0, except when the software for the 78K/III Series is used.

#### (3) Stack pointer (SP)

This is a 24-bit pointer that holds the first address of the stack. Be sure to write 0 to the higher 4 bits of this pointer.

Figure 6-6. Stack Pointer (SP) Format

#### 6.2.3 Special function registers (SFRs)

The special function registers, such as the mode registers and control registers of the internal peripheral hardware, are registers to which special functions are allocated. These registers are mapped to a 256-byte space of addresses 0FF00H to 0FFFFH<sup>Note</sup>.

**Note** On execution of the LOCATION 0H instruction. FFF00H to FFFFH on execution of the LOCATION 0FH www.datasheet4u.com instruction.

Caution Do not access an address in this area to which no SFR is allocated. If such an address is accessed by mistake, the  $\mu$ PD784225 may be in the deadlock status. This deadlock status can be cleared only by inputting the  $\overline{\text{RESET}}$  signal.

Table 6-1 lists the special function registers (SFRs). The meanings of the symbols in this table are as follows:

| • | Symbol | Symbol indicating an SFR.   | This symbol is reserved for NEC's assembler        |

|---|--------|-----------------------------|----------------------------------------------------|

|   |        | (RA78K4). It can be used an | sfr variable by the #pragma sfr directive with the |

|   |        | C compiler (CC78K4).        |                                                    |

R/W : Read/writeR : Read-onlyW : Write-only

• Bit units for manipulation .. Bit units in which the value of the SFR can be manipulated.

SFRs that can be manipulated in 16-bit units can be described as the operand sfrp of an instruction. To specify the address of this SFR, describe an even

address.

SFRs that can be manipulated in 1-bit units can be described as the operand of

a bit manipulation instruction.

Table 6-1. Special Function Register (SFR) List (1/4)

| Address No.                            | Special Function Register (SFR) Name | Symbol | R/W | Bit Unit | s for Man | ipulation | At Reset  |

|----------------------------------------|--------------------------------------|--------|-----|----------|-----------|-----------|-----------|

|                                        |                                      |        |     | 1 Bit    | 8 Bits    | 16 Bits   |           |

| 0FF00H                                 | Port 0                               | P0     | R/W | 0        | 0         | _         | 00HNote 2 |

| 0FF01H                                 | Port 1                               | P1     | R   | 0        | 0         | _         |           |

| ww.da <del>tasheet4u.d</del><br>0FF02H | Port 2                               | P2     | R/W | 0        | 0         | _         |           |

| 0FF03H                                 | Port 3                               | P3     |     | 0        | 0         | _         |           |

| 0FF04H                                 | Port 4                               | P4     |     | 0        | 0         | _         |           |

| 0FF05H                                 | Port 5                               | P5     |     | 0        | 0         |           |           |

| 0FF06H                                 | Port 6                               | P6     |     | 0        | 0         | _         |           |

| 0FF07H                                 | Port 7                               | P7     |     | 0        | 0         | _         |           |

| 0FF0CH                                 | Port 12                              | P12    |     | 0        | 0         | _         |           |

| 0FF0DH                                 | Port 13                              | P13    |     | 0        | 0         | _         |           |

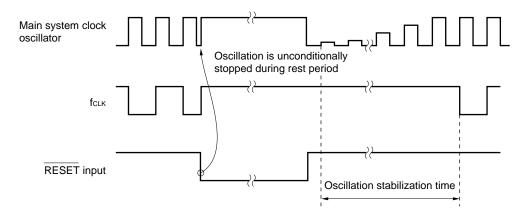

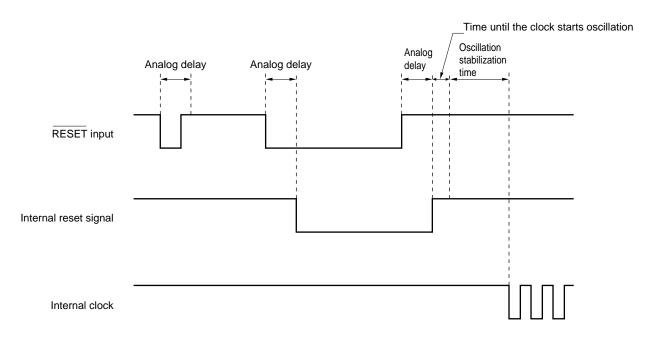

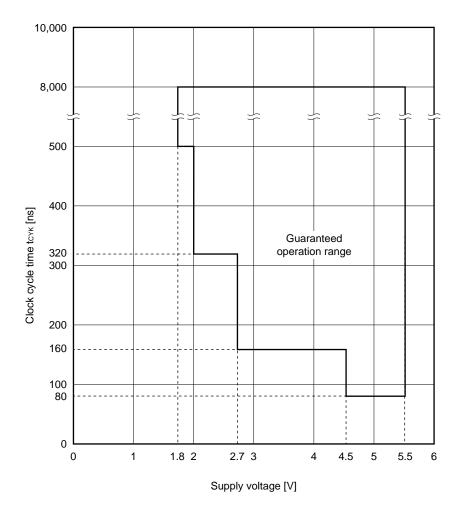

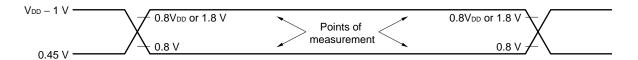

| 0FF10H                                 | 16-bit timer counter                 | TM0    | R   | _        | _         | 0         | 0000H     |