### **General Description**

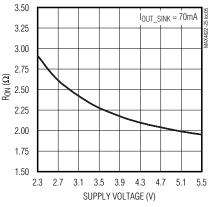

The MAX4822–MAX4825 8-channel relay drivers offer built-in kickback protection and drive +3V/+5V nonlatching or dual-coil-latching relays. Each independent open-drain output features a 2.7 $\Omega$  (typ) on-resistance and is guaranteed to sink 70mA (min) of load current. These devices consume less than 300µA (max) quies-cent current and have 1µA output off-leakage current. A Zener-kickback-protection circuit significantly reduces recovery time in applications where switching speed is critical.

The MAX4822/MAX4824 feature a unique power-save mode where the relay current, after activation, can be reduced to a level just above the relay hold-current threshold. This mode keeps the relay activated while significantly reducing the power consumption.

The MAX4822/MAX4823 feature a 10MHz SPI™-/ QSPI™-/MICROWIRE™-compatible serial interface. Input data is shifted into a shift register and latched to the outputs when CS transitions from low to high. Each data bit in the shift register corresponds to a specific output, allowing independent control of all outputs.

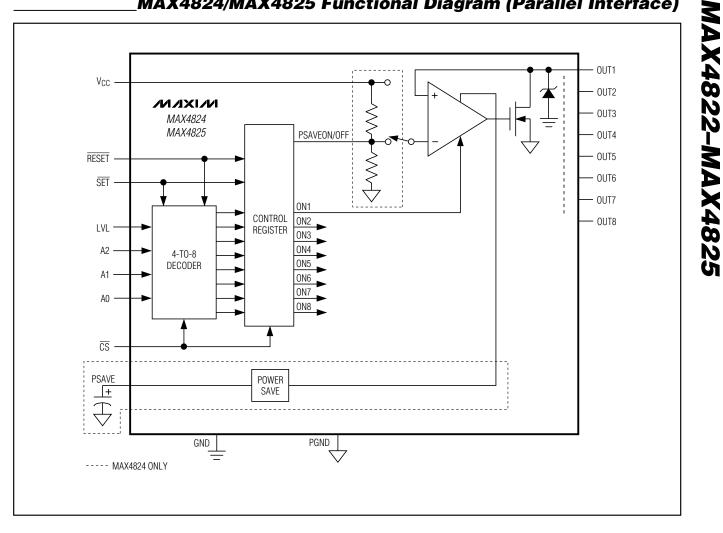

The MAX4824/MAX4825 feature a 4-bit parallel-input interface. The first 3 bits (A0, A1, A2) determine the output address, and the fourth bit (LVL) determines whether the selected output is switched on or off. Data is latched to the outputs when  $\overline{\text{CS}}$  transitions from low to high.

The MAX4822–MAX4825 feature separate set and reset functions, allowing turn-on or turn-off of all outputs simultaneously with a single control line. Built-in hysteresis (Schmidt trigger) on all digital inputs allows these devices to be used with slow-rising and falling signals, such as those from optocouplers or RC power-up initialization circuits. The MAX4822–MAX4825 are available in space-saving 4mm x 4mm, 20-pin thin QFN packages. They are specified over the -40°C to +85°C extended temperature range.

\_ Applications

ATE Equipment

DSL Redundancy Protection (ADSL/VDSL/HDSL)

T1/E1 Redundancy Protection

T3/E3 Redundancy Protection

Industrial Equipment

Test Equipment (Oscilloscopes, Spectrum Analyzers)

SPI is a trademark of Motorola, Inc. QSPI is a trademark of Motorola, Inc. MICROWIRE is a trademark of National Semiconductor Corp.

#### **\_ Features**

- Built-In Zener Kickback Protection for Fast Recovery

- Programmable Power-Save Mode Reduces Relay Power Consumption (MAX4822/MAX4824)

- 10MHz SPI-/QSPI-/MICROWIRE-Compatible Serial Interface

- Eight Independent Output Channels

- Drive +3V and +5V Relays

- ♦ Guaranteed 70mA (min) Coil Drive Current

- Guaranteed 5Ω (max) RON

- ♦ SET / RESET Functions to Turn On/Off All Outputs Simultaneously

- Serial Digital Output for Daisy Chaining

- Optional Parallel Interface (MAX4824/MAX4825)

- ♦ Low 300µA (max) Quiescent Supply Current

- Space-Saving, 4mm x 4mm, 20-Pin TQFN Package

### **Ordering Information**

| PART       | TEMP RANGE     | P RANGE PIN-<br>PACKAGE |         |

|------------|----------------|-------------------------|---------|

| MAX4822ETP | -40°C to +85°C | 20 TQFN-EP*             | T2044-3 |

| MAX4823ETP | -40°C to +85°C | 20 TQFN-EP*             | T2044-3 |

| MAX4824ETP | -40°C to +85°C | 20 TQFN-EP*             | T2044-3 |

| MAX4825ETP | -40°C to +85°C | 20 TQFN-EP*             | T2044-3 |

\*For maximum heat dissipation, packages have an exposed pad (EP) on the bottom. Solder exposed pad to GND.

### **Selector Guide**

| PART    | INTERFACE | POWER SAVE |

|---------|-----------|------------|

| MAX4822 | Serial    | Yes        |

| MAX4823 | Serial    | No         |

| MAX4824 | Parallel  | Yes        |

| MAX4825 | Parallel  | No         |

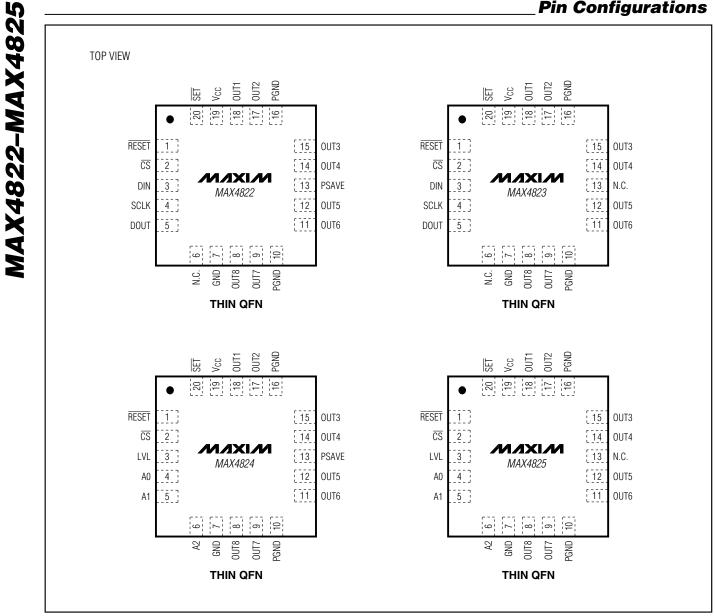

Pin Configurations appear at end of data sheet.

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> 0.3V to                           | +6.0V   |

|---------------------------------------------------|---------|

| OUT0.3V to                                        | 5 +11V  |

| CS, SCLK, DIN, SET, RESET, A0, A1, A2, LVL0.3V to | +6.0V   |

| DOUT0.3V to (V <sub>CC</sub> +                    | ⊦ 0.3V) |

| PSAVE0.3V to (V <sub>CC</sub> +                   | ⊦ 0.3V) |

| Continuous OUT_ Current (all outputs turned on)   | 150mA   |

| Continuous OUT_ Current (single output turned on) | 300mA   |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

|-------------------------------------------------------|----------------|

| 20-Lead Thin QFN (derate 16.9mW/°C above              | +70°C)1350mW   |

| Operating Temperature Range                           | 40°C to +85°C  |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 65°C to +150°C |

| Soldering Temperature (10s)                           | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

(V<sub>CC</sub> = +2.7V to +5.5V,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at V<sub>CC</sub> = 2.7V,  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                  | SYMBOL                             | CONDITIONS                                                       |                 | MIN                      | ТҮР   | MAX  | UNITS |  |

|----------------------------|------------------------------------|------------------------------------------------------------------|-----------------|--------------------------|-------|------|-------|--|

| Operating Voltage          | V <sub>CC</sub>                    |                                                                  |                 | 2.3                      |       | 5.5  | V     |  |

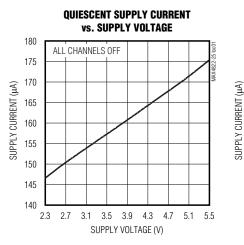

| Quiescent Current          |                                    | I <sub>OUT_</sub> = 0,                                           | $V_{CC} = 3.6V$ |                          | 160   | 300  |       |  |

| Quiescent Current          | Icc                                | logic inputs = 0 or $V_{CC}$                                     | $V_{CC} = 5.5V$ |                          | 180   | 300  | μA    |  |

| Dynamic Supply Current     | ID                                 | f <sub>SCLK</sub> =10MHz, C <sub>DOUT</sub> = 50pF               | $V_{CC} = 3.6V$ |                          | 1.2   |      | mA    |  |

| Dynamic Supply Current     | цD                                 | SCLK  =  OMHZ, CDOU  = SOPF                                      | $V_{CC} = 5.5V$ |                          | 1.6   |      | ШA    |  |

| Thermal Shutdown           |                                    | Power-save disable threshold (                                   | Note 2)         |                          | +130  |      | °C    |  |

| Thermal Shutdown           |                                    | Output disable threshold (Note                                   | 3)              |                          | +150  |      | υ     |  |

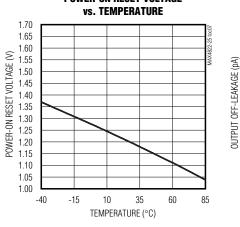

| Power-On Reset             |                                    | Transform from high voltage to                                   | low voltage     | 0.6                      | 1.2   | 2.0  | V     |  |

| Power-On Reset Hysteresis  |                                    |                                                                  |                 |                          | 140   |      | mV    |  |

| DIGITAL INPUTS (SCLK, DIN, | <u>CS,</u> LVL, A0, A <sup>-</sup> | 1, A2, RESET, SET)                                               |                 |                          |       |      |       |  |

| Input Logia High Voltage   | \/                                 | V <sub>CC</sub> = 2.7V to 3.6V<br>V <sub>CC</sub> = 4.2V to 5.5V |                 | 2.0                      |       |      | v     |  |

| Input Logic-High Voltage   | VIH                                |                                                                  |                 | 2.4                      |       |      | V     |  |

| Input Logic-Low Voltage    | Mu                                 | $V_{CC} = 2.7V \text{ to } 3.6V$                                 |                 |                          |       | 0.6  | V     |  |

| Input Logic-Low Voltage    | VIL                                | $V_{CC} = 4.2V$ to 5.5V                                          |                 |                          |       | 0.8  | v     |  |

| Input Logic Hysteresis     | VHYST                              |                                                                  |                 |                          | 150   |      | mV    |  |

| Input Leakage Current      | ILEAK                              | Input voltages = 0 or 5.5V                                       |                 | -1.0                     | +0.01 | +1.0 | μA    |  |

| Input Capacitance          | C <sub>IN</sub>                    |                                                                  |                 |                          | 5     |      | pF    |  |

| DIGITAL OUTPUT (DOUT)      |                                    |                                                                  |                 |                          |       |      |       |  |

| DOUT Low Voltage           | Vol                                | I <sub>SINK</sub> = 6mA                                          |                 |                          |       | 0.4  | V     |  |

| DOUT High Voltage          | Voh                                | ISOURCE = 0.5mA                                                  |                 | V <sub>CC</sub> -<br>0.5 |       |      | V     |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

(V<sub>CC</sub> = +2.7V to +5.5V,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at V<sub>CC</sub> = 2.7V,  $T_A$  = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                         | SYMBOL          |                                        | CONDITIONS                                                            | MIN                       | ТҮР                      | MAX                       | UNITS |

|---------------------------------------------------|-----------------|----------------------------------------|-----------------------------------------------------------------------|---------------------------|--------------------------|---------------------------|-------|

| <b>RELAY OUTPUT DRIVERS (OU</b>                   | T1–OUT8)        |                                        |                                                                       | ·                         |                          |                           |       |

|                                                   |                 |                                        | PS = 001                                                              | 0.65 x<br>V <sub>CC</sub> | 0.7 x<br>V <sub>CC</sub> | 0.75 x<br>V <sub>CC</sub> |       |

|                                                   |                 |                                        | PS = 010                                                              | 0.55 x<br>V <sub>CC</sub> | 0.6 x<br>V <sub>CC</sub> | 0.65 x<br>V <sub>CC</sub> |       |

|                                                   |                 |                                        | PS = 011                                                              | 0.45 x<br>V <sub>CC</sub> | 0.5 x<br>V <sub>CC</sub> | 0.55 x<br>V <sub>CC</sub> | V     |

| OUT_ Drive Voltage,<br>Power-Save On<br>(MAX4822) | VOUTPS_         | V <sub>CC</sub> = 2.7V<br>(Note 4)     | PS = 100                                                              | 0.35 x<br>V <sub>CC</sub> | 0.4 x<br>V <sub>CC</sub> | 0.45 x<br>V <sub>CC</sub> |       |

|                                                   |                 |                                        | PS = 101                                                              | 0.25 x<br>V <sub>CC</sub> | 0.3 x<br>V <sub>CC</sub> | 0.35 x<br>V <sub>CC</sub> |       |

|                                                   |                 |                                        | PS = 110                                                              | 0.15 x<br>V <sub>CC</sub> | 0.2 x<br>V <sub>CC</sub> | 0.25 x<br>V <sub>CC</sub> |       |

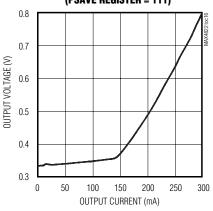

|                                                   |                 |                                        | PS = 111                                                              | 0.05 x<br>V <sub>CC</sub> | 0.1 x<br>Vcc             | 0.15 x<br>Vcc             |       |

| OUT_ Drive Voltage,<br>Power-Save On (MAX4824)    | VOUTPS_         | V <sub>CC</sub> = 2.7V (Note 4)        |                                                                       | 0.35 x<br>V <sub>CC</sub> | 0.4 x<br>V <sub>CC</sub> | 0.45 x<br>V <sub>CC</sub> | V     |

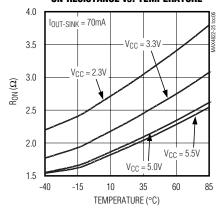

| OUT_ On-Resistance                                | R <sub>ON</sub> | $V_{CC} = 2.7 V, I$                    | OUT_ = 70mA                                                           |                           | 2.7                      | 5.0                       | Ω     |

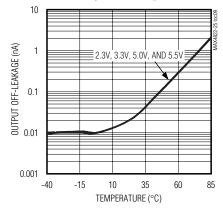

| OUT_ Off-Leakage Current                          | ILEAK           | Vout_ = Vcc                            | , all outputs off                                                     | -1                        |                          | +1                        | μA    |

| Zener Clamping Voltage                            | VCLAMP          | $I_{OUT} = 70 m/$                      | A (Note 5)                                                            | 7.0                       | 9                        | 10.5                      | V     |

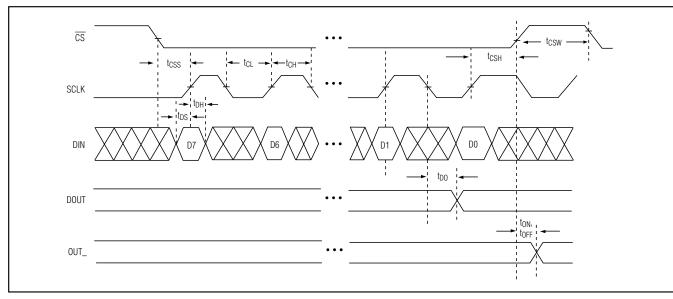

| SPI TIMING (MAX4822/MAX482                        | 3)              |                                        |                                                                       |                           |                          |                           |       |

| Turn-On Time (OUT_)                               | ton             | From rising e<br>C <sub>L</sub> = 50pF | dge of $\overline{\text{CS}}$ , $\text{R}_{\text{L}}$ = 50 $\Omega$ , |                           |                          | 1.0                       | μs    |

| Turn-Off Time (OUT_)                              | tOFF            | From rising e<br>C <sub>L</sub> = 50pF | dge of $\overline{\text{CS}}$ , $\text{R}_{\text{L}}$ = 50 $\Omega$ , |                           |                          | 3.0                       | μs    |

| SCLK Frequency                                    | <b>f</b> SCLK   |                                        |                                                                       | 0                         |                          | 10                        | MHz   |

| Cycle Time                                        | tCH + tCL       |                                        |                                                                       | 100                       |                          |                           | ns    |

| CS Fall-to-SCLK Rise Setup                        | tcss            |                                        |                                                                       | 50                        |                          |                           | ns    |

| CS Rise-to-SCLK Hold                              | tCSH            |                                        |                                                                       | 50                        |                          |                           | ns    |

| SCLK High Time                                    | tсн             |                                        |                                                                       | 40                        |                          |                           | ns    |

| SCLK Low Time                                     | tCL             |                                        |                                                                       | 40                        |                          |                           | ns    |

| Data Setup Time                                   | tDS             |                                        |                                                                       | 20                        |                          |                           | ns    |

### **ELECTRICAL CHARACTERISTICS (continued)**

(V<sub>CC</sub> = +2.7V to +5.5V, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at V<sub>CC</sub> = 2.7V, T<sub>A</sub> = +25°C, unless otherwise noted.) (Note 1)

| PARAMETER                                     | SYMBOL          | CONDITIONS                                                                                       | MIN | ТҮР | MAX | UNITS |

|-----------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Data Hold Time                                | t <sub>DH</sub> |                                                                                                  | 0   |     |     | ns    |

| SCLK Fall to DOUT Valid                       | t <sub>DO</sub> | 50% of SCLK to (V <sub>IH</sub> , V <sub>IL</sub> of D <sub>IN</sub> ),<br>C <sub>L</sub> = 50pF |     | 17  | 28  | ns    |

| Rise Time (DIN, SCLK, CS, SET, RESET)         | tSCR            | 20% of V <sub>CC</sub> to 70% of V <sub>CC</sub> , $C_L = 50pF$<br>(Note 6)                      |     |     | 2   | μs    |

| Fall Time (DIN, SCLK, CS, RESET, SET)         | tSCF            | 20% of V <sub>CC</sub> to 70% of V <sub>CC</sub> , $C_L = 50pF$<br>(Note 6)                      |     |     | 2   | μs    |

| RESET Minimum Pulse Width                     | t <sub>RW</sub> |                                                                                                  | 70  |     |     | ns    |

| SET Minimum Pulse Width                       | tsw             |                                                                                                  | 70  |     |     | ns    |

| CS Minimum Pulse Width                        | tcsw            |                                                                                                  | 40  |     |     | ns    |

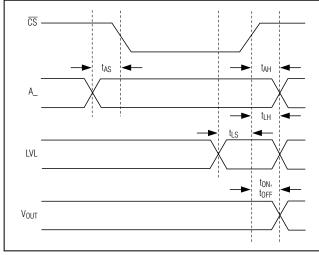

| PARALLEL TIMING (MAX4824/                     | MAX4825)        |                                                                                                  |     |     |     |       |

| Turn-On Time                                  | ton             | From rising edge of $\overline{CS}$ , $R_L = 50\Omega$ , $C_L = 50pF$                            |     |     | 1   | μs    |

| Turn-Off Time                                 | tOFF            | From rising edge of $\overline{CS}$ , $R_L = 50\Omega$ , $C_L = 50pF$                            |     |     | 3   | μs    |

| LVL Setup Time                                | tLS             |                                                                                                  | 20  |     |     | ns    |

| LVL Hold Time                                 | tLH             |                                                                                                  | 0   |     |     | ns    |

| Address to CS Setup Time                      | t <sub>AS</sub> |                                                                                                  | 20  |     |     | ns    |

| Address to $\overline{\text{CS}}$ Hold Time   | tah             |                                                                                                  | 0   |     |     | ns    |

| Rise Time (A2, A1, A0, LVL)                   | tscr            | 20% of V <sub>CC</sub> to 70% of V <sub>CC</sub> , $C_L = 50pF$ (Note 6)                         |     |     | 2   | μs    |

| Fall Time (A2, A1, A0, LVL)                   | tSCF            | 20% of V <sub>CC</sub> to 70% of V <sub>CC</sub> , $C_L = 50pF$<br>(Note 6)                      |     |     | 2   | μs    |

| RESET Pulse Width                             | t <sub>RW</sub> |                                                                                                  | 70  |     |     | ns    |

| SET Pulse Width                               | tsw             |                                                                                                  | 70  |     |     | ns    |

| CS Minimum Pulse Width                        | tcsw            |                                                                                                  | 40  |     |     | ns    |

| POWER-SAVE TIMING (MAX48                      | 22/MAX4824)     |                                                                                                  |     |     |     |       |

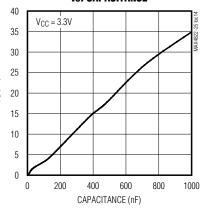

| Power-Save Delay Time                         | tps             | Variation from typical value, $C_L = 100$ nF (Note 7)                                            | 1.6 | 3.2 | 5.4 | ms    |

| Minimum PSAVE Low Time to<br>Power-Save Reset | tpsr            |                                                                                                  |     | 2   | 3.5 | ms    |

Note 1: Specifications at -40°C are guaranteed by design and not production tested.

Note 2: Thermal shutdown disables power save from all channels to reduce power dissipation inside the device.

Note 3: Thermal shutdown turns off all channels.

Note 4: The circuit can set the output voltage in power-save mode only if IOUT x RON < VOUTP.

Note 5: After relay turn-off, inductive kickback can momentarily cause the OUT\_ voltage to exceed V<sub>CC</sub>. This is considered part of normal operation and does not damage the device.

Note 6: Guaranteed by design.

Note 7: For other capacitance values, use the equation  $t_{PS} = 32 \times C$ .

**QUIESCENT SUPPLY CURRENT**

vs. TEMPERATURE

#### $(V_{CC} = 3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

**QUIESCENT SUPPLY CURRENT**

vs. LOGIC-INPUT VOLTAGE

$V_{CC} = 3.3V$

2

1

ALL LOGIC INPUTS

$V_{CC} = 5.5V$

CONNECTED

1100

1000

900

800

700

600 500

400

300

200

100

0

0

SUPPLY CURRENT (µA)

200  $V_{CC} = 5.5V$ 190  $V_{CC} = 5.0V$ 180 170 160 150 140  $V_{CC} = 3.3V$ 130 = 2.3 120 110 100 -40 -15 10 35 60 85 TEMPERATURE (°C)

vs. FREQUENCY 2.00  $C_{DOUT} = 50 pF$ 1.80 DVNAMIC SUPPLY CURRENT (mA) 1.60 1.20 1.00 0.80 0.60  $V_{CC} = 5.5V$  $V_{CC} = 3.6V$ 0.40 0.20 1 2 3 4 5 6 7 8 9 10

DYNAMIC SUPPLY CURRENT

MAX4822-MAX4825

**Typical Operating Characteristics**

#### **ON-RESISTANCE vs. TEMPERATURE**

FREQUENCY (MHz)

**OUTPUT OFF-LEAKAGE CURRENT** vs. TEMPERATURE

3 4 5 LOGIC-INPUT VOLTAGE (V) **POWER-ON RESET VOLTAGE**

6

5

4

3

2

1

0

2.3

2.7 3.1

**ON-RESISTANCE vs. SUPPLY VOLTAGE**

**OUTPUT OFF-LEAKAGE CURRENT**

vs. SUPPLY VOLTAGE

3.5 3.9 4.3

SUPPLY VOLTAGE (V)

4.7 5.1 5.5

5

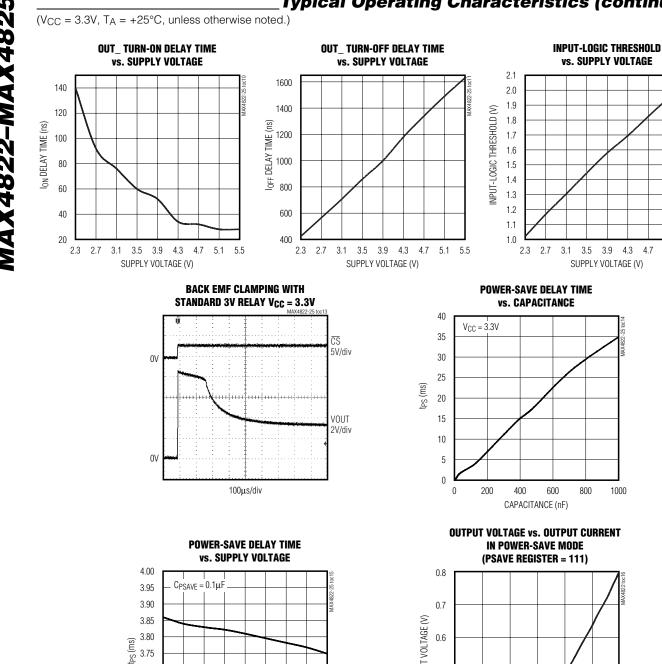

### **Typical Operating Characteristics (continued)**

3.75 3.70 3.65 3 60 3.55 3.50 2.3 2.7 3.1 3.5 3.9 4.3 4.7 5.1 5.5 SUPPLY VOLTAGE (V)

**POWER-SAVE DELAY TIME**

3.5 3.9 4.3

4.7

5.1 5.5

#### **OUTPUT VOLTAGE vs. OUTPUT CURRENT IN POWER-SAVE MODE**

///XI//

### MAX4822/MAX4823 Pin Description

| Р       | PIN     |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|---------|---------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MAX4822 | MAX4823 | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 1       | 1       | RESET | Reset Input. Drive RESET low to clear all latches and registers (all outputs are high impedance). RESET overrides all other inputs. If RESET and SET are pulled low at the same time, then RESET takes precedence.                                                                                                                                                                                                                                                                                                                 |  |  |

| 2       | 2       | CS    | Chip-Select Input. Drive $\overline{CS}$ low to select the device. When $\overline{CS}$ is low, data at DIN is clocked into the shift register on SCLK's rising edge. Drive $\overline{CS}$ from low to high to latch the data to the registers and activate the relay outputs.                                                                                                                                                                                                                                                    |  |  |

| 3       | 3       | DIN   | Serial Data Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 4       | 4       | SCLK  | Serial Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 5       | 5       | DOUT  | Serial Data Output. DOUT is the output of the shift register. DOUT can be used to daisy-<br>chain multiple MAX4822/MAX4823 devices. The data at DOUT appears synchronous to<br>SCLK's falling edge.                                                                                                                                                                                                                                                                                                                                |  |  |

| 6       | 6, 13   | N.C.  | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 7       | 7       | GND   | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 8       | 8       | OUT8  | Open-Drain Output 8. Connect OUT8 to the low side of a relay coil. This output is pulled to PGND when activated, but otherwise is high impedance.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 9       | 9       | OUT7  | Open-Drain Output 7. Connect OUT7 to the low side of a relay coil. This output is pulled to PGND when activated, but otherwise is high impedance.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 10, 16  | 10, 16  | PGND  | Power Ground. PGND is a return for the output sinks. Connect PGND pins together and to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| 11      | 11      | OUT6  | Open-Drain Output 6. Connect OUT6 to the low side of a relay coil. This output is pulled to PGND when activated, but otherwise is high impedance.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 12      | 12      | OUT5  | Open-Drain Output 5. Connect OUT5 to the low side of a relay coil. This output is pulled to PGND when activated, but otherwise is high impedance.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 13      |         | PSAVE | Power-Save Control. Connect a timing capacitor from PSAVE to ground. The capacitor value determines power-save timing as explained under the <i>Applications Information</i> section. PSAVE can also be driven externally to control power-save mode asynchronously. When asserted high, PSAVE reduces the current to all active outputs as determined by the <i>Power-Save Configuration Register</i> (see Figure 1). To disable power-save mode in all channels, drive PSAVE low for at least 3ms after the last output setting. |  |  |

| 14      | 14      | OUT4  | Open-Drain Output 4. Connect OUT4 to the low side of a relay coil. This output is pulled to PGND when activated, but otherwise is high impedance.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 15      | 15      | OUT3  | Open-Drain Output 3. Connect OUT3 to the low side of a relay coil. This output is pulled to PGND when activated, but otherwise is high impedance.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 17      | 17      | OUT2  | Open-Drain Output 2. Connect OUT2 to the low side of a relay coil. This output is pulled to PGND when activated, but otherwise is high impedance.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 18      | 18      | OUT1  | Open-Drain Output 1. Connect OUT1 to the low side of a relay coil. This output is pulled to PGND when activated, but otherwise is high impedance.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| Р       | IN      |                 |                                                                                                                                                                                                 |

|---------|---------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX4822 | MAX4823 | NAME            | FUNCTION                                                                                                                                                                                        |

| 19      | 19      | V <sub>CC</sub> | Input Supply Voltage. Bypass $V_{CC}$ to GND with a 0.1µF capacitor.                                                                                                                            |

| 20      | 20      | SET             | Set Input. Drive SET low to set all latches and registers high (all outputs are low impedance). SET overrides all parallel and serial control inputs. RESET overrides SET under all conditions. |

| EP      | EP      | EP              | Exposed Pad. Connect exposed paddle to GND.                                                                                                                                                     |

### MAX4824/MAX4825 Pin Description

| P       | IN      |       |                                                                                                                                                                                                                    |  |

|---------|---------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX4824 | MAX4825 | NAME  | FUNCTION                                                                                                                                                                                                           |  |

| 1       | 1       | RESET | Reset Input. Drive RESET low to clear all latches and registers (all outputs are high impedance). RESET overrides all other inputs. If RESET and SET are pulled low at the same time, then RESET takes precedence. |  |

| 2       | 2       | CS    | Chip-Select Input. Drive $\overline{CS}$ low to select the device. The $\overline{CS}$ falling edge latches the output address (A0, A1, A2). The $\overline{CS}$ rising edge latches level data (LVL).             |  |

| 3       | 3       | LVL   | Level Input. LVL determines whether the selected address is switched on or off. Logic-<br>high on LVL switches on the addressed output. A logic-low on LVL switches off the<br>addressed output.                   |  |

| 4       | 4       | AO    | Digital Address 0 Input. (See Figure 3 for address mapping.)                                                                                                                                                       |  |

| 5       | 5       | A1    | Digital Address 1 Input. (See Figure 3 for address mapping.)                                                                                                                                                       |  |

| 6       | 6       | A2    | Digital Address 2 Input. (See Figure 3 for address mapping.)                                                                                                                                                       |  |

| 7       | 7       | GND   | Ground                                                                                                                                                                                                             |  |

| 8       | 8       | OUT8  | Open-Drain Output 8. Connect OUT8 to the low side of a relay coil. This output is pulled to PGND when activated, but otherwise is high impedance.                                                                  |  |

| 9       | 9       | OUT7  | Open-Drain Output 7. Connect OUT7 to the low side of a relay coil. This output is pulled to PGND when activated, but otherwise is high impedance.                                                                  |  |

| 10, 16  | 10, 16  | PGND  | Power Ground. PGND is a return for the output sinks. Connect PGND pins together and to GND.                                                                                                                        |  |

| 11      | 11      | OUT6  | Open-Drain Output 6. Connect OUT6 to the low side of a relay coil. This output is pulled to PGND when activated, but otherwise is high impedance.                                                                  |  |

| 12      | 12      | OUT5  | Open-Drain Output 5. Connect OUT5 to the low side of a relay coil. This output is pulled to PGND when activated, but otherwise is high impedance.                                                                  |  |

### \_MAX4824/MAX4825 Pin Description (continued)

| Р       | PIN     |                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX4824 | MAX4825 | NAME                                                                                                                                            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 13      | _       | PSAVE                                                                                                                                           | Power-Save Control. Connect a timing capacitor from PSAVE to ground. The capacitor value determines power-save timing as explained under the <i>Applications Information</i> section. PSAVE can also be driven externally to control power-save mode asynchronously. When PSAVE is asserted high, the current through the coils is reduced to 60% of the initial nominal current value. To disable power-save mode in all channels, drive PSAVE low for at least 3ms after last output setting. |

| 14      | 14      | OUT4 Open-Drain Output 4. Connect OUT4 to the low side of a relay coil. This output is to PGND when activated, but otherwise is high impedance. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 15      | 15      | OUT3 Open-Drain Output 3. Connect OUT3 to the low side of a relay coil. This output is to PGND when activated, but otherwise is high impedance. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 17      | 17      | OUT2 Open-Drain Output 2. Connect OUT2 to the low side of a relay coil. This output to PGND when activated, but otherwise is high impedance.    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 18      | 18      | OUT1                                                                                                                                            | Open-Drain Output 1. Connect OUT1 to the low side of a relay coil. This output is pulled to PGND when activated, but otherwise is high impedance.                                                                                                                                                                                                                                                                                                                                               |

| 19      | 19      | V <sub>CC</sub>                                                                                                                                 | Input Supply Voltage. Bypass V <sub>CC</sub> to GND with a 0.1µF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 20      | 20      | SET                                                                                                                                             | Set Input. Drive SET low to set all latches and registers high (all outputs are low impedance). SET overrides all parallel and serial control inputs. RESET overrides SET under all conditions.                                                                                                                                                                                                                                                                                                 |

|         | 13      | N.C.                                                                                                                                            | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| EP      | EP      | EP                                                                                                                                              | Exposed Pad. Connect exposed paddle to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

### \_Detailed Description

### Serial Interface (MAX4822/MAX4823)

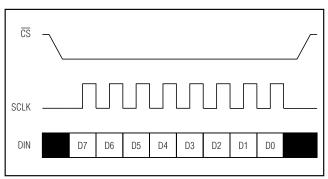

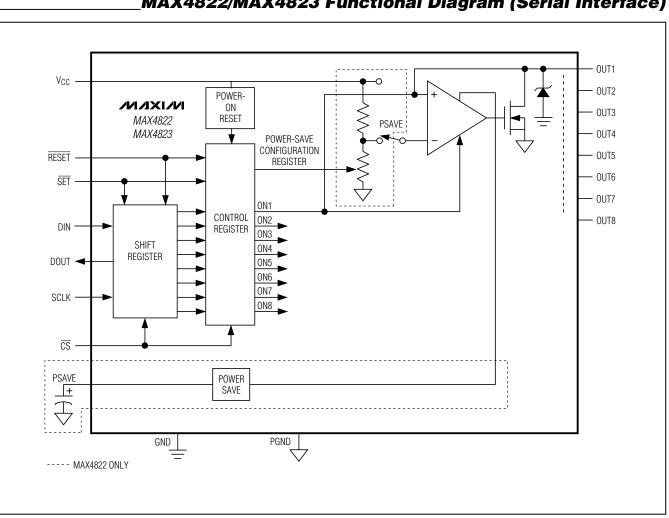

Depending on the MAX4822/MAX4823 device, the serial interface can be controlled by either 8- or 16-bit words as depicted in Figures 1 and 2. The MAX4823 does not support power-save mode, so the serial interface consists of an 8-bit-only shift register for faster control.

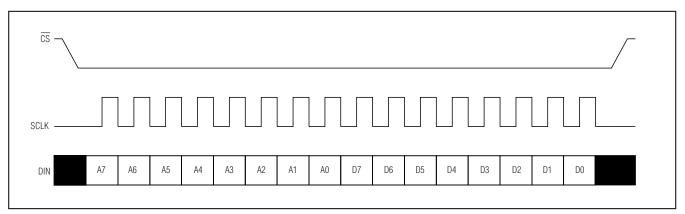

The MAX4822 consists of a 16-bit shift register and parallel latch controlled by SCLK and  $\overline{\text{CS}}$ . The input to the shift register is a 16-bit word. In the MAX4822, the first 8 bits determine the register address and are followed by 8 bits of data as depicted in Figure 1. Bit A7 corresponds to the MSB of the 8-bit register address in Figure 1, while bit D7 corresponds to the MSB of the 8 bits of data in the same Figure 1.

The MAX4823 consists of an 8-bit shift register and parallel latch controlled by SCLK and  $\overline{CS}$ . The input to the shift register is an 8-bit word. Each data bit controls one of the eight outputs, with the most significant bit (D7) corresponding to OUT8, and the least significant bit (D0) corresponding to OUT1 (see Figure 2).

| ADDRESS [A7A0] | ACTIVE REGISTER                         |  |  |  |  |

|----------------|-----------------------------------------|--|--|--|--|

| 00h            | Output Control Register—OUTR            |  |  |  |  |

| 01h            | Power-Save Configuration<br>Register—PS |  |  |  |  |

Serial-Input Address Map

| D7               | D <sub>6</sub>   | D5               | D4               | D <sub>3</sub>   | D2               | D <sub>1</sub>   | D <sub>0</sub>   |

|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| OUT <sub>8</sub> | OUT <sub>7</sub> | OUT <sub>6</sub> | OUT <sub>5</sub> | OUT <sub>4</sub> | OUT <sub>3</sub> | OUT <sub>2</sub> | OUT <sub>1</sub> |

| MSB              |                  |                  |                  |                  |                  |                  | LSB              |

#### Output Control Register—OUT<sub>R</sub> (Address = 00h)

Note: Setting  $D_N$  to logic 1 turns on output OUT<sub>N+1</sub>. Setting  $D_N$  to logic 0, turns off OUT<sub>N+1</sub>. Example: Setting  $D_2 = 1$  turns on OUT<sub>3</sub>.

| D7                                             | D <sub>6</sub> | D5 | D4 | D <sub>3</sub> | D2  | D <sub>1</sub> | D <sub>0</sub> |

|------------------------------------------------|----------------|----|----|----------------|-----|----------------|----------------|

| x                                              | х              | х  | x  | Х              | PS0 | PS1            | PS2            |

| MSB                                            |                |    |    |                |     |                | LSB            |

| Deven Overflerentler Devictor DO (Address Oth) |                |    |    |                |     |                |                |

Power-Save Configuration Register—PS (Address= 01h)

| PS0 | PS1 | PS2 | POWER-SAVE CONFIGURATION                                                                                                                                                                                      |

|-----|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | 0   | 0   | Power-save is disabled (Default Operation)                                                                                                                                                                    |

| 0   | 0   | 1   | Power-save is enabled. V <sub>OUT</sub> set to 70% of V <sub>CC</sub> , typical after t <sub>PS</sub> ms (see Note 1), causes $I_{OUT}$ to be reduced to approximately 30%, typical after t <sub>PS</sub> ms. |

| 0   | 1   | 0   | Power-save is enabled. V <sub>OUT</sub> set to 60% of V <sub>CC</sub> , typical after t <sub>PS</sub> ms (see Note 1), causes $I_{OUT}$ to be reduced to approximately 40%, typical after t <sub>PS</sub> ms. |

| 0   | 1   | 1   | Power-save is enabled. V <sub>OUT</sub> set to 50% of V <sub>CC</sub> , typical after t <sub>PS</sub> ms (see Note 1), causes $I_{OUT}$ to be reduced to approximately 50%, typical after t <sub>PS</sub> ms. |

| 1   | 0   | 0   | Power-save is enabled. $V_{OUT}$ set to 40% of $V_{CC}$ , typical after t <sub>PS</sub> ms (see Note 1), causes $I_{OUT}$ to be reduced to approximately 60%, typical after t <sub>PS</sub> ms.               |

| 1   | 0   | 1   | Power-save is enabled. V <sub>OUT</sub> set to 30% of V <sub>CC</sub> , typical after t <sub>PS</sub> ms (see Note 1), causes $I_{OUT}$ to be reduced to approximately 70%, typical after t <sub>PS</sub> ms. |

| 1   | 1   | 0   | Power-save is enabled. V <sub>OUT</sub> set to 20% of V <sub>CC</sub> , typical after t <sub>PS</sub> ms (see Note 1), causes $I_{OUT}$ to be reduced to approximately 80%, typical after t <sub>PS</sub> ms. |

| 1   | 1   | 1   | Power-save is enabled. $V_{OUT}$ set to 10% of $V_{CC}$ , typical after t <sub>PS</sub> ms (see Note 1), causes $I_{OUT}$ to be reduced to approximately 90%, typical after t <sub>PS</sub> ms.               |

Note 1: The time period tps is determined by the capacitor connected to PSAVE.

When  $\overline{\text{CS}}$  is low (MAX4822/MAX4823 device is selected), data at DIN is clocked into the shift register synchronously with SCLK's rising edge. Driving  $\overline{\text{CS}}$  from low to high latches the data in the shift register (Figures 5 and 6).

DOUT is the output of the shift register. Data appears on DOUT synchronously with SCLK's falling edge and is identical to the data at DIN delayed by eight clock cycles for the MAX4823, or 16 clock cycles for the MAX4822. When shifting the input data, A7 is the first input bit in and out of the shift register for the MAX4822 device. D7 is the first bit in or out of the shift register for

Figure 1. 16-Bit Register Map for MAX4822

| MSB              |                |                  |                  |                  |                  |                  | LSB              |

|------------------|----------------|------------------|------------------|------------------|------------------|------------------|------------------|

| D7               | D <sub>6</sub> | D <sub>5</sub>   | D4               | D3               | D <sub>2</sub>   | D1               | D <sub>0</sub>   |

| OUT <sub>8</sub> | OUT7           | OUT <sub>6</sub> | OUT <sub>5</sub> | OUT <sub>4</sub> | OUT <sub>3</sub> | OUT <sub>2</sub> | OUT <sub>1</sub> |

**Note:** Setting  $D_N$  to logic 1 turns on output  $OUT_{N+1}$ . Setting  $D_N$  to logic 0 turns off output  $OUT_{N+1}$ . Example: Setting the  $D_2 = 1$  turns  $OUT_3$  on.

Figure 2. 8-Bit Register Map for MAX4823

|      |      |      | <u></u> |

|------|------|------|---------|

| A2   | A1   | A0   | OUTPUT  |

| Low  | Low  | Low  | OUT1    |

| Low  | Low  | High | OUT2    |

| Low  | High | Low  | OUT3    |

| Low  | High | High | OUT4    |

| High | Low  | Low  | OUT5    |

| High | Low  | High | OUT6    |

| High | High | Low  | OUT7    |

| High | High | High | OUT8    |

Figure 3. Register Address Map for MAX4824/MAX4825

Figure 4. 3-Wire Serial-Interface Timing Diagram

the MAX4823 device. If the address A0......A7 is not 00h or 01h, then the outputs and the PSAVE configuration register are not updated. The address is stored in the shift register only.

While  $\overline{CS}$  is low, the OUT\_ outputs always remain in their previous state. For the MAX4823, drive  $\overline{CS}$  high after 8 bits of data have been shifted in to update the output state of the MAX4823, and to further inhibit data from entering the shift register. For the MAX4822, drive  $\overline{CS}$  high after 16 bits of data have been shifted in to update the output state of the MAX4822, and to further inhibit data from entering the shift register. When  $\overline{CS}$  is high, transitions at DIN and SCLK have no effect on the output, and the first input bit A7 (or D7) is present at DOUT. For the MAX4822, if the number of data bits entered while  $\overline{CS}$  is low is greater or less than 16, the shift register contains only the last 16 bits, regardless of when they were entered. For the MAX4823, if the number of data bits entered while  $\overline{CS}$  is low is greater or less than 8, the shift register contains only the last 8 data bits, regardless of when they were entered.

#### Parallel Interface (MAX4824/MAX4825)

The parallel interface consists of 3 address bits (A0, A1, A2) and one level selector bit (LVL). The address bits determine which output is updated, and the level bit determines whether the addressed output is switched on (LVL = high) or off (LVL = low). When  $\overline{CS}$  is high, the address and level bits have no effect on the state of the outputs. Driving  $\overline{CS}$  from low to high latches

Figure 5. 3-Wire Serial-Interface Operation for MAX4822

level data to the parallel register and updates the state of the outputs. Address data entered after  $\overline{CS}$  is pulled low is not reflected in the state of the outputs following the next low-to-high transition on  $\overline{CS}$  (Figure 7).

#### **SET/RESET** Functions

The MAX4822–MAX4825 feature set and reset inputs that allow simultaneous turn-on or turn-off of all outputs using a single control line. Drive SET low to set all latches and registers to 1 and turn all outputs on. SET overrides all serial/parallel control inputs. Drive RESET low to clear all latches and registers and to turn all outputs off. RESET overrides all other inputs including SET.

#### **Power-On Reset**

The MAX4822–MAX4825 feature power-on reset. The power-on reset function causes all latches to be cleared automatically upon power-up. This ensures that all outputs come up in the off or high-impedance state.

### Applications Information

#### **Daisy Chaining**

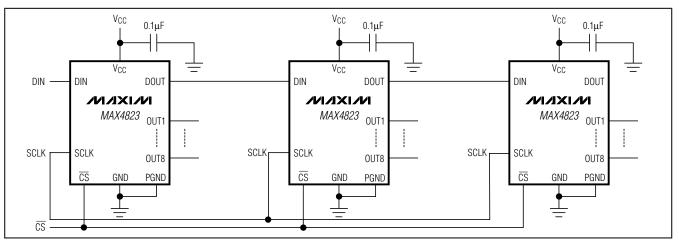

The MAX4822/MAX4823 feature a digital output (DOUT) that provides a simple way to daisy chain multiple devices. This feature allows driving large banks of relays using only a single serial interface. To daisy chain multiple devices, connect all CS inputs together, and connect the DOUT of one device to the DIN of another device (see Figure 8). During operation, a stream of serial data is shifted through the MAX4822/ MAX4823 devices in series. When CS goes high, all outputs update simultaneously.

The MAX4822/MAX4823 can also be used in a slave configuration that allows individual addressing of devices. Connect all the DIN inputs together, and use

the  $\overline{CS}$  input to address one device at a time. Drive  $\overline{CS}$  low to select a slave and input the data into the shift register. Drive  $\overline{CS}$  high to latch the data and turn on the appropriate outputs. Typically, in this configuration only one slave is addressed at a time.

#### **Power-Save Mode**

The MAX4822/MAX4824 feature a unique power-save mode where the relay current, after activation, can be reduced to a level just above the relay hold-current threshold. This mode keeps the relay activated while significantly reducing the power consumption.

In serial mode (MAX4822), choose between seven current levels ranging from 30% to 90% of the nominal current in 10% increments. The actual percentage is determined by the power-save configuration register (Figure 1).

In parallel mode (MAX4824), the power-save current is fixed at 60% of the nominal current.

#### Power-Save Timer

Every time there is a write operation to the device ( $\overline{\text{CS}}$  transitions from low to high), the MAX4822/MAX4824 start charging the capacitor connected to PSAVE. The serial power-save implementation is such that a write operation does not change the state of channels already in power-save mode (unless the write turns the channel OFF).

After a certain time period,  $t_{PS}$  (determined by the capacitor value), the capacitor reaches a voltage threshold that sets all active outputs to power-save mode. The tps period should be made long enough to allow the relay to turn on completely. The time period tps can be adjusted by using different capacitor values

connected to PSAVE. The value  $\ensuremath{\mathsf{tPS}}$  is given by the following formula:

$$t_{PS} = 32 \times C$$

where C is in  $\mu F$  and  $t_{PS}$  is in ms.

For example, if the desired tps is 20ms, then the required capacitor value is  $20/32 = 0.625\mu$ F.

#### Power-Save Mode Accuracy

The current through the relay is controlled by setting the voltage at OUT\_ to a percentage of the V<sub>CC</sub> supply as specified under the *Electrical Characteristics* and in the register description. The current through the relay (I<sub>OUT</sub>) depends on the switch on-resistance, R<sub>ON</sub>, in addition to the relay resistance R<sub>R</sub> according to the following relation:

$$I_{OUT} = V_{CC} / (R_{ON} + R_R)$$

The power-save, current-setting IPS depends on the fraction  $\alpha$  of the supply voltage V<sub>CC</sub> that is set by the loop depending on the following relation:

$$I_{PS} = V_{CC} - (\alpha \times V_{CC}) / R_R$$

Therefore:

$$I_{PS} / I_{OUT} = (1 - \alpha) \times (1 + R_{ON} / R_{R})$$

This relation shows how the fraction of reduction in the current depends on the switch on-resistance, as well as from the accuracy of the voltage setting ( $\alpha$ ). The higher the R<sub>ON</sub> with respect to R<sub>R</sub>, the higher the inaccuracy. This is particularly true at low voltage when the relay resistance is low (less than 40 $\Omega$ ) and the switch can account for up to 10% of the total resistance. In addition, when the supply-voltage setting ( $\alpha$ ) is low (10% or 20%) and the supply voltage (V<sub>CC</sub>) is low, the voltage drop across the switch (I<sub>OUT</sub> x R<sub>ON</sub>) may already exceed, or may be very close to, the desired voltage setting value.

#### **Daisy Chaining and Power-Save Mode**

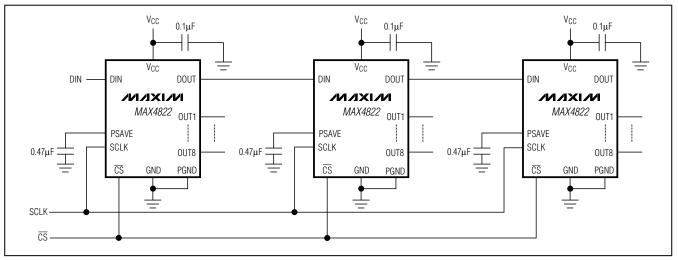

In a normal configuration using the power-save feature, several MAX4822s can be daisy chained as shown in Figure 9. For each MAX4822, the power-save timing tpD (time it takes to reduce the relay current once the relay is actuated) is controlled by the capacitor connected to PSAVE.

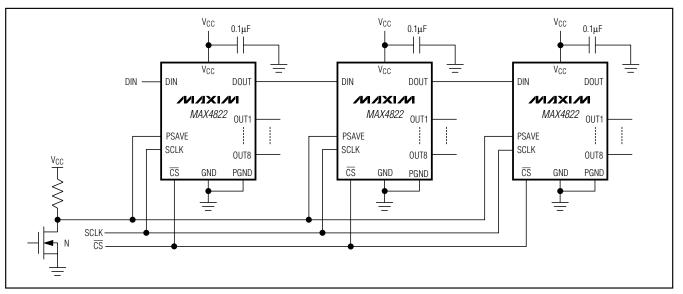

An alternative configuration that eliminates the PSAVE capacitors uses a common PSAVE control line driven by an open-drain n-channel MOSFET (Figure 10). In this configuration, the PSAVE inputs are connected together to asynchronously control the power-save timing for all the MAX4822s in the chain. The  $\mu$ C/ $\mu$ P drives the n-channel MOSFET low for the duration of a write cycle to the SPI chain, plus some delay time to allow the relays to close.

Figure 6. 3-Wire Serial-Interface Operation for the MAX4823

Figure 7. Parallel-Interface Timing Diagram

(This time is typically specified in the relay data sheet.) Once this delay time has elapsed, the n-channel MOSFET is turned off, allowing the MAX4822's internal 35µA pullup current to raise PSAVE to a logic-high level, activating the power-save mode in all active outputs.

#### **MOSFET Selection**

In the daisy-chain configuration of Figure 10, the n-channel MOSFET drives PSAVE low. When the n-channel MOSFET is turned off, PSAVE is pulled high by an internal 35µA pullup in each MAX4822, and the power-save mode is enabled. Because of the paralleled PSAVE pullup currents, the required size of the n-channel MOSFET depends upon the number of MAX4822 devices in the chain. Determine the size of the n-channel MOSFET by the following relation:

Ron < 1428 / N

Figure 8. Daisy-Chain Configuration

Figure 9. Daisy-Chained MAX4822s with a Capacitor Connected to PSAVE

where N is the total number of MAX4822 devices in a single chain, and  $R_{ON}$  is the on-resistance of the n-channel MOSFET in  $\Omega s.$

For example, if N = 10:

#### $R_{ON} < 142\Omega$

An n-channel MOSFET with Ron less than 142  $\!\Omega$  is required for a daisy chain of 10 MAX4822 devices.

#### Inductive Kickback Protection with Fast Recovery Time

The MAX4822–MAX4825 feature built-in inductive kickback protection to reduce the voltage spike on OUT\_ generated by a relay's coil inductance when the output is suddenly switched off. An internal Zener clamp allows the inductor current to flow back to ground. The Zener configuration significantly reduces the recovery time (time it takes to turn off the relay) when compared to protection configurations with just one diode across the coil.

Figure 10. Daisy-Chaining MAX4822s with a PSAVE Connected to an n-Channel MOSFET

### **Chip Information**

TRANSISTOR COUNT: 5799 PROCESS: BICMOS

MAX4822/MAX4823 Functional Diagram (Serial Interface)

MAX4824/MAX4825 Functional Diagram (Parallel Interface)

### **Pin Configurations**

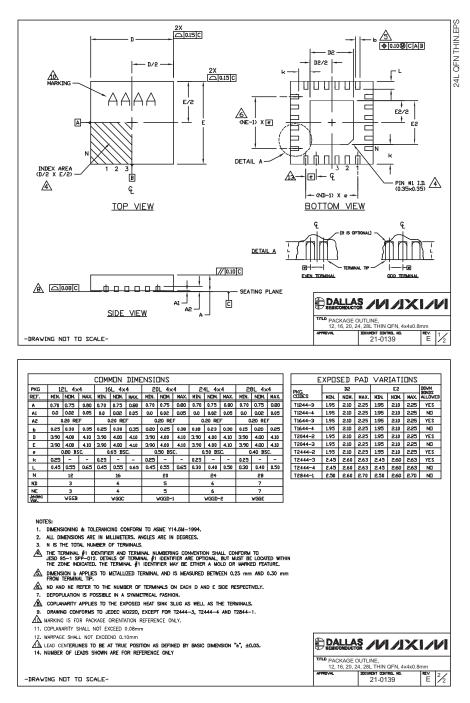

### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to **www.maxim-ic.com/packages**.)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_

Printed USA *MAXIM* is a registered trademark of Maxim Integrated Products, Inc.

| <u>ENGLISH</u> • <u>2222</u> • <u>222</u> • <u>222</u>                                                         |                                                              |                                                               |                                                                      |                                                                                                              |                        |                                               |                                                        |  |  |

|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------|-----------------------------------------------|--------------------------------------------------------|--|--|

|                                                                                                                |                                                              |                                                               |                                                                      |                                                                                                              |                        |                                               |                                                        |  |  |

| WHAT'S NEWPROI                                                                                                 | DUCTSSOI                                                     | LUTIONS                                                       | DESIGN                                                               | APPNOTES SUPPO                                                                                               | <u>ORT</u>             | <u>BUY</u>                                    | COMPANY MEMBERS                                        |  |  |

|                                                                                                                | <u>MAX4824</u>                                               |                                                               |                                                                      |                                                                                                              |                        |                                               |                                                        |  |  |

|                                                                                                                | Part Number Table                                            |                                                               |                                                                      |                                                                                                              |                        |                                               |                                                        |  |  |

| Notes:                                                                                                         |                                                              |                                                               |                                                                      |                                                                                                              |                        |                                               |                                                        |  |  |

| <ol> <li><u>Didn't Find V</u><br/>business day</li> <li>Part number<br/><u>sheet</u> or <u>Part</u></li> </ol> | s and links for<br>What You N<br>suffixes: T or<br>Naming Co | or purchas<br><u>eed?</u> Ask<br>or T&R =<br><u>nventions</u> | sing parts are<br>our application<br>tape and reel<br>isted on the d | listed at: <u>http://www.ma</u> ons engineers. Expert as<br>; + = RoHS/lead-free; ;<br>hrawing. "PkgCode/Var | ssistance i<br># = RoH | in finding pa<br>S/lead-exer<br>ells which va | npt. More: See <u>full data</u>                        |  |  |

|                                                                                                                | Sample                                                       | Direct                                                        | U                                                                    | DRAWING CODE/VA                                                                                              | AR *                   |                                               | Materials Analysis                                     |  |  |

| MAX4824ETP                                                                                                     |                                                              |                                                               | Dwg: 21-01                                                           | 20 pin;4X4X0.8mm<br><u>39E</u> (PDF)<br>e/variation: T2044-3*                                                | -40                    | )C to +85C                                    | RoHS/Lead-Free: <u>No</u><br><u>Materials Analysis</u> |  |  |

| MAX4824ETP-T                                                                                                   |                                                              |                                                               |                                                                      |                                                                                                              | -40                    | )C to +85C                                    | RoHS/Lead-Free: <u>No</u>                              |  |  |

| MAX4824EUP                                                                                                     |                                                              |                                                               | TSSOP;20 p<br>Dwg: <u>21-01(</u><br>Use pkgcode                      |                                                                                                              | -40                    | )C to +85C                                    | RoHS/Lead-Free: <u>No</u><br><u>Materials Analysis</u> |  |  |

Didn't Find What You Need?

### CONTACT US: SEND US AN EMAIL

Copyright 2007 by Maxim Integrated Products, Dallas Semiconductor • Legal Notices • Privacy Policy