REVISIONS DATE **APPROVED DESCRIPTION** LTR Convert to military drawing format. 27 JAN Add an LCC package. Editorial 88 changes throughout. **CURRENT CAGE CODE 67268** CC CC С С REV 25 26 28 30 31 32 33 24 PAGE С С Ċ С С C С CC C C С C REV **REV STATUS** 19 15 10 3 **OF PAGES** PAGES 2 3 4 5 8 9 PREPARED BY **Defense Electronics Supply Center** This drawing is available for use by all Departments and Agencies of the Dayton, Ohio CHECKED BY/ Department of Defense MICROCIRCUITS, MICROPROCESSOR PE-TITLE:RIPHERAL COUNTER/TIMER, PARALLEL APPROVED Original date NPUT/OUTPUT N-CHANNEL, MONOLITHIC SILICON of drawing: COOE IDENT. NO. SIZE DWG NO. 83001 7 April 1983 14933 AMSC N/A REV PAGE OF С 34 5962-E709

DISTRIBUTION STATEMENT A. Approved for public release; distribution is unlimited.

DESC FORM 193

MAY 86

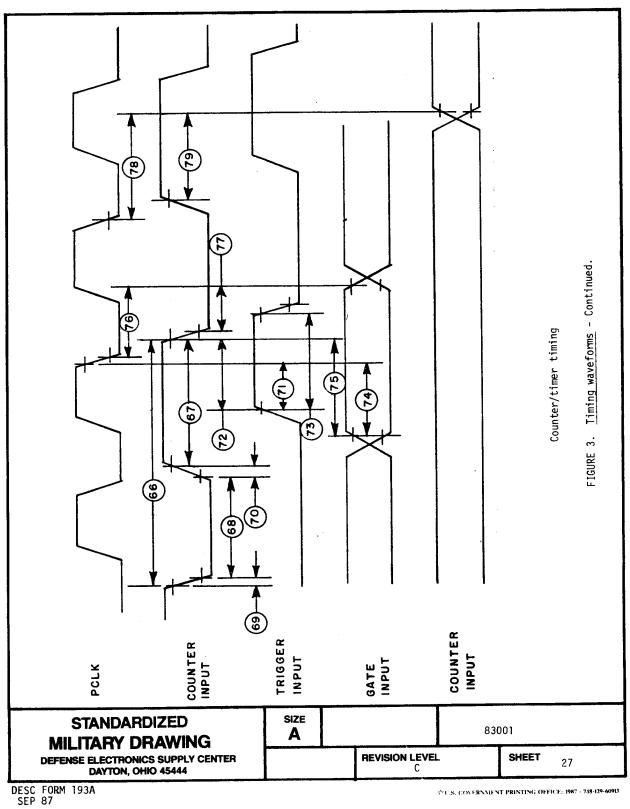

| Parameter                                    | Reference<br>number 1/ | Minimum | Maximum | Unit |

|----------------------------------------------|------------------------|---------|---------|------|

| Trigger input                                |                        |         |         |      |

| to PCLK setup                                |                        |         |         |      |

| time (timer                                  | 71                     | 150     |         |      |

| mode) $\frac{2}{}$                           | 71                     | 150     |         | ns   |

| Trigger input                                |                        |         |         |      |

| to counter                                   |                        |         |         |      |

| input setup<br>time (counter                 |                        |         |         |      |

| mode) $\frac{2}{}$                           | 72                     | 150     |         | ns   |

| _                                            | ,2                     | 200     |         |      |

| Trigger input                                | 73                     | 200     |         | ne   |

| pulse width                                  | /3                     | 200     |         | ns   |

| (high or low)                                |                        |         |         |      |

| Gate input to                                |                        |         |         |      |

| PCLK setup                                   |                        |         |         |      |

| time (timer                                  |                        |         |         |      |

| mode) $\underline{2}/$                       | 74                     | 100     |         | ns   |

| Gate input to                                |                        |         |         |      |

| counter input                                |                        |         |         |      |

| setup time                                   |                        |         |         |      |

| (counter                                     |                        |         |         |      |

| mode) $\frac{2}{2}$                          | 75                     | 100     |         | ns   |

| • · • · · ·                                  |                        |         |         |      |

| Gate input to                                |                        |         |         |      |

| PCLK hold                                    |                        |         |         |      |

| time (timer                                  | 76                     | 100     |         |      |

| mode) $\underline{2}/$                       | 70                     | 100     |         | ns   |

| Gate input                                   |                        |         |         |      |

| to counter                                   |                        |         |         |      |

| input, hold                                  |                        |         |         |      |

| time (counter                                | 77                     | 100     |         |      |

| mode) $\frac{2}{2}$                          | //                     | 100     |         | ns   |

| PCLK to                                      |                        |         |         |      |

| counter output                               |                        |         |         |      |

| delay (timer                                 |                        |         |         |      |

| mode)                                        | 78                     |         | 475     | ns   |

| Counter input                                |                        |         |         |      |

| to counter                                   |                        |         |         |      |

| output delay                                 |                        |         |         |      |

| (counter mode)                               | 79                     |         | 475     | ns   |

| e reference number romese parameters must be | •                      |         |         |      |

| me. Oyotet                                   |                        |         |         |      |

**MILITARY DRAWING** 83001 DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 REVISION LEVEL SHEET

DESC FORM 193A SEP 87

## 2. APPLICABLE DOCUMENTS

2.1 Government specification and standard. Unless otherwise specified, the following specification and standard, of the issue listed in that issue of the Department of Defense Index of Specifications and Standards specified in the solicitation, form a part of this drawing to the extent specified herein.

**SPECIFICATION**

MILITARY

MIL-M-38510

- Microcircuits. General Specification for.

STANDARD

MILITARY

MIL-STD-883

- Test Methods and Procedures for Microelectronics.

(Copies of the specification and standard required by manufacturers in connection with specific acquisition functions should be obtained from the contracting activity or as directed by the contracting activity.)

- 2.2 Order of precedence. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing shall take precedence.

- 3. REQUIREM

- 3.1 Item requirements. The individual item requirements shall be in accordance with 1.2.1 of MIL-STD-883, "Provisions for the use of MIL-STD-883 in conjunction with compliant non-JAN devices" and as specified herein.

- 3.2 Design, construction, and physical dimensions. The design, construction, and physical dimensions shall be as specified in MIL-M-38510 and herein.

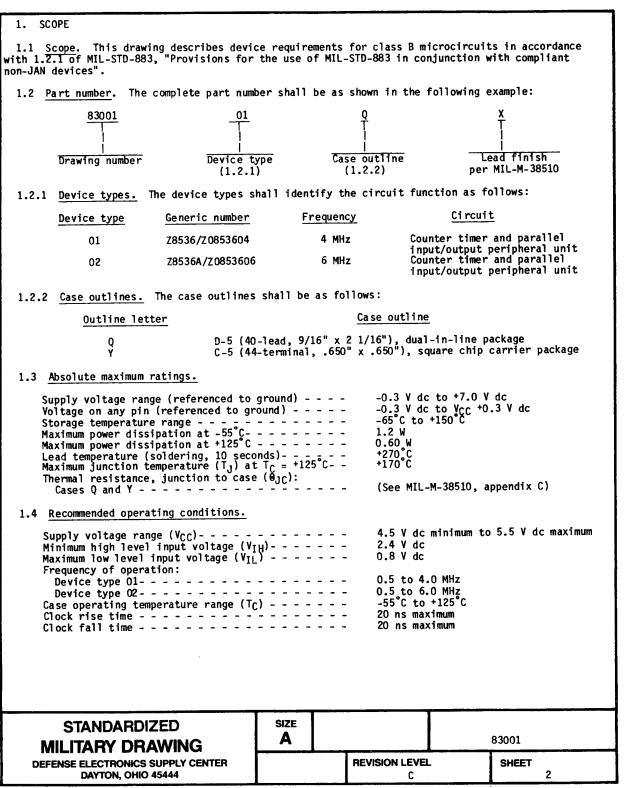

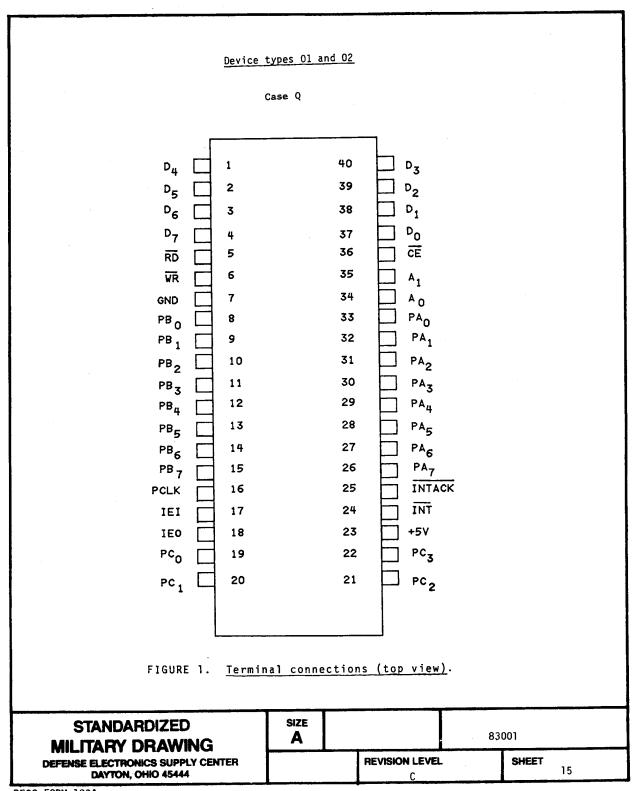

- 3.2.1 Terminal connections. The terminal connections shall be as specified on figure 1. .

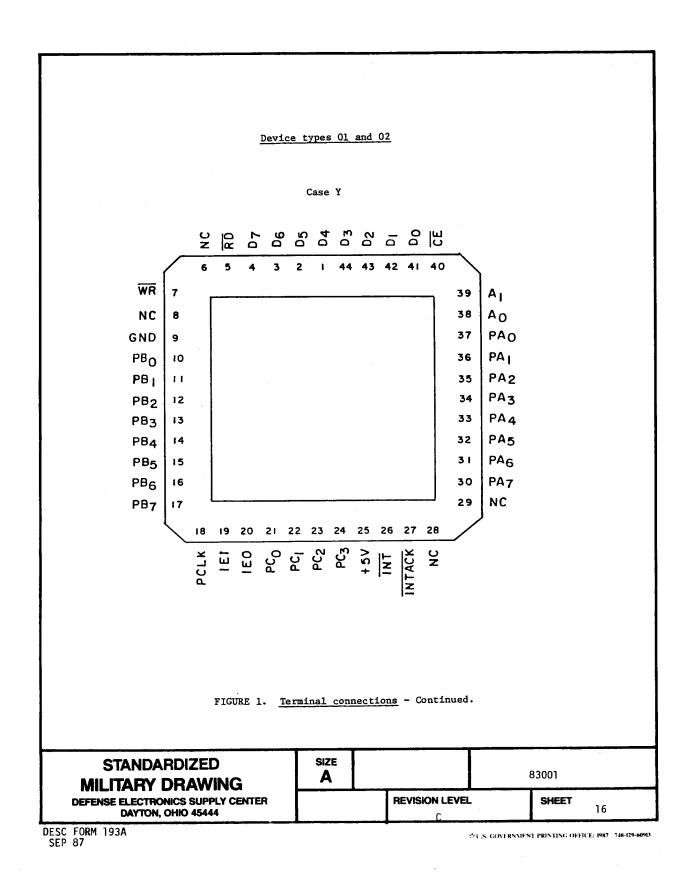

- 3.2.2 Logic functions. The logic functions shall be as specified on figure 2.

- 3.2.3 Case outlines. The case outlines shall be in accordance with 1.2.2 herein.

- 3.3 Electrical performance characteristics. Unless otherwise specified, the electrical performance characteristics are as specified in table I and apply over the full recommended case operating temperature range.

- 3.4 Marking. Marking shall be in accordance with MIL-STD-883 (see 3.1 herein). The part shall be marked with the part number listed in 1.2 herein. In addition, the manufacturer's part number may also be marked as listed in 6.5 herein.

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE 83001

REVISION LEVEL SHEET 4

DESC FORM 193A SEP 87

|                                                          | T                      | ABLE I. Electr                                      | ical performance c                                                       | haracteristic    | :s.               |                    |                                          |                                       |

|----------------------------------------------------------|------------------------|-----------------------------------------------------|--------------------------------------------------------------------------|------------------|-------------------|--------------------|------------------------------------------|---------------------------------------|

|                                                          |                        | T                                                   | Conditions                                                               |                  | 1                 | Lim                | its                                      |                                       |

| Parameter                                                | Symbol                 | j -55°C <<br>i unless o                             | $T_{C} \le +125^{\circ}C$ ,<br>therwise specified $\le V_{CC} \le 5.5$ V | Device<br>d type | Group A subgroups | Min                | Max                                      | Unit                                  |

| Input high voltage                                       | v <sub>IH</sub>        |                                                     |                                                                          | All              | 1, 2, 3           | 2.2                | ν <sub>CC</sub><br> +0.3<br>  <u>1</u> / | ٧                                     |

| Input low voltage                                        | V <sub>IL</sub>        |                                                     |                                                                          | <br>             |                   | -0.3<br><u>1</u> / | 0.8                                      | ٧                                     |

| Output low voltage                                       | v <sub>OL</sub>        | I <sub>OL</sub> = 2.0 mA                            |                                                                          |                  |                   |                    | 0.4                                      | ٧                                     |

| Output high voltage                                      | V <sub>ОН</sub>        | i<br>I <sub>OH</sub> = -250 μA                      |                                                                          | ļ                |                   | 2.4                |                                          | ٧                                     |

| Power supply current                                     | ICC                    | <br> Outputs open V<br>                             | /cc = 5.5 V                                                              |                  |                   | 1                  | 200                                      | mA                                    |

| Input capacitance                                        | CIN                    |                                                     |                                                                          | 01,02            | 4                 | <br>               | 10 1/                                    | pF                                    |

| Output capacitance                                       | COUT                   |                                                     |                                                                          | 01,02            | 4                 | <br> <br>          | 15 1/                                    | i pF                                  |

| Bidirectional capacitance                                | <br> C <sup>I</sup> \0 |                                                     |                                                                          | 01,02            | 4                 |                    | 20 1/                                    | pF                                    |

| Output leakage<br>current low, open<br>drain outputs     | I <sub>LOL</sub>       | <br> 0.4 V <u>&lt;</u> V <sub>OUT</sub> <u>&lt;</u> | <u>+</u> +2.4 V                                                          | All              | 1, 2, 3           | -10                | +10                                      | μ <b>Α</b>                            |

| Output leakage<br>current high,<br>open drain<br>outputs | I<br>I LOH<br>I<br>I   | }<br> <br>                                          |                                                                          |                  |                   | -10                | +10                                      | μ <b>Α</b>                            |

| Input low current<br>(input and bi-<br>directional)      | IIL                    | 0.4 V < VIN <                                       | 2.4 V                                                                    |                  |                   | <br>  -10<br>      | +10                                      | <br>  μ <b>A</b><br>                  |

| Input high current<br>(input and bi-<br>directional)     | IIH                    | -<br> <br> -<br>                                    |                                                                          |                  |                   | -10                | +10                                      | μ <b>Α</b>                            |

| Maximum frequency 1/                                     | f <sub>MAX</sub>       |                                                     |                                                                          | 01<br>02         | 9, 10, 11         | 4.0                |                                          | MHz                                   |

| Functional tests                                         |                        | See 4.3.1c                                          |                                                                          |                  | 7, 8              |                    |                                          |                                       |

| See footnotes at en                                      | d of tab               | ole.                                                |                                                                          |                  |                   |                    |                                          |                                       |

| STANDA                                                   |                        |                                                     | SIZE<br>A                                                                |                  |                   |                    |                                          | · · · · · · · · · · · · · · · · · · · |

| MILITARY DEFENSE ELECTRO                                 | -                      | PPLY CENTER                                         | <del></del>                                                              | REVISION LEVEL   |                   | SHEET              | 5                                        |                                       |

| TA                             | BLE I. <u>E</u> I                      | ectrical perform | ance charac                                                         | teristics -           | Continued          | l <b>.</b>              | <del></del>   |

|--------------------------------|----------------------------------------|------------------|---------------------------------------------------------------------|-----------------------|--------------------|-------------------------|---------------|

| Parameter                      | Symbol                                 | · I Se           | Conditions<br>55°C to +12<br>55 to 5.5<br>ee figure 3<br>50 pF ±10% | 5°C<br>V              | <br> -<br> -<br>   | <br> <br> <br>  Maximum | Unit          |

|                                |                                        | Reference 2/     | Device<br> type                                                     | Group A<br>Isubgroups | <br>               | <br>                    | <br>          |

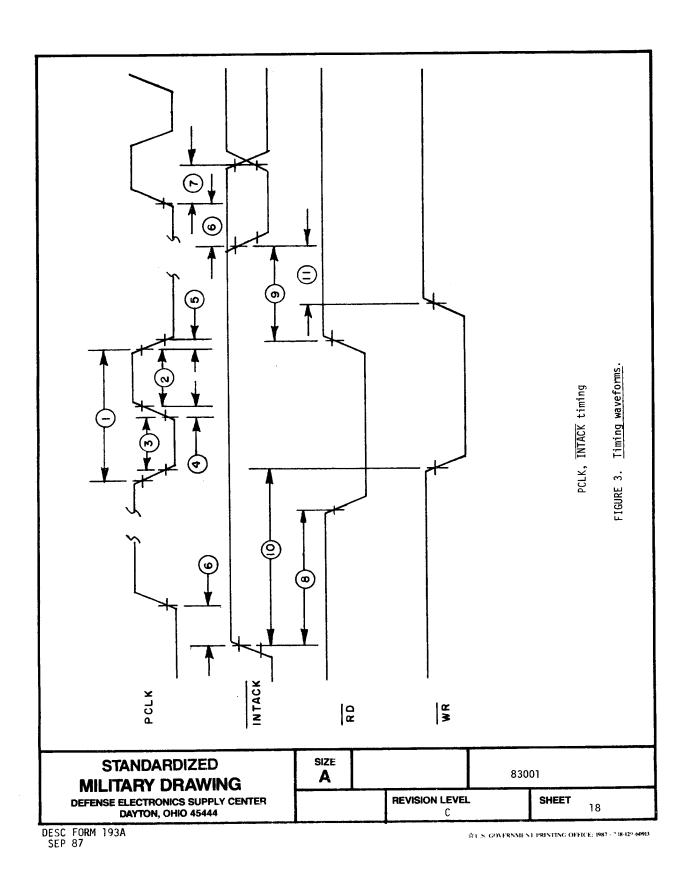

| PCLK cycle<br>time             | tcYC1                                  | 1                | <br>  01<br>  02                                                    | 9,10,11               | 250<br>165         | 1 4000<br>1 4000        | l ns          |

| PCLK width high 1/             | tpWH1                                  | 2                | 01                                                                  | 9,10,11               | l<br>  105<br>  70 | l<br>i 2000<br>l 2000   | l<br>  ns<br> |

| PCLK width<br>low <u>1</u> /   | tpWL1                                  | 3                | 01 02                                                               | 9,10,11               | 105<br>70          | 2000<br>2000            | ns            |

| PCLK rise<br>time <u>1</u> /   | t <sub>RC1</sub>                       | 4                | 01 02                                                               | 9,10,11               | <br>               | <br>  20<br>  10        | ns            |

| PCLK fall time 1/              | t <sub>FC1</sub>                       | 5                | 01 02                                                               | 9,10,11               | <br>               | <br>  20<br>  15<br>    | l ns          |

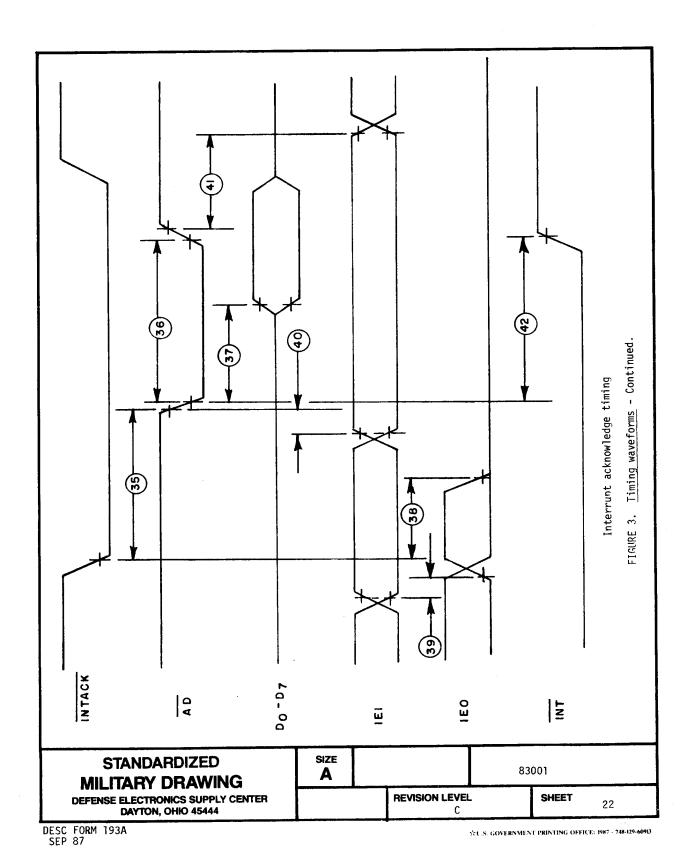

| INTACK to PCLK setup time 1/   | tSHL1<br>tSLH1                         | 6                | A11                                                                 | 9,10,11               | <br>  100<br>      | <br> <br> <br>          | ns            |

| INTACK to PCLK hold time 1/    | t <sub>HHL1</sub>                      | 7                | All                                                                 | 9,10,11               | ]<br>  0<br>       | [                       | ns            |

| INTACK to RD setup time 1/     | t <sub>SHL2</sub><br>t <sub>SLH2</sub> | 8                | A11<br>                                                             | 9,10,11               | I<br>  200<br>     | <br>                    | ns<br> <br>   |

| INTACK to RD hold time 1/      | t <sub>HHL2</sub>                      | 9                | A11                                                                 | 9,10,11               | <br>  0<br>        |                         | l ns          |

| INTACK to WR setup time 1/     | t <sub>SHL3</sub>                      | 10               | All                                                                 | 9,10,11               | 200<br>            |                         | ns            |

| INTACK to WR + hold time 1/    | t <sub>HHL3</sub>                      | 11               | All                                                                 | 9,10,11               | [<br>  0<br>       | <br> <br> <br>          | ns            |

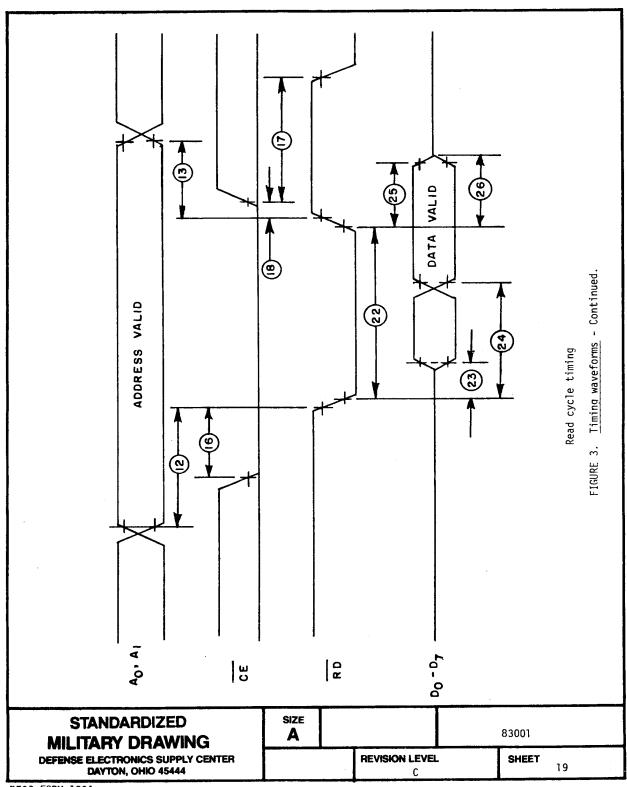

| Address to<br>RD + setup time  | t <sub>SHL4</sub>                      | 12               | All                                                                 | 9,10,11               | l 80<br>l          | <br> <br> <br>          | l ns          |

| See footnotes at end (         | of table.                              |                  |                                                                     | •                     |                    |                         |               |

| STANDAR<br>MILITARY D          |                                        | Siz              |                                                                     |                       |                    | 83001                   |               |

| DEFENSE ELECTRONI<br>DAYTON, O | CS SUPPLY (                            |                  |                                                                     | REVISION LEV          | 'EL                | SHEET                   | 6             |

| TA                                                                                              | ABLE I. El                                        | ectrical pe    | rformance           | e chara  | cteristics -  | Continue   | 1.              |      |

|-------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------|---------------------|----------|---------------|------------|-----------------|------|

| Parameter                                                                                       | Symbol                                            | V <sub>(</sub> | Conditions          |          |               | Minimum    | <br>            | Unit |

| Address to RD + hold time 1/                                                                    | i<br>  t <sub>HHL</sub> 4<br>  t <sub>HLH</sub> 4 | 13             | ]<br>[<br>]<br>     | A11      | 9,10,11       | 0          | [<br> <br> <br> | ns   |

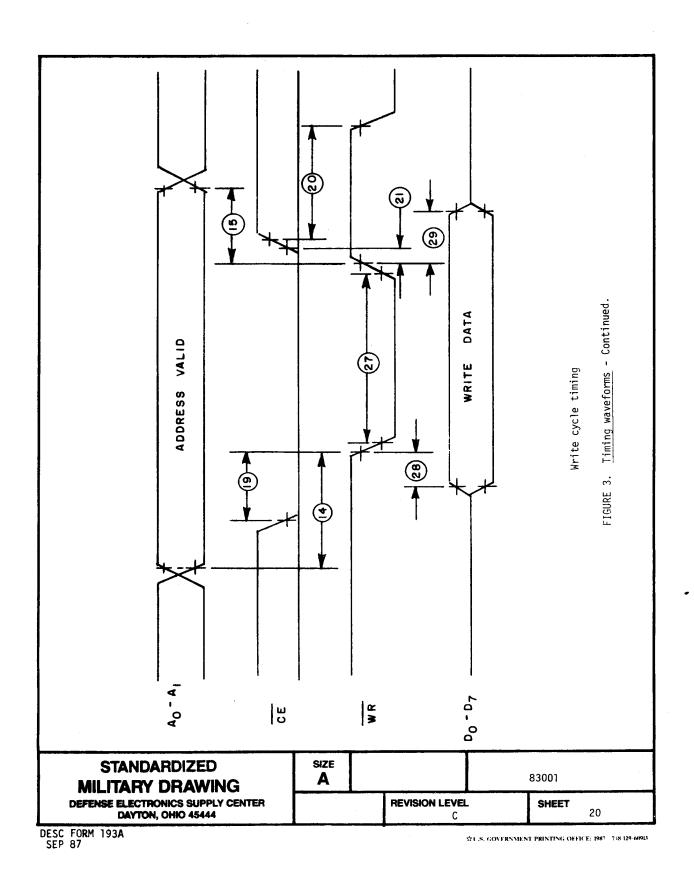

| Address to<br>WR + setup time                                                                   | t <sub>SHL5</sub>                                 | 14             | <br>                | A1 1     | 9,10,11       | 80         |                 | l ns |

| Address to $\overline{WR}$ hold time $\underline{1}$ /                                          | tHHL5                                             | 15             | <br> <br> <br> <br> | All      | 9,10,11       | 0          |                 | l ns |

| CE low to RD + setup time 3/                                                                    | tSHL6                                             | 16             |                     | A1 1     | 9,10,11       | 0          |                 | l ns |

| CE high to $\overline{RD} + setup time 1/3/$                                                    | t <sub>SLH</sub> 7                                | 17             | <br> <br> <br>      | 01<br>02 | 9,10,11       | 100<br>70  | ]<br> <br>      | ns   |

| CE to RD † hold time 3/                                                                         | tHHL6                                             | 18             |                     | A11      | 9,10,11       | 0          | <br>            | ns   |

| CE low to WR + setup time                                                                       | t <sub>SHL8</sub>                                 | 19             |                     | A11      | 9,10,11       | 0          | <br>            | ns   |

| $\overline{\text{CE}}$ high to $\overline{\text{WR}}$ $\downarrow$ setup time $\underline{1}$ / | t <sub>SLH9</sub>                                 | 20             | ]<br> <br>          | 01<br>02 | 9,10,11       | 100<br>70  |                 | l ns |

| CE to WR + hold time                                                                            | <br>  t <sub>HHL</sub> 7<br>  t <sub>HLH</sub> 7  | 21             | I<br>I<br>I         | A1 1     | 9,10,11       | 0          | <br>            | ns   |

| $\frac{1}{3}$ to low width                                                                      | <br>  tpwL2<br>                                   | 22             | i<br>!<br>!         | 01<br>02 | 9,10,11       | 390<br>250 | <br> <br> <br>  | l ns |

| RD + to read data<br>active delay <u>1</u> /                                                    | tpHL1 tpLH1                                       | 23             |                     | All      | 9,10,11       | 0          | <br>            | ns   |

| $RD + to read data$ valid delay $\underline{1}/$                                                | tpHL2                                             | 24             | <br> <br> <br> <br> | 01<br>02 | 9,10,11       |            | i 255<br>i 180  | l ns |

| See footnotes at end o                                                                          | of table.                                         |                | •                   |          |               |            |                 |      |

| STANDAR MILITARY D DEFENSE ELECTRONIC DAYTON, OI                                                | RAWING<br>cs supply c                             | T              | SIZE<br>A           |          | REVISION LEVI |            | 83001<br>SHEET  | 7    |

| TA                                                    | BLE I. Ele                             | ctrical pe | erformance                                                                      | chara    | cteristics -                                                             | Continue    | 1.                                      |      |

|-------------------------------------------------------|----------------------------------------|------------|---------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------|-------------|-----------------------------------------|------|

| Parameter                                             | Symbol                                 | V          | T <sub>C</sub> = -55°C<br>V <sub>CC</sub> = 4.5<br>See f<br>C <sub>L</sub> = 50 |          | onditions<br>C to +125°C<br>5 to 5.5 V<br>figure 3<br>) pF ±10%<br> <br> |             | <br>                                    | Unit |

| RD † to read data<br>not valid delay                  | tpHL3<br>tpLH3                         | 25         |                                                                                 | A11      | 9,10,11                                                                  | 0           |                                         | ns   |

| RD + to read data<br>float delay <u>4</u> /           | tpHZ1                                  | 26         |                                                                                 | 01<br>02 | 9,10,11                                                                  |             | 70<br>45                                | ns   |

| $\overline{WR}$ low width $\underline{1}/$            | t <sub>PWL</sub> 3                     | 27         | i<br>1<br>1                                                                     | 01<br>02 | 9,10,11                                                                  | 390<br>250  |                                         | ns   |

| Write data to WR + setup time 1/                      | t <sub>SHL10</sub>                     | 28         |                                                                                 | All      | 9,10,11                                                                  | 0           |                                         | ns   |

| Write data to WR + hold time 1/                       | <sup>t</sup> нн∟8<br><sup>t</sup> н∟н8 | 29         |                                                                                 | A1 1     | 9,10,11                                                                  | 0           |                                         | ns   |

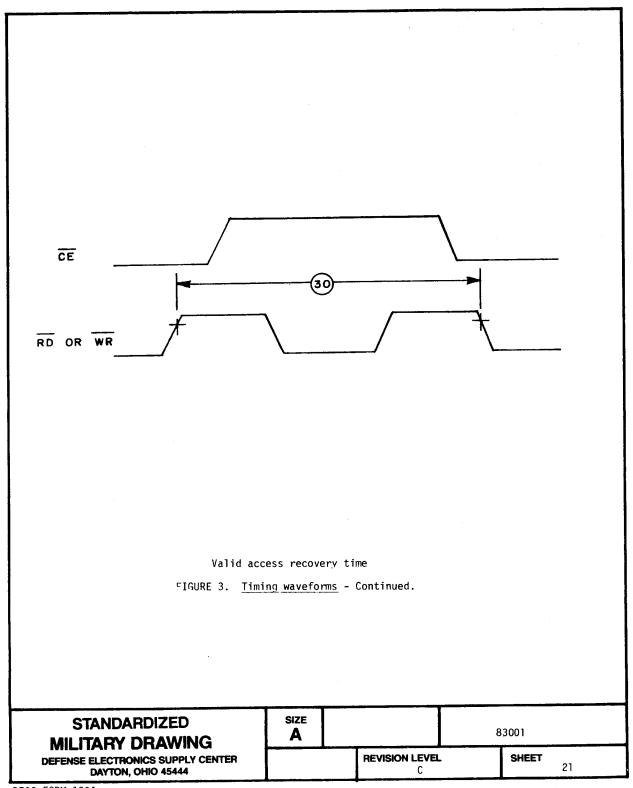

| Valid access recovery time 1/5/                       | t <sub>CYC2</sub>                      | 30         |                                                                                 | 01<br>02 | 9,10,11                                                                  | 1000<br>650 |                                         | ns   |

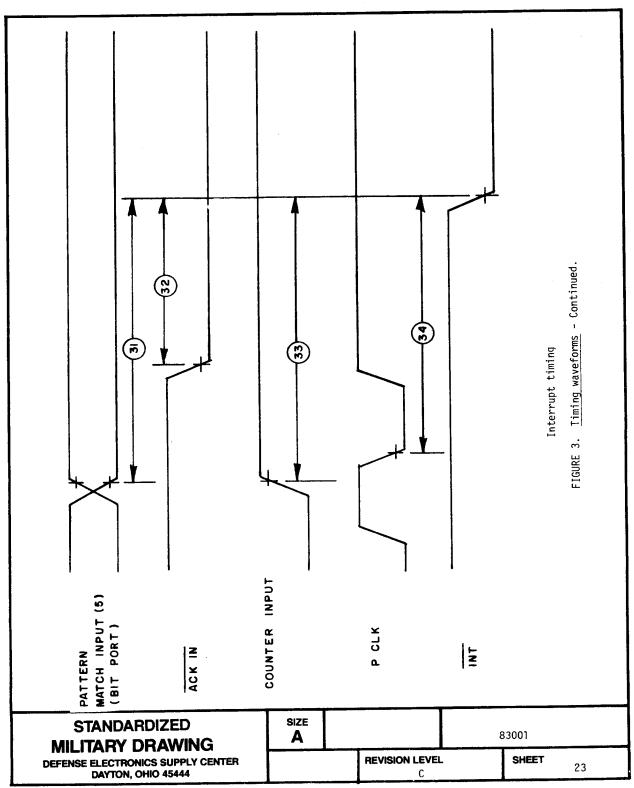

| Pattern match to INT delay (bit port) 1/              | t <sub>PHI_</sub> 4                    | 31         | <br> <br> <br>                                                                  | All      | 9,10,11                                                                  |             | <br> 2* (t <sub>CYC1</sub> ) <br>  +800 | ns   |

| ACKIN to INT delay<br>(port with hand-<br>shake) 1/6/ | t <sub>PHL5</sub>                      | 32         | <br> <br> <br> <br>                                                             | All      | 9,10,11                                                                  |             | 10* (t <sub>CYC1</sub> )<br>  +600      | ns   |

| Counter input to INT delay (counter mode) 1/          | t <sub>PHL6</sub>                      | 33         | j<br> <br> <br> <br>                                                            | All      | 9,10,11                                                                  |             | 2* (t <sub>CYC1</sub> )   +700          | ns   |

| PCLK to TNT delay<br>(timer mode) 1/                  | t <sub>PHL</sub> 7                     | 34         | -                                                                               | A1 1     | 9,10,11                                                                  |             | <br> 3* (tcyc1)<br>  +700               | ns   |

| INTACK to RD + (acknowledge) setup time 1/7/          | tSHL11<br>tSLH11                       | 35         | i<br> <br> <br> <br>                                                            | 01<br>02 | 9,10,11                                                                  | 350<br>250  | <br>                                    | ns   |

| See footnotes at end o                                | of table.                              |            |                                                                                 |          |                                                                          |             |                                         |      |

| STANDAR<br>MILITARY D                                 |                                        | ì          | SIZE<br><b>A</b>                                                                |          |                                                                          |             |                                         |      |

| DEFENSE ELECTRONI-<br>DAYTON, OI                      | CS SUPPLY C                            |            |                                                                                 |          | <b>REVISION LEV</b>                                                      | EL          | SHEET 8                                 |      |

| TAI                                                                                                      | BLE I. Ele                               | ctrical pe | rformance        | chara    | cteristics - | Continued                    | l.                     |           |

|----------------------------------------------------------------------------------------------------------|------------------------------------------|------------|------------------|----------|--------------|------------------------------|------------------------|-----------|

| Parameter                                                                                                | Symbol                                   |            |                  |          | Minimum      | <br> -<br> <br>  Maximum<br> | <br> <br>  Unit        |           |

| <br>                                                                                                     |                                          | l number   | r <del>-</del> ' | type     | subgroups    |                              |                        | <u> </u>  |

| RD acknowledge                                                                                           | tpWL4                                    | 36         |                  | 01<br>02 | 9,10,11      | 350<br>250                   | <br> <br>              | ns        |

| RD <sup>+</sup> (acknowledge) :<br>to read data :<br>valid delay <u>1</u> /                              | tpHL8<br>tpLH8                           | 37         |                  | 01<br>02 | 9,10,11      |                              | <br>  250<br>  180<br> | l ns<br>l |

| INTACK + to 1/ 7/ I<br>IEO + delay I                                                                     | tpHL9                                    | 38         |                  | 01<br>02 | 9,10,11      |                              | 1<br>350<br>250        | ns        |

| IEI to IEO delay <u>1/7</u> /                                                                            | tpHL 10                                  | 39         | <br>             | 01<br>02 | 9,10,11      |                              | <br>  150<br>  100<br> | ns        |

| IEI to $\overline{RD}$ $^{\dagger}$ (acknowledge) setup time $\underline{1}/\underline{7}/\underline{1}$ | t <sub>SHL12</sub><br>t <sub>SLH12</sub> | 40         |                  | 01<br>02 | 9,10,11      | 100<br>70                    |                        | ns        |

| IEI to RD +<br>(acknowledge)<br>hold time <u>1</u> /                                                     | tHHL9<br>tHLH9                           | 41         | <br>             | 01<br>02 | 9,10,11      | 100<br>  70<br>              | <br>                   | ns        |

| RD → (acknowledge) l<br>to INT+ delay 1/                                                                 | tpHL11                                   | 42         |                  | A1 1     | 9,10,11      |                              | 600                    | ns        |

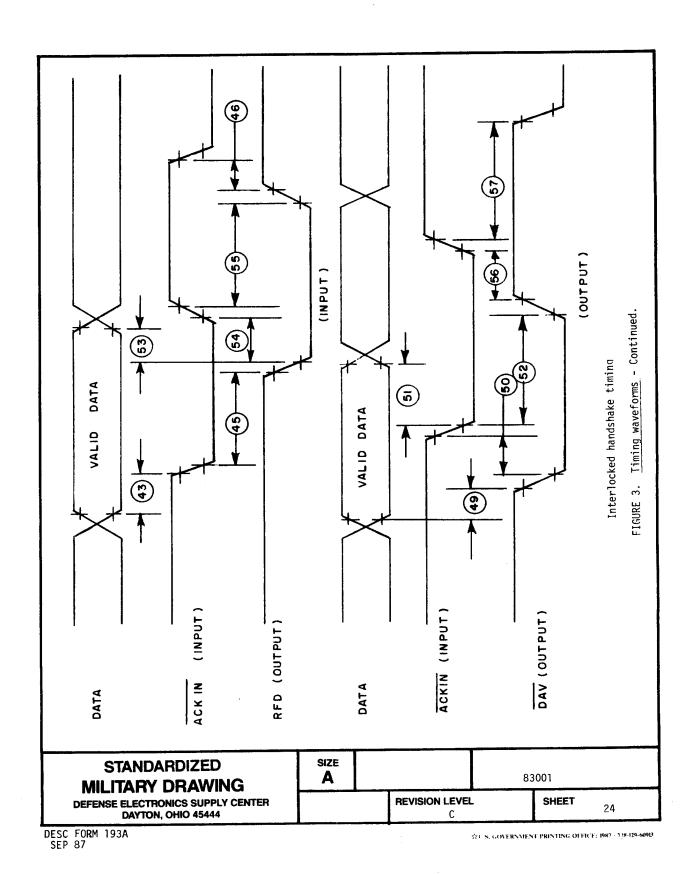

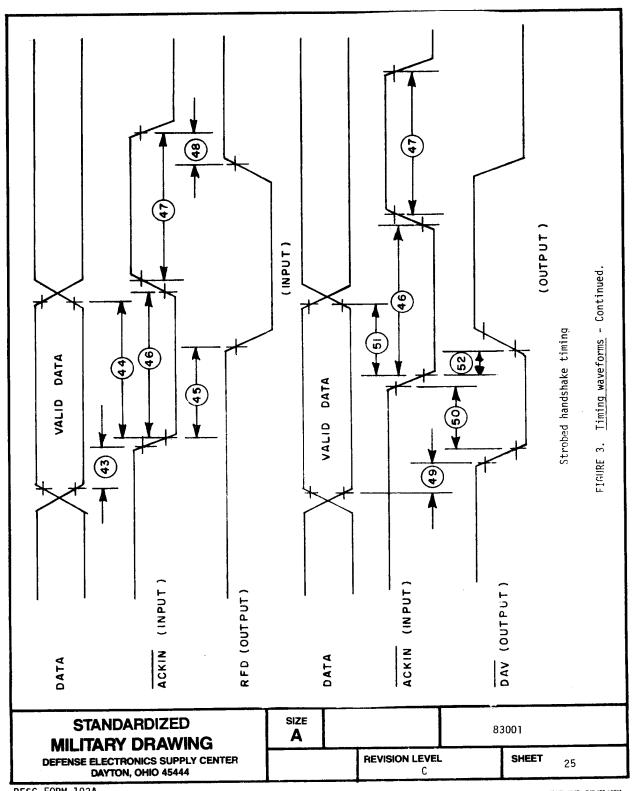

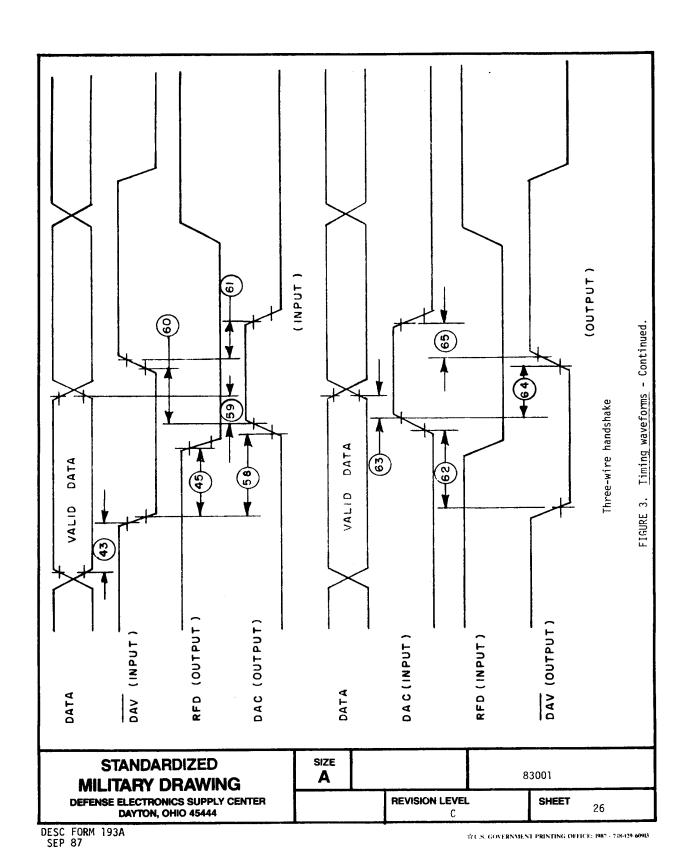

| Data input to ACKIN +   setup time <u>1</u> /                                                            | tSHL13<br>tSLH13                         | 43         | <br> <br> <br>   | A11      | 9,10,11      | <br>  0<br> <br>             | <br>                   | l ns      |

| ACKIN <sup>†</sup> to RFD <sup>†</sup> delay <u>1</u> /                                                  | tpHi_12                                  | 45         |                  | A11      | 9,10,11      | 0                            |                        | ns        |

| RFD <sup>†</sup> to ACKIN <sup>↓</sup><br>delay <u>1</u> /                                               | tHHL10                                   | 48         |                  | A11      | 9,10,11      | 0                            |                        | ns        |

| See footnotes at end o                                                                                   | f table.                                 |            |                  |          |              |                              |                        |           |

| STANDARI<br>MILITARY D                                                                                   |                                          |            | SIZE<br>A        |          |              |                              | 83001                  |           |

| DEFENSE ELECTRONIC<br>DAYTON, OF                                                                         | CS SUPPLY C                              |            |                  |          | REVISION LEV | EL                           | 9                      |           |

| TA                                                                                  | BLE I. Ele                                  | ectrical pe       | rformanc                                                                                                                                                                                                  | e chara  | cteristics - | Continued                       | •                   |                  |

|-------------------------------------------------------------------------------------|---------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------|---------------------------------|---------------------|------------------|

| Parameter                                                                           | Symbol Symbol                               | Vo                | Conditions<br>  t <sub>C</sub> = -55°C to +125°C<br>  V <sub>CC</sub> = 4.5 to 5.5 V<br>  See figure 3<br>  C <sub>L</sub> = 50 pF ±10%<br>  Reference 2/   Device   Group A   number   ltype   subgroups |          |              | <br>                            | Maximum             | Unit             |

|                                                                                     |                                             | number            | . –                                                                                                                                                                                                       | type<br> | subgroups    |                                 |                     | <u> </u>         |

| Data out to $\overline{DAV}$ + setup time $\underline{1}/\underline{8}/$            | tpHL13<br>tpLH13                            | 49                | !                                                                                                                                                                                                         | 01<br>02 | 9,10,11      | 25<br>20                        |                     | ns               |

| DAV+ to ACKIN + delay $\underline{1}/$                                              | t <sub>SHL14</sub>                          | <br>  50<br>      |                                                                                                                                                                                                           | A11      | 9,10,11      | l<br>  0<br> <br>               |                     | l ns             |

| Data out to ACKIN+ hold time 1/                                                     | <sup>‡</sup> ННL 11<br><sup>‡</sup> НL Н 11 | 51                |                                                                                                                                                                                                           | A11      | 9,10,11      | <br> 2*(t <sub>CYC1</sub> )<br> |                     | ns               |

| ACKIN+ to DAV † delay 1/                                                            | tpLH14                                      | 52                |                                                                                                                                                                                                           | A11      | 9,10,11      | <br> 2*(t <sub>CYC1</sub> )<br> |                     | ns               |

| RFD+ to ACKIN+ delay (inter- locked hand- shake) <u>1</u> /                         | tHLH12                                      | <br>  54<br> <br> |                                                                                                                                                                                                           | All      | 9,10,11      | <br>  0<br> <br> <br>           |                     | ns               |

| ACKIN+(DAV)+ to RFD+ delay (interlocked and three wire handshake) 1/                | tpLH15                                      | 55                |                                                                                                                                                                                                           | A11      | 9,10,11      | 0<br>  0<br>   <br>             |                     | ns<br> <br> <br> |

| DAV + ACKIN +<br>(RFD) + (inter-<br>locked and three<br>wire handshake) 1/          | t <sub>HLH13</sub>                          | 56                |                                                                                                                                                                                                           | A11      | 9,10,11      | 0                               |                     | ns<br>l          |

| ACKIN + (RFD) +<br>to DAV+ delay<br>(interlocked<br>and three wire<br>handshake) 1/ | t <sub>PLH16</sub>                          | 57                | !                                                                                                                                                                                                         | A11      | 9,10,11      | 0                               | <br>                | ns               |

| DAV +to DAC +<br>delay (input three<br>wire handshake) <u>1</u> /                   | tPLH17                                      | 58                |                                                                                                                                                                                                           | A11      | 9,10,11      | 0                               | <br> <br> <br> <br> | ns               |

| See footnotes at end o                                                              | of table.                                   | ·                 |                                                                                                                                                                                                           |          |              |                                 |                     |                  |

| STANDAR                                                                             | DIZED                                       |                   | SIZE                                                                                                                                                                                                      | T        |              |                                 | 02221               |                  |

| MILITARY D DEFENSE ELECTRONIC DAYTON, OI                                            | CS SUPPLY C                                 | 1                 | <u> </u>                                                                                                                                                                                                  | 1        | REVISION LEV | /EL                             | 83001<br>SHEET      | 10               |

| TA                                                               | BLE I. Ele                  | ctrical pe     | rformance           | chara    | cteristics - | Continued              | •     |             |

|------------------------------------------------------------------|-----------------------------|----------------|---------------------|----------|--------------|------------------------|-------|-------------|

| Parameter                                                        | <br>  Symbol                | V <sub>C</sub> | Conditions          |          | Minimum      | Maximum                | Unit  |             |

| Data input to DAC † hold time (three wire handshake) 1/          | tHHL14<br>tHLH14            | 59             | <br>  <br> <br>     | A11      | 9,10,11      | 0                      |       | l ns        |

| DAC † to DAV † delay (input three wire handshake) 1/             | tHLH15                      | 60             |                     | All      | 9,10,11      | 0                      | i     | ns          |

| DAV † to DAC † delay (input three wire handshake) 1/             | tpHL18                      | 61             | <br> <br> <br> <br> | A11      | 9,10,11      | 0                      |       | ns l        |

| DAV + to DAC † delay (output three wire handshake) 1/            | tSLH15                      | 62             |                     | A11      | 9,10,11      | 0                      |       | l ns        |

| Data output to DAC † hold time (three wire handshake) <u>1</u> / | tpHL19<br>tpLH19            | 63             |                     | A11      | 9,10,11      | 2*(t <sub>CYC1</sub> ) |       | ns          |

| DAC † to DAV † delay (output three wire handshake) 1/            | tpHL 20                     | 64             |                     | A11      | 9,10,11      | 2*(t <sub>CYC1</sub> ) |       | ns<br> <br> |

| DAV + to DAC + delay (output three wire handshake) 1/            | tHHL16                      | 65             | i<br>i<br>i         | A11      | 9,10,11      | 0                      |       | ns          |

| Counter input cycle time 1/                                      | tcyc3                       | 66             | ]<br> <br> <br>     | 01<br>02 | 9,10,11      | 500<br>330             |       | l ns        |

| Counter input<br>high width <u>1</u> /                           | <br>  t <sub>PWH5</sub><br> | 67             | <br> <br> <br>      | 01<br>02 | 9,10,11      | 230<br>1 150           |       | ns          |

| See footnotes at end                                             | ·                           | 1              |                     | 1        |              | 1                      |       |             |

| STANDAR<br>MILITARY D                                            |                             | <u> </u>       | SIZE<br>A           |          |              |                        | 83001 |             |

| DEFENSE ELECTRONI<br>DAYTON, O                                   |                             | NTER           |                     |          | REVISION LEV | EL                     | SHEET | 11          |

| Parameter                                   | <br> <br> <br>  Symbol T | tc = -5!<br>Vcc = 4.<br>See | onditions C to +12 5 to 5.5 c figure ( 50 pF ±109 | 25°C<br>V  <br>3     | !<br> <br> <br>  Minimum<br> | <br> <br> <br>  Maximum            | Unit         |

|---------------------------------------------|--------------------------|-----------------------------|---------------------------------------------------|----------------------|------------------------------|------------------------------------|--------------|

|                                             |                          | Reference 2/<br>number      | Device                                            | Group A<br>subgroups | <b>7</b><br>                 | ]<br> <br>                         |              |

| Counter input 1/                            | tpWL5                    | 68                          | 01<br>  02                                        | 9,10,11              | 230<br>150                   |                                    | ns           |

| Counter input fall time 1/                  | t <sub>FC2</sub>         | 69                          | <br>  01<br>  02                                  | 9,10,11              |                              | 20<br>  25<br>  15                 | ns           |

| Counter input rise time 1/                  | t <sub>RC2</sub>         | 70                          | 01 02                                             | 9,10,11              |                              | 20<br>  15                         | ns           |

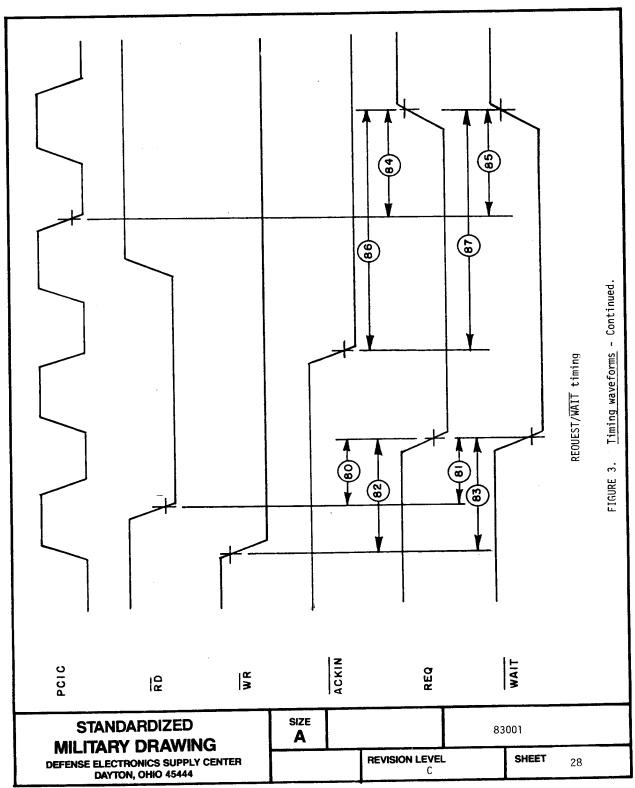

| RD + to REQ +<br>delay                      | tpHL21                   | 80                          | 01                                                | 9,10,11              |                              | <br>  500<br>                      | ns           |

| RD → to WAIT →<br>delay                     | t <sub>PHL22</sub>       | 81                          | 01                                                | 9,10,11              |                              | 500                                | ns           |

| WR + to REQ+<br>delay                       | t <sub>PHL23</sub>       | 82                          | 01                                                | 9,10,11              |                              | 500                                | ns           |

| WR + to WAIT+<br>delay                      | tpHL24                   | 83                          | 01                                                | 9,10,11              |                              | 500                                | ns           |

| PCLK + to REQ +<br>delay                    | t <sub>PHL25</sub>       | 84                          | 01                                                | 9,10,11              |                              | 300 I                              | ns           |

| PCLK+ to WAIT +<br>delay                    | tPHL26                   | 85                          | 01                                                | 9,10,11              |                              | 300 I                              | ns           |

| ACKIN+ to REQ+<br>delay <u>6</u> /          | t <sub>PHL27</sub>       | 86                          | 01                                                | 9,10,11              |                              | <br> 8*(t <sub>CYC1</sub> )        | ns           |

| ACKIN+ to WAIT+ delay 6/                    | tPHL28                   | 87                          | 01                                                | 9,10,11              |                              | 10*(t <sub>CYC1</sub> ) <br>  +600 | ns           |

| See footnotes at end                        | i of table.              |                             | <u> </u>                                          |                      |                              | • ,                                | <del> </del> |

| STANDA                                      |                          | SIZE<br>A                   |                                                   |                      |                              |                                    | _            |

| MILITARY (<br>DEFENSE ELECTRON<br>DAYTON, ( | NICS SUPPLY CENT         | <u> </u>                    |                                                   | REVISION LEVE        | L                            | 83001<br>SHEET                     |              |

| T.F                                                                                             | ABLE I. Ele                  | ctrical perf        | ormance chara                                                  | cteristics -   | Continue                | 1.                           |                |

|-------------------------------------------------------------------------------------------------|------------------------------|---------------------|----------------------------------------------------------------|----------------|-------------------------|------------------------------|----------------|

| Parameter                                                                                       | <br> <br> <br>  Symbol       | Vcc                 | Condition = -55°C to +1° = 4.5 to 5.5° See figure = 50 pF ±10° | 25°C<br>V<br>3 | <br>                    | <br> <br> -<br>  Maximum<br> | Unit           |

|                                                                                                 | !<br>!<br>[                  | number =            | type                                                           | subgroups      |                         | <br>                         |                |

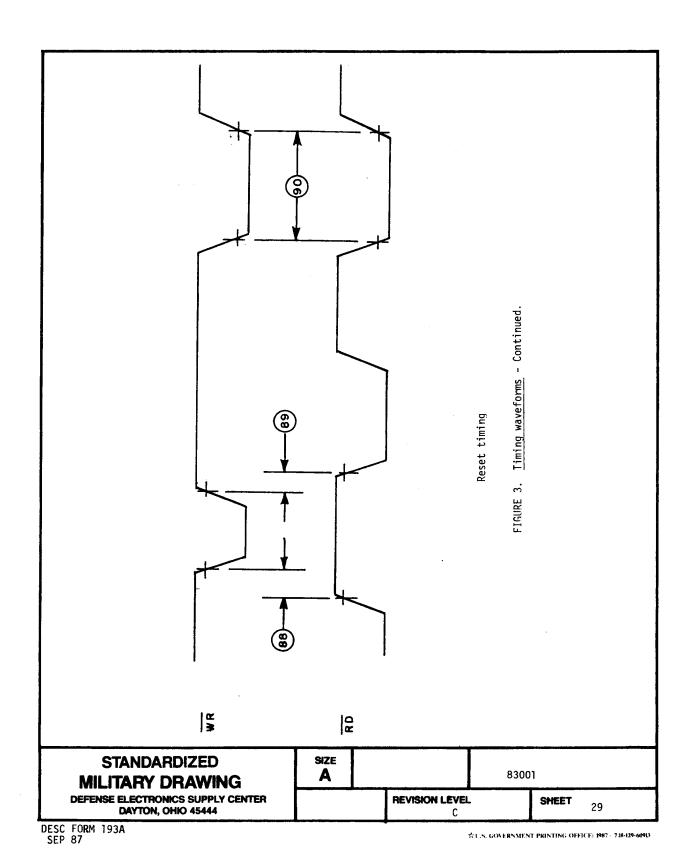

| Delay from $\overline{\text{RD}}$ + , to $\overline{\text{WR}}$ + for no reset $\underline{1}/$ | t <sub>SHL16</sub>           | 88                  | A11                                                            | 9,10,11        | 50<br>  50<br>          | <br>                         | ns             |

| Delay from WR †<br>to RD + for no<br>reset <u>1</u> /                                           | t <sub>SHL17</sub><br> <br>  | 89                  | All                                                            | 9,10,11        | <br>  50<br> <br>       | [<br> <br> <br> <br>         | ns             |

| Width of RD and<br>WR low to<br>insure reset                                                    | <br>  tpwL6<br>              | 90                  | All                                                            | 9,10,11        | <br>  250<br> <br> <br> | <br>                         | l ns<br>l<br>l |

| Any input rise time not otherwise specified 1/                                                  | t <sub>RI1</sub>             | 91                  | A11                                                            | 9,10,11        | <br>                    | <br>  100<br> <br> <br>      | l ns           |

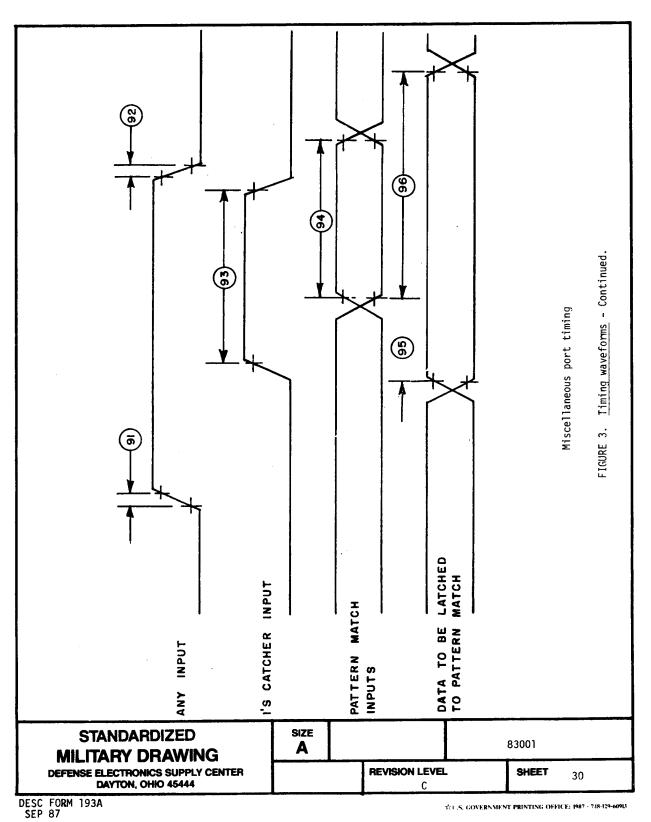

| Any input fall time not otherwise specified 1/                                                  | t <sub>FI1</sub>             | <br>  92<br> <br>   | A11                                                            | 9,10,11        | <br>                    | <br>  100<br> <br> <br>      | ns<br>ns       |

| l's catcher high<br>width <u>1</u> / <u>9</u> /                                                 | tpwH7                        | 93                  | <br>  01<br>  02                                               | 9,10,11        | 250<br>170              | [<br> <br> <br>              | hs<br> <br>    |

| Pattern match input valid (bit port)                                                            | tPWL8                        | 94                  | 01 02                                                          | 9,10,11        | 750<br>500              | ]<br> <br> <br>              | ns             |

| Data latched on pattern match setup time (bit port) 1/                                          | tSHL18                       | 95<br>  95<br> <br> | All                                                            | 9,10,11        | 0                       |                              | ns             |

| Data latched on pattern match hold time (bit port) 1/                                           | <br>  tHHL17<br>  tHLH17<br> | 96                  | 01 02                                                          | 9,10,11        | 1 1000<br>1 650<br>1    |                              | l ns           |

| See footnotes on next                                                                           | page.                        | ····                |                                                                |                | ·                       |                              |                |

| STANDAF                                                                                         |                              |                     | SIZE<br>A                                                      |                |                         | 83001                        |                |

| MILITARY D<br>DEFENSE ELECTRON<br>DAYTON, O                                                     | ICS SUPPLY C                 |                     |                                                                | REVISION LEV   | /EL                     | SHEET                        | 13             |

- 1/ Guaranteed if not tested.

- 2/ The reference number refers to the parameter being measured on figure 3.

- 3/ Parameter does not apply to Interrupt Acknowledge transactions.

- 4/ Float delay is measured to the time when the output has changed 0.5 V with minimum ac load and maximum dc load.

- 5/ t<sub>CYC2</sub> is 1  $\mu$ s or t<sub>CYC1</sub>, whichever is longer.

- 6/ The delay is from  $\overline{DAV}$  + for 3-wire input handshake. The delay is from DAC + for 3-wire output handshake.

- 7/ The parameters for the devices in any particular daisy chain must meet the following constraint: The delay from  $\overline{\text{INTACK}}$  + to  $\overline{\text{RD}}$  + must be greater than the sum of tdIA(IEO) for the highest priority peripheral, tsIEI(RDA) for the lowest priority peripheral, and tdIEI(IEO) for each peripheral separating them in the chain.

- 8/ This time can be extended through the use of deskew timers.

- 9/ If the input is programmed inverting, a low-going pulse of the same width will be detected.

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE

A

83001

REVISION LEVEL

SHEET

DESC FORM 193A SEP 87

☆U.S. GOVERNMENT PRINTING OFFICE: 1987 - 748-129-60913

\$\tau\_s.\text{ GOVERNMENT PRINTING OFFICE: 1987 - 7 i8-120-60913

771. S. GOVERNMENT PRINTING OFFICE: 1987 - 748-129-60913

$\dot{\Upsilon} U.S.$  GOVERNMENT PRINTING OFFICE: 1987 - 748-429-60913

ទាំប.S. GOVERNMENT PRINTING OFFICE: 1987 - 748-129-60913

$\Delta$  L.S. GOVERNMENT PRINTING OFFICE: 1987 - 748-129-60913

$\dot{\gamma}_{V,S,\text{-}GOV}$ ERNMENT PRINTING OFFICE: 1987 - 748-129-60913

☆ U.S. GOVERNMENT PRINTING OFFICE: 1987 - 748-129-60913

\$1.5. GOVERNMENT PRINTING OFFICE: 1987 - 748-129-60913

- 3.5 Certificate of compliance. A certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in 6.5. The certificate of compliance submitted to DESC-ECS prior to listing as an approved source of supply shall state that the manufacturer's product meets the requirements of MIL-STD-883 (see 3.1 herein) and the requirements herein.

- 3.6 Certificate of conformance. A certificate of conformance as required in MIL-STD-883 (see 3.1 herein) shall be provided with each lot of microcircuits delivered to this drawing.

- 3.7 Notification of change. Notification of change to DESC-ECS shall be required in accordance with MIL-STD-883 (see 3.1 herein).

- 3.8 Verification and review. DESC, DESC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 4. QUALITY ASSURANCE PROVISIONS

- 4.1 Sampling and inspection. Sampling and inspection procedures shall be in accordance with section 4 of MIL-M-38510 to the extent specified in MIL-STD-883 (see 3.1 herein).

- 4.2 <u>Screening</u>. Screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection. The following additional criteria shall apply:

- a. Burn-in test (method 1015 of MIL-STD-883).

- (1) Test condition A, B, C, or D using the circuit submitted with the certificate of compliance (see 3.5 herein).

- (2)  $T_A = +125^{\circ}C$ , minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein, except interim electrical parameter tests prior to burn-in are optional at the discretion of the manufacturer.

- 4.3 Quality conformance inspection. Quality conformance inspection shall be in accordance with method 5005 of MIL-STD-883 including groups A, B, C, and D inspections. The following additional criteria shall apply.

- 4.3.1 Group A inspection.

- a. Tests shall be as specified in table II herein.

- b. Subgroups 5 and 6 in table I, method 5005 of MIL-STD-883 shall be omitted.

- c. Subgroup 7 functional test shall include verification of programming set.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br><b>A</b> |                | 8: | 33001    |  |

|------------------------------------------------------|------------------|----------------|----|----------|--|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | REVISION LEVEL | -  | SHEET 31 |  |

## 4.3.2 Groups C and D inspections.

- a. End-point electrical parameters shall be as specified in table II herein.

- b. Steady-state life test (method 1005 of MIL-STD-883) conditions:

- (1) Test condition A, B, C, or D using the circuit submitted with the certificate of compliance (see 3.5 herein).

- (2)  $T_A = +125^{\circ}C$ , minimum.

- (3) Test duration: 1,000 hours, except as permitted by appendix B of MIL-M-38510 and method 1005 of MIL-STD-883.

TABLE II. Electrical test requirements.

| MIL-STD-883 test requirements                                      | Subgroups<br>(per method<br>5005, table I) |

|--------------------------------------------------------------------|--------------------------------------------|

| Interim electrical parameters (method 5004)                        |                                            |

| Final electrical test parameters (method 5004)                     | 1*,2,3,9                                   |

| Group A test requirements (method 5005)                            | 1,2,3,7,8,9,<br>10, 11**                   |

| Groups C and D end-point<br>electrical parameters<br>(method 5005) | 1,2,3                                      |

$\star$  PDA applies to subgroup 1.

## 5. PACKAGING

5.1 Packaging requirements. The requirements for packaging shall be in accordance with MIL-M-38510.

## 6. NOTES

- 6.1 Intended use. Microcircuits conforming to this drawing are intended for use when military specifications do not exist and qualified military devices that will perform the required function are not available for OEM application. When a military specification exists and the product covered by this drawing has been qualified for listing on QPL-38510, the device specified herein will be inactivated and will not be used for new design. The QPL-38510 product shall be the preferred item for all applications.

- 6.2 Replaceability. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.3 Comments. Comments on this drawing should be directed to DESC-ECS, Dayton, Ohio 45444, or telephone 513-296-5375.

| STANDARDIZED MILITARY DRAWING                        | SIZE<br><b>A</b> |    |              | 83001    |  |

|------------------------------------------------------|------------------|----|--------------|----------|--|

| DEFENSE ELECTRONICS SUPPLY CENTER DAYTON, OHIO 45444 |                  | RE | VISION LEVEL | SHEET 32 |  |

DESC FORM 193A SEP 87

<sup>\*\*</sup> Subgroups 10 and 11, if not tested, shall be guaranteed to the specified limits in table I.

6.4 Terminal and functional definitions. Terminal and functional definitions and descriptions for this device shall be as follows: Interrupt enable in (input, active high). When this line is active, the CIO is IEI able to interrupt the CPU. Interrupt enable out (output, active high). This output is high only if IEI is high and the CPU is not servicing an interrupt from this CIO. In conjunction with IEI, this line can be used to implement a system-wide interrupt priority daisy IE0 chain. Interrupt request (output, open drain, active low). This signal is pulled low when INT the CIO requests an interrupt. Interrupt acknowledge (input, active low). This signal indicates to the CIO that INTACK an interrupt acknowledge cycle is in progress. INTACK must be synchronized to P clock. Port A I/O lines (bidirectional, tristate or open drain). These eight I/O lines transfer information between the CIO's port A and external devices. PAO-PA7 Port B I/O lines (bidirectional, tristate or open drain). These eight I/O lines transfer information between the CIO's port B and external devices. They also PRO-PR7 provide external access to counter/timers 1 and 2. Port C I/O lines (bidirectional, tristate or open drain). These four I/O lines are used to provide handshake, WAIT, and REQUEST lines for ports A and B, to provide PCO-PC3 external access to counter/timer 3 or to the CIO's port C. Peripheral clock (input, TTL compatible). This is a peripheral clock that may be, but is not necessarily the CPU clock. It is used with the timers and the REQUEST/WAIT logic. The maximum input frequency is 4 MHz. PCLK Address lines (input). These two lines are used to select the register involved in A0-A1 a data transaction between the CIO and CPU. Chip enable (input, active low). A low level on this input enables the CPU to be CE read from or written to. Data bus (bidirectional, tristate). These eight data lines are used for transfers DO-D7 between the CPU and the CIO. Read (input, active low). This signal indicates that a CPU is reading from the RD \* CIO. During an INT ACK cycle, gates the interrupt vector on to data bus. Write (input, active low). This signal indicates a CPU write to the CIO. **₩**R \* When RD and WR are detected low at same time (normally an illegal condition) the device is reset. SIZE **STANDARDIZED** Α 83001 MILITARY DRAWING **DEFENSE ELECTRONICS SUPPLY CENTER REVISION LEVEL**

DESC FORM 193A SEP 87

☆ U.S. GOVERNMENT PRINTING OFFICE: 1987--549-096

33

SHEET

С

DAYTON, OHIO 45444

6.5 Approved source of supply. An approved source of supply is listed herein. Additional sources will be added as they become available. The vendor listed herein has agreed to this drawing and a certificate of compliance (see 3.5) has been submitted to DESC-ECS.

| Military<br>drawing<br>part number | Vendor<br>  CAGE<br>  number | Vendor<br>  similar par<br>  number <u>1</u> |    | Replacement<br> military specification<br>  part number |

|------------------------------------|------------------------------|----------------------------------------------|----|---------------------------------------------------------|

| 8300101QX<br>8300101YX             | 56708<br>56708               | <br> Z0853604CMB<br> Z0853604LMB             | 2/ |                                                         |

| 83001020X<br>8300102YX             | 56708<br>56708               | <br> Z0853606CMB<br> Z0853606LMB             | 3/ |                                                         |

- $\frac{1}{I}$  Caution: Do not use this number for item acquisition. Items acquired to this number may not satisfy the performance requirements of this drawing.

- 2/ Part was previously designated Z8536CMB.

- 3/ Part was previously designated Z8536ACMB.

Vendor CAGE number 56708 Vendor name and address

Zilog Incorporated 210 Hacienda Avenue Campbell, California 95008

STANDARDIZED

MILITARY DRAWING

DEFENSE ELECTRONICS SUPPLY CENTER

DAYTON, OHIO 45444

SIZE A 83001

REVISION LEVEL SHEET 34

DESC FORM 193A SEP 87