# **MULTILEVEL PIPELINE REGISTERS** Integrated Device Technology, Inc.

16-BIT CMOS

IDT73200 IDT73201

#### **FEATURES:**

- IDT73200: Eight 16-bit high-speed pipeline registers

- · IDT73201: Seven 16-bit high-speed pipeline registers plus a direct feed-through path

- 12ns to 20ns access time

- · Programmable multilevel register configurations

- Powerful instruction set: transfer, hold, load directly

- Functionally replaces four Am29520s

- Read/Write buffer for 32-bit RISC/CISC microprocessors

- Applications as temporary address storage or programmable pipeline registers for DSP products

- Coefficient storage for FIR filters

- Three-state outputs

- TTL-compatible

- Produced with advanced submicron CEMOS™ high-performance technology

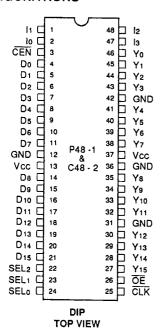

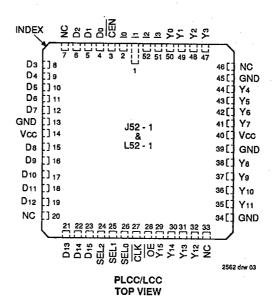

- Available in 48-pin plastic and ceramic DIP and 52-pin surface mount PLCC and LCC

- · Military product compliant to MIL-STD-883. Class B

## **DESCRIPTION:**

The IDT73200 and IDT73201 are mutilevel pipeline registers. With IDT's high-performance CEMOS™ technology, the IDT73200 and IDT73201 have access times of 12ns.

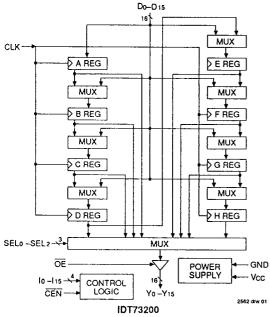

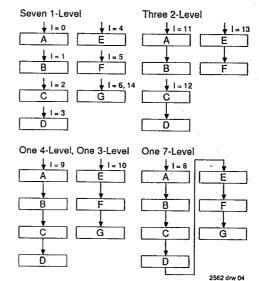

The IDT73200 contains eight 16-bit registers which can be configured as one 8-level, two 4-level, four 2-level or eight 1-level pipeline registers.

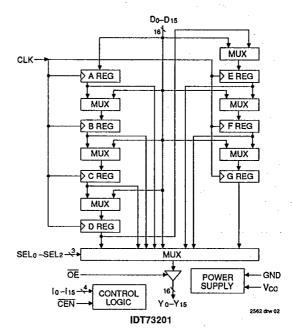

The IDT73201 contains seven 16-bit registers and a direct feed-through path. The seven registers can be configured as one 7-level, a 4-level plus a 3-level, three 2-level or seven 1-level pipeline registers.

An eight-to-one output multiplexer allows data to be read from any one of the registers or from the feed-through path on the IDT73201. Three input control pins (SELo-SEL2) select which of the multiplexer inputs are directed to the output (Y0-Y15).

These pipeline registers are ideal for high throughput, vector-oriented operations such as those in digital signal processing (DSP). The IDT73200 and IDT73201 can also be used as quick access scratch pad registers for general purpose computing.

The two pipeline registers are packaged in 48-pin plastic and ceramic DIPs for through-hole designs as well as 52-pin PLCC and LCC for surface mount designs. Military grade product is manufactured in compliance with the latest revision of MIL-STD-883, Class B.

#### **FUNCTIONAL BLOCK DIAGRAMS**

CEMOS is a trademark of Integrated Device Technology Inc.

MILITARY AND COMMERCIAL TEMPERATURE RANGES

**JUNE 1990**

# MILITARY AND COMMERCIAL TEMPERATURE RANGES

### **PIN CONFIGURATIONS**

T-46-09-27

## PIN DESCRIPTIONS

| Pin Name    | 1/0 | Description                                                                                                                                   |

|-------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Do - D:5    | - 1 | Sixteen-bit data input port.                                                                                                                  |

| Y0 - Y15    | 0   | Sixteen-bit data output port.                                                                                                                 |

| lo — la     | l   | Four control pins to select the register operation performed.                                                                                 |

| SEL0 - SEL2 | I   | Three control pins to select the register appearing at the output.                                                                            |

| CLK         | 1   | Clock input.                                                                                                                                  |

| CEN         | l   | Clock enable control pin. When this pin is low, the instruction lo-ls is performed on the registers. When high, no register operation occurs. |

| ŌĒ          | 1   | Output enable control pin. When this pin is high, the output port Y is in a high impedance state. When low, the output port Y is active.      |

| Vcc         |     | Power supply pin, 5V.                                                                                                                         |

| GND         |     | Ground pins, 0V.                                                                                                                              |

#### IDT73200 OUTPUT SELECTION

| 1 1                          |   | SEL2 |

|------------------------------|---|------|

| $A \rightarrow Y_0 - Y_{15}$ | 0 | 0    |

| B → Y0 - Y15                 | 0 | 0    |

| C → Y0 - Y15                 | 1 | 0    |

| D → Y0 - Y15                 | 1 | 0    |

| E → Y0 − Y15                 | 0 | 1    |

| F → Y0 - Y15                 | 0 | 1    |

| G → Y0 - Y15                 | 1 | 1    |

| H → Y0 - Y15                 | 1 | 1    |

| _                            | 1 | 1    |

# **IDT73201 OUTPUT SELECTION**

| SEL2 | SEL1 | SEL <sub>0</sub> | Y Output             |

|------|------|------------------|----------------------|

| 0    | 0    | 0                | A → Y0 - Y15         |

| 0    | 0    | 1                | B → Y0 - Y15         |

| 0    | 1    | 0                | C → Y0 - Y15         |

| 0    | 1    | 1                | D → Y0 - Y15         |

| 1    | 0    | 0                | E → Y0 - Y15         |

| 11   | 0    | 1                | F → Y0 - Y15         |

| 1    | 1    | 0                | G → Y0 - Y15         |

| 1    | 1    | 1                | Do - D15 -> Y0 - Y15 |

2562 tbl 03

2562 tbl 01

IDT73200, IDT73201 16-BIT CMOS MULTILEVEL PIPELINE REGISTERS

### MILITARY AND COMMERCIAL TEMPERATURE RANGES

# **IDT73200 INSTRUCTION TABLE**

# T-46-09-27

| l3  | l2 | l1 | lo | Mnemonic | Function                                                                                                                   | Pipeline Levels |

|-----|----|----|----|----------|----------------------------------------------------------------------------------------------------------------------------|-----------------|

| 0   | 0  | 0  | 0  | LDA      | Do - D15 → A                                                                                                               | 1               |

| 0   | 0  | 0  | 1  | LD8      | Do - D15 → B                                                                                                               | 1               |

| 0   | 0  | 1  | 0  | LDC      | Do - D15 → C                                                                                                               | 1               |

| 0   | 0  | 1  | 1  | LDD      | Do − D15 → D                                                                                                               | 1               |

| 0   | 11 | 0  | 0  | LDE      | Do - D15 → E                                                                                                               | 1               |

| 0   | 1  | 0  | 1  | LDF      | Do - D15 → F                                                                                                               | 1               |

| 0   | 1  | 1  | 0  | LDG      | Do - D15 → G                                                                                                               | 1               |

| 0   | 1  | 1  | 1  | LDH      | Do − D15 → H                                                                                                               | 1               |

| 1   | 0  | 0  | 0  | LSHAH    | $D0 - D15 \rightarrow A \rightarrow B \rightarrow C \rightarrow D \rightarrow E \rightarrow F \rightarrow G \rightarrow H$ | 8               |

| 1   | 0  | 0  | 1  | LSHAD    | $D0 - D15 \rightarrow A \rightarrow B \rightarrow C \rightarrow D$                                                         | 4               |

| _ 1 | 0  | 1  | 0  | LSHEH    | $D0 - D15 \rightarrow E \rightarrow F \rightarrow G \rightarrow H$                                                         | 4               |

| 1   | 0  | 1  | 1  | LSHAB    | $D_0 - D_{15} \rightarrow A \rightarrow B$                                                                                 | 2               |

| 1   | 1  | 0  | 0  | LSHCD    | $D_0 - D_{15} \rightarrow C \rightarrow D$                                                                                 | 2               |

| 1   | 1  | 0  | 1  | LSHEF    | Do - D15 → E → F                                                                                                           | 2               |

| _ 1 | 1  | 1  | 0  | LSHGH    | $D_0 - D_{15} \rightarrow G \rightarrow H$                                                                                 | 2               |

| 1   | 1  | 1  | 1  | HOLD     | Hold All Registers                                                                                                         |                 |

#### 2562 tbl 04

# **IDT73201 INSTRUCTION TABLE**

| 13 | l2 | l1 | lo | Mnemonic | Function                                                                                                     | Pipeline Levels |

|----|----|----|----|----------|--------------------------------------------------------------------------------------------------------------|-----------------|

| 0  | 0  | 0  | 0  | LDA      | Do - D15 → A                                                                                                 | 1               |

| 0  | 0  | 0  | 1  | LDB      | Do - D15 → B                                                                                                 | 1               |

| 0  | 0  | 1  | 0  | LDC      | Do − D15 → C                                                                                                 | 1 .             |

| 0  | 0  | 1_ | 1  | LDD      | Do - D15 → D                                                                                                 | 1               |

| 0  | 1  | 0  | 0  | LDE      | Do - D15 → E                                                                                                 | 1               |

| 0  | 1  | 0  | 1  | LDF      | Do - D15 → F                                                                                                 | 1               |

| 0  | 1  | 1  | 0  | LDG      | Do - D15 → G                                                                                                 | 1               |

| 0  | 1  | 1  | 1  | HOLD     | Hold All Registers                                                                                           |                 |

| 1  | 0  | 0  | 0  | LSHAG    | $D0 - D15 \rightarrow A \rightarrow B \rightarrow C \rightarrow D \rightarrow E \rightarrow F \rightarrow G$ | 7               |

| 1  | 0  | 0  | 1  | LSHAD    | $D0 - D15 \rightarrow A \rightarrow B \rightarrow C \rightarrow D$                                           | 4               |

| 1  | 0  | 1  | 0  | LSHEG    | $D0 - D15 \rightarrow E \rightarrow F \rightarrow G$                                                         | 3               |

| 1  | 0  | 1  | 1  | LSHAB    | $D_0 - D_{15} \rightarrow A \rightarrow B$                                                                   | 2               |

| 1  | 1  | 0  | 0  | LSHCD    | $D_0 - D_{15} \rightarrow C \rightarrow D$                                                                   | 2               |

| 1  | 1  | 0  | 1  | LSHEF    | Do − D15 → E → F                                                                                             | 2               |

| 1  | 1  | 11 | 0  | LDG      | Do - D15 → G                                                                                                 | 1               |

| 1  | 1  | 1  | 1  | HOLD     | Hold All Registers                                                                                           |                 |

T-46-09-27

MILITARY AND COMMERCIAL TEMPERATURE RANGES

IDT73200, IDT73201 16-BIT CMOS MULTILEVEL PIPELINE REGISTERS

# **IDT73200 PIPELINE CONFIGURATIONS**

# **IDT73201 PIPELINE CONFIGURATIONS**

# **ABSOLUTE MAXIMUM RATINGS**(1)

| Symbol | Rating                               | Commercial           | Military             | Unit |

|--------|--------------------------------------|----------------------|----------------------|------|

| Vcc    | Power Supply<br>Voltage              | -0.5 to +7.0         | -0.5 to +7.0         | ٧    |

| VTERM  | Terminal Voltage with Respect to GND | -0.5 to<br>Vcc + 0.5 | -0.5 to<br>Vcc + 0.5 | V    |

| Ta     | Operating<br>Temperature             | 0 to +70             | -55 to +125          | °C   |

| TBIAS  | Temperature<br>Under Bias            | -55 to +125          | -65 to +135          | °C   |

| Tstg   | Storage<br>Temperature               | -55 to +125          | -65 to +155          | °C   |

| lout   | DC Output<br>Current                 | 50                   | 50                   | mΑ   |

#### NOTE:

2562 tbi 06 Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability. CAPACITANCE (TA = +25°C, F = 1.0MHz)

|   | Symbol | Parameter <sup>(1)</sup> | Conditions | Тур. | Unit |

|---|--------|--------------------------|------------|------|------|

| 1 | CIN    | Input Capacitance        | VIN = OV   | 10   | pF   |

|   | Соит   | Output Capacitance       | Vout = 0V  | 12   | ρF   |

#### NOTE:

1. This parameter is sampled at initial characterization and is not 100%

# **TEST CIRCUIT**

| Switch |

|--------|

| Closed |

| Closed |

| Closed |

| Open   |

|        |

#### **DEFINITIONS:**

2562 tol 10

CL = Load capacitance includes jig and probe capacitance.

RT = Termination should be equal to ZouT of the pulse generator. (Typically 50Ω)

Vin = 0V to 3.0V

INPUT: tr = tr = 2.5ns (10% to 90%) unless otherwise specified

IDT73200, IDT73201 16-BIT CMOS MULTILEVEL PIPELINE REGISTERS

MILITARY AND COMMERCIAL TEMPERATURE RANGES

#### DC ELECTRICAL CHARACTERISTICS

Commercial: 0°C to +70°C, 5V  $\pm$  5%; Military: -55°C to +125°C, 5V  $\pm$  10%

T-46-09-27

| Symbol | Parameter                                      | Test Condition                          |            | Min. | Max  | Unit |

|--------|------------------------------------------------|-----------------------------------------|------------|------|------|------|

| ViH    | High-Level Input Voltage                       |                                         | 2.0        |      | V    |      |

| VIL    | Low-Level Input Voltage                        |                                         | _          |      | 0.8  | V    |

| liн    | High Level Input Current                       | Vcc = Max. VI = Vcc                     |            |      | 10   | μА   |

| lır.   | Low-Level Input Current                        | Vcc = Max. Vi = GND                     |            |      | -10  | μА   |

| Vон    | High-Level Output Voltage                      | Vcc = Min.,<br>Iон = -8mA(COM'L.), -    | -6mA(MIL.) | 2.4  | _    | v    |

| Vol    | Low-Level Output Voltage                       | Vcc = Min.,<br>lot = 16mA(COM'L.),      | 12mA(MIL.) | -    | 0.4  | V    |

| Vik    | Input Clamp Voltage                            | lı = -18mA                              |            |      | -1.2 | l ∨  |

| los    | Short Circuit Output<br>Current <sup>(2)</sup> | Vcc = Max., Vo = GNI<br>VI = Vcc or GND | D          | -20  | _    | mA   |

| lozн   | High Impedance Output<br>Current               | Vcc = Max.                              | VI = VCC   | -    | 20   | μА   |

| lozL   | Low Impedance Output<br>Current                | Vcc = Max.                              | VI = GND   |      | -20  | μА   |

1. For conditions shown as Min. or Max., use appropriate value based on temperature range.

2562 tol 08

2562 tol 09

2. Not more than one output should be shorted at one time. Duration of the short circuit test should not exceed 100 milliseconds.

#### POWER SUPPLY CHARACTERISTICS

| Symbol               | Parameter                                  | Test Conditions <sup>(1)</sup>                    | Min.   | Typ. <sup>(2)</sup> | Max. | Unit |    |

|----------------------|--------------------------------------------|---------------------------------------------------|--------|---------------------|------|------|----|

| lccoc                | Quiescent Power Supply Current             | Vcc = Max.<br>Vi = Vtc or Vhc                     |        | -                   | 2    | 10   | mA |

| ICCOT (3)            | Quiescent Power Supply Current Inputs HIGH | VCC = Max.<br>Vt = 3.4V                           |        | _                   | 15   | 45   | mA |

| ICCD1 <sup>(4)</sup> | Dynamic Power Supply Current               | Vcc = Max. Outputs Disabled, OE = HIGH            | COM'L. | . —                 | 10   | 30   | mA |

|                      |                                            | fCP = 10MHz, 50% Duty Cycle<br>VI ≤ VHC, VI ≥ VLC | MIL.   | _                   | . 10 | .40  |    |

| ICCD1 <sup>(4)</sup> | Dynamic Power Supply Current               | Vcc = Max. Outputs Disabled, OE = HIGH            | COM'L. | 1                   | 10   | 60   | mA |

|                      |                                            | fcP = 40MHz, 50% Duty Cycle<br>VI ≤ VHC, VI ≥ VLC | MIL.   | _                   | 10   | 80   |    |

#### NOTES:

- For conditions shown as Min. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type. Typical values are at Vcc = 5.0V, +25°C ambient and maximum loading, not production tested. This parameter is not directly testable but is derived for use in the total power supply calculation.

IC = IQUIESCENT + INPUTS + IDYNAMIC

Ic = Iccac + (Iccat x DH x Nt) + Icca Iccac = Quiescent Current

Iccot = Guescart Current Iccot = Power Supply Current for a TTL High Input (VIN = 3.4V) DH = Duty Cycle for each TTL Input High

NT = Number of TTL Inputs at DH

Icco = Dynamic Charge moved by an input transition pair (HLH or LHL)

All currents are in milliamps and all frequencies are in megahertz

MILITARY AND COMMERCIAL TEMPERATURE RANGES

#### **AC ELECTRICAL CHARACTERISTICS**

T-46-09-27

2562 tbl 11

Commercial: TA = 0°C to +70°C, Vcc = 5V  $\pm$ 5%; Military: TA = -55°C to +125°C, Vcc = 5V  $\pm$ 10%

|                                                |                      | Comm | ercial               |      | Military             |      |                      |      |      |  |

|------------------------------------------------|----------------------|------|----------------------|------|----------------------|------|----------------------|------|------|--|

|                                                | 73200L12<br>73201L12 |      | 73200L15<br>73201L15 |      | 73200L15<br>73201L15 |      | 73200L20<br>73201L20 |      | ]    |  |

| Parameter                                      | Min.                 | Max. | Min.                 | Max. | Min.                 | Max. | Min.                 | Max. | Unit |  |

| CLK to Yo-Y15 Propagation Delay                |                      | 12   | _                    | 15   |                      | 15   | -                    | 20   | ns   |  |

| SELo-SEL2 to Yo-Y15 Propagation Delay          | _                    | 12   | _                    | 15   | _                    | 15   |                      | 20   | ns   |  |

| Do-D15 to CLK Set-up Time                      | 3                    |      | 4                    | _    | 4                    |      | 5                    |      | ns   |  |

| Do-D15 to CLK Hold Time                        | 1                    |      | 2                    | _    | 2                    | _    | 3                    |      | ns   |  |

| lo-l3 to CLK Set-up Time                       | 4                    |      | 5                    |      | 5                    | _    | 6                    | _    | ns   |  |

| lo-l3 to CLK Hold Time                         | 2                    | _    | 2                    |      | 2                    | _    | 3                    | -    | ns   |  |

| CEN to CLK Set-up Time                         | 4                    | -    | 5                    | _    | 5                    |      | 6                    |      | ns   |  |

| CEN to CLK Hold Time                           | 2                    |      | 2                    |      | 2                    | _    | 3                    | _    | nš   |  |

| OE Enable Time <sup>(1)</sup>                  | _                    | 9    | _                    | 10   |                      | 10   | _                    | 13   | ns   |  |

| OE Disable Time <sup>(1)</sup>                 | _                    | 8    |                      | 9    | _                    | 9    | _                    | 13   | ns   |  |

| CLK Pulse Width HIGH                           | 5                    | _    | 5                    | _    | 5                    | _    | 6                    | _    | ns   |  |

| CLK Pulse Width LOW                            | 5                    | -    | 5                    | _    | 5                    | -    | 6                    | -    | ns   |  |

| CLK Period                                     | _                    | 12   | _                    | 15   |                      | 15   |                      | 20   | ns   |  |

| Data In to Data Out Flowthrough <sup>(2)</sup> |                      | 12   | _                    | 15   | _                    | -15  | _                    | 20   | ns   |  |

NOTES:

- 1. Output Enable and Disable times measured to 500mV change of output voltage level.

- 2. 73201 only.

#### **AC TEST CONDITIONS**

| Input Pulse Levels            | GND to 4.0V  |

|-------------------------------|--------------|

| Input Rise/Fall Times         | 4ns          |

| Input Timing Reference Levels | 1.5V         |

| Output Reference Levels       | 1.5V         |

| Output Load                   | See Figure 1 |

VCC \$500Ω

PULSE GENERATOR

OLU.T. OL

R1

500Ω

R1

500Ω

R1

2562 drw 05

Figure 1. AC Output Test Circuit

## **CMOS TESTING CONSIDERATIONS**

There are certain testing considerations which must be taken into account when testing high-speed CMOS devices in an automatic environment. These are:

- Proper decoupling at the test head is necessary. Placement of the capacitor set and the value of capacitors used is critical in reducing the potential erroneous failures resulting from large Vcc current changes. Capacitor lead length must be short and as close to the DUT power pins as possible.

- All input pins should be connected to a voltage potential during testing. If left floating, the device may begin to oscilliate causing improper device operation and possible latchup.

- 3) Definition of input levels is very important. Since many inputs may change coincidentally, significant noise at the device pins may cause the V<sub>IL</sub> and V<sub>IH</sub> levels not to be met until the noise has settled. To allow for this testing/board induced noise, IDT recommends using V<sub>IL</sub> ≤ 0V and V<sub>IH</sub> ≥ 3V for AC tests.

- 4) Device grounding is extremely important for proper device testing. The use of multi-layer performance boards with radial decoupling between power and ground planes is required. The ground plane must be sustained from the performance board to the DUT interface board. All unused interconnect pins must be properly connected to the ground pin. Heavy gauge stranded wire should be used for power wiring and twisted pairs are recommended to minimize inductance.

IDT73200, IDT73201 16-BIT CMOS MULTILEVEL PIPELINE REGISTERS

MILITARY AND COMMERCIAL TEMPERATURE RANGES

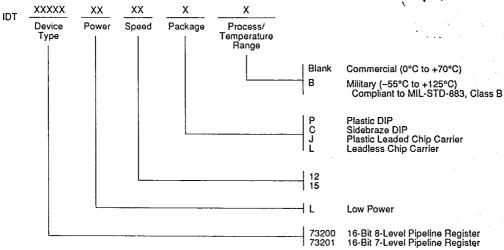

### ORDERING INFORMATION

T-46-09-27

2562 drw 06

5