10-channel integrated LC-filter network with ESD input protection to IEC 61000-4-2 level 4

Rev. 02 — 10 March 2009

**Product data sheet**

# 1. Product profile

## 1.1 General description

The IP3338CX24 is a 10-channel<sup>1</sup> LC low-pass filter network designed to filter undesired RF signals in the 800 MHz to 3000 MHz frequency band. In addition, the IP3338CX24 incorporates diodes which protect downstream components from ElectroStatic Discharge (ESD) voltages as high as 15 kV.

The IP3338CX24 is fabricated using monolithic silicon technology and integrates 10 inductors and 20 back-to-back diodes in a single Wafer-Level Chip-Scale Package (WLCSP) measuring 2.11 mm by 2.11 mm (typical). These features make the IP3338CX24 ideal for use in applications requiring the utmost in miniaturization such as mobile phone handsets, cordless telephones and personal digital devices.

## 1.2 Features

- Pb-free, RoHS compliant and halogen free package; Dark Green compliant

- Integrated 10-channel  $\pi$ -type LC filter network with 60 nH channel inductance

- **125**  $\Omega$  series resistance; 25 pF (typical) capacitance per line

- Integrated ESD protection withstanding ±15 kV contact discharge, far exceeding IEC 61000-4-2, level 4

- WLCSP with 0.4 mm pitch

## **1.3 Applications**

- Cellular and Personal Communication System (PCS) mobile handsets

- Cordless telephones

- Wireless data (WAN/LAN) systems

- PDAs

<sup>1.</sup> Also available as a 7-channel device (IP3337CX18).

10-channel integrated LC-filter network with ESD input protection

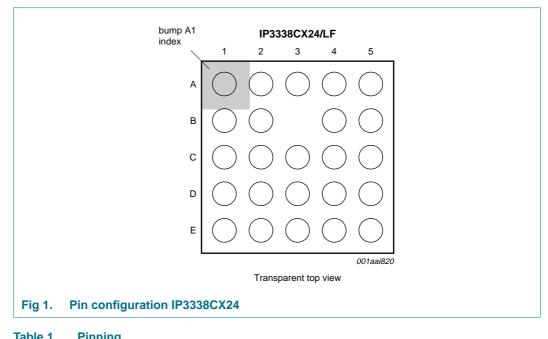

# 2. Pinning information

# 2.1 Pinning

| Table 1. Pinning |                   |

|------------------|-------------------|

| Pin              | Description       |

| A2 and A5        | filter channel 1  |

| A1 and A4        | filter channel 2  |

| B2 and B5        | filter channel 3  |

| B1 and B4        | filter channel 4  |

| C2 and C5        | filter channel 5  |

| C1 and C4        | filter channel 6  |

| D2 and D5        | filter channel 7  |

| D1 and D4        | filter channel 8  |

| E2 and E5        | filter channel 9  |

| E1 and E4        | filter channel 10 |

| A3, C3, D3, E3   | ground            |

| B3               | no ball           |

|                  |                   |

# 3. Ordering information

#### Table 2. Ordering information

| Type number   | Package |                                                                              |               |

|---------------|---------|------------------------------------------------------------------------------|---------------|

|               | Name    | Description                                                                  | Version       |

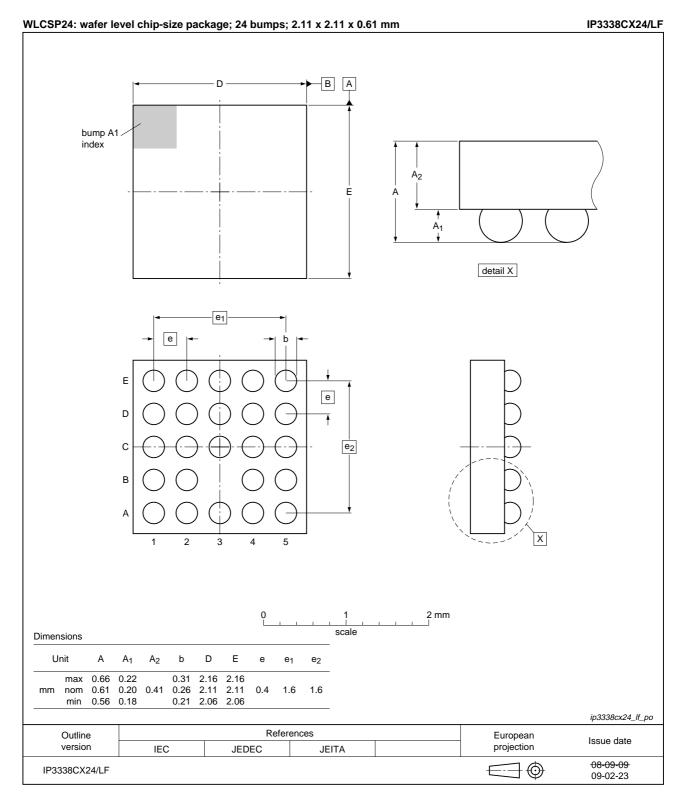

| IP3338CX24/LF | WLCSP24 | wafer level chip-size package; 24 bumps; 2.11 $\times$ 2.11 $\times$ 0.61 mm | IP3338CX24/LF |

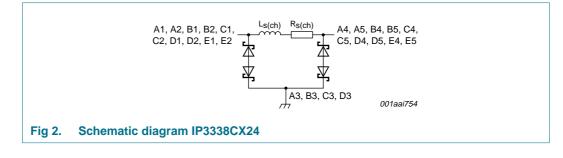

# 4. Functional diagram

# 5. Limiting values

## Table 3.Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                    | Parameter                       | Conditions                                    | Min             | Мах  | Unit |

|---------------------------|---------------------------------|-----------------------------------------------|-----------------|------|------|

| VI                        | input voltage                   |                                               | -4.0            | +4.0 | V    |

| V <sub>ESD</sub>          | electrostatic discharge voltage | all pins to ground                            |                 |      |      |

|                           |                                 | contact discharge                             | [ <u>1]</u> –15 | +15  | kV   |

|                           |                                 | air discharge                                 | [ <u>1]</u> –15 | +15  | kV   |

|                           |                                 | IEC 61000-4-2, level 4; all pins to ground    |                 |      |      |

|                           |                                 | contact discharge                             | -8              | +8   | kV   |

|                           |                                 | air discharge                                 | -15             | +15  | kV   |

| I <sub>ch</sub>           | channel current (DC)            | T <sub>amb</sub> = 70 °C                      | -               | 10   | mA   |

| I <sub>ch(M)</sub>        | peak channel current            | T <sub>amb</sub> = 70 °C; 60 s                | -               | 50   | mA   |

| P <sub>ch</sub>           | channel power dissipation       | continuous power;<br>T <sub>amb</sub> = 70 °C | -               | 10   | mW   |

| P <sub>tot</sub>          | total power dissipation         | T <sub>amb</sub> = 70 °C                      | -               | 100  | mW   |

| T <sub>stg</sub>          | storage temperature             |                                               | -55             | +150 | °C   |

| T <sub>reflow(peak)</sub> | peak reflow temperature         | 10 s maximum                                  | -               | 260  | °C   |

| T <sub>amb</sub>          | ambient temperature             |                                               | -35             | +85  | °C   |

|                           |                                 |                                               |                 |      |      |

[1] Device tested with 1000 pulses of  $\pm$ 15 kV contact discharges, according to the IEC 61000-4-2 model, which far exceeds IEC 61000-4-2, level 4 (8 kV contact discharge).

#### 10-channel integrated LC-filter network with ESD input protection

# 6. Characteristics

| <b>Table 4.</b> $T_{amb} = 25$ | <b>Channel characteristics</b><br>• <i>C</i> ; unless otherwise specifie | d.                              |     |     |     |                     |      |

|--------------------------------|--------------------------------------------------------------------------|---------------------------------|-----|-----|-----|---------------------|------|

| Symbol                         | Parameter                                                                | Conditions                      |     | Min | Тур | Max                 | Unit |

| $R_{s(ch)}$                    | channel series resistance                                                | f = 0 Hz (DC)                   |     | 100 | 125 | 150                 | Ω    |

| C <sub>ch</sub>                | channel capacitance                                                      | $V_{bias(DC)} = 0 V; f = 1 MHz$ |     | -   | 25  | 30 <mark>[1]</mark> | pF   |

| L <sub>s(ch)</sub>             | channel series inductance                                                |                                 | [1] | -   | 60  | -                   | nH   |

| $V_{BR}$                       | breakdown voltage                                                        | I <sub>test</sub> = 1 mA        |     | 6   | -   | 10                  | V    |

|                                |                                                                          | $I_{test} = -1 \text{ mA}$      |     | -10 | -   | -6                  | V    |

| I <sub>LR</sub>                | reverse leakage current                                                  | per channel; $V_I = 3.0 V$      |     | -   | -   | 100                 | nA   |

|                                |                                                                          |                                 |     |     |     |                     |      |

[1] Guaranteed by design.

### Table 5. Frequency characteristics

| Symbol            | Parameter             | Conditions                                                                                 | Min | Тур | Max | Unit |

|-------------------|-----------------------|--------------------------------------------------------------------------------------------|-----|-----|-----|------|

| $\alpha_{il}$     | uil insertion loss    | $R_{gen}$ = 50 $\Omega$ ; $R_L$ = 50 $\Omega$                                              |     |     |     |      |

|                   |                       | 800 MHz < f < 1 GHz                                                                        | 38  | 40  | -   | dB   |

|                   |                       | 1 GHz < f < 3 GHz                                                                          | 35  | 40  | -   | dB   |

|                   |                       | at 0 Hz; $R_{gen}$ = 50 $\Omega$ ;<br>$R_L$ = 50 $\Omega$ ; $V_{bias(DC)}$ = 0 V           | 6   | 7   | 10  | dB   |

| f <sub>-3dB</sub> | cut-off frequency     | measured relative to<br>insertion loss at DC;<br>$R_{gen} = 50 \Omega$ ; $R_L = 50 \Omega$ | 150 | 180 | -   | MHz  |

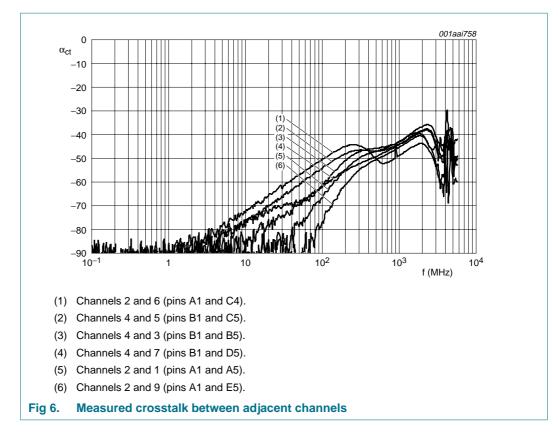

| $\alpha_{ct}$     | crosstalk attenuation | 800 MHz < f < 3 GHz;<br>R <sub>gen</sub> = 50 Ω; R <sub>L</sub> = 50 Ω                     | 35  | 40  | -   | dB   |

# 7. Application information

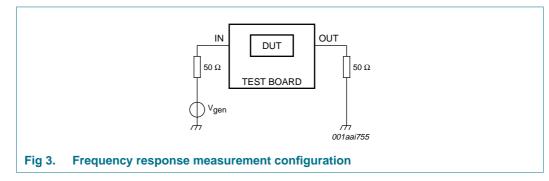

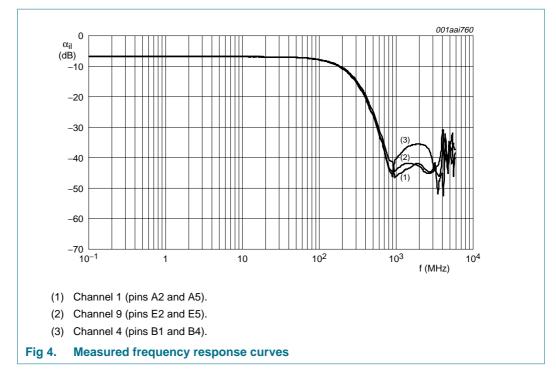

## 7.1 Insertion loss

The setup for measuring insertion loss in a 50  $\Omega$  system is shown in Figure 3.

The measured frequency response curves for all channels are shown in Figure 4.

### 10-channel integrated LC-filter network with ESD input protection

## 7.2 Crosstalk

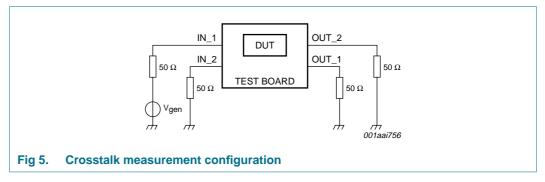

The setup for measuring crosstalk in a 50  $\Omega$  system is shown in Figure 5.

The crosstalk between adjacent channels within the IP3338CX24 for different channel pairs measured in a 50  $\Omega$  NetWork Analyzer (NWA) system, is shown in Figure 6. In all cases, all unused connections are terminated with 50  $\Omega$  to ground.

### 10-channel integrated LC-filter network with ESD input protection

10-channel integrated LC-filter network with ESD input protection

# 8. Package outline

## Fig 7. Package outline IP3338CX24/LF (WLCSP24)

Product data sheet

# 9. Soldering of WLCSP packages

## 9.1 Introduction to soldering WLCSP packages

This text provides a very brief insight into a complex technology. A more in-depth account of soldering WLCSP (Wafer Level Chip-Size Packages) can be found in application note *AN10439 "Wafer Level Chip Scale Package"* and in application note *AN10365 "Surface mount reflow soldering description"*.

Wave soldering is not suitable for this package.

All NXP WLCSP packages are lead-free.

## 9.2 Board mounting

Board mounting of a WLCSP requires several steps:

- 1. Solder paste printing on the PCB

- 2. Component placement with a pick and place machine

- 3. The reflow soldering itself

## 9.3 Reflow soldering

Key characteristics in reflow soldering are:

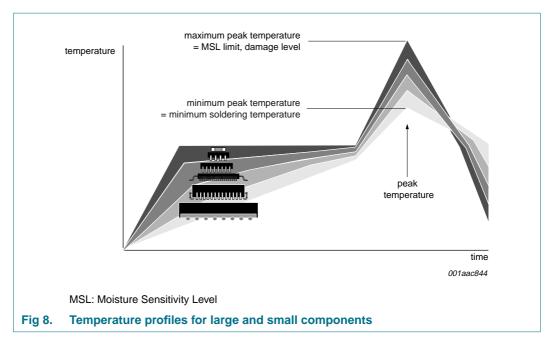

- Lead-free versus SnPb soldering; note that a lead-free reflow process usually leads to higher minimum peak temperatures (see <u>Figure 8</u>) than a PbSn process, thus reducing the process window

- Solder paste printing issues, such as smearing, release, and adjusting the process window for a mix of large and small components on one board

- Reflow temperature profile; this profile includes preheat, reflow (in which the board is heated to the peak temperature), and cooling down. It is imperative that the peak temperature is high enough for the solder to make reliable solder joints (a solder paste characteristic) while being low enough that the packages and/or boards are not damaged. The peak temperature of the package depends on package thickness and volume and is classified in accordance with Table 6.

| Package thickness (mm) | Package reflow temperature (°C)<br>Volume (mm <sup>3</sup> ) |     |     |     |  |

|------------------------|--------------------------------------------------------------|-----|-----|-----|--|

|                        |                                                              |     |     |     |  |

|                        | < 1.6                                                        | 260 | 260 | 260 |  |

| 1.6 to 2.5             | 260                                                          | 250 | 245 |     |  |

| > 2.5                  | 250                                                          | 245 | 245 |     |  |

#### Table 6. Lead-free process (from J-STD-020C)

Moisture sensitivity precautions, as indicated on the packing, must be respected at all times.

Studies have shown that small packages reach higher temperatures during reflow soldering, see Figure 8.

For further information on temperature profiles, refer to application note AN10365 "Surface mount reflow soldering description".

### 9.3.1 Stand off

The stand off between the substrate and the chip is determined by:

- The amount of printed solder on the substrate

- The size of the solder land on the substrate

- The bump height on the chip

The higher the stand off, the better the stresses are released due to TEC (Thermal Expansion Coefficient) differences between substrate and chip.

#### 9.3.2 Quality of solder joint

A flip-chip joint is considered to be a good joint when the entire solder land has been wetted by the solder from the bump. The surface of the joint should be smooth and the shape symmetrical. The soldered joints on a chip should be uniform. Voids in the bumps after reflow can occur during the reflow process in bumps with high ratio of bump diameter to bump height, i.e. low bumps with large diameter. No failures have been found to be related to these voids. Solder joint inspection after reflow can be done with X-ray to monitor defects such as bridging, open circuits and voids.

## 9.3.3 Rework

In general, rework is not recommended. By rework we mean the process of removing the chip from the substrate and replacing it with a new chip. If a chip is removed from the substrate, most solder balls of the chip will be damaged. In that case it is recommended not to re-use the chip again.

Device removal can be done when the substrate is heated until it is certain that all solder joints are molten. The chip can then be carefully removed from the substrate without damaging the tracks and solder lands on the substrate. Removing the device must be done using plastic tweezers, because metal tweezers can damage the silicon. The surface of the substrate should be carefully cleaned and all solder and flux residues and/or underfill removed. When a new chip is placed on the substrate, use the flux process instead of solder on the solder lands. Apply flux on the bumps at the chip side as well as on the solder pads on the substrate. Place and align the new chip while viewing with a microscope. To reflow the solder, use the solder profile shown in application note *AN10365 "Surface mount reflow soldering description"*.

### 9.3.4 Cleaning

Cleaning can be done after reflow soldering.

# **10. Abbreviations**

| Table 7. | Abbreviations                       |

|----------|-------------------------------------|

| Acronym  | Description                         |

| DUT      | Device Under Test                   |

| EMI      | ElectroMagnetic Interference        |

| ESD      | ElectroStatic Discharge             |

| FR4      | Flame Retard 4                      |

| LAN      | Local Area Network                  |

| NSMD     | Non-Solder Mask Design              |

| OSP      | Organic Solderability Preservative  |

| PCB      | Printed-Circuit Board               |

| PCS      | Personal Communication System       |

| PDA      | Personal Digital Assistant          |

| PSU      | Power Supply Unit                   |

| RoHS     | Restriction of Hazardous Substances |

| WAN      | Wide Area Network                   |

| WLCSP    | Wafer-Level Chip-Scale Package      |

# 11. Revision history

#### Table 8.Revision history

| Release date                                                                        | Data sheet status                                                                                    | Change notice                                                                                                                                                                                                                                                        | Supersedes                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20090310                                                                            | Product data sheet                                                                                   | -                                                                                                                                                                                                                                                                    | IP3338CX24_1                                                                                                                                                                                                                                                                                                                     |

| <ul> <li>Removed 'Ma</li> <li><u>Figure 7</u>: repl</li> <li>Removed 'Pa</li> </ul> | arking' section<br>aced bump A1 index marker w<br>cking information' section                         | vith grey square                                                                                                                                                                                                                                                     | rd text inset                                                                                                                                                                                                                                                                                                                    |

| 20081113                                                                            | Product data sheet                                                                                   | -                                                                                                                                                                                                                                                                    | -                                                                                                                                                                                                                                                                                                                                |

|                                                                                     | 20090310<br>• Figure 1: repl<br>• Removed 'Ma<br>• Figure 7: repl<br>• Removed 'Pa<br>• Replaced 'De | 20090310       Product data sheet         Figure 1: replaced bump A1 index marker w         Removed 'Marking' section         Figure 7: replaced bump A1 index marker w         Removed 'Packing information' section         Replaced 'Design and assembly recommer | 20090310       Product data sheet       -         Figure 1: replaced bump A1 index marker with grey square         Removed 'Marking' section         Figure 7: replaced bump A1 index marker with grey square         Removed 'Packing information' section         Replaced 'Design and assembly recommendations' with standard |

# **12. Legal information**

## 12.1 Data sheet status

| Document status[1][2]          | Product status <sup>[3]</sup> | Definition                                                                            |

|--------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development                   | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification                 | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production                    | This document contains the product specification.                                     |

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term 'short data sheet' is explained in section "Definitions".

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

## 12.2 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

## 12.3 Disclaimers

**General** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.

Terms and conditions of sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

## 12.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

# 13. Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

## **NXP Semiconductors**

# IP3338CX24

10-channel integrated LC-filter network with ESD input protection

## 14. Contents

| 1     | Product profile 1                          |

|-------|--------------------------------------------|

| 1.1   | General description                        |

| 1.2   | Features                                   |

| 1.3   | Applications 1                             |

| 2     | Pinning information 2                      |

| 2.1   | Pinning 2                                  |

| 3     | Ordering information 2                     |

| 4     | Functional diagram 3                       |

| 5     | Limiting values 3                          |

| 6     | Characteristics 4                          |

| 7     | Application information                    |

| 7.1   | Insertion loss 4                           |

| 7.2   | Crosstalk 5                                |

| 8     | Package outline                            |

| 9     | Soldering of WLCSP packages                |

| 9.1   | Introduction to soldering WLCSP packages 8 |

| 9.2   | Board mounting 8                           |

| 9.3   | Reflow soldering 8                         |

| 9.3.1 | Stand off                                  |

| 9.3.2 | Quality of solder joint 9                  |

| 9.3.3 | Rework                                     |

| 9.3.4 | Cleaning                                   |

| 10    | Abbreviations 10                           |

| 11    | Revision history 10                        |

| 12    | Legal information 11                       |

| 12.1  | Data sheet status 11                       |

| 12.2  | Definitions 11                             |

| 12.3  | Disclaimers                                |

| 12.4  | Trademarks 11                              |

| 13    | Contact information 11                     |

| 14    | Contents 12                                |

|       |                                            |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

#### © NXP B.V. 2009.

All rights reserved.

founded by

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 10 March 2009 Document identifier: IP3338CX24\_2