### **PRELIMINARY**

### **MOSEL VITELIC**

# V58C265804S HIGH PERFORMANCE 2.5 VOLT 8M X 8 DDR SDRAM 4 BANKS X 2Mbit X 8

|                                        | 6       | 7       | 8       |

|----------------------------------------|---------|---------|---------|

| System Frequency (f <sub>CK</sub> )    | 166 MHz | 143 MHz | 125 MHz |

| Clock Cycle Time (t <sub>CK3</sub> )   | 6 ns    | 7 ns    | 8 ns    |

| Clock Cycle Time (t <sub>CK2.5</sub> ) | 6.5 ns  | 7.5 ns  | 9 ns    |

| Clock Cycle Time (t <sub>CK2</sub> )   | 7ns     | 8ns     | 10ns    |

#### **Features**

- 4 banks x 2Mbit x 8 organization

- High speed data transfer rates with system frequency up to 166 MHz

- Data Mask for Write Control (DM)

- Four Banks controlled by BA0 & BA1

- Programmable CAS Latency: 2, 2.5, 3

- Programmable Wrap Sequence: Sequential or Interleave

- Programmable Burst Length: 2, 4, 8 for Sequential Type 2, 4, 8 for Interleave Type

- Automatic and Controlled Precharge Command

- Suspend Mode and Power Down Mode

- Auto Refresh and Self Refresh

- Refresh Interval: 4096 cycles/64 ms

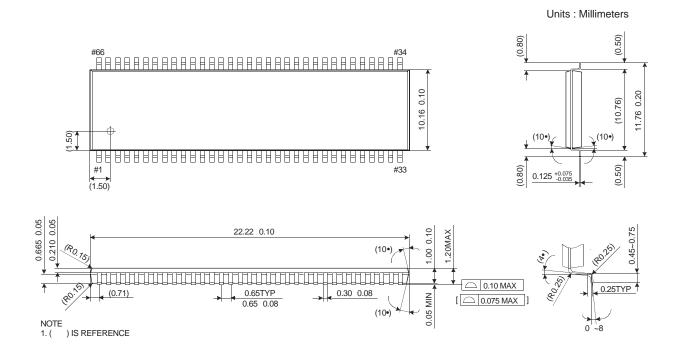

- Available in 66-pin 400 mil TSOP-II

- SSTL-2 Compatible I/Os

- Double Data Rate (DDR)

- Bidirectional Data Strobe (DQs) for input and output data, active on both edges

- On-Chip DLL aligns DQ and DQs transitions with CLK transitions

- Differential clock inputs CLK and CLK

- Power Supply 2.5V ± 0.2V

### Description

The  $\dot{V}58C265804S$  is a four bank DDR DRAM organized as 4 banks x 2Mbit x 8. The  $\dot{V}58C265804S$  achieves high speed data transfer rates by employing a chip architecture that prefetches multiple bits and then synchronizes the output data to a system clock

All of the control, address, circuits are synchronized with the positive edge of an externally supplied clock. I/O transactions are possible on both edges of DQS.

Operating the four memory banks in an interleaved fashion allows random access operation to occur at a higher rate than is possible with standard DRAMs. A sequential and gapless data rate is possible depending on burst length,  $\overline{\text{CAS}}$  latency and speed grade of the device.

### **Device Usage Chart**

| Operating            | Package Outline  | CLK Cycle Time (ns) |    |    | Pov  | wer | Tomporaturo         |  |

|----------------------|------------------|---------------------|----|----|------|-----|---------------------|--|

| Temperature<br>Range | JEDEC 66 TSOP II | -6                  | -7 | -8 | Std. | L   | Temperature<br>Mark |  |

| 0°C to 70 °C         | •                | •                   | •  | •  | •    | •   | Blank               |  |

1

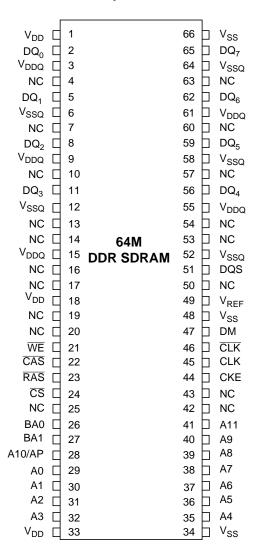

# 66 Pin Plastic TSOP-II PIN CONFIGURATION Top View

#### Pin Names

| CLK, CLK                         | Differential Clock Input     |

|----------------------------------|------------------------------|

| CKE                              | Clock Enable                 |

| CS                               | Chip Select                  |

| RAS                              | Row Address Strobe           |

| CAS                              | Column Address Strobe        |

| WE                               | Write Enable                 |

| DQS                              | Data Strobe (Bidirectional)  |

| A <sub>0</sub> -A <sub>11</sub>  | Address Inputs               |

| BA0, BA1                         | Bank Select                  |

| DQ <sub>0</sub> –DQ <sub>7</sub> | Data Input/Output            |

| DM                               | Data Mask                    |

| V <sub>DD</sub>                  | Power (+2.5V)                |

| V <sub>SS</sub>                  | Ground                       |

| $V_{DDQ}$                        | Power for I/O's (+2.5V)      |

| V <sub>SSQ</sub>                 | Ground for I/O's             |

| NC                               | Not connected                |

| VREF                             | Reference Voltage for Inputs |

# Capacitance\*

$T_A = 0$  to  $70^{\circ}C$ ,  $V_{CC} = 2.5V \pm 0.2V$ , f = 1 Mhz

| Symbol           | Parameter                                  | Max. | Unit |

|------------------|--------------------------------------------|------|------|

| C <sub>I1</sub>  | Input Capacitance (A0 to A11)              | 5    | pF   |

| C <sub>I2</sub>  | Input Capacitance<br>RAS, CAS, WE, CS, CKE | 5    | pF   |

| C <sub>IO</sub>  | Output Capacitance (DQ)                    | 6.5  | pF   |

| C <sub>CLK</sub> | Input Capacitance (CCLK, CLK)              | 4    | pF   |

<sup>\*</sup>Note: Capacitance is sampled and not 100% tested.

### Absolute Maximum Ratings\*

| 0 to 70 °C                 |

|----------------------------|

| 55 to 150 °C               |

| -0.3 to ( $V_{CC}$ +0.3) V |

| 0.3 to 4.6 V               |

| 1.6 W                      |

| 50 mA                      |

|                            |

<sup>\*</sup>Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage of the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

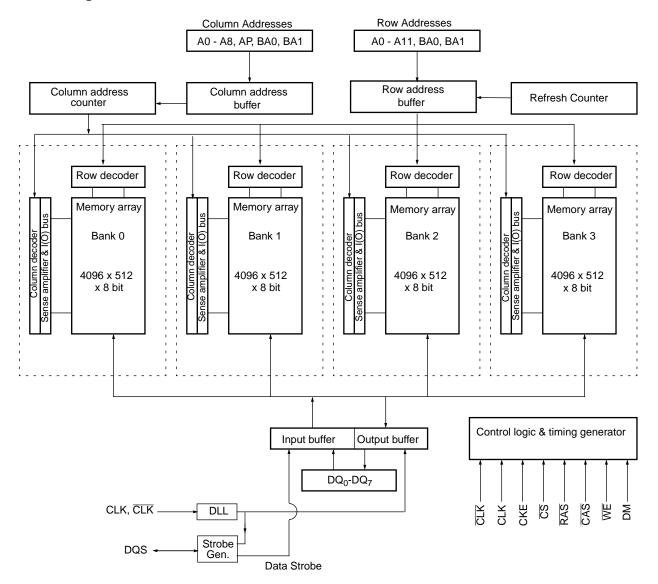

### **Block Diagram**

# Signal Pin Description

| Pin            | Туре             | Signal | Polarity         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|------------------|--------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK<br>CLK     | Input            | Pulse  | Positive<br>Edge | The system clock input. All inputs except DQs and DMs are sampled on the rising edge of CLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CKE            | Input            | Level  | Active High      | Activates the CLK signal when high and deactivates the CLK signal when low, thereby initiates either the Power Down mode, Suspend mode, or the Self Refresh mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CS             | Input            | Pulse  | Active Low       | $\overline{\text{CS}}$ enables the command decoder when low and disables the command decoder when high. When the command decoder is disabled, new commands are ignored but previous operations continue.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RAS, CAS<br>WE | Input            | Pulse  | Active Low       | When sampled at the positive rising edge of the clock, $\overline{\text{CAS}}$ , $\overline{\text{RAS}}$ , and $\overline{\text{WE}}$ define the command to be executed by the SDRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DQS            | Input/<br>Output | Pulse  | Active High      | Active on both edges for data input and output. Center aligned to input data Edge aligned to output data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A0 - A11       | Input            | Level  |                  | During a Bank Activate command cycle, A0-A11 defines the row address (RA0-RA11) when sampled at the rising clock edge.  During a Read or Write command cycle, A0-An defines the column address (CA0-CAn) when sampled at the rising clock edge.CAn depends from the SDRAM organization:  8M x 8 SDRAM CAn = CA8 (Page Length = 512 bits)  In addition to the column address, A10(=AP) is used to invoke autoprecharge operation at the end of the burst read or write cycle. If A10 is high, autoprecharge is selected and BA0, BA1 defines the bank to be precharged. If A10 is low, autoprecharge is disabled. During a Precharge command cycle, A10(=AP) is used in conjunction with BA0 and BA1 to control which bank(s) to precharge. If A10 is high, all four banks will be precharged simultaneously regardless of state of BA0 and BA1. |

| BA0,<br>BA1    | Input            | Level  | _                | Selects which bank is to be active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DQx            | Input/<br>Output | Level  | _                | Data Input/Output pins operate in the same manner as on conventional DRAMs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DM             | Input            | Pulse  | Active High      | In Write mode, DM has a latency of zero and operates as a word mask by allowing input data to be written if it is low but blocks the write operation if is high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| VDD, VSS       | Supply           |        |                  | Power and ground for the input buffers and the core logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| VDDQ<br>VSSQ   | Supply           | _      | _                | Isolated power supply and ground for the output buffers to provide improved noise immunity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VREF           | Input            | Level  |                  | SSTL Reference Voltage for Inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

#### Functional Description

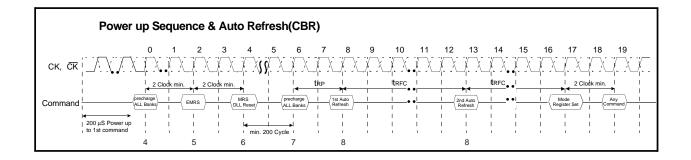

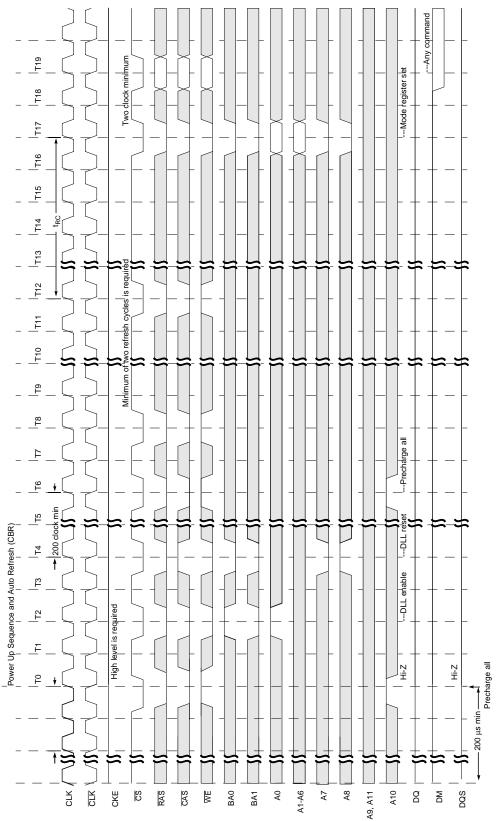

### ■ Power-Up Sequence

The following sequence is required for POWER UP.

- 1. Apply power and attempt to maintain CKE at a low stately other inputs may be undefined.)

- Apply VDD before or at the same time as VDDQ.

- Apply VDDQ before or at the same time as VTT & Vref.

- 2. Start clock and maintain stable condition for a minimum of 200us.

- 3. The minimum of 200us after stable power and clock (CLK, CLK), apply NOP & take CKE high.

- 4. Precharge all banks.

- 5. Issue EMRS to enable DLL.(To issue "DLL Enable" command, provide "Low" to A0, "High" to BA0 and "Low" to all of the rest address pins, A1~A11 and BA1)

- 6. Issue a mode register set command for "DLL reset". The additional 200 cycles of clock input is required to lock the DLL. (To issue DLL reset command, provide "High" to A8 and "Low" to BA0)

- 7. Issue precharge commands for all banks of the device.

- 8. Issue 2 or more auto-refresh commands.

- 9. Issue a mode register set command to initialize device operation.

Note1 Every "DLL enable" command resets DLL. Therefore sequence 6 can be skipped during power up. Instead of it, the additional 200 cycles of clock input is required to lock the DLL after enabling DLL.

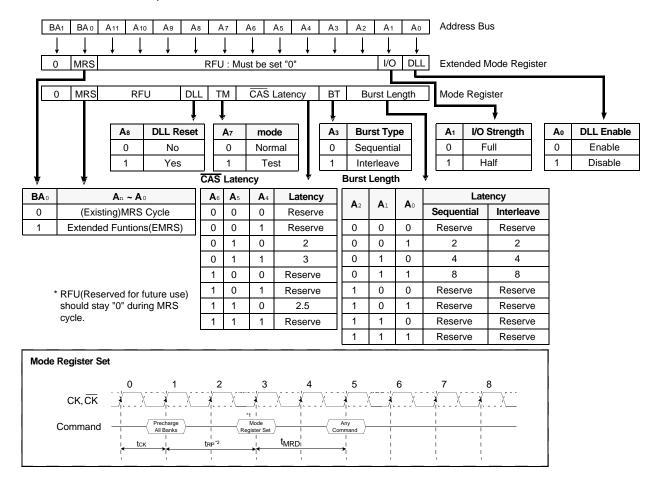

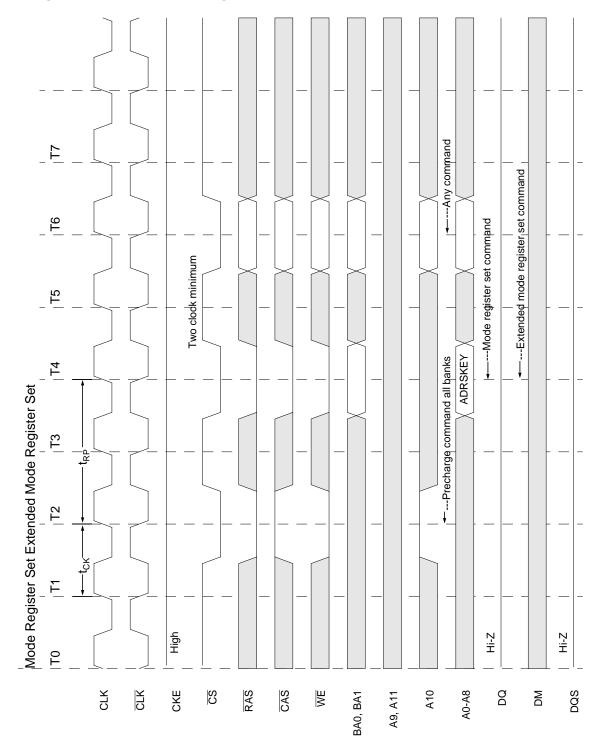

#### Extended Mode Register Set (EMRS)

The extended mode register stores the data for enabling or disabling DLL. The default value of the extended mode register is not defined, therefore the extended mode register must be written after power up for enabling or disabling DLL. The extended mode register is written by asserting low on  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$ ,  $\overline{WE}$  and high on BA $_0$  (The DDR SDRAM should be in all bank precharge with CKE already high prior to writing into the extended mode register). The state of address pins A $_0$  ~ A $_{11}$  and BA $_1$  in the same cycle as  $\overline{CS}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$  and  $\overline{WE}$  low is written in the extended mode register. Two clock cycles are required to complete the write operation in the extended mode register. The mode register contents can be changed using the same command and clock cycle requirements during operation as long as all banks are in the idle state. A $_0$  is used for DLL enable or disable. "High" on BA $_0$  is used for EMRS. All the other address pins except A $_0$  and BA $_0$  must be set to low for proper EMRS operation. A $_1$  is used at EMRS to indicate I/O strength A $_1$  = 0 full strength, A $_1$  = 1 half strength. Refer to the table for specific codes.

#### Mode Register Set (MRS)

The mode register stores the data for controlling the various operating modes of DDR SDRAM. It programs  $\overline{\text{CAS}}$  latency, addressing mode, burst length, test mode, DLL reset and various vendor specific options to make DDR SDRAM useful for a variety of different applications. The default value of the mode register is not defined, therefore the mode register must be written after EMRS setting for proper DDR SDRAM operation. The mode register is written by asserting low on  $\overline{\text{CS}}$ ,  $\overline{\text{RAS}}$ ,  $\overline{\text{CAS}}$ ,  $\overline{\text{WE}}$  and BA $_0$  (The DDR SDRAM should be in all bank precharge with CKE already high prior to writing into the mode register). The state of address pins A $_0 \sim A_{11}$  in the same cycle as  $\overline{\text{CS}}$ ,  $\overline{\text{RAS}}$ ,  $\overline{\text{CAS}}$ ,  $\overline{\text{WE}}$  and BA $_0$  low is written in the mode register. Two clock cycles are required to meet  $t_{\text{MRD}}$  spec. The mode register contents can be changed using the same command and clock cycle requirements during operation as long as all banks are in the idle state. The mode register is divided into various fields depending on functionality. The burst length uses A $_0 \sim A_2$ , addressing mode uses A $_3$ ,  $\overline{\text{CAS}}$  latency (read latency from column address) uses A $_4 \sim A_6$ . A $_7$  is a Mosel Vitelic specific test mode during production test. A $_8$  is used for DLL reset. A $_7$  must be set to low for normal MRS operation. Refer to the table for specific codes for various burst length, addressing modes and  $\overline{\text{CAS}}$  latencies.

- 1. MRS can be issued only at all banks precharge state.

- 2. Minimum tRP is required to issue MRS command.

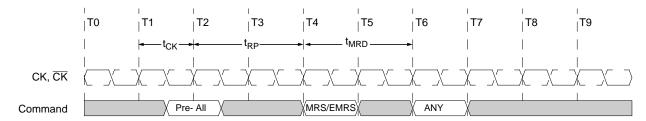

# Mode Register Set Timing

Mode Register set (MRS) or Extended Mode Register Set (EMRS) can be issued only when all banks are in the idle state.

If a MRS command is issued to reset the DLL, then an additional 200 clocks must occur prior to issuing any new command to allow time for the DLL to lock onto the clock.

### **Burst Mode Operation**

Burst Mode Operation is used to provide a constant flow of data to memory locations (Write cycle), or from memory locations (Read cycle). Two parameters define how the burst mode will operate: burst sequence and burst length. These parameters are programmable and are determined by address bits  $A_0$ — $A_3$  during the Mode Register Set command. Burst type defines the sequence in which the burst data will be delivered or stored to the SDRAM. Two types of burst sequence are supported: sequential and interleave. The burst length controls the number of bits that will be output after a Read command, or the number of bits to be input after a Write command. The burst length can be programmed to values of 2, 4, or 8. See the Burst Length and Sequence table below for programming information.

### Burst Length and Sequence

| Burst Length | Starting Length (A <sub>2</sub> , A <sub>1</sub> , A <sub>0</sub> ) | Sequential Mode           | Interleave Mode        |

|--------------|---------------------------------------------------------------------|---------------------------|------------------------|

| 2            | xx0                                                                 | 0, 1                      | 0, 1                   |

| 2            | xx1                                                                 | 1, 0                      | 1, 0                   |

|              | x00                                                                 | 0, 1, 2, 3                | 0, 1, 2, 3             |

|              | x01                                                                 | 1, 2, 3, 0                | 1, 0, 3, 2             |

| 4            | x10                                                                 | 2, 3, 0, 1                | 2, 3, 0, 1             |

|              | x11                                                                 | 3, 0, 1, 2                | 3, 2, 1, 0             |

|              | 000                                                                 | 0,1, 2, 3, 4, 5, 6, 7     | 0,1, 2, 3, 4, 5, 6, 7  |

|              | 001                                                                 | 1, 2, 3, 4, 5, 6, 7, 0    | 1, 0, 3, 2, 5, 4, 7, 6 |

|              | 010                                                                 | 2, 3, 4, 5, 6, 7, 0, 1    | 2, 3, 0, 1, 6, 7, 4, 5 |

| _            | 011                                                                 | 3, 4, 5, 6, 7, 0, 1, 2    | 3, 2, 1, 0, 7, 6, 5, 4 |

| 8            | 100                                                                 | 4, 5, 6, 7, 0, 1, 2, 3    | 4, 5, 6, 7, 0, 1, 2, 3 |

|              | 101                                                                 | 5, 6, 7, 0, 1, 2, 3, 4    | 5, 4, 7, 6, 1, 0, 3, 2 |

|              | 110                                                                 | 6, 7, 0, 1, 2, 3, 4, 5, 6 | 6, 7, 4, 5, 2, 3, 0, 1 |

|              | 111                                                                 | 7, 0, 1, 2, 3, 4, 5, 6    | 7, 6, 5, 4, 3, 2, 1, 0 |

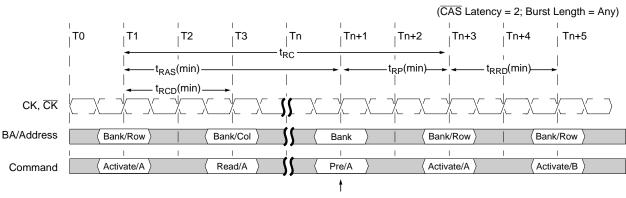

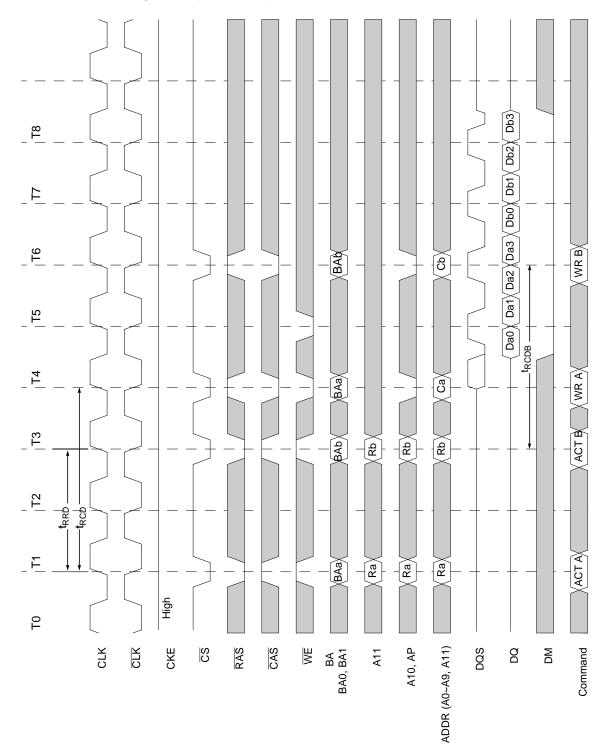

#### Bank Activate Command

The Bank Activate command is issued by holding  $\overline{CAS}$  and  $\overline{WE}$  high with  $\overline{CS}$  and  $\overline{RAS}$  low at the rising edge of the clock. The DDR SDRAM has four independent banks, so two Bank Select addresses (BA $_0$  and BA $_1$ ) are supported. The Bank Activate command must be applied before any Read or Write operation can be executed. The delay from the Bank Activate command to the first Read or Write command must meet or exceed the minimum  $\overline{RAS}$  to  $\overline{CAS}$  delay time ( $t_{RCD}$  min). Once a bank has been activated, it must be precharged before another Bank Activate command can be applied to the same bank. The minimum time interval between interleaved Bank Activate commands (Bank A to Bank B and vice versa) is the Bank to Bank delay time ( $t_{RRD}$  min).

### **Bank Activation Timing**

Begin Precharge Bank A

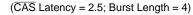

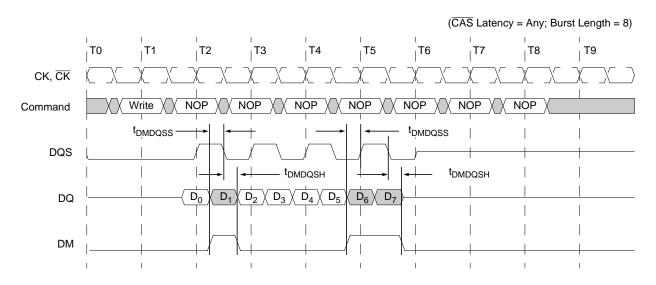

### **Read Operation**

With the DLL enabled, all devices operating at the same frequency within a system are ensured to have the same timing relationship between DQ and DQS relative to the CK input regardless of device density, process variation, or technology generation.

The data strobe signal (DQS) is driven off chip simultaneously with the output data (DQ) during each read cycle. The same internal clock phase is used to drive both the output data and data strobe signal off chip to minimize skew between data strobe and output data. This internal clock phase is nominally aligned to the input differential clock ( $\overline{CK}$ ) by the on-chip DLL. Therefore, when the DLL is enabled and the clock frequency is within the specified range for proper DLL operation, the data strobe (DQS), output data (DQ), and the system clock ( $\overline{CK}$ ) are all nominally aligned.

Since the data strobe and output data are tightly coupled in the system, the data strobe signal may be delayed and used to latch the output data into the receiving device. The tolerance for skew between DQS and DQ ( $t_{DQSQ}$ ) is tighter than that possible for CK to DQ ( $t_{AC}$ ) or DQS to CK ( $t_{DQSCK}$ ).

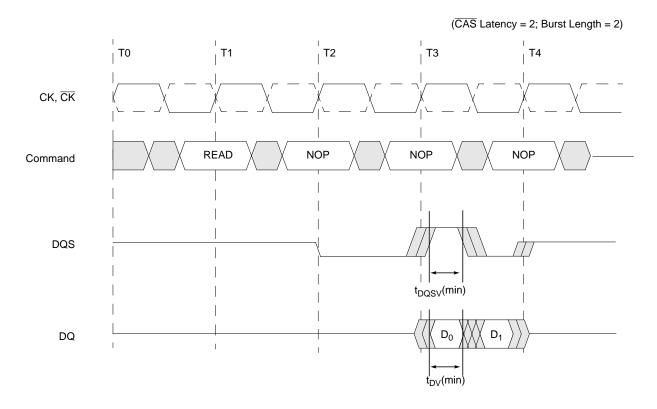

# Output Data (DQ) and Data Strobe (DQS) Timing Relative to the Clock (CK) During Read Cycles

The minimum time during which the output data (DQ) is valid is critical for the receiving device (i.e., a memory controller device). This also applies to the data strobe during the read cycle since it is tightly coupled to the output data. The minimum data output valid time  $(t_{DV})$  and minimum data strobe valid time  $(t_{DQSV})$  are derived from the minimum clock high/low time minus a margin for variation in data access and hold time due to DLL jitter and power supply noise.

### Output Data and Data Strobe Valid Window for DDR Read Cycles

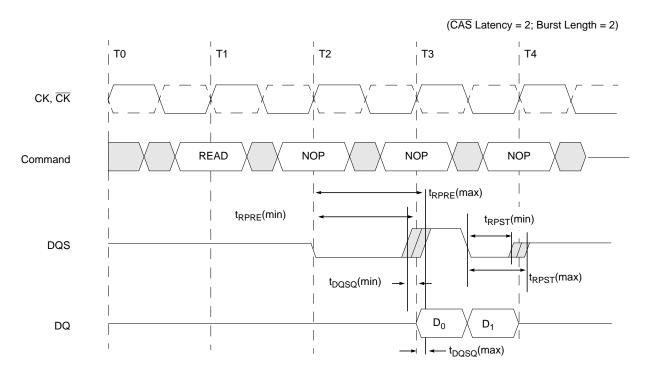

### Read Preamble and Postamble Operation

Prior to a burst of read data and given that the controller is not currently in burst read mode, the data strobe signal (DQS), must transition from Hi-Z to a valid logic low. The is referred to as the data strobe "read preamble" (t<sub>RPRE</sub>). This transition from Hi-Z to logic low nominally happens one clock cycle prior to the first edge of valid data.

Once the burst of read data is concluded and given that no subsequent burst read operations are initiated, the data strobe signal (DQS) transitions from a logic low level back to Hi-Z. This is referred to as the data strobe "read postamble" (t<sub>RPST</sub>). This transition happens nominally one-half clock period after the last edge of valid data.

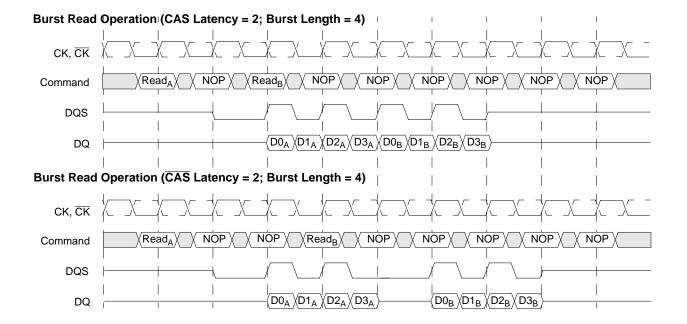

Consecutive or "gapless" burst read operations are possible from the same DDR SDRAM device with no requirement for a data strobe "read" preamble or postamble in between the groups of burst data. The data strobe read preamble is required before the DDR device drives the first output data off chip. Similarly, the data strobe postamble is initiated when the device stops driving DQ data at the termination of read burst cycles.

# Data Strobe Preamble and Postamble Timings for DDR Read Cycles

# Consecutive Burst Read Operation and Effects on the Data Strobe Preamble and Postamble

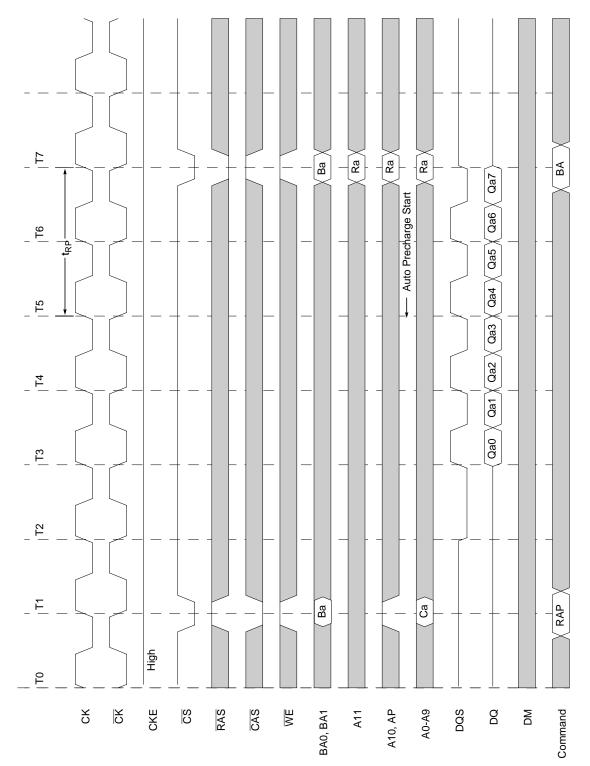

# Auto Precharge Operation

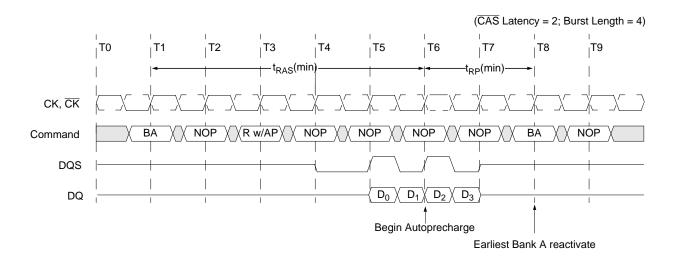

The Auto Precharge operation can be issued by having column address  $A_{10}$  high when a Read or Write command is issued. If  $A_{10}$  is low when a Read or Write command is issued, then normal Read or Write burst operation is executed and the bank remains active at the completion of the burst sequence. When the Auto Precharge command is activated, the active bank automatically begins to precharge at the earliest possible moment during the Read or Write cycle once  $t_{RAS}(min)$  is satisfied.

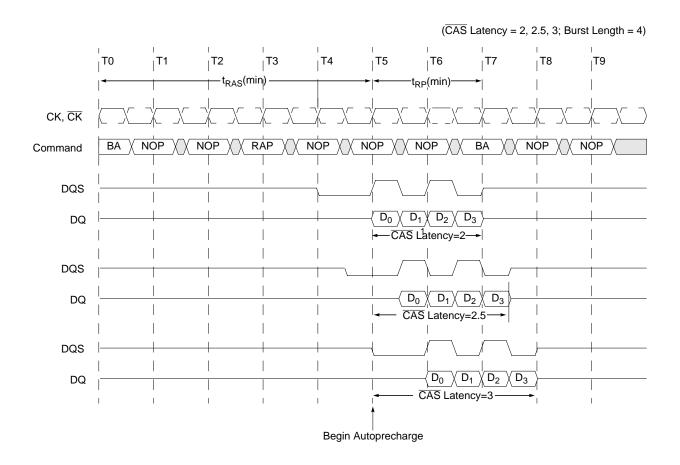

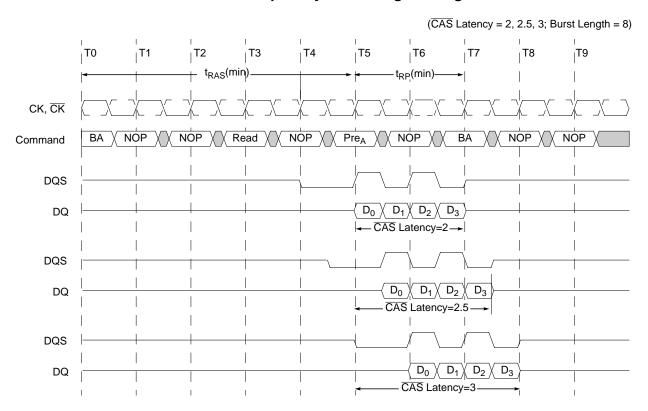

### Read with Auto Precharge

If a Read with Auto Precharge command is initiated, the DDR SDRAM will enter the precharge operation N-clock cycles measured from the last data of the burst read cycle where N is equal to the  $\overline{\text{CAS}}$  latency programmed into the device. If a Read with autoprecharge command is issued before  $t_{\text{RAS}}(\text{min})$  is satisfied, the precharge operation will be delayed until that time when  $t_{\text{RAS}}(\text{min})$  is met. Once the autoprecharge operation has begun, the bank cannot be reactivated until the minimum precharge time ( $t_{\text{RP}}$ ) has been satisfied.

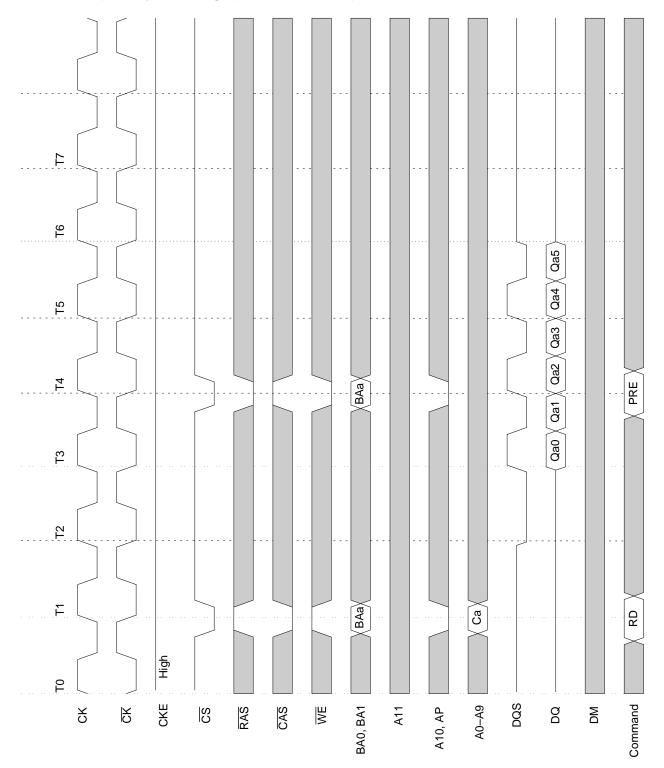

### Read with Autoprecharge Timing

# Read with Autoprecharge Timing as a Function of CAS Latency

### **Precharge Timing During Read Operation**

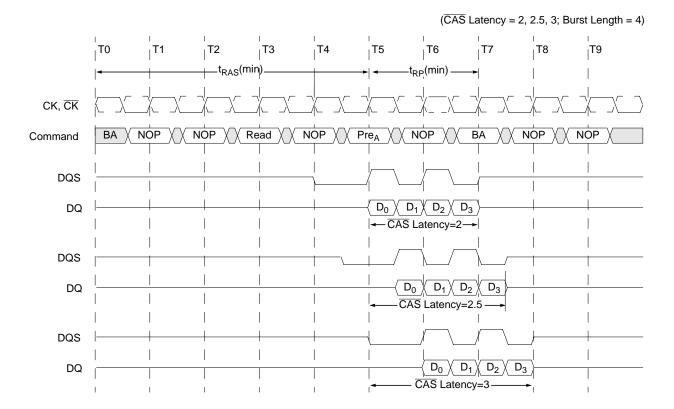

For the earliest possible Precharge command without interrupting a Read burst, the Precharge command may be issued on the rising clock edge which is  $\overline{\text{CAS}}$  latency (CL) clock cycles before the end of the Read burst. A new Bank Activate (BA) command may be issued to the same bank after the  $\overline{\text{RAS}}$  precharge time ( $t_{\text{RP}}$ ). A Precharge command can not be issued until  $t_{\text{RAS}}$ (min) is satisfied.

# Read with Precharge Timing as a Function of CAS Latency

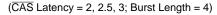

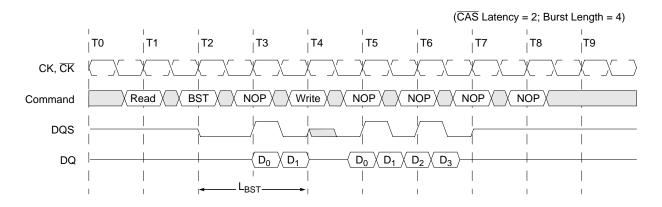

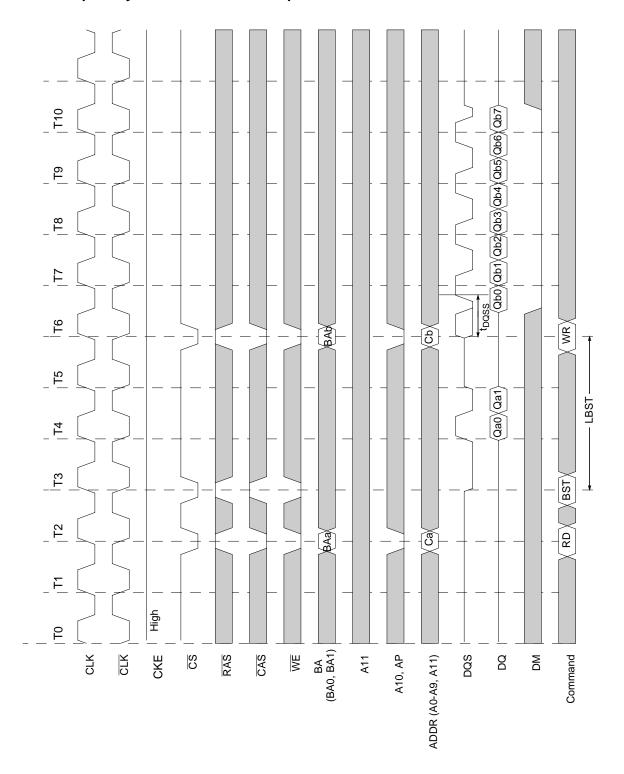

# **Burst Stop Command**

The Burst Stop command is valid only during burst read cycles and is initiated by having  $\overline{RAS}$  and  $\overline{CAS}$  high with  $\overline{CS}$  and  $\overline{WE}$  low at the rising edge of the clock. When the Burst Stop command is issued during a burst Read cycle, both the output data (DQ) and data strobe (DQS) go to a high impedance state after a delay (L<sub>BST</sub>) equal to the  $\overline{CAS}$  latency programmed into the device. If the Burst Stop command is issued during a burst Write cycle, the command will be treated as a NOP command.

# Read Terminated by Burst Stop Command Timing

#### Read Interrupted by a Precharge

A Burst Read operation can be interrupted by a precharge of the same bank. The Precharge command to Output Disable latency is equivalent to the  $\overline{\text{CAS}}$  latency.

#### Read Interrupted by a Precharge Timing

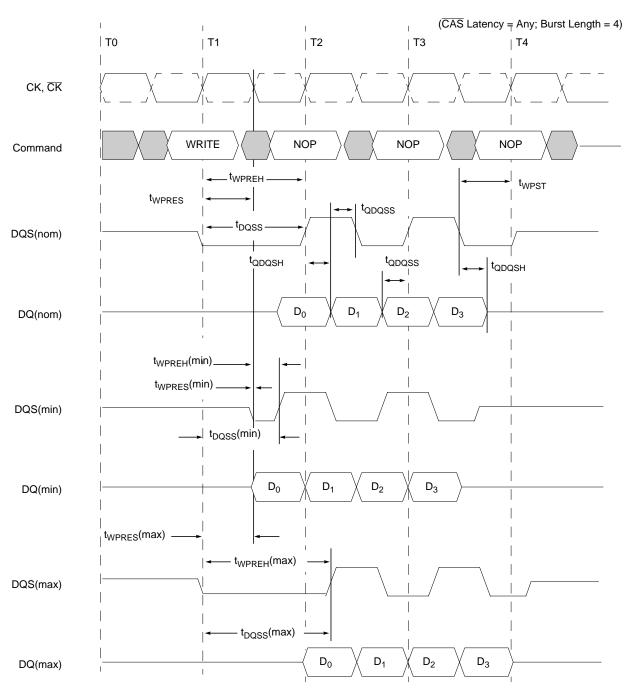

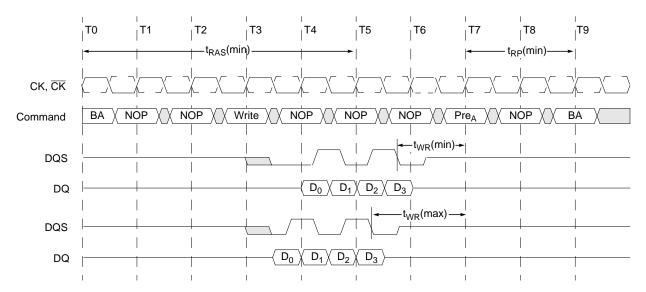

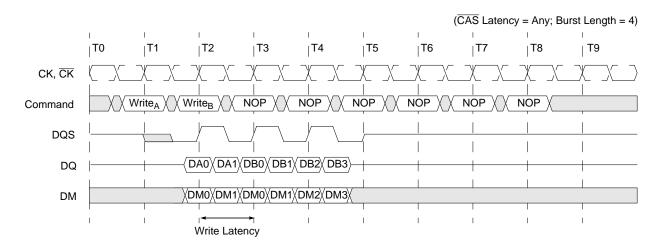

#### **Burst Write Operation**

The Burst Write command is issued by having  $\overline{\text{CS}}$ ,  $\overline{\text{CAS}}$ , and  $\overline{\text{WE}}$  low while holding  $\overline{\text{RAS}}$  high at the rising edge of the clock. The address inputs determine the starting column address. The memory controller is required to provide an input data strobe (DQS) to the DDR SDRAM to strobe or latch the input data (DQ) and data mask (DM) into the device. During Write cycles, the data strobe applied to the DDR SDRAM is required to be nominally centered within the data (DQ) and data mask (DM) valid windows. The data strobe must be driven high nominally one clock after the write command has been registered. Timing parameters  $t_{DQSS}(min)$  and  $t_{DQSS}(max)$  define the allowable window when the data strobe must be driven high.

Input data for the first Burst Write cycle must be applied one clock cycle after the Write command is registered into the device (WL=1). The input data valid window is nominally centered around the midpoint of the data strobe signal. The data window is defined by DQ to DQS setup time ( $t_{QDQSS}$ ) and DQ to DQS hold time ( $t_{QDQSH}$ ). All data inputs must be supplied on each rising and falling edge of the data strobe until the burst length is completed. When the burst has finished, any additional data supplied to the DQ pins will be ignored.

#### **Write Preamble and Postamble Operation**

Prior to a burst of write data and given that the controller is not currently in burst write mode, the data strobe signal (DQS), must transition from Hi-Z to a valid logic low. This is referred to as the data strobe "write preamble". This transition from Hi-Z to logic low nominally happens on the falling edge of the clock after the write command has been registered by the device. The preamble is explicitly defined by a setup time (t<sub>WPRES</sub>(min)) and hold time (t<sub>WPREH</sub>(min)) referenced to the first falling edge of CK after the write command.

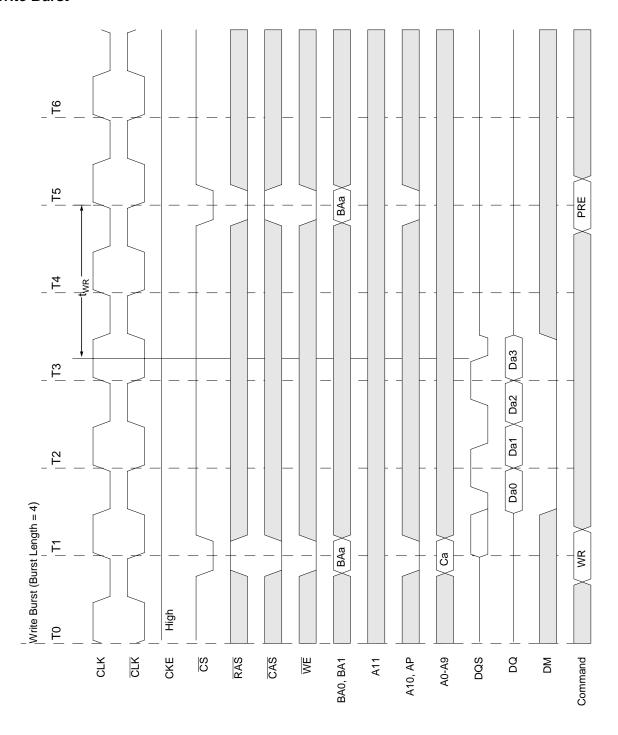

# **Burst Write Timing**

Once the burst of write data is concluded and given that no subsequent burst write operations are initiated, the data strobe signal (DQS) transitions from a logic low level back to Hi-Z. This is referred to as the data strobe "write postamble". This transition happens nominally one-half clock period after the last data of the burst cycle is latched into the device.

### Write Interrupted by a Precharge

A Burst Write can be interrupted before completion of the burst by a Precharge command, with the only restriction being that the interval that separates the commands be at least one clock cycle. When the previous burst is interrupted, the remaining addresses are overridden by the new address and data will be written into the device until the programmed burst length is satisfied.

### Write Interrupted by a Precharge Timing

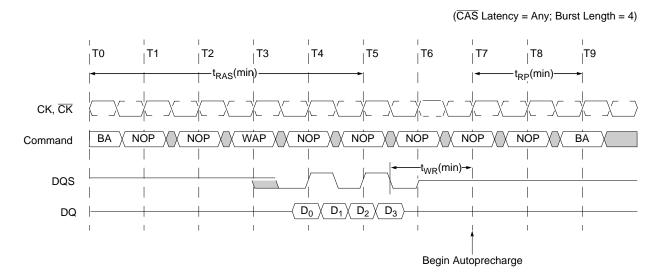

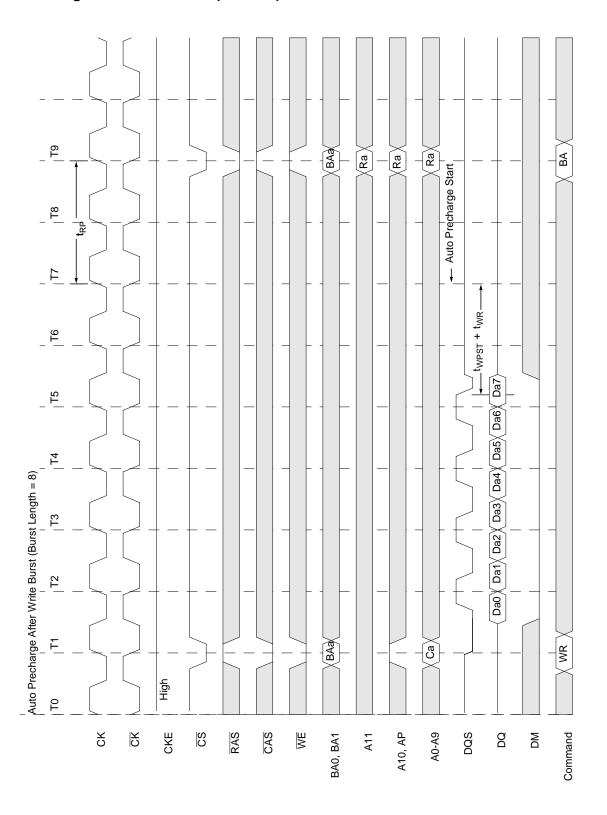

#### Write with Auto Precharge

If  $A_{10}$  is high when a Write command is issued, the Write with auto Precharge function is performed. Any new command to the same bank should not be issued until the internal precharge is completed. The internal precharge begins after keeping  $t_{WR}$  (min.).

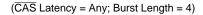

### Write with Auto Precharge Timing

# Precharge Timing During Write Operation

Precharge timing for Write operations in DRAMs requires enough time to satisfy the write recovery requirement. This is the time required by a DRAM sense amp to fully store the voltage level. For DDR SDRAMs, a timing parameter ( $t_{WR}$ ) is used to indicate the required amount of time between the last valid write operation and a Precharge command to the same bank.

The "write recovery" operation begins on the rising clock edge after the last DQS edge that is used to strobe in the last valid write data. "Write recovery" is complete on the next rising clock edge that is used to strobe in the Precharge command.

For the earliest possible Precharge command following a Write burst without interrupting the burst, the minimum time for "write recovery" is 1.25 clock cycles. Maximum "write recovery" time is 1.75 clock cycles.

# Write with Precharge Timing

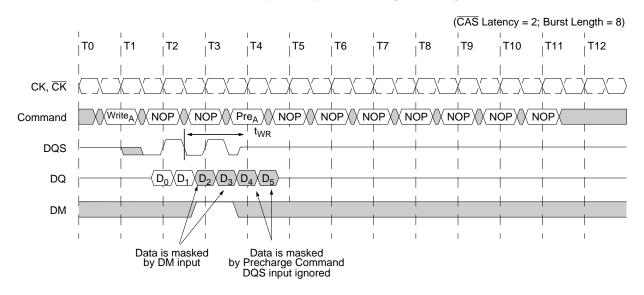

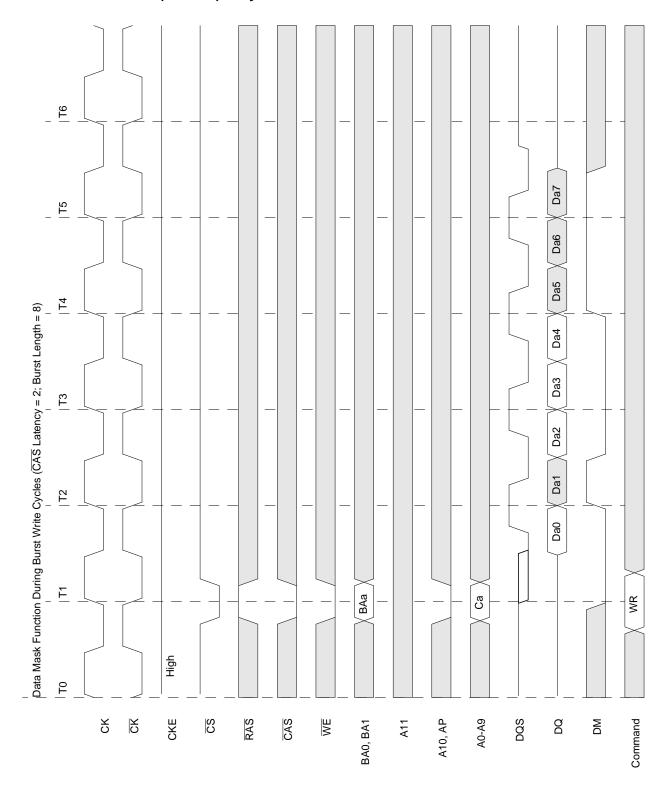

### Data Mask Function

The DDR SDRAM has a Data Mask function that is used in conjunction with the Write cycle, but not the Read cycle. When the Data Mask is activated (DM high) during a Write operation, the Write is blocked (Mask to Data Latency = 0).

When issued, the Data Mask must be referenced to both the rising and falling edges of Data Strobe.

### Data Mask Timing

### **Burst Interruption**

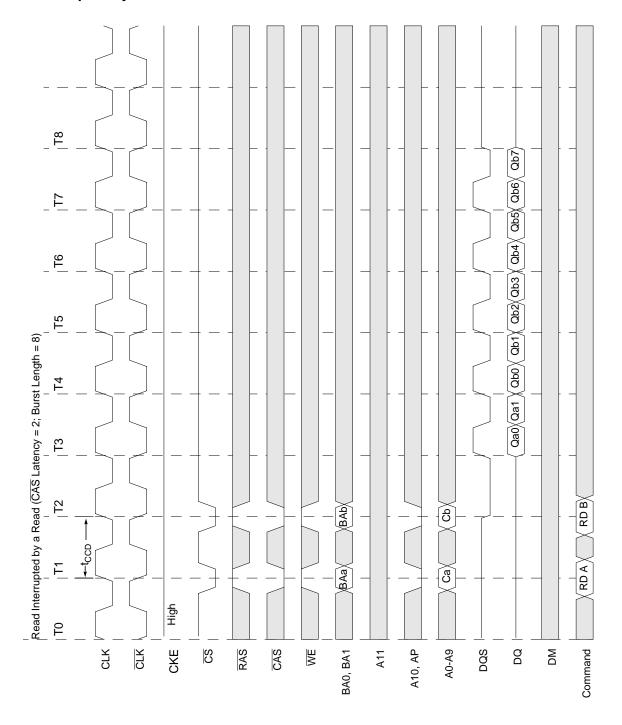

#### Read Interrupted by a Read

A Burst Read can be interrupted before completion of the burst by issuing a new Read command to any bank. When the previous burst is interrupted, the remaining addresses are overridden with a full burst length starting with the new address. The data from the first Read command continues to appear on the outputs until the  $\overline{\text{CAS}}$  latency from the interrupting Read command is satisfied. At this point, the data from the interrupting Read command appears on the bus. Read commands can be issued on each rising edge of the system clock. It is illegal to interrupt a Read with autoprecharge command with a Read command.

# Read Interrupted by a Read Command Timing

#### Read Interrupted by a Write

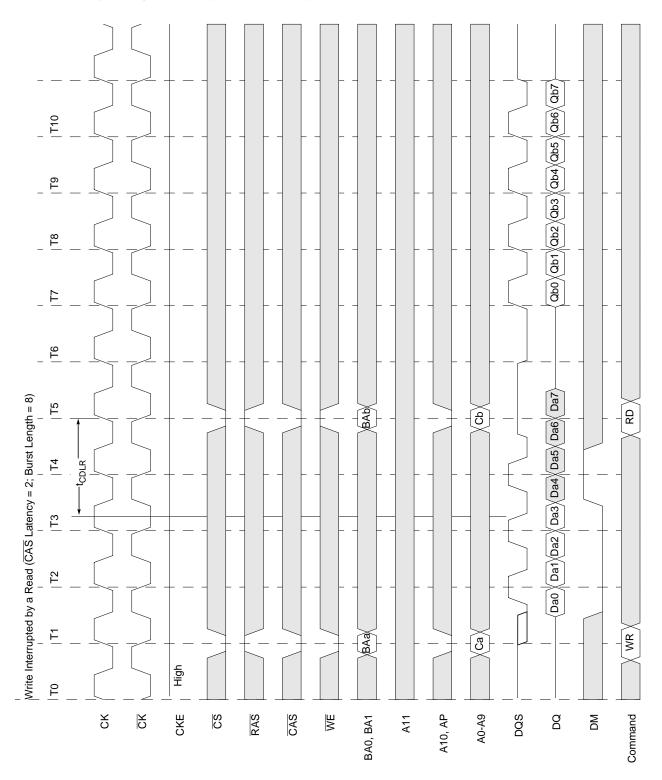

To interrupt a Burst Read with a Write command, a Burst Stop command must be asserted to stop the burst read operation and 3-state the DQ bus. Additionally, control of the DQS bus must be turned around to allow the memory controller to drive the data strobe signal (DQS) into the DDR SDRAM for the write cycles. Once the Burst Stop command has been issued, a Write command can not be issued until a minimum delay or latency ( $L_{BST}$ ) has been satisfied. This latency is measured from the Burst Stop command and is equivalent to the  $\overline{CAS}$  latency programmed into the mode register. In instances where  $\overline{CAS}$  latency is measured in half clock cycles, the minimum delay ( $L_{BST}$ ) is rounded up to the next full clock cycle (i.e., if CL=2 then  $L_{BST}=2$ , if CL=2.5 then  $L_{BST}=3$ ). It is illegal to interrupt a Read with autoprecharge command with a Write command.

### Read Interrupted by Burst Stop Command Followed by a Write Command Timing

### Write Interrupted by a Write

A Burst Write can be interrupted before completion by a new Write command to any bank. When the previous burst is interrupted, the remaining addresses are overridden with a full burst length starting with the new address. The data from the first Write command continues to be input into the device until the Write Latency of the interrupting Write command is satisfied (WL=1) At this point, the data from the interrupting Write command is input into the device. Write commands can be issued on each rising edge of the system clock. It is illegal to interrupt a Write with autoprecharge command with a Write command.

# Write Interrupted by a Write Command Timing

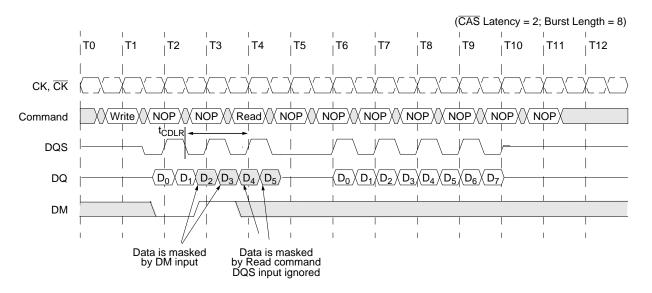

#### Write Interrupted by a Read

A Burst Write can be interrupted by a Read command to any bank. If a burst write operation is interrupted prior to the end of the burst operation, then the last two pieces of input data prior to the Read command must be masked off with the data mask (DM) input pin to prevent invalid data from being written into the memory array. Any data that is present on the DQ pins coincident with or following the Read command will be masked off by the Read command and will not be written to the array. The memory controller must give up control of both the DQ bus and the DQS bus at least one clock cycle before the read data appears on the outputs in order to avoid contention. In order to avoid data contention within the device, a delay is required (t<sub>CDLR</sub>) from the last valid data input before a Read command can be issued to the device. It is illegal to interrupt a Write with autoprecharge command with a Read command.

# Write Interrupted by a Read Command Timing

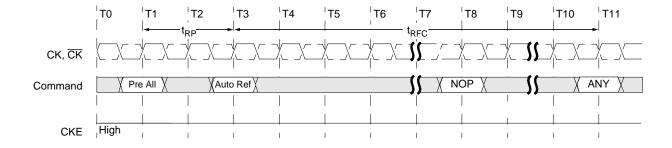

#### Auto Refresh

The Auto Refresh command is issued by having  $\overline{\text{CS}}$ ,  $\overline{\text{RAS}}$ , and  $\overline{\text{CAS}}$  held low with CKE and  $\overline{\text{WE}}$  high at the rising edge of the clock. All banks must be precharged and idle for a  $t_{\text{RP}}(\text{min})$  before the Auto Refresh command is applied. No control of the address pins is required once this cycle has started because of the internal address counter. When the Auto Refresh cycle has completed, all banks will be in the idle state. A delay between the Auto Refresh command and the next Activate command or subsequent Auto Refresh command must be greater than or equal to the  $t_{\text{RFC}}(\text{min})$ . Commands may not be issued to the device once an Auto Refresh cycle has begun.  $\overline{\text{CS}}$  input must remain high during the refresh period or NOP commands must be registered on each rising edge of the CK input until the refresh period is satisfied.

#### Auto Refresh Timing

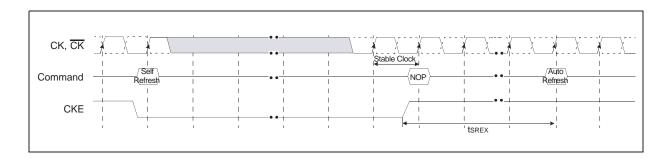

#### Self Refresh

A self refresh command is defined by having  $\overline{\text{CS}}$ ,  $\overline{\text{RAS}}$ ,  $\overline{\text{CAS}}$  and CKE held low with  $\overline{\text{WE}}$  high at the rising edge of the clock (CK). Once the self refresh command is initiated, CKE must be held low to keep the device in self refresh mode. During the self refresh operation, all inputs except CKE are ignored. The clock is internally disabled during self refresh operation to reduce power consumption. The self refresh is exited by supplying stable clock input before returning CKE high, asserting deselect or NOP command and then asserting CKE high for longer than  $t_{\text{SREX}}$  for locking of DLL. The auto refresh is required before self refresh entry and after self refresh exit.

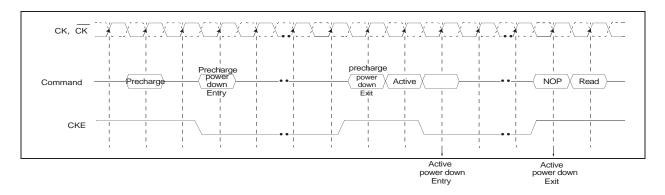

#### Power Down Mode

The power down mode is entered when CKE is low and exited when CKE is high. Once the power down mode is initiated, all of the receiver circuits except clock, CKE and DLL circuit are gated off to reduce power consumption. The both banks should be in idle state prior to entering the precharge power down mode and CKE should be set high at least 1tck+tlS prior to row active command. During power down mode, refresh operations cannot be performed, therefore the device cannot remain in power down mode longer than the refresh period (t<sub>REF</sub>) of the device.

# SSTL\_2 Input AC/DC Logic Levels

| Symbol               | Parameter           | Min                    | Max                    | Units | Notes |

|----------------------|---------------------|------------------------|------------------------|-------|-------|

| V <sub>IH</sub> (DC) | DC Input Logic High | V <sub>REF</sub> +0.18 | V <sub>DDQ</sub> +0.3  | V     | 1     |

| V <sub>IH</sub> (AC) | AC Input Logic High | V <sub>REF</sub> +0.35 | _                      | V     |       |

| V <sub>IL</sub> (DC) | DC Input Logic Low  | -0.30                  | V <sub>REF</sub> -0.18 | V     |       |

| V <sub>IL</sub> (AC) | AC Input Logic Low  | _                      | V <sub>REF</sub> -0.35 | V     |       |

Note: 1. The relationship of the V<sub>DDQ</sub> of the driving device and the V<sub>REF</sub> of the receiving device is what determines noise margins. However, in the case of V<sub>IH</sub> (max) (input overdrive), it is the V<sub>DDQ</sub> of the receiving device that is referenced. In the case where a device is implemented such that supports SSTL\_2 inputs but has no SSTL\_2 outputs (e.g., a translator), and therefore no V<sub>DDQ</sub> supply voltage connection, inputs must tolerate input overdrive to 3.0V (High corner V<sub>DDQ</sub>+300mV.)

### SSTL\_2 AC Test Conditions

| Symbol                   | Parameter Value                         |                      | Units | Notes |

|--------------------------|-----------------------------------------|----------------------|-------|-------|

| V <sub>REF</sub>         | Input Reference Voltage                 | 0.5*V <sub>DDQ</sub> | V     | 1     |

| V <sub>SWING</sub> (max) | Input Signal Maximum Peak to Peak Swing | 1.5                  | V     | 1, 2  |

| SLEW                     | Input Signal Minimum Slew Rate          | 1.0                  | V/ns  | 3     |

**Notes:** 1. Input waveform timing is referenced to the input signal crossing the  $V_{\mathsf{REF}}$  level applied to the device.

- 2. Compliant devices must still meet the V<sub>IH</sub> (AC) and V<sub>IL</sub> (AC) specifications under actual use conditions.

- 3. The 1 V/ns input signal minimum slew rate is to be maintained in the V<sub>IL</sub> max (AC) to V<sub>IL</sub> min (AC) range of the input signal swing.

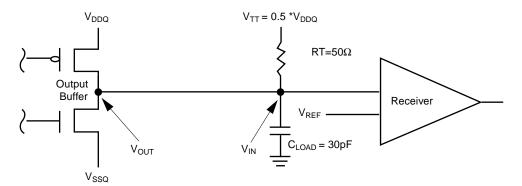

#### SSTL\_2 Output Buffers

The input voltage provided to the receiver depends on three parameters:

- V<sub>DDQ</sub> and current drive capabilities of the output buffer

- Termination voltage

- Termination resistance

- $\blacksquare$   $V_{DDQ} \le V_{DD}$

# Class II SSTL\_2 Output Buffer (Driver)

# DC CHARACTERISTICS

Recommended operating conditions Unless Otherwise Noted,  $T_A=0$  to  $70^{\circ}C$

| Parameter                                         | Cumbal             | Took Condition                                                                 | CAS | Version |                                                                            |     |      |     |     |    |

|---------------------------------------------------|--------------------|--------------------------------------------------------------------------------|-----|---------|----------------------------------------------------------------------------|-----|------|-----|-----|----|

| Parameter                                         | Symbol             | mbol Test Condition                                                            |     | -6      | <b>-7</b>                                                                  | -8  | Unit |     |     |    |

| Operating Current<br>(One Bank Active)            | I <sub>CC</sub> 1  | Burst Length=2 t <sub>RC</sub> =t <sub>RC</sub> (min) I <sub>OL</sub> =0mA     |     |         | Burst Length=2 t <sub>RC</sub> =t <sub>RC</sub> (min) I <sub>OL</sub> =0mA |     |      | 120 | 110 | mA |

| Precharge Standby Current in Power-Down Mode      | I <sub>CC2</sub> P | CKE=V <sub>IL</sub> (max), t <sub>CC</sub> =10ns                               |     |         | CKE=V <sub>IL</sub> (max), t <sub>CC</sub> =10ns 20                        |     |      |     |     | mA |

| Precharge Standby Current in Non Power-Down Mode  | I <sub>CC2</sub> N | CKE=VIH(min), CS-VIH(min), tCC=10ns Input signals are changed once during 20ns |     |         | , , , ,                                                                    |     |      |     |     |    |

| Active Standby Current in Power-Down Mode         | I <sub>CC3</sub> P | CKE=V <sub>IL</sub> (max), t <sub>CC</sub> =10ns                               |     |         | 30                                                                         |     |      |     |     |    |

| Active Standby Current in Non-<br>Power-Down Mode | I <sub>CC3</sub> N | CKE=VIH(min), CS-VIH(min), tCC=10ns Input signals are changed once during 20   |     | 60      |                                                                            |     | mA   |     |     |    |

| Operating Current (Burst Mode)                    | I <sub>CC4</sub>   | I <sub>OL</sub> =0mA Page Burst All Banks activated t <sub>CCD</sub> =2CKs     | 2   | 140     | 130                                                                        | 120 | mA   |     |     |    |

| Refresh Current                                   | I <sub>CC5</sub>   | t <sub>RC</sub> =t <sub>RFC</sub> (min)                                        |     | 200     |                                                                            |     | mA   |     |     |    |

| Self Refresh Current                              | I <sub>CC6</sub>   | CKE=0.2V                                                                       |     |         | 2                                                                          |     | mA   |     |     |    |

# $\textit{AC Characteristics}~(T_A \!\!=\!\! 0 \text{ to +} 70^{\circ}\text{C},\, V_{CC} \!\!=\!\! 2.5 \pm 0.2 \text{V})$

|                        |                      |             | _      | -8    | _      | 7     | _      | -6    |                 |

|------------------------|----------------------|-------------|--------|-------|--------|-------|--------|-------|-----------------|

| Symbol                 | Param                | eter        | Min.   | Max.  | Min.   | Max.  | Min.   | Max.  | Unit            |

| Clock Cyc              | le                   |             | 1      | 1     | '      | •     |        |       | -!              |

| t <sub>CK</sub>        | Clock Cycle          | CL = 2.0    | 10     | 15    | 8      | 15    | 7      | 15    | ns              |

|                        |                      | CL = 2.5    | 9      | 15    | 7.5    | 15    | 6.5    | 15    | ns              |

|                        |                      | CL = 3.0    | 8      | 15    | 7      | 15    | 6      | 15    | ns              |

| t <sub>CH</sub>        | Clock Duty Cycle     | ,           | 0.45   | 0.55  | 0.45   | 0.55  | 0.45   | 0.55  | %               |

| t <sub>CL</sub>        |                      |             | 0.45   | 0.55  | 0.45   | 0.55  | 0.45   | 0.55  | %               |

| Command                | Cycle                |             | •      |       |        |       |        | •     |                 |

| t <sub>RAS</sub>       | Row Active Time (AC  | CT->PRE)    | 56     | -     | 49     | -     | 42     | -     | ns              |

| t <sub>RP</sub>        | Row Precharge (PRI   | E->ACT)     | 24     | -     | 21     | -     | 18     | -     | ns              |

| t <sub>RC</sub>        | Row Cycle (ACT->A    | CT)         | 80     | -     | 70     | -     | 60     | -     | ns              |

| t <sub>RCD</sub>       | RAS->CAS Delay (A    | CT->WR/RD)  | 24     | -     | 21     | -     | 18     | -     | ns              |

| t <sub>RRD</sub>       | RAS->RAS Delay (A    | CTa->ACTb)  | 16     | -     | 14     | -     | 12     | -     | ns              |

| t <sub>RFC</sub>       | Auto-Refresh (REF->  | >REF/ACT)   | 88     | -     | 77     | -     | 66     | -     | ns              |

| t <sub>REF</sub>       | Refresh Cycle        |             | -      | 64    | -      | 64    | -      | 64    | ms              |

| t <sub>SREX(DLL)</sub> | Self-Refresh Exit De | lay         | 200    | -     | 200    | -     | 200    | -     | cycles          |

| t <sub>SREX</sub>      |                      |             | 1      | -     | 1      | -     | 1      | -     | t <sub>RC</sub> |

| t <sub>IS</sub>        | CMD, ADDR->CLK       | Setup       | 0.15   | -     | 0.15   | -     | 0.15   | -     | t <sub>CK</sub> |

| t <sub>IH</sub>        | CMD, ADDR->CLK I     | Hold        | 0.15   | -     | 0.15   | -     | 0.15   | -     | t <sub>CK</sub> |

| t <sub>CCD</sub>       | CAS->CAS Delay (C    | cola->Colb) | 1      |       | 1      |       | 1      |       | t <sub>CK</sub> |

| t <sub>MRD</sub>       | Mode Register Set D  | Pelay       | 2      |       | 2      |       | 2      |       | t <sub>CK</sub> |

| t <sub>PDENT</sub>     | Power Down Entry D   | elay        | 1      |       | 1      |       | 1      |       | t <sub>CK</sub> |

| t <sub>PDEX(DLL)</sub> | Power Down Exit De   | lay         | 1      |       | 1      |       | 1      |       | t <sub>CK</sub> |

| t <sub>PDEX</sub>      |                      |             | 1      |       | 1      |       | 1      |       | t <sub>CK</sub> |

| Read Cycl              | e                    |             |        |       |        |       |        | •     | •               |

| t <sub>AC</sub>        | CLK->DQ Skew         |             | -0.1   | 0.1   | -0.1   | 0.1   | -0.1   | 0.1   | t <sub>CK</sub> |

| t <sub>DQSCK</sub>     | CLK->DQS Skew        |             | -0.1   | 0.1   | -0.1   | 0.1   | -0.1   | 0.1   | t <sub>CK</sub> |

| t <sub>DQSQ</sub>      | DQS->DQ Skew         |             | -0.075 | 0.075 | -0.075 | 0.075 | -0.075 | 0.075 | t <sub>CK</sub> |

| t <sub>DV</sub>        | DQ/DQS Valid Wind    | ow          | 0.3    | -     | 0.3    | -     | 0.3    | -     | t <sub>CK</sub> |

| t <sub>RPRE</sub>      | Read DQS Preamble    | e           | 0.9    | 1.1   | 0.9    | 1.1   | 0.9    | 1.1   | t <sub>CK</sub> |

| t <sub>RPST</sub>      | Read DQS Postamb     | le          | 0.4    | 0.6   | 0.4    | 0.6   | 0.4    | 0.6   | t <sub>CK</sub> |

# AC Characteristics (Continued) (T\_A=0 to +70°C, $V_{CC}$ =2.5 $\pm$ 0.2V)

|                     |                                      | _     | 8    | _     | 7    | -6    |      |                 |

|---------------------|--------------------------------------|-------|------|-------|------|-------|------|-----------------|

| Symbol              | Parameter                            | Min.  | Max. | Min.  | Max. | Min.  | Max. | Unit            |

| Write Cyc           | le                                   |       |      |       |      |       |      | •               |

| t <sub>WPRES</sub>  | Write Preamble DQS Setup             | 0     | 0.5  | 0     | 0.5  | 0     | 0.5  | t <sub>CK</sub> |

| t <sub>WPREH</sub>  | Write Preamble DQS Hold              | 0.25  | 1.25 | 0.25  | 1.25 | 0.25  | 1.25 | t <sub>CK</sub> |

| t <sub>DQSS</sub>   | Write Preamble CLK->DQS (first)      | 0.75  | 1.25 | 0.75  | 1.25 | 0.75  | 1.25 | t <sub>CK</sub> |

| t <sub>DSH</sub>    | Write DQS High Width                 | 0.4   | 0.6  | 0.4   | 0.6  | 0.4   | 0.6  | t <sub>CK</sub> |

| t <sub>DSL</sub>    | Write DQS Low Width                  | 0.4   | 0.6  | 0.4   | 0.6  | 0.4   | 0.6  | t <sub>CK</sub> |

| t <sub>WPST</sub>   | Write Postamble DQS (last) -> Hi-Z   | 0.4   | 0.6  | 0.4   | 0.6  | 0.4   | 0.6  | t <sub>CK</sub> |

| t <sub>DQSR</sub>   | Write (last DIN) -> READ Command     | 1.25  | 1.75 | 1.25  | 1.75 | 1.25  | 1.75 | t <sub>CK</sub> |

| t <sub>WR</sub>     | Write (last DIN) -> PRE Command      | 1.25  | 1.75 | 1.25  | 1.75 | 1.25  | 1.75 | t <sub>CK</sub> |

| t <sub>DS</sub>     | DQ/DM -> DQS Setup (Data Setup)      | 0.075 | -    | 0.075 | -    | 0.075 | -    | t <sub>CK</sub> |

| t <sub>DH</sub>     | DQ/DM -> DQS Hold (Data Hold)        | 0.075 | -    | 0.075 | -    | 0.075 | -    | t <sub>CK</sub> |

| t <sub>QDQSS</sub>  | Date Input to Data Strobe Setup Time | 0.075 | -    | 0.075 | -    | 0.075 | -    | t <sub>CK</sub> |

| t <sub>QDQSH</sub>  | Date Input to Data Strobe Hold Time  | 0.075 | -    | 0.075 | -    | 0.075 | -    | t <sub>CK</sub> |

| t <sub>DMDSQS</sub> | Date Mask to Data Strobe Setup Time  | 0.075 | -    | 0.075 | -    | 0.075 | -    | t <sub>CK</sub> |

| t <sub>DMDQSH</sub> | Date Mask to Data Strobe Hold Time   | 0.075 | -    | 0.075 | -    | 0.075 | -    | t <sub>CK</sub> |

# Complete List of Operation Commands

# **DDR SDRAM Function Truth Table**

| CURRENT<br>STATE <sup>1</sup> | cs | RAS | CAS | WE | BS  | Addr  | ACTION                                                   |

|-------------------------------|----|-----|-----|----|-----|-------|----------------------------------------------------------|

| Idle                          | Н  | Х   | Х   | Х  | Х   | Х     | NOP or Power Down                                        |

|                               | L  | Н   | Н   | Н  | X   | Х     | NOP                                                      |

|                               | L  | Н   | Н   | L  | BS  | Х     | ILLEGAL <sup>2</sup>                                     |

|                               | L  | Н   | L   | X  | BS  | Х     | ILLEGAL <sup>2</sup>                                     |

|                               | L  | L   | Н   | Н  | BS  | RA    | Row (&Bank) Active; Latch Row Address                    |

|                               | L  | L   | Н   | L  | BS  | AP    | NOP <sup>4</sup>                                         |

|                               | L  | L   | L   | Н  | X   | Х     | Auto-Refresh or Self-Refresh <sup>5</sup>                |

|                               | L  | L   | L   | L  | Op- | Code  | Mode reg. Access <sup>5</sup>                            |

| Row Active                    | Н  | Х   | X   | Х  | Х   | Х     | NOP                                                      |

|                               | L  | Н   | Н   | X  | X   | X     | NOP                                                      |

|                               | L  | Н   | L   | Н  | BS  | CA,AP | Begin Read; Latch CA; DetermineAP                        |

|                               | L  | Н   | L   | L  | BS  | CA,AP | Begin Write; Latch CA; DetermineAP                       |

|                               | L  | L   | Н   | Н  | BS  | X     | ILLEGAL <sup>2</sup>                                     |

|                               | L  | L   | Н   | L  | BS  | AP    | Precharge                                                |

|                               | L  | L   | L   | Х  | Х   | Х     | ILLEGAL                                                  |

| Read                          | Н  | X   | X   | ×  | ×   | X     | NOP (Continue Burst to End;>Row Active)                  |

|                               | L  | Н   | Н   | Н  | X   | X     | NOP (Continue Burst to End;>Row Active)                  |

|                               | L  | Н   | Н   | L  | BS  | X     | ILLEGAL                                                  |

|                               | L  | Н   | L   | Н  | BS  | CA,AP | Term Burst, New Read, DetermineAP <sup>3</sup>           |

|                               | L  | Н   | L   | L  | BS  | CA,AP | Term Burst, Start Write, DetermineAP <sup>3</sup>        |

|                               | L  | L   | Н   | Н  | BS  | X     | ILLEGAL to Same Bank, other Bank 0K if tRRD is Satisfied |

|                               | L  | L   | Н   | L  | BS  | AP    | Term Burst, Precharge                                    |

|                               | L  | L   | L   | Х  | Х   | Х     | ILLEGAL                                                  |

| Write                         | Н  | X   | ×   | ×  | ×   | Х     | NOP (Continue Burst to End;>Row Active)                  |

|                               | L  | Н   | Н   | Н  | X   | Х     | NOP (Continue Burst to End;>Row Active)                  |

|                               | L  | Н   | H   | L  | BS  | X     | ILLEGAL                                                  |

|                               | L  | Н   | L   | Н  | BS  | CA,AP | Term Burst, Start Read, DetermineAP                      |

|                               | L  | Н   | L   | L  | BS  | CA,AP | Term Burst, New Write, DetermineAP <sup>3</sup>          |

|                               | L  | L   | Н   | Н  | BS  | X     | ILLEGAL <sup>2</sup>                                     |

|                               | L  | L   | H   | L  | BS  | AP    | Term Burst, Precharge <sup>3</sup>                       |

|                               | L  | L   | L   | Х  | Х   | Х     | ILLEGAL                                                  |

| Read                          | Н  | Х   | X   | X  | X   | Х     | NOP (Continue Burst to End;> Precharge)                  |

| with                          | L  | Н   | Н   | Н  | X   | Х     | NOP (Continue Burst to End;> Precharge)                  |

| Auto                          | L  | Н   | Н   | L  | BS  | Х     | ILLEGAL <sup>2</sup>                                     |

| Precharge                     | L  | Н   | L   | Н  | BS  | Х     | ILLEGAL <sup>2</sup>                                     |

|                               | L  | Н   | L   | L  | X   | Х     | ILLEGAL                                                  |

|                               | L  | L   | Н   | Н  | BS  | Х     | ILLEGAL <sup>2</sup>                                     |

|                               | L  | L   | Н   | L  | BS  | AP    | ILLEGAL <sup>2</sup>                                     |

|                               | L  | L   | L   | X  | X   | Х     | ILLEGAL                                                  |

# DDR SDRAM Function Truth Table (continued)

| CURRENT<br>STATE <sup>1</sup> | cs | RAS | CAS | WE | BS | Addr | ACTION                                   |  |

|-------------------------------|----|-----|-----|----|----|------|------------------------------------------|--|

| Write                         | Н  | Х   | Х   | Х  | Х  | Х    | NOP (Continue Burst to End;> Precharge)  |  |

| with                          | L  | Н   | Н   | Н  | X  | X    | NOP (Continue Burst to End;> Precharge)  |  |

| Auto                          | L  | Н   | Н   | L  | BS | X    | ILLEGAL <sup>2</sup>                     |  |

| Precharge                     | L  | Н   | L   | Н  | BS | X    | ILLEGAL <sup>2</sup>                     |  |

|                               | L  | Н   | L   | L  | X  | X    | ILLEGAL                                  |  |

|                               | L  | L   | Н   | Н  | BS | X    | ILLEGAL <sup>2</sup>                     |  |

|                               | L  | L   | Н   | L  | BS | AP   | ILLEGAL <sup>2</sup>                     |  |

|                               | L  | L   | L   | Х  | Х  | X    | ILLEGAL                                  |  |

| Precharging                   | Н  | Х   | Х   | Х  | X  | X    | NOP;> Idle after tRP                     |  |

|                               | L  | Н   | Н   | Н  | X  | X    | NOP;> Idle after tRP                     |  |

|                               | L  | Н   | Н   | L  | BS | X    | ILLEGAL <sup>2</sup>                     |  |

|                               | L  | Н   | L   | X  | BS | X    | ILLEGAL <sup>2</sup>                     |  |

|                               | L  | L   | Н   | Н  | BS | X    | (0K Provided tRP Satisfied) ACT          |  |

|                               | L  | L   | Н   | L  | BS | AP   | NOP <sup>4</sup>                         |  |

|                               | L  | L   | L   | Х  | Х  | Х    | ILLEGAL                                  |  |

| Row                           | Н  | X   | X   | X  | X  | X    | NOP;> Row Active after tRCD              |  |

| Activating                    | L  | Н   | Н   | Н  | X  | X    | NOP;> Row Active after tRCD              |  |

|                               | L  | Н   | Н   | L  | BS | X    | ILLEGAL <sup>2</sup>                     |  |

|                               | L  | Н   | L   | X  | BS | X    | (0K if tRCD satisfied) Read/Write        |  |

|                               | L  | L   | Н   | Н  | BS | X    | (0K to other Bank if tRRD Satisfied) ACT |  |

|                               | L  | L   | Н   | L  | BS | AP   | Precharge                                |  |

|                               | L  | L   | L   | Х  | X  | X    | ILLEGAL                                  |  |

| Write                         | Н  | X   | Х   | Х  | X  | X    | NOP                                      |  |

| Recovering                    | L  | Н   | Н   | Н  | X  | X    | NOP                                      |  |

|                               | L  | Н   | Н   | L  | BS | X    | ILLEGAL <sup>2</sup>                     |  |

|                               | L  | Н   | L   | X  | BS | X    | ILLEGAL <sup>2</sup>                     |  |

|                               | L  | L   | Н   | Н  | BS | X    | ILLEGAL <sup>2</sup>                     |  |

|                               | L  | L   | Н   | L  | BS | AP   | ILLEGAL <sup>2</sup>                     |  |

|                               | L  | L   | L   | Х  | Х  | X    | ILLEGAL                                  |  |

| Refreshing                    | Н  | X   | X   | X  | ×  | X    | NOP;> Idle after tRC                     |  |

|                               | L  | Н   | Н   | X  | X  | X    | NOP;> Idle after tRC                     |  |

|                               | L  | Н   | L   | X  | X  | X    | ILLEGAL                                  |  |

|                               | L  | L   | Н   | X  | X  | X    | ILLEGAL                                  |  |

|                               | L  | L   | L   | Х  | Х  | Х    | ILLEGAL                                  |  |

| Mode                          | Н  | X   | X   | X  | ×  | X    | NOP                                      |  |

| Register                      | L  | Н   | Н   | Н  | X  | X    | NOP                                      |  |

|                               | L  | Н   | Н   | L  | X  | X    | ILLEGAL                                  |  |

| Accessing                     | L  | H   | L   | X  | X  | X    | ILLEGAL                                  |  |

|                               | L  | L   | Х   | Х  | Х  | Х    | ILLEGAL                                  |  |

### Clock Enable (CKE) Truth Table

| STATE(n)                  | CKE<br>n-1 | CKE<br>n | cs | RAS | CAS | WE | Addr | ACTION                                       |

|---------------------------|------------|----------|----|-----|-----|----|------|----------------------------------------------|

| Self-Refresh <sup>6</sup> | Н          | Х        | Х  | Х   | Х   | Х  | Х    | INVALID                                      |

|                           | L          | Н        | Н  | Х   | X   | Х  | X    | EXIT Self-Refresh, Idle after tRC            |

|                           | L          | Н        | L  | Н   | Н   | Н  | X    | EXIT Self-Refresh, Idle after tRC            |

|                           | L          | Н        | L  | Н   | Н   | L  | Х    | ILLEGAL                                      |

|                           | L          | Н        | L  | Н   | L   | X  | Х    | ILLEGAL                                      |

|                           | L          | Н        | L  | L   | X   | X  | Х    | ILLEGAL                                      |

|                           | L          | L        | X  | X   | X   | X  | X    | NOP (Maintain Self-Refresh)                  |

| Power-Down                | Н          | Х        | Х  | Х   | Х   | Х  | Х    | INVALID                                      |

|                           | L          | Н        | Н  | X   | X   | X  | X    | EXIT Power-Down, > Idle.                     |

|                           | L          | Н        | L  | Н   | Н   | Н  | X    | EXIT Power-Down, > Idle.                     |

|                           | L          | Н        | L  | Н   | Н   | L  | X    | ILLEGAL                                      |

|                           | L          | Н        | L  | Н   | L   | X  | X    | ILLEGAL                                      |

|                           | L          | Н        | L  | L   | X   | X  | X    | ILLEGAL                                      |

|                           | L          | L        | Х  | Х   | Х   | Х  | Х    | NOP (Maintain Low-Power Mode)                |

| All. Banks                | Н          | Н        | Х  | Х   | X   | Х  | Х    | Refer to the function truth table            |

| Idle <sup>7</sup>         | Н          | L        | Н  | X   | X   | X  | X    | Enter Power- Down                            |

|                           | Н          | L        | L  | Н   | Н   | Н  | X    | Enter Power- Down                            |

|                           | Н          | L        | L  | Н   | Н   | L  | X    | ILLEGAL                                      |

|                           | Н          | L        | L  | Н   | L   | X  | X    | ILLEGAL                                      |

|                           | Н          | L        | L  | L   | Н   | X  | X    | ILLEGAL                                      |

|                           | Н          | L        | L  | L   | L   | Н  | X    | Enter Self-Refresh                           |

|                           | Н          | L        | L  | L   | L   | L  | X    | ILLEGAL                                      |

|                           | L          | L        | Х  | Х   | Х   | Х  | Х    | NOP                                          |

| Any State                 | Н          | Н        | Х  | Х   | X   | Х  | х    | Refer to the function truth table            |

| other than                | Н          | L        | Х  | X   | X   | X  | X    | Begin Clock Suspend next cycle <sup>8</sup>  |

| listed above              | L          | Н        | Х  | X   | X   | X  | X    | Exit Clock Suspend next cycle <sup>8</sup> . |

|                           | L          | L        | Х  | Х   | Х   | Х  | Х    | Maintain Clock Suspend.                      |

### Abbreviations:

RA = Row Address BS = Bank Select Address

CA = Column Address AP = Auto Precharge

#### Notes for SDRAM function truth table:

- 1. Current State is state of the bank determined by BS. All entries assume that CKE was active (HIGH) during the preceding clock cycle.

- 2. Illegal to bank in specified state; Function may be legal in the bank indicated by BS, depending on the state of that bank.

- 3. Must satisfy bus contention, bus turn around, and/or write recovery requirements.

- 4. NOP to bank precharging or in Idle state. The precharge bank(s) indicated by BS and AP.

- 5. Illegal if any bank is not ldle.

- 6. CKE Low to High transition will re-enable CLK and other inputs asynchronously. A minimum setup time must be satisfied before any command other than EXIT.

- 7. Power-Down and Self-Refresh can be entered only from the All Banks Idle State.

- 8. Must be legal command as defined in the SDRAM function truth table.

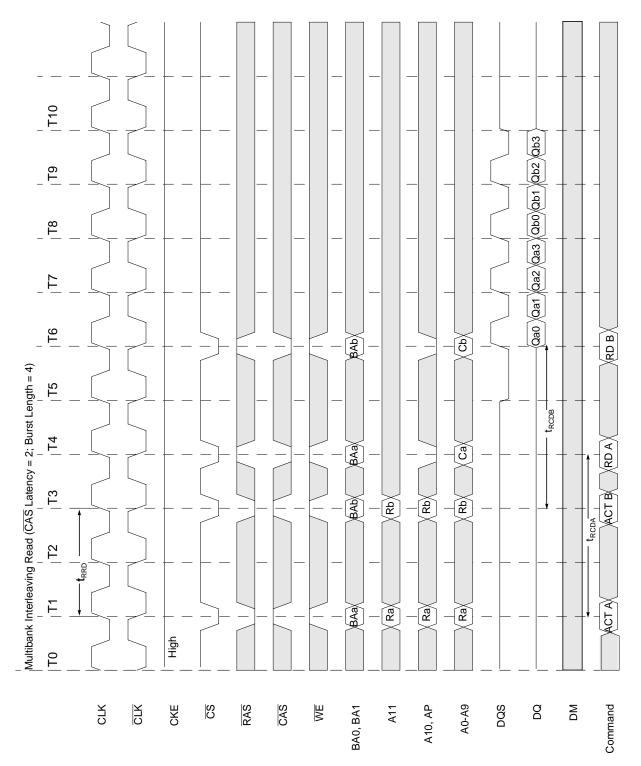

# Multibank Interleaving Read

# Read Interrupted by a Read

# Multi Bank Interleaving Write (@ BL = 4)

# Auto Precharge After Read Burst (@ BL = 8, CL = 2)

# Auto Precharge After Write Burst (@ BL=8)

# Read Interrupted by Precharge (@BL = 8, CL = 2)

# Write Interrupted by a Read (@BL=8, CL=2)

# Write Burst

# Read Interrupted by a Write and Burst Stop

# Data Mask Function (@BL=8) Only for Write

# Power up Sequence and Auto Refresh (CBR)

# Mode Register/Extended Mode Register Set

# Package Diagram 66-Pin TSOP-II (400 mil)

### **MOSEL VITELIC**

### **WORLDWIDE OFFICES**

### V58C265804S

#### U.S.A.

3910 NORTH FIRST STREET SAN JOSE, CA 95134 PHONE: 408-433-6000 FAX: 408-433-0952

#### **HONG KONG**

19 DAI FU STREET TAIPO INDUSTRIAL ESTATE TAIPO, NT, HONG KONG PHONE: 852-2666-3307 FAX: 852-2770-8011

#### **TAIWAN**

7F, NO. 102 MIN-CHUAN E. ROAD, SEC. 3 TAIPEI

PHONE: 886-2-2545-1213 FAX: 886-2-2545-1209

NO 19 LI HSIN RD. SCIENCE BASED IND. PARK HSIN CHU, TAIWAN, R.O.C. PHONE: 886-3-579-5888 FAX: 886-3-566-5888

#### **SINGAPORE**

10 ANSON ROAD #23-13 INTERNATIONAL PLAZA SINGAPORE 079903 PHONE: 65-3231801 FAX: 65-3237013

#### **JAPAN**

WBG MARIVE WEST 25F 6, NAKASE 2-CHOME MIHAMA-KU, CHIBA-SHI CHIBA 261-7125 PHONE: 81-43-299-6000

FAX: 81-43-299-6000

#### **UK & IRELAND**

SUITE 50, GROVEWOOD BUSINESS CENTRE STRATHCLYDE BUSINESS PARK BELLSHILL, LANARKSHIRE, SCOTLAND, ML4 3NQ PHONE: 01698-748515 FAX: 01698-748516

#### GERMANY (CONTINENTAL EUROPE & ISRAEL)

71083 HERRENBERG BENZSTR. 32 GERMANY

PHONE: +49 7032 2796-0 FAX: +49 7032 2796 22

# U.S. SALES OFFICES

#### **NORTHWESTERN**

3910 NORTH FIRST STREET SAN JOSE, CA 95134 PHONE: 408-433-6000 FAX: 408-433-0952

#### **SOUTHWESTERN**

302 N. EL CAMINO REAL #200 SAN CLEMENTE, CA 92672 PHONE: 949-361-7873 FAX: 949-361-7807

#### CENTRAL, NORTHEASTERN & SOUTHEASTERN

604 FIELDWOOD CIRCLE RICHARDSON, TX 75081 PHONE: 972-690-1402 FAX: 972-690-0341

© Copyright 2000, MOSEL VITELIC Inc.

5/0 Printed in U.S.A.

The information in this document is subject to change without notice.

MOSEL VITELIC makes no commitment to update or keep current the information contained in this document. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of MOSEL-VITELIC.

MOSEL VITELIC subjects its products to normal quality control sampling techniques which are intended to provide an assurance of high quality products suitable for usual commercial applications. MOSEL VITELIC does not do testing appropriate to provide 100% product quality assurance and does not assume any liability for consequential or incidental arising from any use of its products. If such products are to be used in applications in which personal injury might occur from failure, purchaser must do its own quality assurance testing appropriate to such applications.