### **Switching Regulator IC for Buck Converter**

w/ 40V/1A MOSFET

#### **■ GENERAL DESCRIPTION**

The **NJW4152** is a buck converter with **40V/1A** MOSFET. It corresponds to high oscillating frequency, and Low ESR Output Capacitor (MLCC) within wide input range from 3.6V to 40V. Therefore, the **NJW4152** can realize downsizing of an application with a few external parts.

Also, it has a soft start function, an over current protection and a thermal shutdown circuit. Moreover there is an automotive for extended operating temperature range version.

It is suitable for logic voltage generation from high voltage that Car Accessory, Office Automation Equipment, Industrial Instrument and so on.

#### ■ PACKAGE OUTLINE

NJW4152GM1-AB

#### **■** FEATURES

Maximum Rating Input Voltage 45V

Wide Operating Voltage Range

Switching Current

3.6V to 40V @AB version

1.4A(min.) @AB version

PWM Control

Wide Oscillating Frequency

300kHz to 1MHz

Soft Start Function

4ms typ.

UVLO (Under Voltage Lockout)

Over Current Protection / Thermal Shutdown Protection

Standby Function

◆ Package Outline

NJW4152GM1: HSOP8

#### ■ PRODUCT CLASSIFICATION

| Status | Part Number      | Version | Output<br>Current | Switching<br>Current Limit<br>(MIN.) | Operating<br>Voltage | Package         | Operating<br>Temperature Range       |

|--------|------------------|---------|-------------------|--------------------------------------|----------------------|-----------------|--------------------------------------|

| MP     | NJW4152GM1-A     | Α       | 1.0A              | 1.4A                                 | 4.6 to 40V           | HSOP8           | General Spec.<br>-40 to +85°C        |

| MP     | NJW4152GM1-A-T   | Α       | 1.0A              | 1.4A                                 | 4.6 to 40V           | HSOP8           | Automotive T Spec.<br>-40 to +105°C  |

| MP     | NJW4152GM1-A-T1  | Α       | 1.0A              | 1.4A                                 | 4.6 to 40V           | HSOP8           | Automotive T1 Spec.<br>-40 to +125°C |

| MP     | NJW4152GM1-AB    | AB      | 1.0A              | 1.4A                                 | 3.6 to 40V           | HSOP8           | General Spec.<br>-40 to +85°C        |

| MP     | NJW4152GM1-AB-T1 | AB      | 1.0A              | 1.4A                                 | 3.6 to 40V           | HSOP8           | Automotive T1 Spec.<br>-40 to +125°C |

| MP     | NJW4152R-B       | В       | 600mA             | 0.8A                                 | 4.6 to 40V           | MSOP8<br>(VSP8) | General Spec.<br>-40 to +85°C        |

| U.D.   | NJW4152R-BA-Z    | BA      | 600mA             | 0.8A                                 | 4.4 to 40V           | MSOP8<br>(VSP8) | Automotive Z Spec.<br>-40 to +125°C  |

This data sheet is applied to "NJW4152GM1-AB".

Please refer to each data sheet for other versions.

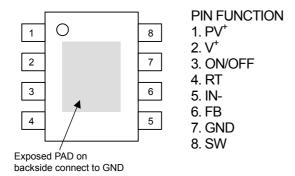

### ■ PIN CONFIGURATION

#### NJW4152GM1-AB

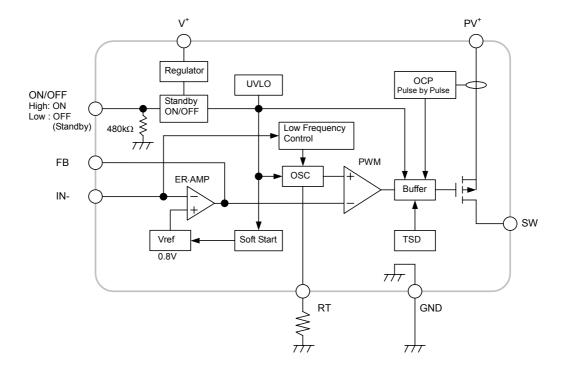

#### ■ BLOCK DIAGRAM

#### ■ ABSOLUTE MAXIMUM RATINGS

(Ta=25°C)

| PARAMETER                                                   | SYMBOL             | MAXIMUM RATINGS              | UNIT |

|-------------------------------------------------------------|--------------------|------------------------------|------|

| Supply Voltage<br>(V <sup>+</sup> pin, PV <sup>+</sup> pin) | V <sup>+</sup>     | +45                          | V    |

| PV⁺- SW pin Voltage                                         | $V_{PV-SW}$        | +45                          | V    |

| IN- pin Voltage                                             | V <sub>IN-</sub>   | -0.3 to +6                   | V    |

| ON/OFF pin Voltage                                          | V <sub>ONOFF</sub> | +45                          | V    |

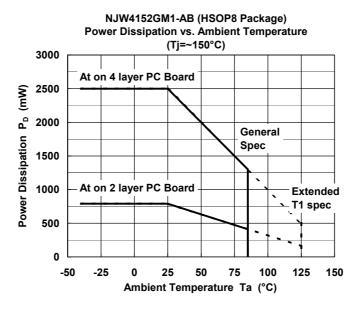

| Power Dissipation                                           | $P_D$              | HSOP8 790 (*1)<br>2,500 (*2) | mW   |

| Junction Temperature Range                                  | Tj                 | -40 to +150                  | °C   |

| Operating Temperature Range                                 | T <sub>opr</sub>   | -40 to +85                   | °C   |

| Storage Temperature Range                                   | T <sub>stg</sub>   | -40 to +150                  | °C   |

<sup>(\*1):</sup> Mounted on glass epoxy board. (76.2×114.3×1.6mm:EIA/JDEC standard size, 2Layers)

internal Cu area: 74.2×74.2mm

#### ■ RECOMMENDED OPERATING CONDITIONS

| PARAMETER             | SYMBOL           | MIN. | TYP. | MAX.  | UNIT |

|-----------------------|------------------|------|------|-------|------|

| Supply Voltage        | V <sup>+</sup>   | 3.6  | _    | 40    | V    |

| Output Current (*3)   | I <sub>OUT</sub> | -    | _    | 1.0   | Α    |

| Timing Resistor       | $R_T$            | 18   | 27   | 68    | kΩ   |

| Oscillating Frequency | fosc             | 300  | 700  | 1,000 | kHz  |

<sup>(\*3):</sup> At Static Status

<sup>(\*2):</sup> Mounted on glass epoxy board. (76.2×114.3×1.6mm:EIA/JDEC standard size, 4Layers),

## **NJW4152-AB**

| PARAMETER                                        | SYMBOL               | TEST CONDITION                                                    | MIN.  | TYP.  | MAX.           | UNI                                   |

|--------------------------------------------------|----------------------|-------------------------------------------------------------------|-------|-------|----------------|---------------------------------------|

|                                                  |                      |                                                                   |       |       |                |                                       |

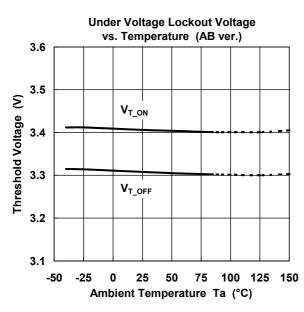

| Under Voltage Lockout Block                      | 1                    | T. 4                                                              |       |       |                |                                       |

| ON Threshold Voltage                             | $V_{T\_ON}$          | $V^{\dagger} = L \rightarrow H$                                   | 3.2   | 3.4   | 3.6            | V                                     |

| OFF Threshold Voltage                            | $V_{T\_OFF}$         | $V^{\dagger} = H \rightarrow L$                                   | 3.1   | 3.3   | 3.5            | V                                     |

| Hysteresis Voltage                               | $V_{HYS}$            |                                                                   | 60    | 100   | _              | mV                                    |

| Soft Start Block                                 |                      |                                                                   |       |       |                |                                       |

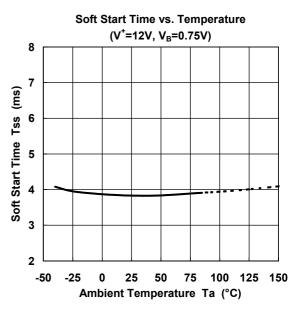

| Soft Start Time                                  | T <sub>SS</sub>      | V <sub>B</sub> =0.75V                                             | 2     | 4     | 8              | ms                                    |

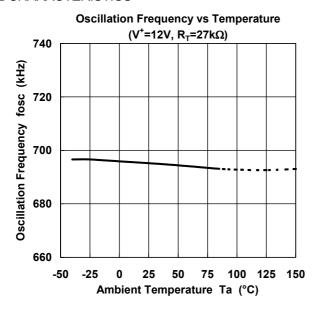

| Oscillator Block                                 |                      |                                                                   |       |       |                |                                       |

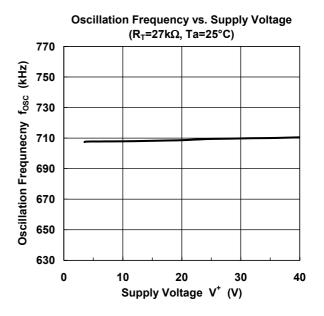

| Oscillation Frequency                            | f <sub>OSC</sub>     |                                                                   | 630   | 700   | 770            | kHz                                   |

| Oscillation Frequency                            |                      | \\ -0.4\\\\ -0.55\\                                               |       |       | -              |                                       |

| (Low Frequency Control)                          | f <sub>OSC_LOW</sub> | V <sub>IN-</sub> =0.4V, V <sub>FB</sub> =0.55V                    | _     | 270   | _              | kHz                                   |

| RT pin Voltage                                   | $V_{RT}$             |                                                                   | 0.24  | 0.275 | 0.31           | V                                     |

| Oscillation Frequency deviation (Supply voltage) | $f_{DV}$             | V <sup>+</sup> =4.6V to 40V                                       | _     | 1     | -              | %                                     |

| Oscillation Frequency deviation                  | f <sub>DT</sub>      | Ta=-40°C to +85°C                                                 | _     | 2     | _              | %                                     |

| (Temperature)                                    | וטי                  | 14 16 6 6 766 6                                                   |       | _     |                | ,,                                    |

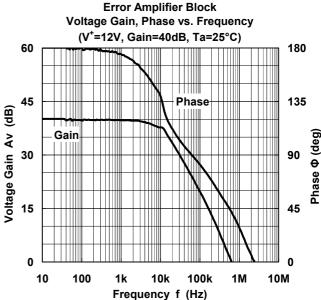

| Error Amplifier Block                            |                      |                                                                   |       |       |                |                                       |

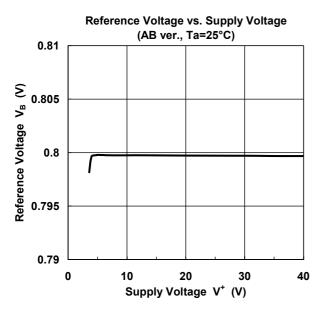

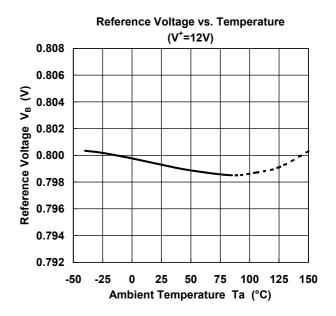

| Reference Voltage                                | $V_B$                |                                                                   | -1.0% | 8.0   | +1.0%          | V                                     |

| Input Bias Current                               | I <sub>B</sub>       |                                                                   | -0.1  | _     | +0.1           | μΑ                                    |

| Open Loop Gain                                   | $A_V$                |                                                                   | _     | 80    | _              | dB                                    |

| Gain Bandwidth                                   | G <sub>B</sub>       |                                                                   | _     | 0.6   | _              | MH:                                   |

| Output Source Current                            | I <sub>OM+</sub>     | V <sub>FB</sub> =1V, V <sub>IN-</sub> =0.7V                       | 8     | 16    | 24             | μΑ                                    |

| Output Sink Current                              | I <sub>OM-</sub>     | V <sub>FB</sub> =1V, V <sub>IN-</sub> =0.9V                       | 1     | 2     | 4              | mA                                    |

| PWM Comparate Block                              |                      |                                                                   |       |       |                |                                       |

| Maximum Duty Cycle                               | $M_{AX}D_{UTY}$      | V <sub>IN-</sub> =0.7V                                            | 100   | _     | _              | %                                     |

| Output Block                                     |                      |                                                                   |       |       |                |                                       |

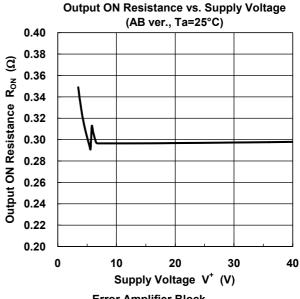

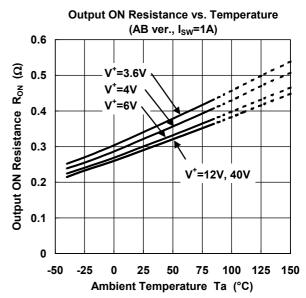

| Output Block Output ON Resistance                | R <sub>oN</sub>      | I <sub>SW</sub> =1A                                               | T _   | 0.3   | 0.5            | Ω                                     |

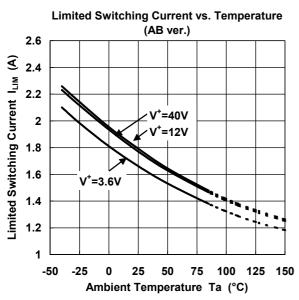

| Switching Current Limit                          | I <sub>LIM</sub>     | ISW-1A                                                            | 1.4   | 1.7   | 2.0            | A                                     |

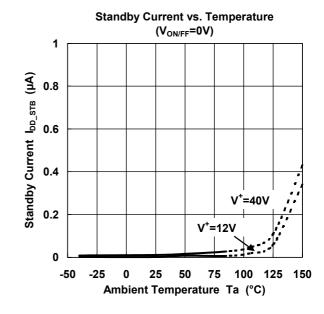

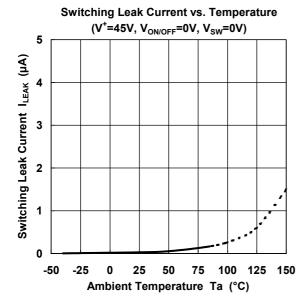

| Switching Leak Current                           | I <sub>LEAK</sub>    | V <sub>ON/OFF</sub> =0V, V <sup>+</sup> =45V, V <sub>SW</sub> =0V | -     | -     | 1              | μA                                    |

| ·                                                | LEAK                 | TOINOFF ST, T 1ST, TSW ST                                         |       |       |                | μ                                     |

| ON/OFF Block                                     | \ \/                 | Tv =1 11                                                          | 1.0   | T     | \ /+           | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| ON Control Voltage                               | V <sub>ON</sub>      | $V_{ONOFF} = L \rightarrow H$                                     | 1.6   | _     | V <sup>+</sup> | V                                     |

| OFF Control Voltage                              | $V_{OFF}$            | $V_{ON/OFF} = H \rightarrow L$                                    | 0     | -     | 0.5            | V                                     |

| Pull-down Resistance                             | $R_{PD}$             |                                                                   | _     | 480   | _              | kΩ                                    |

| General Characteristics                          |                      |                                                                   |       |       |                |                                       |

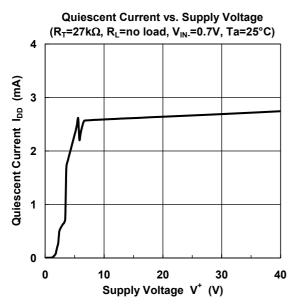

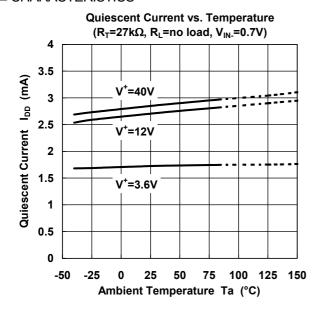

| 0: 10 1                                          |                      | D =no load \/ =0.7\/\/ =0.55\/                                    |       | 2.5   | 2.8            | mΑ                                    |

| Quiescent Current                                | l <sub>DD</sub>      | $R_L$ =no load, $V_{IN-}$ =0.7V, $V_{FB}$ =0.55V                  | _     | 2.5   | 2.0            | 1117                                  |

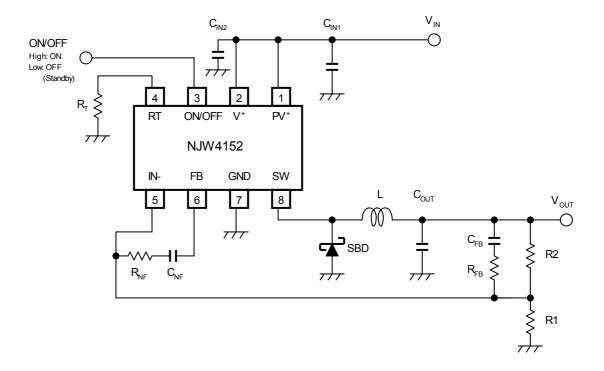

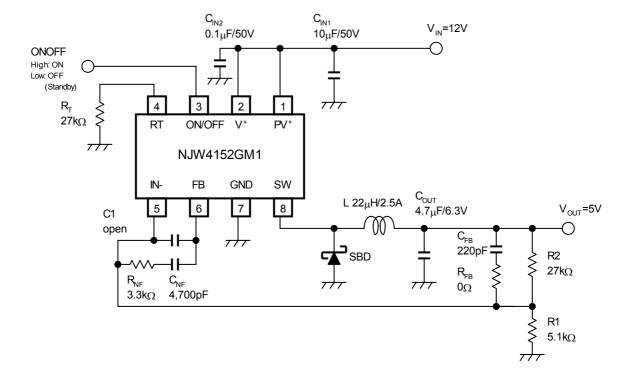

#### ■ TYPICAL APPLICATIONS

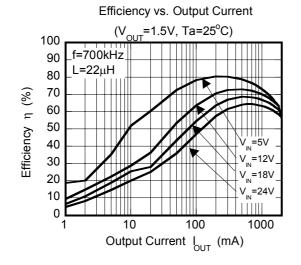

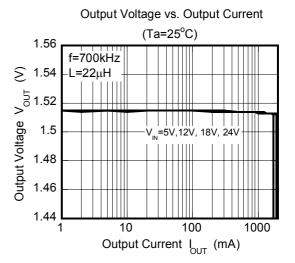

#### **■ CHARACTERISTICS**

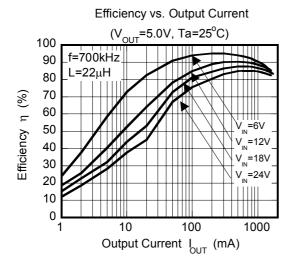

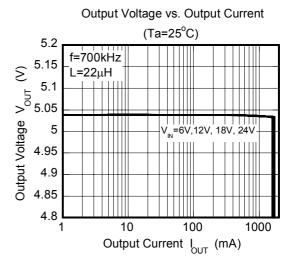

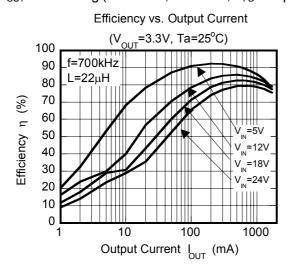

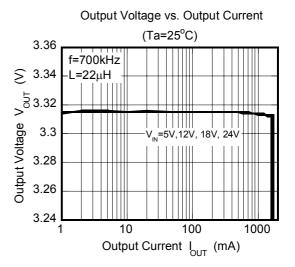

#### **■ CHARACTERISTICS**

#### **■** CHARACTERISTICS

### **Technical Information**

#### ■ PIN DESCRIPTIONS

| PIN<br>NUMBER | PIN NAME       | FUNCTION                                                                                                                                                                       |  |

|---------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1             | $PV^{^{+}}$    | Power Supply pin for Power Line                                                                                                                                                |  |

| 2             | V <sup>+</sup> | Power Supply pin for IC Control                                                                                                                                                |  |

| 3             | ON/OFF         | ON/OFF Control pin The ON/OFF pin internally pulls down with $480 \text{k}\Omega$ . Normal Operation at the time of High Level. Standby Mode at the time of Low Level or OPEN. |  |

| 4             | RT             | Oscillating Frequency Setting pin by Timing Resistor. Oscillating Frequency should set between 300kHz and 1MHz.                                                                |  |

| 5             | IN-            | Output Voltage Detecting pin Connects output voltage through the resistor divider tap to this pin in order to voltage of the IN- pin become 0.8V.                              |  |

| 6             | FB             | Feedback Setting pin The feedback resistor and capacitor are connected between the FB pin and the IN- pin.                                                                     |  |

| 7             | GND            | GND pin                                                                                                                                                                        |  |

| 8             | SW             | Switch Output pin of Power MOSFET                                                                                                                                              |  |

| _             | Exposed PAD    | Connect to GND                                                                                                                                                                 |  |

#### ■ Description of Block Features

- 1. Basic Functions / Features

- Error Amplifier Section (ER-AMP)

0.8V±1% precise reference voltage is connected to the non-inverted input of this section.

To set the output voltage, connects converter's output to inverted input of this section (IN- pin). If requires output voltage over 0.8V, inserts resistor divider.

Because the reference voltage has decreased supply voltage on the operating conditions less than 4V\*, please confirm "Reference voltage vs. Supply voltage" characteristic.

This AMP section has high gain and external feedback pin (FB pin). It is easy to insert a feedback resistor and a capacitor between the FB pin and the IN- pin, making possible to set optimum loop compensation for each type of application. (\* Design value)

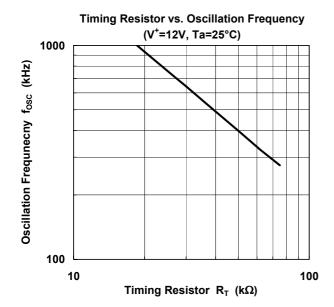

#### Oscillation Circuit Section (OSC)

Oscillation frequency can be set by inserting resistor between the RT pin and GND. Referring to the sample characteristics in "Timing Resistor and Oscillation Frequency", set oscillation between 300kHz and 1MHz.

### **Technical Information**

- Description of Block Features (Continued)

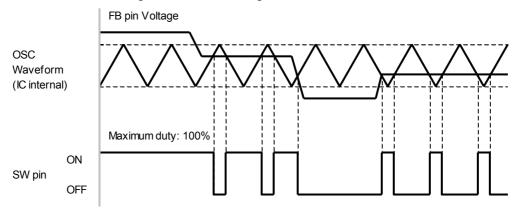

- PWM Comparator Section (PWM)

This section controls the switching duty ratio.

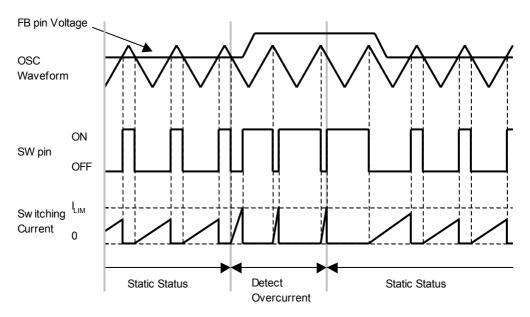

PWM comparator receives the signal of the error amplifier and the triangular wave, and controls the duty ratio between 0% and 100%. The timing chart is shown in Fig.1.

Fig. 1. Timing Chart PWM Comparator and SW pin

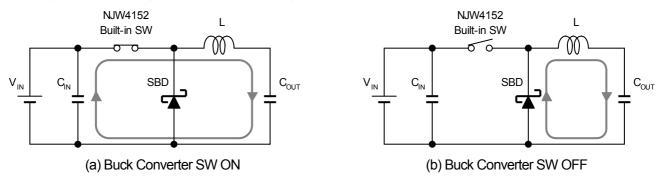

#### Power MOSFET (SW Output Section)

The power is stored in the inductor by the switch operation of built-in power MOSFET. The output current is limited to 1.4A(min.)@AB version by the overcurrent protection function. In case of step-down converter, the forward direction bias voltage is generated with inductance current that flows into the external regenerative diode when MOSFET is turned off.

The SW pin allows voltage between the PV<sup>+</sup> pin and the SW pin up to +45V. However, you should use an Schottky diode that has low saturation voltage.

When the power supply voltage decreases, ON resistance rises. Because a dropout voltage in the MOSFET becomes large if an output current is large, please be careful about input-output differential voltage of the application.

#### Power Supply, GND pin (V<sup>+</sup>, PV<sup>+</sup> and GND)

In line with switching element drive, current flows into the IC according to frequency. If the power supply impedance provided to the power supply circuit is high, it will not be possible to take advantage of IC performance due to input voltage fluctuation. Therefore insert a bypass capacitor close to the  $V^{\dagger}$  pin – the GND pin connection in order to lower high frequency impedance.

### **Technical Information**

#### 2. Additional and Protection Functions / Features

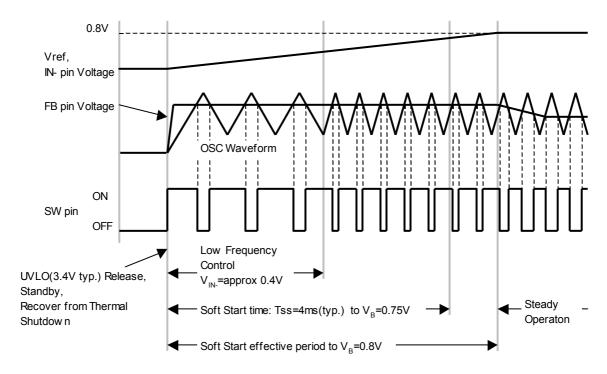

#### Under Voltage Lockout (UVLO)

The UVLO circuit operating is released above  $V^{\dagger}$ =3.4V(typ.) and IC operation starts. When power supply voltage is low, IC does not operate because the UVLO circuit operates. There is 100mV width hysteresis voltage at rise and decay of power supply voltage. Hysteresis prevents the malfunction at the time of UVLO operating and releasing.

#### Soft Start Function (Soft Start)

The output voltage of the converter gradually rises to a set value by the soft start function. The soft start time is 4ms (typ). It is defined with the time of the error amplifier reference voltage becoming from 0V to 0.75V. The soft start circuit operates after the release UVLO and/or recovery from thermal shutdown. The operating frequency is controlled with a low frequency, approximately 40% of the set value by the timing resistor, until voltage of the IN- pin becomes approximately 0.4V.

Fig. 2. Startup Timing Chart

### **Technical Information**

- Description of Block Features (Continued)

- Over Current Protection Circuit (OCP)

At when the switching current becomes  $I_{LIM}$  or more, the overcurrent protection circuit is stopped the MOSFET output. The switching output holds low level down to next pulse output at OCP operating.

The NJW4152 output returns automatically along with release from the over current condition because the OCP is pulse-by-pulse type.

Fig.3. shows the timing chart of the over current protection detection.

If voltage of the IN- pin becomes less than 0.4V, the oscillation frequency decreases to approximately 40% and the energy consumption is suppressed.

Fig. 3. Timing Chart at Over Current Detection

#### Thermal Shutdown Function (TSD)

When Junction temperature of the NJW4152 exceeds the  $175^{\circ}C^{*}$ , internal thermal shutdown circuit function stops SW function. When junction temperature decreases to  $145^{\circ}C^{*}$  or less, SW operation returns with soft start operation.

The purpose of this function is to prevent malfunctioning of IC at the high junction temperature. Therefore it is not something that urges positive use. You should make sure to operate within the junction temperature range rated (150°C). (\* Design value)

#### ON/OFF Function (Standby Control)

The NJW4152 stops the operating and becomes standby status when the ON/OFF pin becomes less than 0.5V. The ON/OFF pin internally pulls down with  $480k\Omega$ , therefore the NJW4152 becomes standby mode when the ON/OFF pin is OPEN. You should connect this pin to V<sup>+</sup> when you do not use ON/OFF function.

### **Technical Information**

#### ■ Application Information

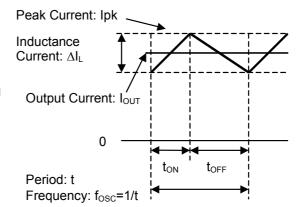

#### Inductors

Large currents flow into inductor, therefore you must provide current capacity that does not saturate.

Reducing L, the size of the inductor can be smaller. However, peak current increases and adversely affecting efficiency.

On the other hand, increasing L, peak current can be reduced at switching time. Therefore conversion efficiency improves, and output ripple voltage reduces. Above a certain level, increasing inductance windings increases loss (copper loss) due to the resistor element.

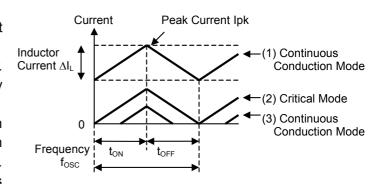

Fig. 4. Inductor Current State Transition

Ideally, the value of L is set so that inductance current is in continuous conduction mode. However, as the load current decreases, the current waveform changes from (1) CCM: Continuous Conduction Mode  $\rightarrow$  (2) Critical Mode  $\rightarrow$  (3) DCM: Discontinuous Conduction Mode (Fig. 4.).

In discontinuous mode, peak current increases with respect to output current, and conversion efficiency tend to decrease. Depending on the situation, increase L to widen the load current area to maintain continuous mode.

If the application needs maximum output current, the inductor ripple current should be set less than 20% to prevent operating the over current protection circuit at the minimum switching limiting current.

#### Catch Diode

When the switch element is in OFF cycle, power stored in the inductor flows via the catch diode to the output capacitor. Therefore during each cycle current flows to the diode in response to load current. Because diode's forward saturation voltage and current accumulation cause power loss, a Schottky Barrier Diode (SBD), which has a low forward saturation voltage, is ideal.

An SBD also has a short reverse recovery time. If the reverse recovery time is long, through current flows when the switching transistor transitions from OFF cycle to ON cycle. This current may lower efficiency and affect such factors as noise generation.

#### Input Capacitor

Transient current flows into the input section of a switching regulator responsive to frequency. If the power supply impedance provided to the power supply circuit is large, it will not be possible to take advantage of the NJW4152 performance due to input voltage fluctuation. Therefore insert an input capacitor as close to the MOSFET as possible.

#### Output Capacitor

An output capacitor stores power from the inductor, and stabilizes voltage provided to the output.

When selecting an output capacitor, you must consider Equivalent Series Resistance (ESR) characteristics, ripple current, and breakdown voltage.

Also, the ambient temperature affects capacitors, decreasing capacitance and increasing ESR (at low temperature), and decreasing lifetime (at high temperature). Concerning capacitor rating, it is advisable to allow sufficient margin.

Output capacitor ESR characteristics have a major influence on output ripple noise. A capacitor with low ESR can further reduce ripple voltage. Be sure to note the following points; when ceramic capacitor is used, the capacitance value decreases with DC voltage applied to the capacitor.

### **Technical Information**

- Application Information (Continued)

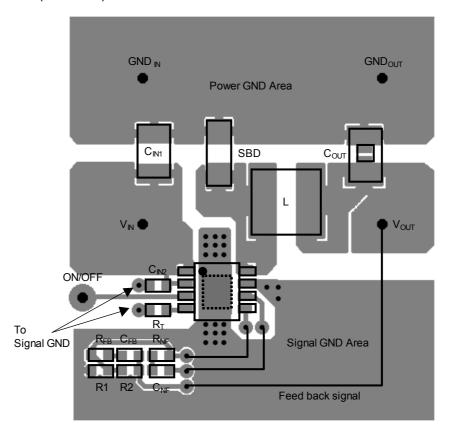

- Board Layout

In the switching regulator application, because the current flow corresponds to the oscillation frequency, the substrate (PCB) layout becomes an important.

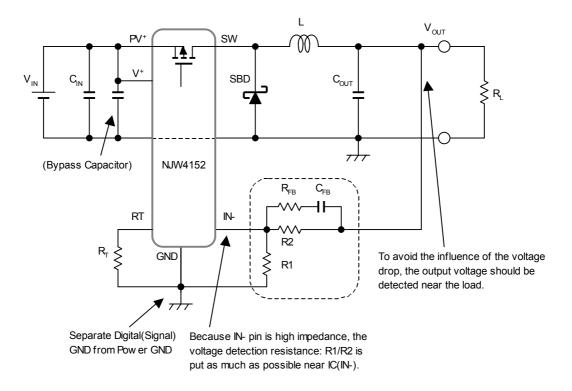

You should attempt the transition voltage decrease by making a current loop area minimize as much as possible. Therefore, you should make a current flowing line thick and short as much as possible. Fig.5. shows a current loop at step-down converter. Especially, should lay out high priority the loop of  $C_{IN}$ -SW-SBD that occurs rapid current change in the switching. It is effective in reducing noise spikes caused by parasitic inductance.

Fig. 5. Current Loop at Buck Converter

Concerning the GND line, it is preferred to separate the power system and the signal system, and use single ground point.

The voltage sensing feedback line should be as far away as possible from the inductance. Because this line has high impedance, it is laid out to avoid the influence noise caused by flux leaked from the inductance.

Fig. 6. shows example of wiring at buck converter. Fig. 7 shows the PCB layout example.

Fig. 6. Board Layout at Buck Converter

## **Technical Information**

■ Application Information (Continued)

Connect Signal GND line and Power GND line on backside pattern

Fig. 7 Layout Example (upper view)

### **Technical Information**

#### ■ Calculation of Package Power

A lot of the power consumption of buck converter occurs from the internal switching element (Power MOSFET). Power consumption of NJW4152 is roughly estimated as follows.

Input Power:  $P_{IN} = V_{IN} \times I_{IN} \quad [W]$  Output Power:  $P_{OUT} = V_{OUT} \times I_{OUT} \quad [W]$

Diode Loss:  $P_{DIODE} = V_F \times I_{L(avg)} \times OFF \text{ duty } [W]$ NJW4152 Power Consumption:  $P_{LOSS} = P_{IN} - P_{OUT} - P_{DIODE}$  [W]

#### Where:

OFF duty : Switch OFF Duty

Efficiency  $(\eta)$  is calculated as follows.

$$\eta = (P_{OUT} \div P_{IN}) \times 100 \, [\%]$$

You should consider temperature derating to the calculated power consumption: PD.

You should design power consumption in rated range referring to the power dissipation vs. ambient temperature characteristics (Fig. 8).

Mounted on glass epoxy board. (76.2×114.3×1.6mm:EIA/JDEC standard size, 2Layers)

Mounted on glass epoxy board. (76.2×114.3×1.6mm:EIA/JDEC standard size, 4Layers),

internal Cu area: 74.2×74.2mm

Fig. 8. Power Dissipation vs. Ambient Temperature Characteristics

## **Technical Information**

#### ■ Application Design Examples

Step-Down Application Circuit

$\begin{array}{lll} IC & : NJW4152GM1 \\ Input Voltage & : V_{IN} = 12V \\ Output Voltage & : V_{OUT} = 5V \\ Output Current & : I_{OUT} = 1A \\ Oscillation frequency & : fosc = 700kHz \end{array}$

Output Ripple Voltage : V<sub>ripple(P-P)</sub>=less than 20mV

| Reference          | Qty. | Part Number       | Description                                       | Manufacturer |

|--------------------|------|-------------------|---------------------------------------------------|--------------|

| IC                 | 1    | NJW4152GM1        | Internal 1A MOSFET SW.REG. IC                     | New JRC      |

| L                  | 1    | CDRH8D28HPNP-220N | Inductor 22μH,<br>2.5A(Ta=20°C) / 1.9A (Ta=100°C) | Sumida       |

| D                  | 1    | CMS11             | Schottky Diode 40V, 2A                            | Toshiba      |

| C <sub>IN1</sub>   | 1    | UMK325BJ106MM     | Ceramic Capacitor 3225 10µF, 50V, X5R             | Taiyo Yuden  |

| C <sub>IN2</sub>   | 1    | 0.1μF             | Ceramic Capacitor 1608 0.1µF, 50V, B              | Std.         |

| C <sub>OUT</sub>   | 1    | JMK212ABJ475KG    | Ceramic Capacitor 2012 4.7µF, 6.3V, X5R           | Taiyo Yuden  |

| C <sub>NF</sub>    | 1    | 4,700pF           | Ceramic Capacitor 1608 4,700pF, 50V, B            | Std.         |

| $C_{FB}$           | 1    | 220pF             | Ceramic Capacitor 1608 220pF, 50V, CH             | Std.         |

| C1                 | 0    | —(Optional)       | Optional                                          |              |

| R1                 | 1    | 5.1kΩ             | Resistor 1608 5.1kΩ, ±1%, 0.1W                    | Std.         |

| R2, R <sub>T</sub> | 2    | 27kΩ              | Resistor 1608 27kΩ, ±1%, 0.1W                     | Std.         |

| R <sub>NF</sub>    | 1    | 3.3kΩ             | Resistor 1608 3.3kΩ, ±5%, 0.1W                    | Std.         |

| R <sub>FB</sub>    | 1    | 0Ω (Short)        | Resistor 1608 0Ω, 0.1W                            | Std.         |

### **Technical Information**

- Application Design Examples (Continued)

- Setting Oscillation Frequency

From the Oscillation frequency vs. Timing Resistor Characteristic,  $R_T$ =27 [ $k\Omega$ ], t=1.43[ $\mu$ s] at fosc=700kHz.

Step-down converter duty ratio is shown with the following equation.

$$Duty = \frac{V_{OUT} + V_F}{V_{IN}} \times 100 = \frac{5 + 0.4}{12} \times 100 = 45 \, [\%]$$

Therefore,  $t_{ON}$ =0.64 [ $\mu$ s],  $t_{OFF}$ =0.79 [ $\mu$ s]

Fig. 9. Inductor Current Waveform

#### Selecting Inductance

To assume maximum output current: 1A, and the inductor ripple current should be set not to exceed the minimum switching limiting current: I<sub>LIM</sub>=1.4A (min.).

$\Delta IL$  is Inductance ripple current. When to  $\Delta IL$  = output current 20%:

$$\Delta I_L = 0.2 \times I_{OUT} = 0.2 \times 1 = 0.2 [A]$$

This obtains inductance L. V<sub>DS RON</sub> is drop voltage by MOSFET on resistance.

$$L = \frac{V_{{\scriptscriptstyle IN}} - V_{{\scriptscriptstyle DS-RON}} - V_{{\scriptscriptstyle OUT}}}{\Delta I_{{\scriptscriptstyle L}}} \times t_{{\scriptscriptstyle ON}} = \frac{12 - 0.5 - 5}{0.2} \times 0.64 \, \mu = 20.8 \, \text{[} \, \mu \text{H]} \, \Rightarrow \text{22[} \, \mu \text{H]}$$

Inductance L is a theoretical value. The optimum value varies according such factors as application specifications and components. Fine-tuning should be done on the actual device.

This obtains the peak current lpk at switching time.

$$Ipk = I_{OUT} + \frac{\Delta I_L}{2} = 1 + \frac{0.2}{2} = 1.1[A]$$

The current that flows into the inductance provides sufficient margin for peak current at switching time. In the application circuit, use L= $22\mu$ H, 2.5A(Ta= $20^{\circ}$ C) / 1.9A (Ta= $100^{\circ}$ C).

### **Technical Information**

#### ■ Application Design Examples (Continued)

#### Selecting the Input Capacitor

The input capacitor corresponds to the input of the power supply. It is required to adequately reduce the impedance of the power supply. The input capacitor selection should be determined by the input ripple current and the maximum input voltage of the capacitor rather than its capacitance value.

The effective input current can be expressed by the following formula.

$$I_{\mathit{RMS}} = I_{\mathit{OUT}} \times \frac{\sqrt{V_{\mathit{OUT}} \times \left(V_{\mathit{IN}} - V_{\mathit{OUT}}\right)}}{V_{\mathit{IN}}} \left[A\right]$$

In the above formula, the maximum current is obtained when  $V_{IN}$  = 2 ×  $V_{OUT}$ , and the result in this case is  $I_{RMS} = I_{OUT(MAX)} \div 2$ .

When selecting the input capacitor, carry out an evaluation based on the application, and use a capacitor that has adequate margin.

#### Selecting the Output Capacitor

The output capacitor is an important component that determines output ripple noise. Equivalent Series Resistance (ESR), ripple current, and capacitor breakdown voltage are important in determining the output capacitor.

The output ripple noise can be expressed by the following formula.

$$ESR = \frac{V_{ripple(p-p)}}{\Delta I_L}$$

When selecting output capacitance, select a capacitor that allows for sufficient ripple current. The effective ripple current that flows in a capacitor ( $I_{rms}$ ) is obtained by the following equation.

$$I_{rms} = \frac{\Delta I_L}{2\sqrt{3}} = \frac{0.2}{2\sqrt{3}} = 58 [mArms]$$

Consider sufficient margin, and use a capacitor that fulfills the above spec.

In the application circuit, use  $C_{OUT}$ =4.7 $\mu$ F/6.3V.

#### Setting Output Voltage

The output voltage  $V_{OUT}$  is determined by the relative resistances of R1, R2. The current that flows in R1, R2 must be a value that can ignore the bias current that flows in ER AMP.

$$V_{OUT} = \left(\frac{R2}{R1} + 1\right) \times V_B = \left(\frac{27k}{5.1k} + 1\right) \times 0.8 = 5.04 [V]$$

### **Technical Information**

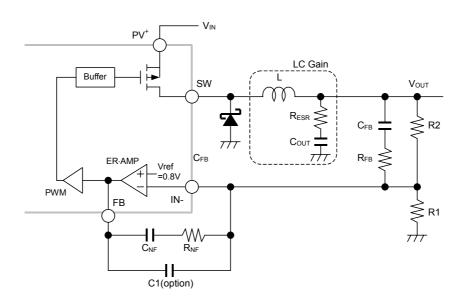

#### ■ Compensation design example

A switching regulator requires a feedback circuit for acquiring a stable output. Because the frequency characteristics of the application change according to the inductance, output capacitor, and so on, the compensation constant should ideally be determined in such a way that the maximum band is acquired while the necessary phase for stable operation is maintained.

These compensation constants play an important role in the adjustment of the NJW4152 when mounted in an actual unit. Finally, select the constants while performing measurement, in consideration of the application specifications.

Basically, the feedback loop should be designed in such a way that the open loop phase shift at the point where the loop gain is 0 dB is less than -180°. It is also important that the loop characteristics have margin in consideration of ringing and immunity to oscillation during load fluctuations. With the NJW4152, the feedback circuit can be freely designed, enabling the arrangement of the poles and zeros which is important for loop compensation, to be optimized.

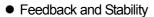

Pole

The characteristics of the poles and zeros are shown in Fig. 10.

Poles: The gain has a slope of -20 dB/dec, and the phase shifts -90°.

Zeros: The gain has a slope of +20 dB/dec, and the phase shift +90°.

Fig. 10. Characteristics of Pole and Zero

If the number of factors constituting poles is defined as "n", the change in the gain and phase will be "n"-fold. This also applies to zeros as well. The poles and zeros are in a reciprocal relationship, so if there is one factor for each pole and zero, they will cancel each other.

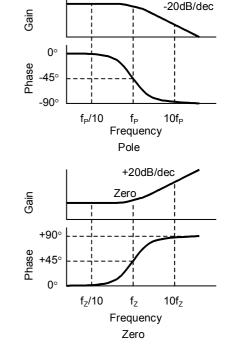

#### Configuration of the compensation circuit

Fig. 11. Compensation Circuit Configuration

### **Technical Information**

- Compensation Design (Continued)

- Poles and zeros due to the inductance and output capacitor

Double poles  $f_{P(LC)}$  are generated by the inductance and output capacitor. Simultaneously, single zeros  $f_{Z(ESR)}$  are generated by the output capacitor and ESR. Each pole and zero is expressed by the following formula.

$$f_{Z(ESR)} = \frac{1}{2\pi C_{OUT} R_{ESR}} \qquad \qquad f_{P(LC)} = \frac{1}{2\pi \sqrt{LC_{OUT}}} \label{eq:fz}$$

If the ESR of the output capacitor is high,  $f_{Z(ESR)}$  will be located in the vicinity of  $f_{P(LC)}$ . In an application such as this, the zero  $f_{Z(ESR)}$  compensates the double poles  $f_{P(LC)}$ , resulting in a tendency for stability to be readily maintained.

However, if the ESR of the output capacitor is low,  $f_{Z(ESR)}$  shifts to the high region, and the phase is shifted -180° by  $f_{P(LC)}$ . The NJW4152 compensation circuit enables compensation to be realized by using zeros  $f_{Z1}$  and  $f_{Z2}$ .

#### Poles and zeros due to error amplifier

The single poles and zeros generated by the error amplifier are obtained using the following formula.

| Zero                                    | Pole                                                                          |

|-----------------------------------------|-------------------------------------------------------------------------------|

| $f_{Z1} = \frac{1}{2\pi C_{NF} R_{NF}}$ | $f_{P1} = \frac{1}{2\pi C_{NF} A_{V} \left(\frac{R1R2}{R1 + R2}\right)}$      |

|                                         | (Av: Amplifier Open Loop Gain=80dB)                                           |

| $f_{Z2} = \frac{1}{2\pi C_{FB}R2}$      | $f_{P2} = \frac{1}{2\pi C_{FB} \left( R_{FB} + \frac{R1R2}{R1 + R2} \right)}$ |

|                                         | $f_{P3} = \frac{1}{2\pi C1R_{NF}}$ (Option)                                   |

$f_{Z1}$  and  $f_{Z2}$  are located on both sides of  $f_{P(LC)}$ .

Because the inductance and output capacitor vary, they are each set using the following as a rough guide.

$$f_{P(LC)} \times 0.5$$

-fold — 0.9-fold  $f_{P(LC)} \times 1.1$ -fold — 2.0-fold

Fig12. Loop Gain examples

There is also a method in which  $f_{Z1}$  and  $f_{Z2}$  are located at positions lower than even  $f_{P(LC)}$ . Because there is a tendency for the phase shift to increase and the gain to rise, it can be expected that the response will improve.

However, there is a tendency for the phase margin to become insufficient, so care is necessary.

$f_{P1}$  creates poles in the low frequency region due to the Miller effect of the error amplifier. The stability becomes better as  $f_{P1}$  becomes lower. On the other hand, the frequency characteristics do not improve, so the response is adversely affected.  $f_{P1}$  is set using a frequency gain of 20 dB for  $f_{P(LC)}$  as a rough guide.

If the open loop gain of the error amplifier is made 80 dB, design is carried out using  $f_{P1} < f_{P(LC)} \div 10^3$  (= 60 dB) as a rough guide.

Above several 100 kHz, various poles are generated, so the upper limit of the frequency range where the loop gain is 0 dB is set to fifth (1/5) to tenth (1/10) of oscillation frequency. The  $f_{Z(ESR)}$  in the high frequency region sometimes causes a loop gain to be generated (See Fig.12 Loop Gain "). Using  $f_{P2}$  and  $f_{P3}$ , perform adjustment with the NJW4152 mounted in an actual unit, so as to adequately reduce the loop gain in the high frequency region.

## **Technical Information**

- ■Application Characteristics: NJW4152GM1-A

- At  $V_{OUT}$ =5.0V setting (R1=5.1k $\Omega$ , R2=27k $\Omega$ , C<sub>FB</sub>=220pF, R<sub>FB</sub>=0 $\Omega$ )

• At  $V_{OUT}$ =3.3V setting (R1=5.1k $\Omega$ , R2=16k $\Omega$ ,  $C_{FB}$ =220pF,  $R_{FB}$ =0 $\Omega$ )

• At  $V_{OUT}$ =1.5V setting (R1=30k $\Omega$ , R2=27k $\Omega$ , C<sub>FB</sub>=220pF, R<sub>FB</sub>=10k $\Omega$ )

## **MEMO**

[CAUTION]

The specifications on this databook are only given for information, without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.