UM83C002

# RAM Buffer Controller

#### Features

- 3 DMA channels

- Host processor port

- Refresh circuit for dynamic RAM built-in

- RAM access priority network

- Address multiplexing for dynamic RAM

- Multiplexed address and data lines from processor

- Pins arranged for easy integration into 8088/8086 systems

- No lost RAM cycles for DMA break-in

- DMA carry output permits DMA across 64K boundaries

- 24 bit timer or baud rate generator

- TTL compatible inputs and outputs. Outputs drive 8 LSTTL loads

# **General Description**

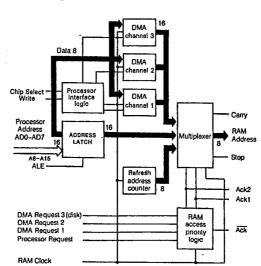

The RAM BUFFER CONTROLLER contains three high-speed DMA channels: a host computer address port, dynamic RAM refresh circuitry, and RAM access priority logic. One of the DMA address counters points inside the buffer RAM for transferring data between the RAM and the disk. A refresh address counter handles dynamic RAM refreshing. Also on chip is an address multiplexer.

The DISK CONTROLLER UM83C001 connects to one of the RAM controller chip's DMA channels. The two other DMA channels may be used by other

high-speed memory-peripheral drives or tape systems — if the chip set is being used with its own on-board processor.

When teamed with the UM83C001, the UM83C002 gives the disk direct access to a buffer RAM array. What's more, it does so at a speed high enough to accommodate 5 Mbit, 10 Mbit and 15 Mbit data transfer rates. The new ST412HP interface, for instance, which operates at 10 Mbits with MFM encoding, would have a 15 Mbit throughput if it employed RLL2, 7 encoding instead.

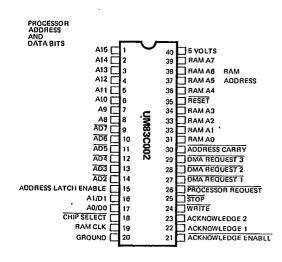

# **Pin Configuration**

# **Block Diagram**

# Absolute Maximum Ratings\*

# Power Supply Voltage, $V_{DD}$ . . . . . -0.5 to +7.0 V Input Voltage, $V_1$ . . . . . -0.5 V to $V_{DD}$ + 0.5 V Operating Temperature, $T_{OPT}$ . . . . -40 to +85° C Storage Temperature, $T_{STG}$ . . . . . -65 to +150° C

## \*Comments

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied and exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# Recommended Operating Conditions

| Parameter                   | 0                               | ·    | Limits |                 | Units | Test Conditions |

|-----------------------------|---------------------------------|------|--------|-----------------|-------|-----------------|

|                             | Symbol                          | Min. | Тур.   | Max.            | Onta  | Test Conditions |

| Power<br>Supply Voltage     | V <sub>DD</sub>                 | 4.5  | 5      | 5.5             | ٧     |                 |

| Input Voltage               | V <sub>I</sub>                  | 0    |        | V <sub>DD</sub> | ٧     |                 |

| Low-Level<br>Input Voltage  | V <sub>IL</sub>                 | 0    |        | 0.8             | ٧     | TTL Level*      |

| High-Level<br>Input Voltage | V <sub>IH</sub>                 | 2.0  |        | V <sub>DD</sub> | v.    | TTL Level*      |

| Input Rise<br>Fall Times    | t <sub>R</sub> , t <sub>F</sub> |      |        | 10              | μS    |                 |

Note:  $(T_A = 0 \text{ to } +70^{\circ}\text{C}, V_{DD} = 5 \text{ V} + 5\% \text{ unless otherwise specified})$

## **DC** Electrical Characteristics

| _                            | Parameter Symbol Limits Units  Min: Typ. Max. |                      | Limits |              | I Inite | Test Conditions                         |

|------------------------------|-----------------------------------------------|----------------------|--------|--------------|---------|-----------------------------------------|

| Parameter                    |                                               |                      |        | ,500,500,600 |         |                                         |

| Static Current               | ال                                            |                      | 0,1    | 200          | μΑ      | V <sub>I</sub> = V <sub>DD</sub> or GND |

| Dynamic Current              | I <sub>DD</sub>                               |                      | 4      |              | μΑ      | 1 MHz/cell                              |

| Input Current                | l <sub>1</sub>                                |                      | 0,1    | 10           | μΑ      | V <sub>I</sub> = V <sub>DD</sub> or GND |

| Low-Level<br>Output Current  | l <sub>OL</sub>                               | 3.2                  | 9      |              | mA      | V <sub>OL</sub> = 0.4 V                 |

| High-Level<br>Output Current | l <sub>oH</sub>                               | 1                    | 3      |              | mA      | $V_{OH} = (V_{DD} - 0.4) V$             |

| Low-Level<br>Output Voltage  | V <sub>OL</sub>                               |                      |        | 0.1          | ٧       | 1 <sub>0</sub> = 0                      |

| High-Level<br>Output Voltage | V <sub>OH</sub>                               | V <sub>DD</sub> =0.1 |        |              | ٧       | l <sub>O</sub> = 0                      |

# UM83C002

# **AC Characteristics**

| Parameter                         | Symbol           |            | Limits |      | Units | Tark Orandistan        |

|-----------------------------------|------------------|------------|--------|------|-------|------------------------|

| , digitiaral                      | Symbol           | Min.       | Тур.   | Max. | Units | Test Conditions        |

| Maximum<br>Operating<br>Frequency | f <sub>MAX</sub> | DC         |        | 50   | MHz   |                        |

| Output<br>Rise Time               | t <sub>R</sub>   | ·········· | 8      |      | ns    | C <sub>L</sub> = 15 pF |

| Output<br>Fall Time               | t <sub>F</sub>   |            | 4      |      | ns    | C <sub>L</sub> = 15 pF |

# Pin Description

| Pin No.                  | Symbol                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|--------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1 THRU 14,<br>16, AND 17 | PROCESSOR ADDRESS<br>AND'DATA BITS | These 16 pins are time multiplexed to provide a 16 bit CPU Addres and an 8 bit CPU data bus to the UM83C001                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| 15                       | ADDRESS LATCH<br>ENABLE<br>(ALE)   | When the ADDRESS LATCH ENABLE signal is high, the address on the AD0 to AD15 lines is enabled into the ADDRESS LATCH in the UM83C002. When the ALE signal goes low, this address is held in the latch to be used for addressing the RAM. After ALE goes low, data may be placed on the AD0 to AD7 lines.                                                                                                                                                                                                                                |  |  |  |  |  |

| 18                       | CHIP SELECT (CSEL)                 | The CHIP SELECT lines are driven low by the processor to read from or write to the registers inside the UM83C002. This signal is not intended to be gated by the processor's acknowledge signal. When the processor does a read of registers within the UM83C002, the read data will be held on the data lines until the CSEL line goes back high.                                                                                                                                                                                      |  |  |  |  |  |

| 19                       | RAM CLOCK                          | This line is an input that serves two purposes. It provides the timing for multiplexing the RAS and CAS addresses to the dynamic RAM and its trailing or rising edge provides the clock to define all memory cycles. When this line is high the RAS addresses are output at RAM A0 to RAM A7. When it is low, the CAS addresses are output at RAM A0 to RAM A7.  The input lines REQ1, REQ2, REQ3 and REQH are sampled at the rising edge of this clock to determine who will be granted access to memory during the next memory cycle. |  |  |  |  |  |

| 20                       | GROUND                             | Negative supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| 21                       | ACKNOWLEDGE<br>ENABLE              | A low on this line indicates that one of the REQUEST lines has been granted access to RAM. The REQUEST lines are sampled on the rising edge of RAM CLOCK                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 22                       | ACKNOWLEDGE 1                      | When the ACKNOWLEDGE ACK ACK2 ACK1 Request Granted line is low, these two lines L H H REQUEST 3                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 23                       | ACKNOWLEDGE 2                      | are encoded to indicate which request has been granted access to RAM,  L H L REQUEST 2  L L H REQUEST 1  L L CPU REQUEST                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

# Pin Description (Continued)

| Pin No. | Symbol            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24      | WRITE (WRT)       | This line indicates whether a read or a write is to be performed. A low indicates a write and a high indicates a read. During processor cycles, it is driven by the processor. During DMA cycles, it is normally driven by the UM83C002. However, the UM 83C002 may be programmed to allow the I/O device to drive this line. During unused cycles and refresh cycles, the UM83C002 drives this line high to eliminate the need for an external pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 25      | STOP              | This line goes low to indicate the last cycle of a DMA transfer. It is normally driven low by the UM83C002 when the byte counter of the active DMA channel has reached zero. The DMA channel becomes disabled after this last cycle and it will ignore any further requests until it has been restarted by writing to its command register. Each channel can be programmed to allow the external I/O device to drive this line. However, internal byte counts are always active so that transfer will stop when \$\overline{STOP}\$ goes low or when the byte count reaches zero, whichever comes first. This line is driven by the UM83C002 during unused cycles (cycles during which \$\overline{ACKNOWLEDGE}\$ is high). It is normally driven low. However, a refresh cycle is indicated when \$\overline{STOP}\$ \$\overline{ACKNOWLEDGE}\$ and \$\overline{WRITE}\$ are high at the same time. A timer cycle is indicated by \$\overline{WRITE}\$ being low when \$\overline{ACKNOWLEDGE}\$ and \$\overline{STOP}\$ are high. |

| 26      | PROCESSOR REQUEST | The processor requests access to RAM by placing a low on this line. This line is sampled by the rising edge of the RAM CLOCK. The processor has lowest priority. It will be granted access to RAM only if all three DMA requests are HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 27      | DMA REQUEST 1     | This is the lowest priority DMA REQUEST. It samples on the rising edge of RAM CLOCK. DMA CHANNEL 1 will be granted access to RAM, If DMA REQUEST 2 and DMA REQUEST 3 are high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 28      | DMA REQUEST 2     | This is the middle priority DMA REQUEST. This channel will be granted access to RAM only if DMA REQUEST 3 is high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 29      | DMA REQUEST 3     | This is the highest priority DMA REQUEST. If this line is low when the rising edge of RAM CLOCK occurs, DMA CHANNEL 3 will control the next memory cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 30      | ADDRESS CARRY     | This output goes low to indicate that the memory address of the DMA channel that is acknowledged is at its maximum count of 65,535 and will roll over to O at the end of this memory cycle. This line also goes low on a refresh cycle when the refresh address counter is at its maximum count of 255. This line also goes low on a timer cycle when the timer is at its maximum count.  When operating in the address decrement mode, that line goes low to indicate that the DMA channel address is OOOO and this it is going to roll over to FFFF at the end of the current memory cycle.  This line is provided so that DMA transfers can be performed across 64K boundaries if desired. This line would be used to increment an external counter containing the higher order address bits. This line can also be used to increment additional external refresh address counter bits if more than 8 bits of refresh address are required. This line can also be used to extend the timer beyond 24 bits.                       |

# Pin Description (Continued)

| Pin No.            | Symbol                    | Description                                                                                                                                                                                                                                                                                                                                          |

|--------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31 ~ 34<br>36 ~ 39 | A0 ~ A3<br>A4 ~ A7<br>RAM | These are the multiplexed address lines for use with dynamic RAMS. When RAM CLOCK is high, address bits 8 thru 15 are gated to these lines. When RAM CLOCK is low, address bits 0 thru 7 are gated to these lines. During REFRESH cycles, the refresh address is gated to these lines. During TIMER cycles, the timer count is gated to these lines. |

| 35                 | RESET                     | A low on this RESET line resets the UM83C002 to its initial state. The refresh rate is set to maximum refresh every other memory cycle and all three DMA channels are disabled.                                                                                                                                                                      |

| 40.                | +5 VOLTS                  | Positive supply,                                                                                                                                                                                                                                                                                                                                     |

# **RAM BUS Operation**

A combination of pin signals control the BUS OPERATION to and from the UM83C002 chip. These combinations are shown in Table 1.

| CARRY | STOP | CSEL | WRITE | ACK | ACK2 | ACK1 | RAM BUS Operation      |

|-------|------|------|-------|-----|------|------|------------------------|

| X     | Х    | Н    | L     | L   | Ł    | Ļ    | CPU WRITE TO MEM/IO    |

| X     | ×    | Н    | H     | L   | L    | L    | CPU READ FROM MEM/IO   |

| ×     | ×    | L    | L     | L   | L    | L    | CPU WRITE TO UM83C002  |

| X     | X    | L    | н     | L   | L    | L    | CPU READ FROM UM83C002 |

| ×     | ×    | x    | L     | L   | L    | н    | CH 1 WRITE TO MEMORY   |

| ×     | ×    | X    | Н     | L   | L    | н    | CH 1 READ FROM MEMORY  |

| L     | X    | Х    | ×     | L   | L    | н    | CH 1 ADDRESS CARRY     |

| X     | L    | X    | X     | L   | L.   | Н    | CH 1 STOP TRANSFER     |

| ×     | ×    | ×    | L     | L   | н    | L    | CH 2 WRITE TO MEMORY   |

| ×     | l ×  | ×    | н     | Ļ   | н    | L,   | CH 2 READ FROM MEMORY  |

| L     | ×    | ×    | ×     | L   | Н    | L    | CH 2 ADDRESS CARRY     |

| X     | L    | X    | ×     | L   | н    | Ľ    | CH 2 STOP TRANSFER     |

| ×     | ×    | ×    | L     | Ĺ   | н    | Н    | CH 3 WRITE TO MEMORY   |

| l ×   | ×    | ×    | Н     | L   | н    | H    | CH 3 READ FROM MEMORY  |

| L     | x    | ×    | l x   | L   | H    | н    | CH 3 ADDRESS CARRY     |

| X     | L    | ×    | ×     | L   | н    | н    | CH 3 STOP TRANSFER     |

| ×     | Н    | ×    | L     | н   | ×    | ×    | TIMER COUNT ON BUS     |

| L     | н    | . X  | L     | н   | X    | Х    | TIMER COUNT CARRY      |

| x     | Н    | ×    | н     | н   | ×    | ×    | REFRESH ADDRESS ON BUS |

| Ļ     | Н    | ×    | Н     | Н   | ×    | ×    | REFRESH ADDRESS CARRY  |

| ×     | L    | ×    | ×     | н   | X .  | ×    | INACTIVE BUS CYCLE     |

H = HIGH

L = LOW

X = DON'T CARE

Table 1. Signal Combinations

# Register Addressing

The UMC RAM BUFFER CONTROLLER, UM83C002, occupies 2 I/O port locations selected by the ADO pin. ADO driven low selects the REGISTER ADDRESS/STATUS REGISTER and ADO driven high selects the DATA register.

There are 16 internal registers in the UM83C002. These registers are accessed by writing the register address into the REGISTER ADDRESS register. The selected register can then be accessed by doing a READ or WRITE with ADO high.

|        | {                                    | Read                                                                                                  | . Write                                                                                          |

|--------|--------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

|        | BIT                                  | STATUS                                                                                                | REGISTER ADDRESS                                                                                 |

| AO = 0 | 7<br>6<br>5<br>4<br>3<br>2<br>1<br>0 | CHANNEL 3 ACTIVE CHANNEL 2 ACTIVE CHANNEL 1 ACTIVE TIMER ACTIVE , AUTO-INCREMENT REG A2 REG A1 REG A0 | O<br>O<br>CHANNEL NO. BIT 1<br>CHANNEL NO. BIT 0<br>AUTO-INCREMENT<br>REG A2<br>REG A1<br>REG A0 |

|        | BIT                                  | REGISTER DATA                                                                                         | REGISTER DATA                                                                                    |

| A0 = 1 | 7<br>6<br>5<br>4<br>3<br>2<br>1      | D7<br>D6<br>D5<br>D4<br>D3<br>D2<br>D1<br>D0                                                          | D7<br>D6<br>D5<br>D4<br>D3<br>D2<br>D1<br>D0                                                     |

Table 2. Register Addressing

# The following is a list of the WRITE and READ addresses:

| Register<br>Address<br>Decimal                                                    | HEX                                                      | Auto<br>INCR<br>HEX                                                          | Function                                    | Read                                                          | Write                                               |

|-----------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------|

| 0<br>1<br>2<br>3<br>4<br>16<br>17<br>18<br>19<br>20<br>32<br>33<br>34<br>35<br>36 | 00<br>01<br>02<br>03<br>04<br>10<br>11<br>12<br>13<br>14 | 08<br>09<br>0A<br>0B<br>0C*<br>18<br>19<br>1A<br>1B<br>1C*<br>29<br>2A<br>2B | TIMER/REFRESH  DMA CHANNEL 1  DMA CHANNEL 2 | BYTE C<br>CH 1 STATUS<br>ADDRES<br>ADDRES<br>BYTE C<br>BYTE C | S HI<br>OUNT LO<br>OUNT HI<br>CH 1 COMMAND<br>SS LO |

| 36<br>48<br>'49<br>50<br>51<br>52                                                 | 23<br>24<br>30<br>31<br>32<br>33<br>34                   | 2C*<br>38<br>39<br>3A<br>3B<br>3C*                                           | DMA CHANNEL 3                               | ADDRES<br>ADDRES<br>BYTE O                                    | SS LO<br>SS HI<br>OUNT LO<br>OUNT HI                |

<sup>\*</sup> These addresses do not auto-increment.

Table 3. Register Addresses

# Write Register Addresses

## (HEX 00) CLK DIVIDER LO (AUTO INCR HEX 08)

The timer consists of a 16-bit variable CLOCK DIVIDER which divides the RAM CLOCK rate. The divided down RAM CLOCK is then used to increment the 8-bit TIMER COUNT register.

#### (HEX 01) CLK DIVIDER HI (AUTO INCR HEX 09)

To divide by "N", the 16 bit CLOCK DIVIDER is set to N-1.

## (HEX 02) TIMER CONTROL (AUTO INCR HEX OA)

Writing to this address sets one of several timer modes.

BIT 7 = ENABLE TIMER

- 1 = Timer Run

- 0 = Timer Hold

#### BIT 6 = OUTPUT ON INCREMENT

- 1 = Timer Byte Output to Bus When it Increments

- 0 = Timer Byte not Output on Increment

## BIT 5 = OUTPUT ON CARRY

- 1 = Timer Byte Output to Bus When it Rolls over to 0

- 0 = Timer Byte Not Output on Roll Over

#### BIT 4 = STOP AT CARRY

- 1 = Timer Stops When it Rolls Over

- 0 = Timer Does Not Stop When it Rolls Over

BIT 3 = 0

BIT 2 = 0

BIT 1 = 0

BIT 0 = 0

## (HEX 03) TIMER COUNT (AUTO INCR HEX OB)

Writing to this address sets the initial value of the TIMER COUNT. It also initializes the CLOCK DIVIDER.

# (HEX 04) REFRESH RATE (AUTO INCR HEX 00)

An 8-bit register is provided for the setting of the refresh rate. Setting this register to 01 will cause refresh cycles to be inserted at the maximum rate which is one cycle. Setting this register to 00 will cause refresh to be disabled.

#### (HEX XX) ADDRESS LO (AUTO INCR HEX XX)

(HEX 10) = Channel 1 (AUTO INCR HEX 18)

(HEX 20) = Channel 2 (AUTO INCR HEX 28)

(HEX 30) = Channel 3 (AUTO INCR HEX 38)

Low byte of the initial value for the DMA ADDRESS

## (HEX XX) ADDRESS HI (AUTO INCR HEX XX)

(HEX 11) = Channel 1 (AUTO INCR HEX 19)

(HEX 21) = Channel 2 (AUTO INCR HEX 29)

(HEX 31) = Channel 3 (AUTO INCR HEX 39)

High byte of the initial value for DMA ADDRESS

## (HEX XX) BYTE COUNT LO (AUTO INCR HEX XX)

(HEX 12) = Channel 1 (AUTO INCR HEX 1A)

(HEX 22) = Channel 2 (AUTO INCR HEX 2A)

(HEX 32) = Channel 3 (AUTO INCR HEX 3A)

Low byte of the initial value for the BYTE COUNT for the transfer. Set this to N-1 to transfer N bytes.

#### (HEX XX) BYTE COUNT HI (AUTO INCR HEX XX)

(HEX 13) = Channel 1 (AUTO INCR HEX 1C)

(HEX 23) = Channel 2 (AUTO INCR HEX 2C)

(HEX 33) = Channel 3 (AUTO INCR HEX 3C)

High byte for the initial value for the BYTE COUNT

# (HEX XX) COMMAND (AUTO INCR HEX XX)

(HEX 14) = Channel 1 (AUTO INCR HEX 1D)

(HEX 24) = Channel 2 (AUTO INCR HEX 2D)

(HEX 34) = Channel 3 (AUTO INCR HEX 3D)

Writing to these addresses STARTS, STOPS or CONTINUES the DMA operation.

## BIT 7 = ENABLE CHANNEL

- 1 = Enable Channel to Respond to DMA Request

- 0 = Disable Channel so it Ignores DMA Request

# BIT 6 = INITIALIZE ADDRESS

- 1 = Set Address to Initial Value

- 0 = Leave Address at Previous Value

#### BIT 5 = INITIALIZE COUNT

- 1 = Set Count to Initial Value

- 0 = Leave Count at Previous Value

### BIT 4 = AUTO INITIALIZE

- 1 = Address and Byte Count Are Reset to Initial Values When Byte Count Reaches Zero. DMA Operation Continues

- 0 = DMA Operation Stops When Byte Count Reaches Zero.

#### BIT 3 = WRITE TO MEMORY

- 1 = DMA Write to Memory

- 0 = DMA Read from Memory

#### BIT 2 = EXTERNAL STOP

- 1 = Stop Line is Driven from External Source

- 0 = RB1002 Drives Stop Line

# BIT 1 = EXTERNAL WRITE CONTROL

- 1 = Write Line is An Input for This Channel

- 0 = RB1002 Drives Write Line

#### BIT 0 = ADDRESS INCREMENT MODE:

- 1 = Increment Address after Every DMA Read Or .

Write

- 0 = Decrement Address after Every DMA Read Or Write

# Read Registers Addresses

## (HEX 00) TIMER COUNT (AUTO INCR HEX 08)

Current value of the TIMER COUNT.

# (HEX 01) CH 1 STATUS (AUTO INCR HEX 09)

SEE WRITE UP AT READ ADDRESS 14

# (HEX 02) CH 2 STATUS (AUTO INCR HEX 0A)

SEE WRITE UP AT READ ADDRESS 24

#### (HEX 03) CH 3 STATUS (AUTO INCR HEX 0B)

SEE WRITE UP AT READ ADDRESS 34

### (HEX 04) TIMER COUNT (AUTO INCR HEX 00)

Current value of the TIMER COUNT

# (HEX XX) ADDRESS LO (AUTO INCR HEX XX)

- (HEX 10) = Channel 1 (AUTO INCR HEX 18)

- (HEX 20) = Channel 2 (AUTO INCR HEX 28)

- (HEX 30) = Channel 3 (AUTO INCR HEX 38)

Current address low byte

# (HEX XX) ADDRESS HI (AUTO INCR HEX XX)

- (HEX 11) = Channel 1 (AUTO INCR HEX 19)

- (HEX 21) = Channel 2 (AUTO INCR HEX 29)

- (HEX 31) = Channel 3 (AUTO INCR HEX 39)

Current address high byte

### (HEX XX) BYTE COUNT LO (AUTO INCR HEX XX)

(HEX 12) = Channel 1 (AUTO INCR HEX 1A)

(HEX 22) = Channel 2 (AUTO INCR HEX 2A)

(HEX 32) = Channel 3 (AUTO INCR HEX 3A)

**Current BYTE COUNT**

#### (HEX XX) BYTE COUNT HI (AUTO INCR HEX XX)

(HEX 13) = Channel 1 (AUTO INCR HEX 1B)

(HEX 23) = Channel 2 (AUTO INCR HEX 2B)

(HEX 33) = Channel 3 (AUTO (NCR HEX 3B)

Current BYTE COUNT

#### (HEX XX) STATUS (AUTO INCR HEX XX)

(HEX 14) = Channel 1 (AUTO INCR HEX 1C)

(HEX 24) = Channel 2 (AUTO INCR HEX 2C)

(HEX 34) = Channel 3 (AUTO INCR HEX 3C)

The following STATUS information is also available at READ addresses 01, 02 and 03  $\,$

#### BIT 7 = CHANNEL ENABLE

- 1 = Channel is Enabled

- 0 = Channel is Disabled

#### BIT 6 = ADDRESS CARRY

- 1 = Address is at FFFF if Counting up; Address is at OOOO if Counting down

- 0 = Not at Carry

## BIT 5 = TERMINAL COUNT

- 1 = Byte Count is at Zero

- 0 = Byte Count is Not Zero

## BIT 4 = AUTO.INITIALIZE

- 1 = Auto Initialize Mode

- 0 = Stop at Terminal Count

# BIT 3 = WRITE TO MEMORY

- 1 = DMA Write to Memory Mode

- 0 = DMA Read from Memory Mode

# BIT 2 = EXTERNAL STOP

- 1 = Stop is Input

- 0 = Stop is Output

## BIT 1 = EXTERNAL WRITE CONTROL

- 1 = Write is Externally Controlled

- 0 = Write is Internally Controlled

## BIT 0 = ADDRESS INCREMENT MODE

- 1 = Address Counts up

- 0 = Address Counts down

Storage

UM83C002

# **Dynamic RAM Refresh**

The UM83C002 has built-in refresh circuitry for dynamic RAMs, It provides 8 bits of refresh address so that dynamic RAMs up to 256 K bits can be accommodated,

An 8 bit register is also provided for the setting of the refresh rate. Setting this register to 01 will cause refresh cycles to be inserted at the maximum rate which is one cycle out of two. Activating the RESET line also sets the refresh to its maximum rate. Setting this register to 255 will cause one refresh cycle to be inserted for every 256 memory cycles. Setting this register to 00 will cause refresh to be disabled.

The refresh cycles are inserted into otherwise unused memory cycles whenever possible to maximize system performance. For example: If the rate register is set to 255 and there are any unused cycles during the first 255 cycles of the refresh period, the refresh will be inserted into the first of them and it will be totally invisible to the rest of the system.

During a refresh cycle, the ACKNOWLEDGE, STOP and WRITE lines will be high simultaneously. The refresh address will be on the MAO to MA7 lines. If the refresh address is at hexadecimal FF, then the CARRY line will also be low.

# **Timing Specifications**

This section is devoted to the timings of signals and their relationship to each other in order to make the maximum use of the UM83C002. The following tables and diagrams are to be used as design tools when incorporating the UM83C002 into your system.

| Signal | Min. | Тур. | Max. | Units |

|--------|------|------|------|-------|

| MCLK   |      | 1Ò   | 20   | MHZ   |

Table 4. Clock Frequency

| Signal | LO  | HI | Units |

|--------|-----|----|-------|

| MCLK   | 20  | 30 | ns    |

| ALE    |     | 20 | ns    |

| RESET  | 100 |    | ns    |

Table 5. Signal Widths

| Delays<br>From                   | то                | Тур. | Max. | Units |

|----------------------------------|-------------------|------|------|-------|

|                                  | WRITE             | 35   | 70   | ns    |

|                                  | STOP              | 35   | 69   | ns    |

| MCLK HI                          | CARRY             | 37   | 73   | пѕ    |

| MOEKTH                           | ACK1, ACK2        | 26   | 52   | ns    |

|                                  | ACK               | 29   | 57   | ns    |

|                                  | MAO TO MA7        | 40   | 80   | ns    |

| MCLK LO                          | МАО ТО МА7        | 39   | 78   | ns    |

| CSEL LO &<br>WRT HI &<br>MCLK LO | AD0-AD7<br>ACTIVE | 36   | 72   | ns    |

Table 6. Delays

| Set-Up and Hold Times     | Set-<br>Up | то      | Hold | Units |

|---------------------------|------------|---------|------|-------|

| REQ3, REQ2,<br>REQ1, REQH | 15         | MCLK HI | 15   | ns    |

| WRITE                     | 15         | MCLK LO |      | ns    |

| WRITE                     |            | MCLK HI | 15   | ns    |

| CHIP SELECT               | 15         | MCLK LO |      | ns    |

| CHIP SELECT               |            | MCLK HI | 15   | ns    |

| AO                        | 15         | MCLK LO |      | ns    |

| AO,                       |            | MCLK HI | 15   | ns    |

| STOP                      | 15         | мськ ні | 10   | ns    |

Table 7. Set-Up and Hold Times