## LND-SP64HV

# 32MHZ, 64 CHANNEL SERIAL TO PARALLEL CONVERTER WITH PUSH-PULL OUTPUTS

### **Features**

- ♦ HVCMOS<sup>®</sup> Technology

- ♦ 5.0V CMOS Logic

- ◆ Output voltage up to +90V

- Low power level shifting

- ♦ 32MHz equivalent data rate

- Latched data outputs

- Forward and reverse shifting options (DIR pin)

- ◆ Diode to V<sub>PP</sub> allows efficient power recovery

- Outputs may be hot switched

- Hi-Rel processing available

## **General Description**

The LND-SP64HV is a low voltage serial to high voltage parallel converter with push-pull outputs. The device has been designed for use as a driver for EL displays. It can also be used in any application requiring multiple output high voltage current sourcing and sinking capability such

as driving plasma panels, vacuum fluorescent displays, or large matrix LCD displays.

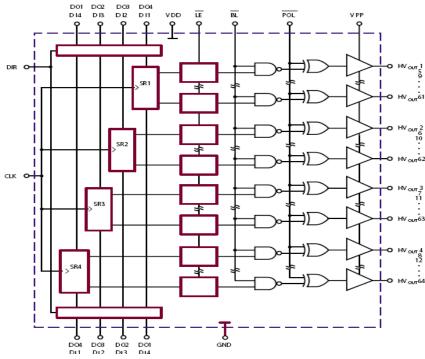

The device has 4 parallel 16-bit registers, permitting data rates 4x the speed of one (they are clocked together). There are also 64 latches and control logic to perform the polarity select and blanking of the outputs. HV<sub>OUT</sub>1 is connected to the first stage of the first shift register through the polarity and blanking logic. Data is shifted through the shift registers on the logic low to high transition of the clock. The DIR pin causes CCW shifting when connected to GND, and CW shifting when connected to V<sub>DD</sub>. A data output buffer is provided for cascading devices. This output reflects the current status of the last bit of the shift register (HV<sub>OUT</sub>64). Operation of the shift register is not affected by the  $\overline{LE}$  (latch enable), BL (blanking), or the POL (polarity) inputs. Transfer of data from the shift registers to the latches occurs when the LE input is high. The data in the latches is stored when the  $\overline{LE}$  is low.

## **Functional Block Diagram**

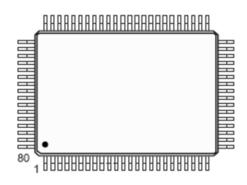

## **Ordering Information**

|            | Package Options                     |  |  |

|------------|-------------------------------------|--|--|

| Device     | 80-Lead PQFP                        |  |  |

|            | 20.00 <i>x</i> 14.00 <i>mm body</i> |  |  |

|            | 3.40mm height (max)                 |  |  |

|            | 0.80mm pitch                        |  |  |

| LND-SP64HV | LND-SP64HV-PG-G                     |  |  |

<sup>-</sup>G indicates package is ROHS compliant ('Green')

# **Absolute Maximum Ratings**

| Parameter                                       | Value                          |  |  |

|-------------------------------------------------|--------------------------------|--|--|

| Supply voltage, V <sub>DD</sub>                 | -0.5V to +5.5V                 |  |  |

| Output voltage, V <sub>PP</sub>                 | -0.5V to +90V                  |  |  |

| Logic input levels                              | -0.3V to V <sub>DD</sub> +0.3V |  |  |

| Ground current <sup>1</sup>                     | 1.5A                           |  |  |

| Continuous total power dissipation <sup>2</sup> | 1200mW                         |  |  |

| Operating temperature range                     | -40°C to +85°C                 |  |  |

| Storage temperature range                       | -65°C to 150°C                 |  |  |

| Lead temperature <sup>3</sup>                   | 260°C                          |  |  |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground.

#### Notes:

- 1. Limited by the total power dissipated in the package

- For operation above 25°C ambient derate linearly to maximum operating temperature at 20mW/°C.

- 3. 1.6mm(1/16inch) from case for 10 seconds

# **Recommended Operating conditions**

| Sym              | Parameter                      | Min                   | Max | Units |

|------------------|--------------------------------|-----------------------|-----|-------|

| $V_{DD}$         | Logic supply voltage           | 4.5                   | 5.5 | V     |

| $V_{PP}$         | Output voltage                 | 8.0                   | 90  | V     |

| $V_{IH}$         | High-level input voltage       | V <sub>DD</sub> -0.5V | ı   | V     |

| $V_{IL}$         | Low-level input voltage        | 0                     | 0.5 | V     |

| f <sub>CLK</sub> | Clock frequency per register   | _                     | 8.0 | MHz   |

| T <sub>A</sub>   | Operating free-air temperature | -40                   | +85 | °C    |

### Notes:

## Power-up sequence should be the following:

- 1. Apply ground.

- 2. Apply V<sub>DD</sub>.

- 3. Set all inputs ( $D_{IN}$ , CLK, Enable, etc.) to a known state.

- Apply V<sub>PP</sub>.

- 5. The  $V_{PP}$  should not drop below  $V_{DD}$  or float during operation.

#### Power-down sequence should be the reverse of the above

## **Pin Configuration**

80-Lead PQFP (PG)

(top view)

## **DC Electrical Characteristics**

| Sym             | Param                                       | neter             | Min                  | Max  | Units | Conditions                                             |

|-----------------|---------------------------------------------|-------------------|----------------------|------|-------|--------------------------------------------------------|

| I <sub>DD</sub> | V <sub>DD</sub> supply current              |                   | _                    | 15   | mA    | $V_{\rm DD} = V_{\rm DD}$ max, $f_{\rm CLK} = 8.0$ MHz |

|                 | I <sub>PP</sub> High voltage supply current |                   | _                    | 100  | μΑ    | Outputs high                                           |

| Ірр             |                                             |                   | _                    | 100  | μΑ    | Outputs low                                            |

| $I_{DDQ}$       | Quiescent V <sub>DD</sub> sup               | ply current       | _                    | 100  | μΑ    | $AIIV_{IN}=V_{DD}$                                     |

| $V_{OH}$        | High level output                           | HV <sub>OUT</sub> | 75                   | _    | V     | $I_0 = -15 \text{mA}, V_{PP} = +90 \text{V}$           |

|                 |                                             | Data out          | V <sub>DD</sub> -0.5 | _    | V     | $I_{O} = -100\mu A$                                    |

| $V_{OL}$        | Low level output                            | HV <sub>OUT</sub> | _                    | 7.0  | V     | $I_0 = 12 \text{mA}, V_{PP} = +90 \text{V}$            |

|                 |                                             | Data out          | _                    | 0.5  | V     | $I_0 = 100 \mu A$                                      |

| I <sub>IH</sub> | High-level logic input current              |                   | _                    | 1.0  | μΑ    | $V_{IH} = V_{DD}$                                      |

| I <sub>IL</sub> | Low-level logic input current               |                   | _                    | -1.0 | μΑ    | $V_{IL} = 0V$                                          |

| $V_{OC}$        | High voltage clamp diode                    |                   | _                    | 1.0  | V     | $I_{OC} = 1.0 \text{mA}$                               |

## **AC Electrical Characteristics** ( $T_A = 85^{\circ}$ C max, Logic signals and Data inputs have $t_r$ , $t_i \le 5$ ns[10% and 90% points]).

| Symbol             | Parameter                                              | Min | Max | Units | Conditions    |

|--------------------|--------------------------------------------------------|-----|-----|-------|---------------|

| f <sub>CLK</sub>   | Clock frequency                                        | -   | 8.0 | MHz   | Per register  |

| $t_{WL}, t_{WH}$   | Clock width high or low                                | 62  | _   | ns    |               |

| t <sub>SU</sub>    | Data set-up time before clock rises                    | 10  | _   | ns    |               |

| t <sub>H</sub>     | Data hold time after clock rises                       | 15  | _   | ns    |               |

| $t_{ON}, t_{OFF}$  | Time from latch enable to HV <sub>OUT</sub>            | _   | 200 | ns    | $C_L = 15 pF$ |

| t <sub>DHL</sub>   | Delay time clock to data high to low                   | _   | 70  | ns    | $C_L = 15 pF$ |

| t <sub>DLH</sub>   | Delay time clock to data low to high                   | _   | 70  | ns    | $C_L = 15pF$  |

| t <sub>DLE</sub> * | Delay time clock to $\overline{\text{LE}}$ low to high | 25  | _   | ns    |               |

| t <sub>WLE</sub>   | LE pulse widthOutput Turn-off Delay                    | 25  | _   | ns    |               |

| t <sub>SLE</sub>   | LE set-up time before clock rises                      | 0   | _   | ns    |               |

<sup>\*</sup> t<sub>DLE</sub> is not required but is recommended to produce stable HV outputs and thus minimize power dissipation and current spikes (allows internal SR output to stabilize)

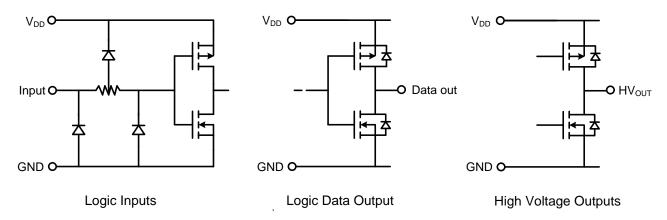

# **Input and Output Equivalent Circuits**