# ±15 kV ESD-Protected, 3.3 V,12 Mbps, EIA RS-485/RS-422 Transceiver

**ADM3485E**

#### **FEATURES**

TIA/EIA RS-485/RS-422 compliant

±15 kV ESD protection on RS-485 input/output pins

12 Mbps data rate

Half-duplex transceiver

Up to 32 nodes on the bus

Receiver open-circuit, fail-safe design

Low power shutdown current

Outputs high-Z when disabled or powered off

Common-mode input range: –7 V to +12 V

Thermal shutdown and short-circuit protection

Industry-standard 75176 pinout

8-lead narrow SOIC package

#### **APPLICATIONS**

Power/energy metering Telecommunications EMI-sensitive systems Industrial control Local area networks

#### **GENERAL DESCRIPTION**

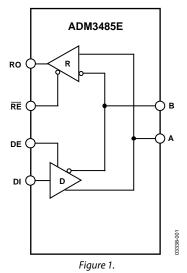

The ADM3485E is a 3.3 V, low power data transceiver with  $\pm 15$  kV ESD protection, suitable for half-duplex communication on multipoint bus transmission lines. The ADM3485E is designed for balanced data transmission and complies with TIA/EIA standards RS-485 and RS-422. The ADM3485E is a half-duplex transceiver that shares differential lines and has separate enable inputs for the driver and the receiver.

The devices have a 12 k $\Omega$  receiver input impedance, which allows up to 32 transceivers on a bus. Because only one driver

#### FUNCTIONAL BLOCK DIAGRAM

should be enabled at any time, the output of a disabled or powered-down driver is tristated to avoid overloading the bus.

The receiver has a fail-safe feature that ensures a logic high output when the inputs are floating. Excessive power dissipation caused by bus contention or by output shorting is prevented with a thermal shutdown circuit.

The part is fully specified over the industrial temperature range and is available in an 8-lead narrow SOIC package.

### **TABLE OF CONTENTS**

5/00—Rev. 0 to Rev. A

| Features1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Applications1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Functional Block Diagram1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| General Description1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Revision History2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Timing Specifications4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Absolute Maximum Ratings5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Thermal Resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ESD Caution5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Pin Configuration and Pin Function Descriptions6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| REVISION HISTORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 8/10—Rev. C to Rev. D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Changes to Table 1, Driver, Logic Inputs 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 12/06—Rev. B to Rev. C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Updated Format       Universal         Removed PDIP Model       Universal         Changes to Features, Applications, and General Description       1         Changes to Specifications       3         Changes to Timing Specifications       4         Changes to Absolute Maximum Ratings       5         Reorganized Test Circuits and Switching       7         Characteristics Section       7         Replaced Figure 3 to Figure 11       7         Deleted Figure 12 to Figure 20       9         Changes to Figure 21 and Figure 22       10         Changes to Table 9       11         Deleted Figure 24       11         Removed Fast Transient Burst Immunity       12         Updated Outline Dimensions       13         Changes to Ordering Guide       13 |

| 10/04—Rev. A to Rev. B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Updated FormatUniversal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Opdated Format         Universal           Changes to Power-Supply Current, Table 1         3           Updated Outline Dimensions         14           Changes to Ordering Guide         14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Test Circuits and Switching Characteristics | 7  |

|---------------------------------------------|----|

| Typical Performance Characteristics         | 9  |

| Standards and Testing                       | 11 |

| ESD Testing                                 | 11 |

| Applications Information                    | 12 |

| Differential Data Transmission              | 12 |

| Cable and Data Rate                         | 12 |

| Receiver Open-Circuit Fail-Safe             | 12 |

| Outline Dimensions                          | 13 |

| Ordering Guide                              | 13 |

### **SPECIFICATIONS**

$V_{\text{CC}}$  = +3.3 V  $\pm$  0.3 V. All specifications  $T_{\text{MIN}}$  to  $T_{\text{MAX}},$  unless otherwise noted.

Table 1.

| Parameter                                                      | Symbol                 | Min              | Тур   | Max  | Unit | Test Conditions/Comments                                                                                      |

|----------------------------------------------------------------|------------------------|------------------|-------|------|------|---------------------------------------------------------------------------------------------------------------|

| DRIVER                                                         |                        |                  |       |      |      |                                                                                                               |

| Differential Outputs                                           |                        |                  |       |      |      |                                                                                                               |

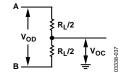

| Differential Output Voltage                                    | $V_{\text{OD}}$        | 2.0              |       |      | V    | $R_L = 100 \Omega$ (RS-422) (see Figure 3)                                                                    |

|                                                                |                        | 1.5              |       |      | V    | $R_L = 54 \Omega$ (RS-485) (see Figure 3)                                                                     |

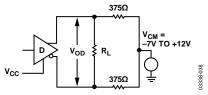

|                                                                |                        | 1.5              |       |      | V    | $R_L = 60 \Omega$ (RS-485) (see Figure 4)                                                                     |

| $\Delta  V_{OD} $ for Complementary Output States <sup>1</sup> | $\Delta V_{\text{OD}}$ |                  |       | 0.2  | V    | $R_L = 54 \Omega$ or $100 \Omega$ (see Figure 3)                                                              |

| Common-Mode Output Voltage                                     | Voc                    |                  |       | 3    | V    | $R_L = 54 \Omega$ or 100 $\Omega$ ( see Figure 3)                                                             |

| $\Delta  V_{OC} $ for Complementary Output States <sup>1</sup> | $\Delta V_{OC}$        |                  |       | 0.2  | V    | $R_L = 54 \Omega$ or 100 $\Omega$ (see Figure 3)                                                              |

| Short-Circuit Output Current                                   | losd                   | -250             |       |      | mA   | $V_{OUT} = -7 \text{ V}$                                                                                      |

|                                                                |                        |                  |       | 250  | mA   | V <sub>OUT</sub> = 12 V                                                                                       |

| Logic Inputs                                                   |                        |                  |       |      |      |                                                                                                               |

| Input Low Voltage                                              | VIL                    |                  |       | 8.0  | V    | DE, DI, RE                                                                                                    |

| Input High Voltage                                             | $V_{IH}$               | 2.0              |       |      | V    | DE, DI, RE                                                                                                    |

| Logic Input Current                                            | I <sub>IN1</sub>       |                  |       | ±2   | μΑ   | DE, DI, RE                                                                                                    |

| RECEIVER                                                       |                        |                  |       |      |      |                                                                                                               |

| Differential Inputs                                            |                        |                  |       |      |      |                                                                                                               |

| Differential Input Threshold Voltage                           | $V_{TH}$               | -0.2             |       | +0.2 | V    | $-7 \text{ V} < \text{V}_{\text{CM}} < +12 \text{ V}$                                                         |

| Input Voltage Hysteresis                                       | $\Delta V_{TH}$        |                  | 50    |      | mV   | $V_{CM} = 0 V$                                                                                                |

| Input Resistance (A, B)                                        | R <sub>IN</sub>        | 12               |       |      | kΩ   | $-7 \text{ V} < \text{V}_{\text{CM}} < +12 \text{ V}$                                                         |

| Input Current (A, B)                                           | I <sub>IN2</sub>       |                  |       | 1.0  | mA   | $DE = 0 \text{ V}, V_{CC} = 0 \text{ V or } 3.6 \text{ V}, V_{IN} = 12 \text{ V}$                             |

|                                                                |                        | -0.8             |       |      | mA   | $DE = 0 \text{ V}, V_{CC} = 0 \text{ V or } 3.6 \text{ V}, V_{IN} = -7 \text{ V}$                             |

| RO Logic Output                                                |                        |                  |       |      |      |                                                                                                               |

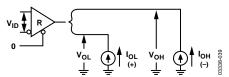

| Output Voltage High                                            | V <sub>OH</sub>        | $V_{CC} - 0.4 V$ |       |      | V    | $I_{OUT} = -1.5 \text{ mA}, V_{ID} = 200 \text{ mV} \text{ (see Figure 5)}$                                   |

| Output Voltage Low                                             | $V_{OL}$               |                  |       | 0.4  | V    | $I_{OUT} = 2.5 \text{ mA}, V_{ID} = 200 \text{ mV} \text{ (see Figure 5)}$                                    |

| Short-Circuit Output Current                                   | I <sub>OSR</sub>       | ±8               |       | ±60  | mA   | $0 \text{ V} < V_{RO} < V_{CC}$                                                                               |

| Tristate Output Leakage Current                                | lozr                   |                  |       | ±1   | μΑ   | $V_{CC} = 3.6 \text{ V}, 0 \text{ V} < V_{OUT} < V_{CC}$                                                      |

| POWER SUPPLY CURRENT                                           |                        |                  |       |      |      |                                                                                                               |

| Voltage Range                                                  | Vcc                    | 3.0              |       | 3.6  | V    |                                                                                                               |

| Supply Current                                                 | Icc                    |                  | 1.1   | 2.2  | mA   | No load, DI = 0 V or $V_{CC}$ , DE = $V_{CC}$ ,<br>$\overline{RE}$ = 0 V or $V_{CC}$                          |

|                                                                |                        |                  | 0.95  | 1.9  | mA   | $\frac{\text{No load, DI} = 0 \text{ V or V}_{\text{CC}}, \text{DE} = 0 \text{ V},}{\text{RE} = 0 \text{ V}}$ |

| Shutdown Current                                               | I <sub>SHDN</sub>      |                  | 0.002 | 1    | μΑ   | $DE = 0 \text{ V}, \overline{RE} = V_{CC}, DI = 0 \text{ V or } V_{CC}$                                       |

| ESD PROTECTION                                                 |                        |                  |       |      |      |                                                                                                               |

| A, B Pins                                                      |                        |                  | ±15   |      | kV   | Human body model                                                                                              |

| All Pins Except A, B                                           |                        |                  | ±4    |      | kV   | Human body model                                                                                              |

$<sup>^1</sup>$   $\Delta |V_{OD}|$  and  $\Delta |V_{OC}|$  are the changes in  $V_{OD}$  and  $V_{OC}$ , respectively, when DI input changes state.

### **TIMING SPECIFICATIONS**

$V_{CC} = 3.3 \text{ V}, T_A = 25^{\circ}\text{C}.$

Table 2.

| Parameter                                                    | Symbol                  | Min | Тур  | Max  | Unit | Test Conditions/Comments                                                         |

|--------------------------------------------------------------|-------------------------|-----|------|------|------|----------------------------------------------------------------------------------|

| DRIVER                                                       |                         |     |      |      |      |                                                                                  |

| Maximum Data Rate                                            |                         | 12  | 15   |      |      |                                                                                  |

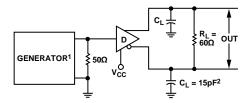

| Differential Output Delay                                    | t <sub>DD</sub>         | 1   | 22   | 35   | ns   | $R_L = 60 \Omega$ , $C_{L1} = C_{L2} = 15 pF$ (see Figure 6)                     |

| Differential Output Transition Time                          | <b>t</b> <sub>TD</sub>  | 3   | 11   | 25   | ns   | $R_L = 60 \Omega$ , $C_{L1} = C_{L2} = 15 pF$ (see Figure 6)                     |

| Propagation Delay                                            |                         |     |      |      |      |                                                                                  |

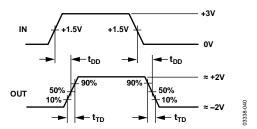

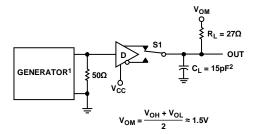

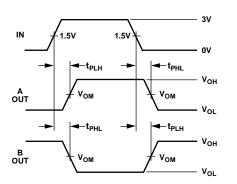

| From Low to High Level                                       | t <sub>PLH</sub>        | 7   | 23   | 35   | ns   | $R_L = 27 \Omega$ (see Figure 7)                                                 |

| From High to Low Level                                       | t <sub>PHL</sub>        | 7   | 23   | 35   | ns   | $R_L = 27 \Omega$ (see Figure 7)                                                 |

| t <sub>PLH</sub> – t <sub>PHL</sub>   Propagation Delay Skew | t <sub>PDS</sub>        |     | -1.4 | ±8   | ns   | $R_L = 27 \Omega$ (see Figure 7)                                                 |

| Enable/Disable Timing                                        |                         |     |      |      |      |                                                                                  |

| Enable Time to Low Level                                     | t <sub>PZL</sub>        |     | 42   | 90   | ns   | $R_L = 110 \Omega$ (see Figure 9)                                                |

| Enable Time to High Level                                    | t <sub>PZH</sub>        |     | 42   | 90   | ns   | $R_L = 110 \Omega$ (see Figure 8)                                                |

| Disable Time from Low Level                                  | t <sub>PLZ</sub>        |     | 35   | 80   | ns   | $R_L = 110 \Omega$ (see Figure 9)                                                |

| Disable Time from High Level                                 | <b>t</b> <sub>PHZ</sub> |     | 35   | 80   | ns   | $R_L = 110 \Omega$ (see Figure 8)                                                |

| Enable Time from Shutdown to Low Level                       | t <sub>PSL</sub>        |     | 650  | 900  | ns   | $R_L = 110 \Omega$ (see Figure 9)                                                |

| Enable Time from Shutdown to High Level                      | t <sub>PSH</sub>        |     | 650  | 900  | ns   | $R_L = 110 \Omega$ (see Figure 8)                                                |

| RECEIVER                                                     |                         |     |      |      |      |                                                                                  |

| Propagation Delay                                            |                         |     |      |      |      |                                                                                  |

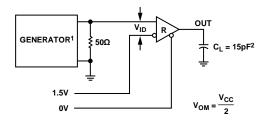

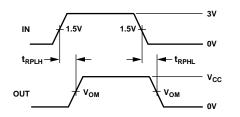

| From Low to High Level                                       | t <sub>RPLH</sub>       | 25  | 62   | 90   | ns   | $V_{ID} = 0 \text{ V to } 3.0 \text{ V, } C_{L} = 15 \text{ pF (see Figure 10)}$ |

| From High to Low Level                                       | t <sub>RPHL</sub>       | 25  | 62   | 90   | ns   | $V_{ID} = 0 \text{ V to } 3.0 \text{ V, } C_{L} = 15 \text{ pF (see Figure 10)}$ |

| $ t_{RPLH} - t_{RPHL} $ Propagation Delay Skew               | t <sub>RPDS</sub>       |     | 6    | ±10  | ns   | $V_{ID} = 0 \text{ V to } 3.0 \text{ V, } C_{L} = 15 \text{ pF (see Figure 10)}$ |

| Enable/Disable Timing                                        |                         |     |      |      |      |                                                                                  |

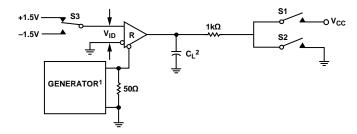

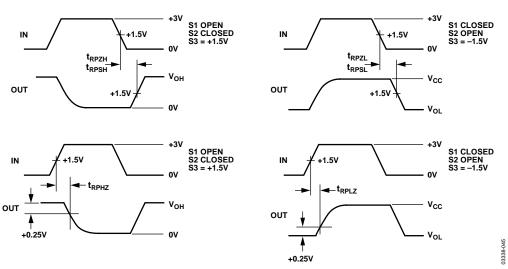

| Enable Time to Low Level                                     | t <sub>RPZL</sub>       |     | 25   | 50   | ns   | $C_L = 15 \text{ pF (see Figure 11)}$                                            |

| Enable Time to High Level                                    | t <sub>RPZH</sub>       |     | 25   | 50   | ns   | $C_L = 15 \text{ pF (see Figure 11)}$                                            |

| Disable Time from Low Level                                  | t <sub>RPLZ</sub>       |     | 25   | 45   | ns   | $C_L = 15 \text{ pF (see Figure 11)}$                                            |

| Disable Time from High Level                                 | t <sub>RPHZ</sub>       |     | 25   | 45   | ns   | $C_L = 15 \text{ pF (see Figure 11)}$                                            |

| Enable Time from Shutdown to Low Level                       | t <sub>RPSL</sub>       |     | 720  | 1400 | ns   | $C_L = 15 \text{ pF (see Figure 11)}$                                            |

| Enable Time from Shutdown to High Level                      | t <sub>RPSH</sub>       |     | 720  | 1400 | ns   | $C_L = 15 \text{ pF (see Figure 11)}$                                            |

| Time to Shutdown <sup>1</sup>                                | t <sub>SHDN</sub>       | 80  | 190  | 300  | ns   |                                                                                  |

<sup>&</sup>lt;sup>1</sup> The transceivers are put into shutdown mode by bringing the RE high and the DE low. If the inputs are in this state for less than 80 ns, the parts are guaranteed not to enter shutdown. If the parts are in this state for 300 ns or more, the parts are guaranteed to enter shutdown.

#### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 3.

| 1 11010 01                                              |                                               |

|---------------------------------------------------------|-----------------------------------------------|

| Parameter                                               | Values                                        |

| V <sub>CC</sub> to GND                                  | -0.3 V to +6 V                                |

| Digital Input/Output Voltage (DE, $\overline{RE}$ , DI) | -0.3 V to +6 V                                |

| Receiver Output Voltage (RO)                            | $-0.3 \text{ V to } (V_{CC} + 0.3 \text{ V})$ |

| Driver Output (A, B)/                                   |                                               |

| Receiver Input (A, B) Voltage                           | −8 V to +13 V                                 |

| Driver Output Current                                   | ±250 mA                                       |

| Power Dissipation (8-Lead SOIC_N)                       | 650 mW                                        |

| Operating Temperature Range                             | -40°C to +85°C                                |

| Storage Temperature Range                               | −65°C to +150°C                               |

| Lead Temperature, Soldering (10 sec)                    | 300°C                                         |

| Vapor Phase (60 sec)                                    | 215°C                                         |

| Infrared (15 sec)                                       | 220°C                                         |

| ESD Rating                                              |                                               |

| Human Body Model (A, B)                                 | ±15 kV                                        |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

**Table 4. Thermal Resistance**

| Package Type  | θ <sub>JA</sub> | Unit |

|---------------|-----------------|------|

| 8-Lead SOIC_N | 158             | °C/W |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

### PIN CONFIGURATION AND PIN FUNCTION DESCRIPTIONS

Figure 2. SOIC\_N Pin Configuration (R-8)

#### **Table 5. Pin Function Descriptions**

|          | Pin    |                                                                                                                                                                                                         |

|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic | Number | Description                                                                                                                                                                                             |

| RO       | 1      | Receiver Output. When enabled, if $A > B$ by 200 mV, then $RO = high$ . If $A < B$ by 200 mV, then $RO = low$ .                                                                                         |

| RE       | 2      | Receiver Output Enable. With RE low, the receiver output (RO) is enabled. With RE high, the output goes into a high impedance state. If RE is high and DE is low, the ADM3485E enters a shutdown state. |

| DE       | 3      | Driver Output Enable. A high level enables the driver differential outputs A and B. A low level places it in a high impedance state.                                                                    |

| DI       | 4      | Driver Input. When the driver is enabled, a logic low on DI forces A low and B high, while a logic high on DI forces A high and B low.                                                                  |

| GND      | 5      | Ground Connection, 0 V.                                                                                                                                                                                 |

| Α        | 6      | Noninverting Receiver Input A/Driver Output A.                                                                                                                                                          |

| В        | 7      | Inverting Receiver Input B/Driver Output B.                                                                                                                                                             |

| Vcc      | 8      | Power Supply, $3.3 \text{ V} \pm 0.3 \text{ V}$ .                                                                                                                                                       |

### TEST CIRCUITS AND SWITCHING CHARACTERISTICS

Figure 3. Driver Differential Output Voltage and Common-Mode Output Voltage

Figure 4. Driver Differential Output Voltage with Varying Common-Mode Voltage

Figure 5. Receiver Output Voltage High and Output Voltage Low

$^{1}\text{PPR}$  = 250kHz, 50% DUTY CYCLE,  $t_{R} \leq 6.0\text{ns}, Z_{O}$  = 50 $\Omega$ .  $^{2}\text{C}_{L}$  INCLUDES PROBE AND STRAY CAPACITANCE.

Figure 6. Driver Differential Output Delay and Transition Times

$^{1}\text{PPR}$  = 250kHz, 50% DUTY CYCLE,  $t_{R}$   $\leq$  6.0ns,  $\rm Z_{O}$  = 50  $\!\Omega$ .  $^{2}\rm C_{L}$  INCLUDES PROBE AND STRAY CAPACITANCE.

Figure 7. Driver Propagation Delays

$^{1}\text{PPR}$  = 250kHz, 50% DUTY CYCLE,  $t_{R}$   $\leq$  6.0ns,  $Z_{O}$  = 50  $\!\Omega$ .  $^{2}C_{L}$  INCLUDES PROBE AND STRAY CAPACITANCE.

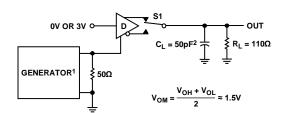

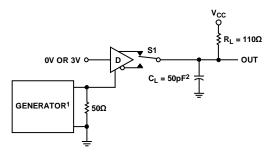

Figure 8. Driver Enable and Disable Times (tpzh, tpsh, tphz)

$^{1}\text{PPR}$  = 250kHz, 50% DUTY CYCLE,  $t_{R} \leq 6.0\text{ns},$   $Z_{O}$  = 50  $\Omega.$   $^{2}\text{C}_{L}$  INCLUDES PROBE AND STRAY CAPACITANCE.

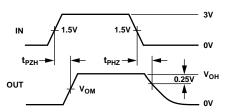

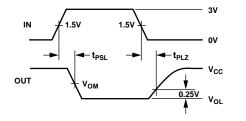

Figure 9. Driver Enable and Disable Times (tpzl, tpsl, tplz)

$^{1}\text{PPR}$  = 250kHz, 50% DUTY CYCLE,  $t_{R}$   $\leq$  6.0ns,  $\rm Z_{O}$  = 50  $\!\Omega$ .  $^{2}\rm C_{L}$  INCLUDES PROBE AND STRAY CAPACITANCE.

Figure 10. Receiver Propagation Delays

$^{1}\text{PPR}$  = 250kHz, 50% DUTY CYCLE,  $t_{R} \leq 6.0\text{ns},$   $Z_{O}$  = 50  $\Omega.$   $^{2}\text{C}_{L}$  INCLUDES PROBE AND STRAY CAPACITANCE.

Figure 11. Receiver Enable and Disable Times

### TYPICAL PERFORMANCE CHARACTERISTICS

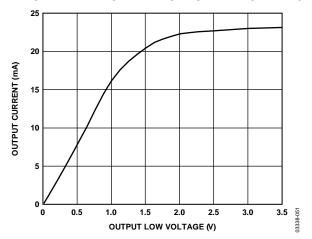

Figure 12. Output Current vs. Receiver Output Low Voltage

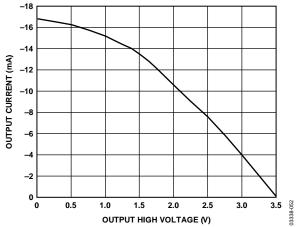

Figure 13. Output Current vs. Receiver Output High Voltage

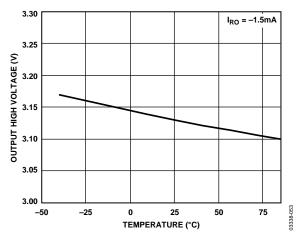

Figure 14. Receiver Output High Voltage vs. Temperature

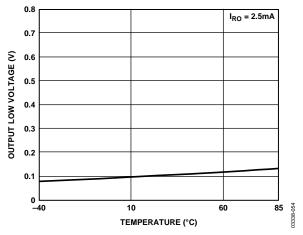

Figure 15. Receiver Output Low Voltage vs. Temperature

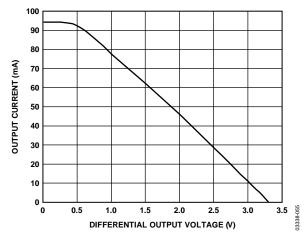

Figure 16. Driver Output Current vs. Differential Output Voltage

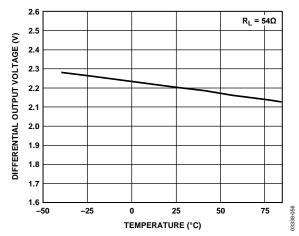

Figure 17. Driver Differential Output Voltage vs. Temperature

Figure 18. Output Current vs. Driver Output Low Voltage

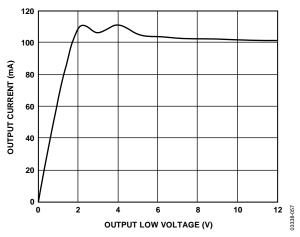

Figure 19. Output Current vs. Driver Output High Voltage

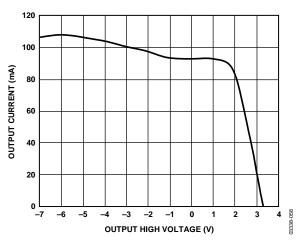

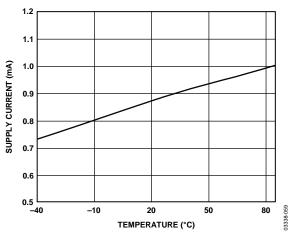

Figure 20. Supply Current vs. Temperature

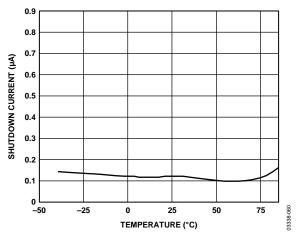

Figure 21. Shutdown Current vs. Temperature

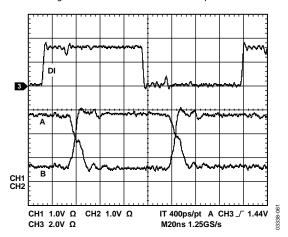

Figure 22. Driver Propagation Delay

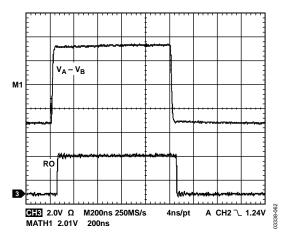

Figure 23. Receiver Propagation Delay, Driven by External RS-485 Device

#### STANDARDS AND TESTING

Table 6 compares RS-422 and RS-485 interface standards, and Table 7 and Table 8 show transmitting and receiving truth tables.

Table 6.

| Specification                        | RS-422       | RS-485        |

|--------------------------------------|--------------|---------------|

| Transmission Type                    | Differential | Differential  |

| Maximum Data Rate                    | 10 Mbps      | 10 Mbps       |

| Maximum Cable Length                 | 4000 ft      | 4000 ft       |

| Minimum Driver Output Voltage        | ±2 V         | ±1.5 V        |

| Driver Load Impedance                | 100 Ω        | 54 Ω          |

| Receiver Input Resistance            | 4 kΩ min     | 12 kΩ min     |

| Receiver Input Sensitivity           | ±200 mV      | ±200 mV       |

| Receiver Input Voltage Range         | −7 V to +7 V | −7 V to +12 V |

| Number of Drivers/Receivers per Line | 1/10         | 32/32         |

Table 7. Transmitting Truth Table

| Tr             | ansmitting | Inputs         | Transmitting Outputs                       |                                            |  |

|----------------|------------|----------------|--------------------------------------------|--------------------------------------------|--|

| RE             | DE         | DI             | В                                          | Α                                          |  |

| X <sup>1</sup> | 1          | 1              | 0                                          | 1                                          |  |

| $X^1$          | 1          | 0              | 1                                          | 0                                          |  |

| 0              | 0          | X <sup>1</sup> | High-Z <sup>2</sup>                        | High-Z <sup>2</sup>                        |  |

| 1              | 0          | X <sup>1</sup> | High-Z <sup>2</sup><br>High-Z <sup>2</sup> | High-Z <sup>2</sup><br>High-Z <sup>2</sup> |  |

<sup>&</sup>lt;sup>1</sup> X = don't care.

**Table 8. Receiving Truth Table**

|    | Receiving Inputs | Receiving Outputs |                     |  |

|----|------------------|-------------------|---------------------|--|

| RE | DE               | A – B             | RO                  |  |

| 0  | X <sup>1</sup>   | >+0.2 V           | 1                   |  |

| 0  | X <sup>1</sup>   | <-0.2 V           | 0                   |  |

| 0  | X <sup>1</sup>   | Inputs open       | 1                   |  |

| 1  | X <sup>1</sup>   | X <sup>1</sup>    | High-Z <sup>2</sup> |  |

<sup>&</sup>lt;sup>1</sup> X = don't care.

#### **ESD TESTING**

Two coupling methods are used for ESD testing, contact discharge and air-gap discharge. Contact discharge calls for a direct connection to the unit being tested. Air-gap discharge uses a higher test voltage but does not make direct contact with the unit under test. With air-gap discharge, the discharge gun is moved toward the unit under test, developing an arc across the air gap, hence the term air-gap discharge. This method is

influenced by humidity, temperature, barometric pressure, distance, and rate of closure of the discharge gun. The contact discharge method, while less realistic, is more repeatable and is gaining acceptance and preference over the air-gap method.

Although very little energy is contained within an ESD pulse, the extremely fast rise time, coupled with high voltages, can cause failures in unprotected semiconductors. Catastrophic destruction can occur immediately as a result of arcing or heating. Even if catastrophic failure does not occur immediately, the device can suffer from parametric degradation, which can result in degraded performance. The cumulative effects of continuous exposure can eventually lead to complete failure.

I/O lines are particularly vulnerable to ESD damage. Simply touching or plugging in an I/O cable can result in a static discharge that can damage or completely destroy the interface product connected to the I/O port. It is extremely important, therefore, to have high levels of ESD protection on the I/O lines.

The ESD discharge could induce latch-up in the device under test, so it is important that ESD testing on the I/O pins be carried out while device power is applied. This type of testing is more representative of a real-world I/O discharge, where the equipment is operating normally when the discharge occurs.

**Table 9. ESD Test Results**

| ESD Test Method  | I/O Pins |

|------------------|----------|

| Human Body Model | ±15 kV   |

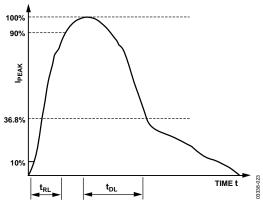

Figure 24. Human Body Model Current Waveform

<sup>&</sup>lt;sup>2</sup> High-Z = high impedance.

<sup>&</sup>lt;sup>2</sup> High-Z = high impedance.

## APPLICATIONS INFORMATION DIFFERENTIAL DATA TRANSMISSION

Differential data transmission is used to reliably transmit data at high rates over long distances and through noisy environments. Differential transmission nullifies the effects of ground shifts and noise signals that appear as common-mode voltages on the line.

Two main standards that specify the electrical characteristics of transceivers used in differential data transmission are approved by the Electronics Industries Association (EIA). The RS-422 standard specifies data rates up to 10 Mbps and line lengths up to 4000 feet. A single driver can drive a transmission line with up to 10 receivers. The RS-485 standard was defined to cater to true multipoint communications. This standard meets or exceeds all the requirements of RS-422 but also allows multiple drivers and receivers to be connected to a single bus. An extended common-mode range of -7 V to +12 V is defined.

The most significant difference between RS-422 and RS-485 is the fact that under the RS-485 standard the drivers may be disabled, thereby allowing more than one to be connected to a single line. Only one driver should be enabled at a time, but the RS-485 standard contains additional specifications to guarantee device safety in the event of line contention.

#### **CABLE AND DATA RATE**

The transmission line of choice for RS-485 communications is a twisted pair. Twisted-pair cable tends to cancel common-mode noise and also causes cancellation of the magnetic fields generated by the current flowing through each wire, thereby reducing the effective inductance of the pair.

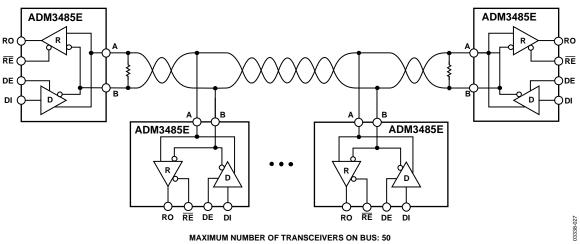

The ADM3485E is designed for bidirectional data communications on multipoint transmission lines. A typical application showing a multipoint transmission network is illustrated in Figure 25. Only one driver can transmit at a particular time, but multiple receivers may be enabled simultaneously.

As with any transmission line, it is important that reflections are minimized. This can be achieved by terminating the extreme ends of the line using resistors equal to the characteristic impedance of the line. Stub lengths off the main line must also be kept as short as possible. A properly terminated transmission line appears purely resistive to the driver.

#### **RECEIVER OPEN-CIRCUIT FAIL-SAFE**

The receiver input includes a fail-safe feature that guarantees a logic high on the receiver when the inputs are open circuit or floating.

Table 10. RS-422 and RS-485 Interface Standards

| Specification                 | RS-422       | RS-485        |

|-------------------------------|--------------|---------------|

| Transmission Type             | Differential | Differential  |

| Maximum Cable Length          | 4000 ft      | 4000 ft       |

| Minimum Driver Output Voltage | ±2 V         | ±1.5 V        |

| Driver Load Impedance         | 100 Ω        | 54 Ω          |

| Receiver Input Resistance     | 4 kΩ min     | 12 kΩ min     |

| Receiver Input Sensitivity    | ±200 mV      | ±200 mV       |

| Receiver Input Voltage Range  | −7 V to +7 V | −7 V to +12 V |

Figure 25. Multipoint Transmission Network

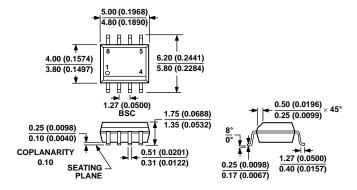

### **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MS-012-AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 26. 8-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-8)

Dimensions shown in millimeters and (inches)

#### **ORDERING GUIDE**

| ****               |                   |                                                |                |

|--------------------|-------------------|------------------------------------------------|----------------|

| Model <sup>1</sup> | Temperature Range | Package Description                            | Package Option |

| ADM3485EAR         | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N] | R-8            |

| ADM3485EAR-REEL7   | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N] | R-8            |

| ADM3485EAR-REEL    | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N] | R-8            |

| ADM3485EARZ        | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N] | R-8            |

| ADM3485EARZ-REEL7  | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N] | R-8            |

| ADM3485EARZ-REEL   | -40°C to +85°C    | 8-Lead Standard Small Outline Package [SOIC_N] | R-8            |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

**NOTES**

### **NOTES**

| ADM3485E |  |

|----------|--|

|----------|--|

NOTES