### EP330 EPLD

High-Performance 8-Macrocell Device

September 1991, ver. 2

Data Sheet

### **Features**

- ☐ High-performance 8-macrocell EPLD

- Combinatorial speeds with t<sub>PD</sub> = 12 ns

- Counter frequencies up to 100 MHz

- Pipelined data rates up to 125 MHz

- $\Box$  Low power;  $I_{CC} = 45 \text{ mA (typical)}$

- Available in one-time-programmable (OTP) plastic chip carrier packages

- 20-pin dual in-line package (PDIP)

- 20-pin J-lead chip carrier (PLCC)

- 20-pin, 300-mil small-outline IC (SOIC)

- Macrocell flip-flops can be individually programmed for registered or combinatorial operation

- ☐ Direct replacement for GAL 16V8 and most 20-pin PAL devices

- "Quiet" outputs minimize output switching noise found in other high-speed CMOS devices

- ☐ Extensive third-party software and programming support

- MAX+PLUS II and A+PLUS software support includes schematic capture, Boolean equation, state machine, and netlist design entry methods; Altera Hardware Description Language (AHDL), waveform entry, and an EDIF 2 0 0 interface are available with MAX+PLUS II.

# General Description

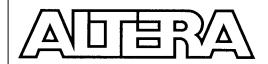

Altera's EP330 Erasable Programmable Logic Device (EPLD) provides a high-speed, low-power, pin-compatible replacement for 20-pin programmable logic devices such as PALs and GALs. The EP330 EPLD is available in 20-pin OTP plastic DIP, J-lead, and SOIC packages. See Figure 1.

Figure 1. EP330 Package Pin-Out Diagrams

Altera Corporation

Page 39

The EP330 EPLD can accommodate up to 18 inputs and 8 outputs. Each of the 8 macrocells contains a programmable-AND/fixed-OR structure that implements logic with up to 8 product terms. An additional product term in each macrocell controls Output Enable.

Altera's proprietary programmable I/O architecture allows the designer to program output and feedback paths for combinatorial or registered operation in active-high and active-low modes. Thus, EP330 devices may be configured as drop-in replacements for PAL and GAL devices such as the 16R8 and 16V8. See *Application Note 2* for more information.

The EP330 CMOS EPROM technology reduces active power consumption to less than 50% of the power required by equivalent bipolar devices, without sacrificing speed. This reduced power consumption makes these EPLDs highly desirable for a wide range of applications. Additionally, EP330 EPLDs are 100% generically testable.

Logic is implemented with Altera's MAX+PLUS II or A+PLUS development systems. Both systems support schematic capture, Boolean equation, state machine, truth table, and netlist design entry methods. MAX+PLUS II also provides the Altera Hardware Description Language (AHDL), waveform design entry, and an EDIF 200 netlist interface. After the design is entered, the software automatically translates the input files into logic equations, performs Boolean minimization, and fits the design into the EPLD. MAX+PLUS II automatically partitions larger designs into multiple EPLDs. The device(s) can then be programmed in seconds at the designer's desktop to create customized working silicon. In addition, extensive third-party support exists for design entry, design processing, and device programming.

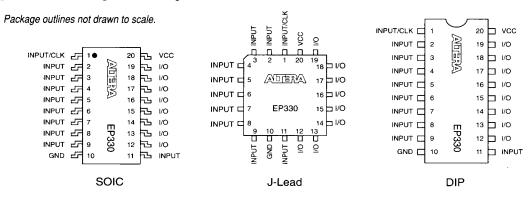

# EP330 EPLD Output Characteristics

The EP330 combines high performance with low noise. For example, Figure 2 shows the switching performance of the EP330-12, Altera's 12-ns version of the EP330 EPLD. The EPLD's "quiet" outputs allow designs to run fast with high system reliability. In addition, enhanced output current capability ( $I_{OL}=24~\text{mA}$ ) allows the EP330 to directly integrate designs requiring high-current drive, such as bus interfaces. The EP330 EPLD is available with  $t_{PD}$  values of 12 ns and 15 ns.

# Functional Description

The EP330 EPLD uses CMOS EPROM technology to configure connections in a programmable-AND logic array. EPROM connections are also used to control the output/feedback options, such as registered or combinatorial feedback, in active-high or active-low modes.

Page 40

Altera Corporation

Figure 2. EP330-12 Output Switching Performance

Channel 2 = 2.000 V/division

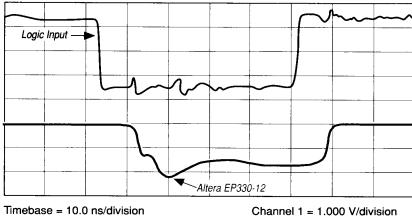

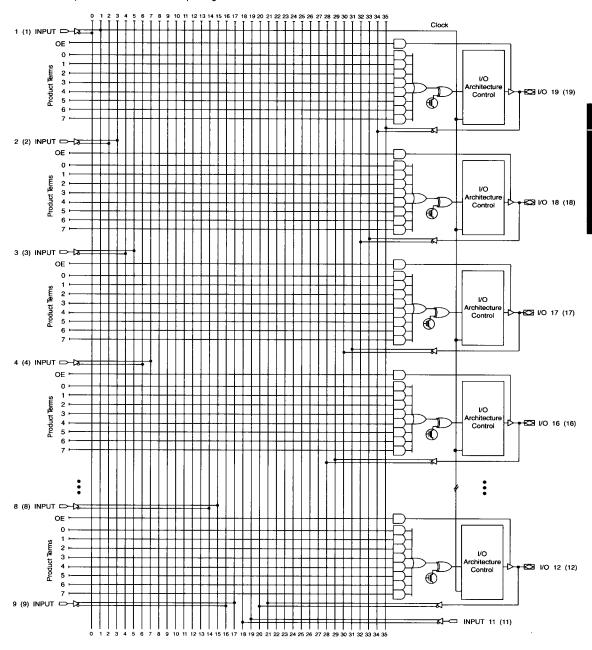

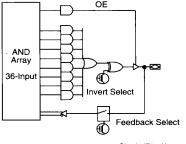

An EP330 EPLD has ten dedicated data inputs and eight I/O pins that can be configured for input, output, or bidirectional operation. Figure 3 shows the EP330 macrocell.

Figure 3. EP330 Macrocell

Altera Corporation

Page 41

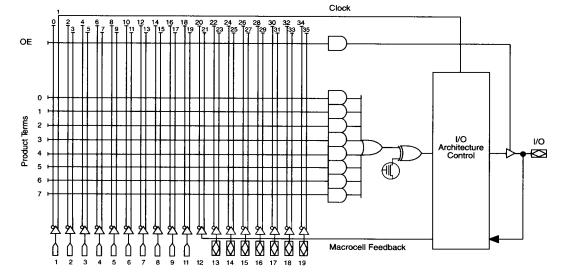

The EP330 block diagram is shown in Figure 4. The internal architecture of this device has a sum-of-products (AND/OR) structure. Inputs to the programmable-AND array come from the true and complement signals of the 10 dedicated input pins, and the true and complement forms of the 8 feedback signals from the I/O architecture control blocks. The 36-input AND array has 72 product terms distributed equally among the 8 macrocells. Each product term represents a 36-input AND gate.

The outputs of eight product terms are ORed together; then the output of the OR gate is fed as an input to an XOR gate. The XOR function allows the designer to use the invert-select EPROM cell to specify the polarity of the output signal. If the EPROM cell is programmed, the true form of the signal (active high) is passed; if not, the complement of the signal (active low) is passed. The XOR output then feeds the I/O architecture control block, in which the output is configured for registered or combinatorial operation. In registered mode, the output is registered via a positive-edge-triggered D-type flip-flop. The feedback signal comes from the output of the flip-flop. In combinatorial mode, the output is not registered, and the feedback signal comes directly from the I/O pin.

### Output Enable Product Term

The Output Enable (OE) product term determines whether an output signal will propagate to the output pin. If the output of the OE product term is high, output to the pin is enabled. If the output is low, the output buffer becomes a high-impedance node and does not allow the output signal to reach the output pin. The I/O pin can then be used as a dedicated input. This OE product term allows true bidirectional operation in combinatorial mode.

The EP330 device contains eight OE product terms, one for each I/O pin. All outputs can be enabled or disabled simultaneously by using an identically programmed product term at each of the outputs. Outputs can be enabled under other conditions by defining a different OE product term for each output.

### I/O Architecture

Figure 5 shows the output configurations available for the eight I/O pins. Either registered or combinatorial outputs can be individually specified for each macrocell. Any I/O pin can be configured as a dedicated input by choosing no output and pin feedback.

In combinatorial mode, active-high or active-low output polarity with pin feedback or no feedback can be chosen. In registered mode, active-high or active-low output polarity with the internal registered feedback or no feedback are available. In the erased state, the I/O architecture is configured for combinatorial active-low output with pin feedback.

Page 42

Altera Corporation

2

EPL

Figure 4. EP330 Block Diagram

Numbers in parentheses are for J-lead packages.

Altera Corporation

Page 43

Figure 5. EP330 I/O Configurations

#### Combinatorial VO Selection

| Output/Polarity    | Feedback  |

|--------------------|-----------|

| Combinatorial/High | Pin, None |

| Combinatorial/Low  | Pin, None |

| None               | Pin       |

#### Registered I/O Selection

| Output/Polarity                           | Feedback                                           |

|-------------------------------------------|----------------------------------------------------|

| D Register/High<br>D Register/Low<br>None | D Register, None<br>D Register, None<br>D Register |

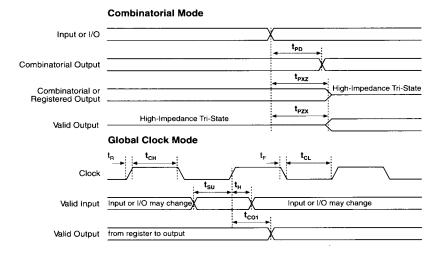

The switching waveforms for the EP330 EPLD are shown in Figure 6.

### Figure 6. EP330 Switching Waveforms

$t_{\rm R}$  and  $t_{\rm F}$  < 2 ns. Inputs are driven at 3 V for a logic high and 0 V for a logic low. All timing characteristics are measured at 1.5 V.

Page 44

Altera Corporation

# Functional Testing

The EP330 EPLD is fully functionally tested and guaranteed through complete testing of each EPROM bit and all internal logic elements. This testing ensures a 100% programming yield.

The testing process eliminates traditional problems associated with fuse-programmed circuits. An EP330 EPLD allows test programming patterns to be used and then erased. The ability to use application-independent, general-purpose tests is called generic testing and is unique to EPLDs.

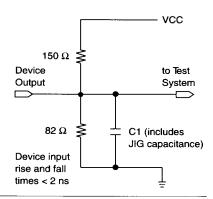

AC test measurements are performed under the conditions shown in Figure 7.

### Figure 7. EP330 AC Test Conditions

Power supply transients can affect AC measurements. Simultaneous transitions of multiple outputs should be avoided for accurate measurement. Threshold tests must not be performed under AC conditions. Large-amplitude, fast ground current transients normally occur as the device outputs discharge the load capacitances. When these transients flow through the parasitic inductance between the device ground pin and the test system ground, it can create significant reductions in observable noise immunity.

## Design Security

An EP330 EPLD contains a programmable Security Bit that controls access to the data programmed into the device. If this feature is used, a proprietary design implemented in the device cannot be copied or retrieved. This feature provides a high level of design security by making programmed data within EPROM cells invisible. The Security Bit, along with all other program data, is reset by erasing the device.

### Absolute Maximum Ratings Note: See Operating Requirements for EPLDs in this data book.

| Symbol           | Parameter                         | Parameter Conditions |      | Max  | Unit |

|------------------|-----------------------------------|----------------------|------|------|------|

| v <sub>cc</sub>  | Supply voltage                    | With respect to GND  | -2.0 | 7.0  | ٧    |

| V <sub>PP</sub>  | Programming supply voltage        | See Note (1)         | -2.0 | 14.0 | ٧    |

| Vi               | DC input voltage                  |                      | -2.0 | 7.0  | ٧    |

| I <sub>MAX</sub> | DC V <sub>CC</sub> or GND current |                      | -160 | 160  | mA   |

| I <sub>OUT</sub> | DC output current, per pin        |                      | -50  | 50   | mA   |

| PD               | Power dissipation                 |                      |      | 800  | mW   |

| T <sub>STG</sub> | Storage temperature               | No bias              | -65  | 150  | °C   |

| T <sub>AMB</sub> | Ambient temperature               | Under bias           | -65  | 135  | °C   |

### **Recommended Operating Conditions**

| Symbol          | Parameter             | Conditions         | Min  | Max             | Unit |

|-----------------|-----------------------|--------------------|------|-----------------|------|

| v <sub>cc</sub> | Supply voltage        |                    | 4.75 | 5.25            | V    |

| VI              | Input voltage         |                    | 0    | v <sub>cc</sub> | ٧    |

| ٧o              | Output voltage        |                    | 0    | v <sub>cc</sub> | ٧    |

| TA              | Operating temperature | For commercial use | 0    | 70              | °C   |

| TA              | Operating temperature | For industrial use |      | 85              | °C   |

| t <sub>R</sub>  | Input rise time       | See Note (2)       |      | 20              | ns   |

| t <sub>F</sub>  | Input fall time       | See Note (2)       |      | 20              | ns   |

### DC Operating Conditions See Notes (3), (4)

| Symbol           | Parameter                                | Conditions                                                                     | Min  | Тур | Max                   | Unit |

|------------------|------------------------------------------|--------------------------------------------------------------------------------|------|-----|-----------------------|------|

| VIH              | High-level input voltage                 |                                                                                | 2.0  |     | V <sub>CC</sub> + 0.3 | ٧    |

| V <sub>IL</sub>  | Low-level input voltage                  |                                                                                | -0.3 |     | 0.8                   | ٧    |

| V <sub>OH</sub>  | High-level TTL output voltage            | I <sub>OH</sub> = -12 mA DC                                                    | 2.4  |     |                       | ٧    |

| V <sub>OL</sub>  | Low-level output voltage                 | I <sub>OL</sub> = 24 mA DC                                                     |      |     | 0.5                   | ٧    |

| I <sub>1</sub>   | Input leakage current                    | V <sub>I</sub> = V <sub>CC</sub> or GND                                        | -10  |     | 10                    | μA   |

| Ioz              | Tri-state output off-state current       | V <sub>O</sub> = V <sub>CC</sub> or GND                                        | -10  |     | 10                    | μА   |

| I <sub>CC1</sub> | V <sub>CC</sub> supply current (standby) | V <sub>1</sub> = V <sub>CC</sub> or GND, No load                               |      | 40  | 75                    | mA   |

| I <sub>CC3</sub> | V <sub>CC</sub> supply current (active)  | V <sub>I</sub> = V <sub>CC</sub> or GND, No load,<br>f = 1.0 MHz, See Note (5) |      | 45  | 75                    | mA   |

### Capacitance See Note (6)

| Symbol           | Parameter             | Conditions                                  | Min | Max | Unit |

|------------------|-----------------------|---------------------------------------------|-----|-----|------|

| CIN              | Input capacitance     | V <sub>IN</sub> = 0 V, f = 1.0 MHz          |     | 10  | pF   |

| C <sub>OUT</sub> | Output capacitance    | V <sub>OUT</sub> = 0 V, f = 1.0 MHz         |     | 15  | pF   |

| C <sub>CLK</sub> | Clock pin capacitance | $V_{IN} = 0 \text{ V}, f = 1.0 \text{ MHz}$ |     | 10  | pF   |

### AC Operating Conditions See Note (4)

|                  |                                    |                         | EP3 | 30-12 | EP3      | 30-15 |      |

|------------------|------------------------------------|-------------------------|-----|-------|----------|-------|------|

| Symbol           | Parameter                          | Conditions              | Min | Max   | Min      | Max   | Unit |

| t <sub>PD1</sub> | Input to non-registered output     |                         |     | 12    |          | 15    | ns   |

| t <sub>PD2</sub> | I/O input to non-registered output | C1 = 35 pF              |     | 13    |          | 16    | ns   |

| t <sub>PZX</sub> | Input to output enable             | 7.                      |     | 12    | _        | 15    | ns   |

| t <sub>PXZ</sub> | Input to output disable            | C1 = 5 pF, See Note (7) |     | 12    |          | 15    | ns   |

| t <sub>IO</sub>  | I/O input pad and buffer delay     |                         |     | 1     | <u> </u> | 1     | ns   |

| Global C         | Global Clock Mode          |              |     | EP330-12 |      | EP330-15 |      |

|------------------|----------------------------|--------------|-----|----------|------|----------|------|

| Symbol           | Parameter                  | Conditions   | Min | Max      | Min  | Max      | Unit |

| f <sub>MAX</sub> | Maximum frequency          | See Note (8) | 125 |          | 100  |          | MHz  |

| t <sub>SU</sub>  | Setup time                 |              | 6   | <u> </u> | 8    |          | ns   |

| t <sub>H</sub>   | Hold time                  |              | 0   |          | 0    |          | ns   |

| t <sub>CH</sub>  | Clock high time            |              | 4   |          | 5    |          | ns   |

| t <sub>CL</sub>  | Clock low time             |              | 4   |          | 5    |          | ns   |

| t <sub>CO1</sub> | Clock to output delay      |              |     | 8        |      | 10       | ns   |

| t <sub>CNT</sub> | Minimum clock period       |              |     | 10       | 1    | 12       | ns   |

| f <sub>CNT</sub> | Internal maximum frequency | See Note (5) | 100 |          | 83.3 |          | MHz  |

#### Notes to tables:

- (1) Minimum DC input is -0.3 V. During transitions, inputs may undershoot to -2.0 V or overshoot to 7.0 V for periods less than 20 ns under no-load conditions.

- (2) For all clocks:  $t_R$  and  $t_F = 20$  ns.

- (3) Typical values are for  $T_A = 25^{\circ} \text{ C}$  and  $V_{CC} = 5 \text{ V}$ .

- (4) Operating conditions:  $V_{CC}$  = 5 V ± 5%,  $T_A$  = 0° C to 70° C for commercial use.  $V_{CC}$  = 5 V ± 10%,  $T_A$  = -40° C to 85° C for industrial use.

- (5) Measured with a device programmed as an 8-bit counter.

- (6) Capacitance measured at 25° C. Sample-tested only. Pin 11 (high-voltage pin during programming) has maximum capacitance of 20 pF.

- (7) Sample-tested only for an output change of 500 mV.

- (8) The f<sub>MAX</sub> values represent the highest frequency for pipelined data.

### **Product Availability**

| Operation  | ng Temperature     | Availability       |

|------------|--------------------|--------------------|

| Commercial | (0° C to 70° C)    | EP330-12, EP330-15 |

| Industrial | (-40° C to 85° C)  | EP330-15           |

| Military   | (-55° C to 125° C) | Consult factory    |

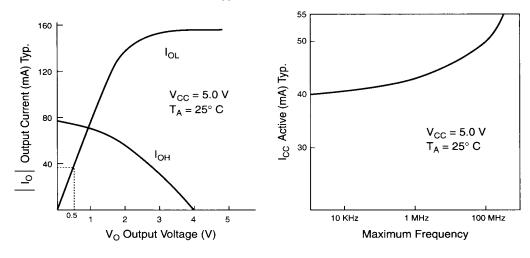

Figure 8 shows output drive characteristics for EP330 I/O pins and typical supply current versus frequency for the EP330 EPLD.

Figure 8. EP330 Output Drive Characteristics and  $I_{CC}$  vs. Frequency

Page 48 Altera Corporation