Quad 16-bit DAC: 10 Gbps JESD204B interface: up to 1.50

Gsps; x2, x4 and x8 interpolating

Rev. 1.03 — 13 May 2013

Advance data sheet

# 1. General description

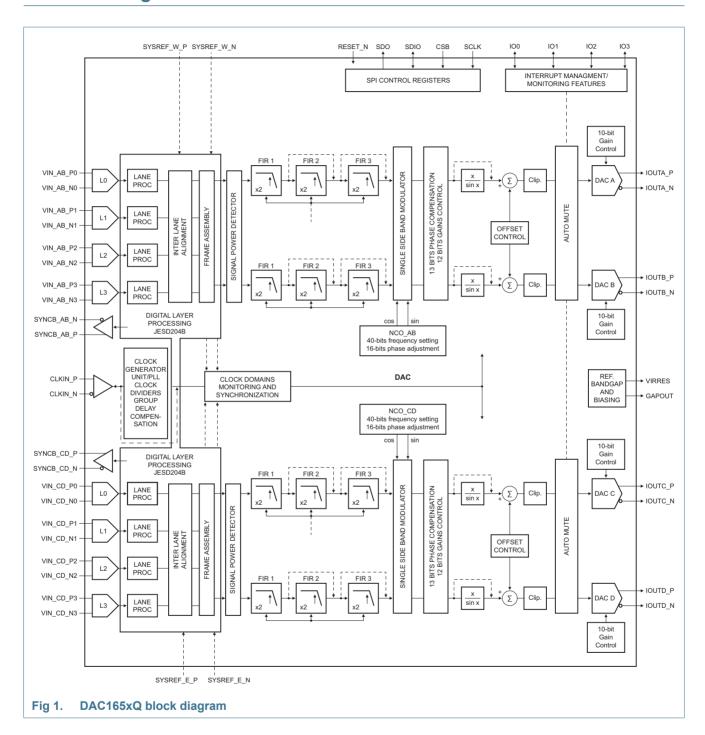

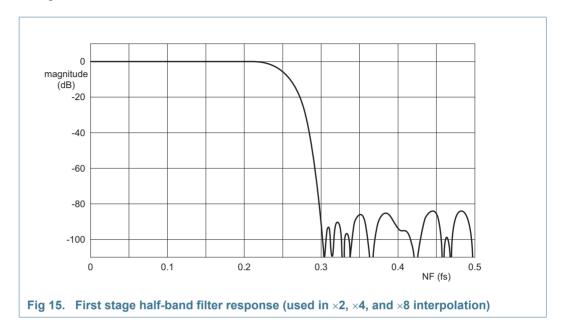

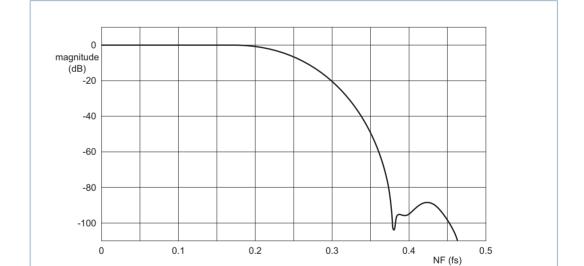

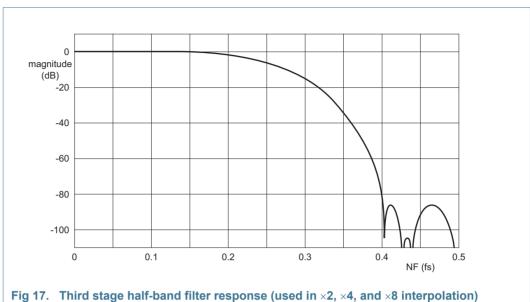

The DAC1658Q and the DAC1653Q are high-speed high-performance 16-bit quad channel digital-to-analog converter (DAC) with high and low common-mode output. The devices provide a sample rate up to 1.50 Gsps with selectable  $\times 2$ ,  $\times 4$  and  $\times 8$  interpolation filters optimized for multi-carrier and broadband wireless transmitters.

When both devices are referred to in this data sheet, the following convention will be used: DAC165xQ.

The DAC165xQ integrates a JESD204B high-speed serial input data interface running up to 10 Gbps allowing quad channel input sampling at up to 750 Msps over eight differential lanes. It offers numerous advantages over traditional parallel digital interfaces:

- · Easier Printed-Circuit Board (PCB) layout

- · Lower radiated noise

- Lower pin count

- Self-synchronous link

- · Skew compensation

- Deterministic latency

- Multiple Device Synchronization (MDS); JESD204B subclass 1 support

- Harmonic clocking support

- Assured FPGA interoperability

There are two versions of the DAC165xQ:

- Low common-mode output voltage (part identification DAC1653Q)

- High common-mode output voltage (part identification DAC1658Q)

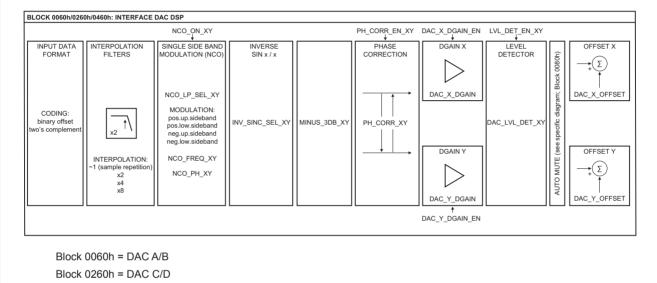

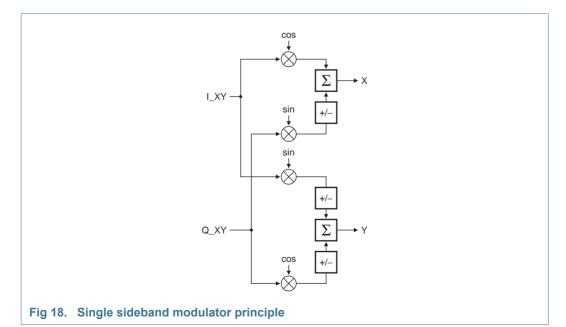

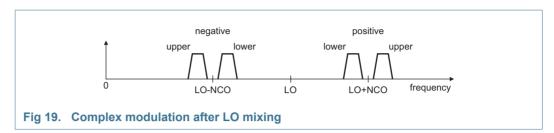

Two optional on-chip digital modulators convert the complex I/Q pattern from baseband to IF. The mixer frequency is set by writing to the Serial Peripheral Interface (SPI) control registers associated with the on-chip 40-bit Numerically Controlled Oscillator (NCO). This accurately places the IF carrier in the frequency domain. The 13-bit phase adjustment feature, the 12-bit digital gain and the 16-bit digital offset enable full control of the analog output signals.

The DAC165xQ is fully compatible with device subclass 1 of the JEDEC JESD204B standard, guaranteeing deterministic and repeatable interface latency using the differential SYSREF signal. The device also supports harmonic clocking to reduce system-level clock synthesis and distribution challenges.

The Advance Information presented herein represents a product that is developmental or prototype. The noted characteristics are design targets. Integrated Device Technologies, Inc. (IDT) reserves the right to change any circuitry or specifications without notice.

Multiple Device Synchronization (MDS) enables multiple DAC channels to be sample synchronous and phase coherent to within one DAC clock period. MDS is ideal for LTE and LTE-A MIMO transceiver applications.

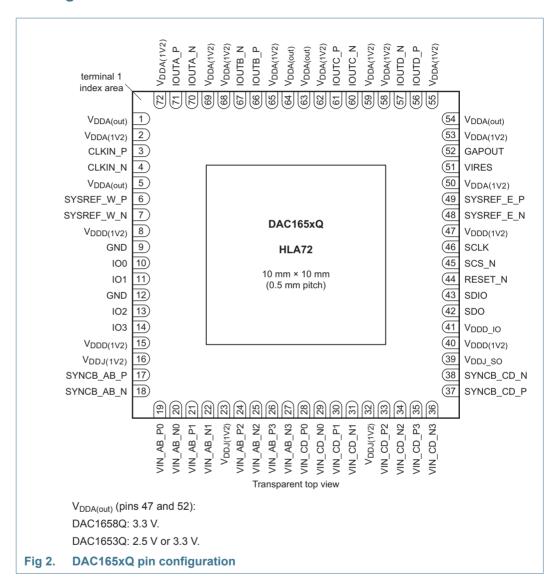

The DAC165xQ includes an internal regulation to adjust the full-scale output current. The internal regulator adjusts the full-scale output current between 8.1 mA and 34 mA. The device is available in a HLA72 package (10 mm × 10 mm). It is supported by customer demo boards that are supplied with or without FPGA logic devices.

### Features and benefits

- quad channel 16-bit resolution

- 1.50 GSps maximum output update rate NSD = -162 dBm/Hz typical

- JEDEC JESD204B device subclass I compatible: SYSREF based deterministic and repeatable interface latency

- Multiple Device Synchronization (MDS) enables multiple DAC channels to be sample synchronous and phase coherent to within one DAC clock period

- 8 configurable JESD204B serial input lanes running up to 10 Gbps with embedded termination and programmable equalization gain

- 750 Msps maximum baseband input data rate

- SPI interface (3-wire or 4-wire mode) for control setting and status monitoring

- differential scalable output current from 8.1 mA to 34 mA

- two embedded NCOs with 40-bit programmable frequency and 16-bit phase adjustment

- embedded complex (IQ) digital modulator

- flexible SPI power supply (1.8 V or 1.2 V) ensuring compatibility with on-board SPI bus

- flexible differential signals (SYNC) power supply (1.8 V or 1.2 V) ensuring compatibility with on-board devices

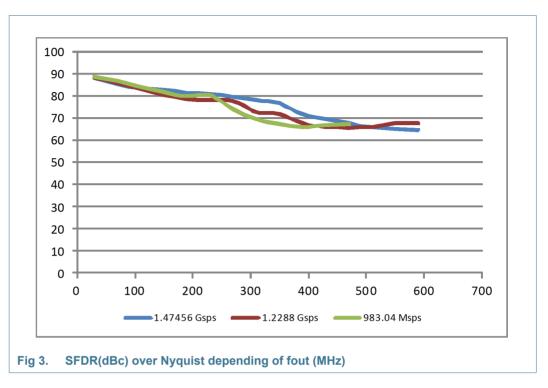

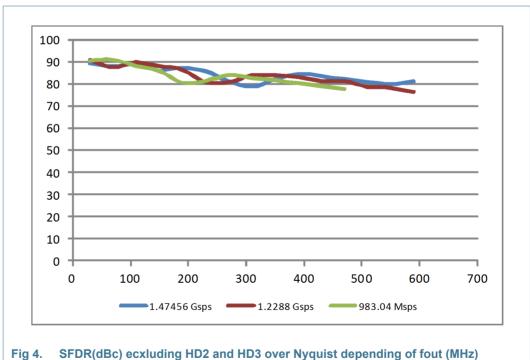

- SFDR<sub>RBW</sub> = 85 dBc typical ( $f_s = 1.47456$  Gsps; interpolation  $\times 2$ ; bandwidth = 250 MHz; f<sub>out</sub> = 150 MHz)

- $(f_0 = 20 \text{ MHz})$

- IMD3 = 85 dBc typical ( $f_s = 1.47456$  Gsps; interpolation  $\times 2$ ;  $f_{o1} = 152 \text{ MHz}; f_{o2} = 153 \text{ MHz})$

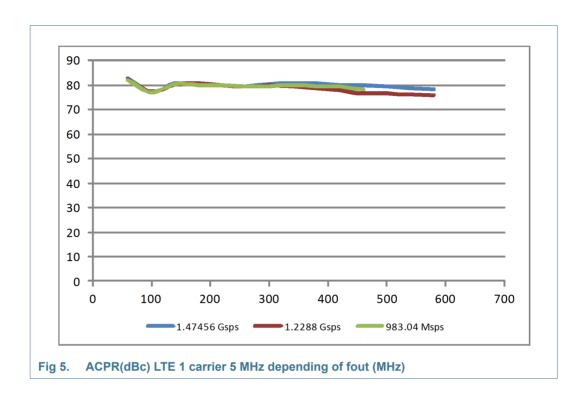

- one carrier ACLR = 77 dB typical  $(f_s = 1.47456 \text{ Gsps}; f_{NCO} = 230 \text{ MHz})$

- RF enable/disable pin and RF automatic mute. The RF enable feature is available via one of the IO pins

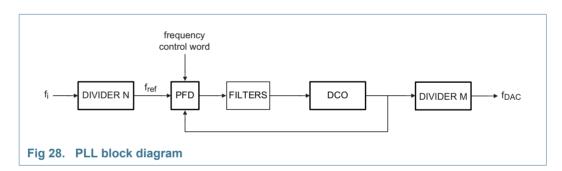

- very low noise bypassable integrated Phase-Locked Loop (PLL); no external capacitors

- clock divider by 2, 4, 6 or 8 available at the input of the clock path

- group delay compensation

- power-down mode control

- on-chip 0.7 V reference

- 1.2 V and 2.5 V or 3.3 V power supplies industrial temperature range -40 °C to +85 °C

- HLA72 package (10 mm × 10 mm)

# 3. Applications

- Wireless infrastructure radio base station transceivers, including: LTE-A, LTE, MC GSM, W-CDMA, TD-SCDMA

- LMDS/MMDS, point-to-point microwave backhaul

- Direct Digital Synthesis (DDS) instruments

- High-definition video broadcast production equipment

- Automated Test Equipment (ATE)

# 4. Ordering information

Table 1. Ordering information

| Type number      | Package | Package                           |          |  |  |  |  |  |

|------------------|---------|-----------------------------------|----------|--|--|--|--|--|

|                  | Name    | Description                       | Version  |  |  |  |  |  |

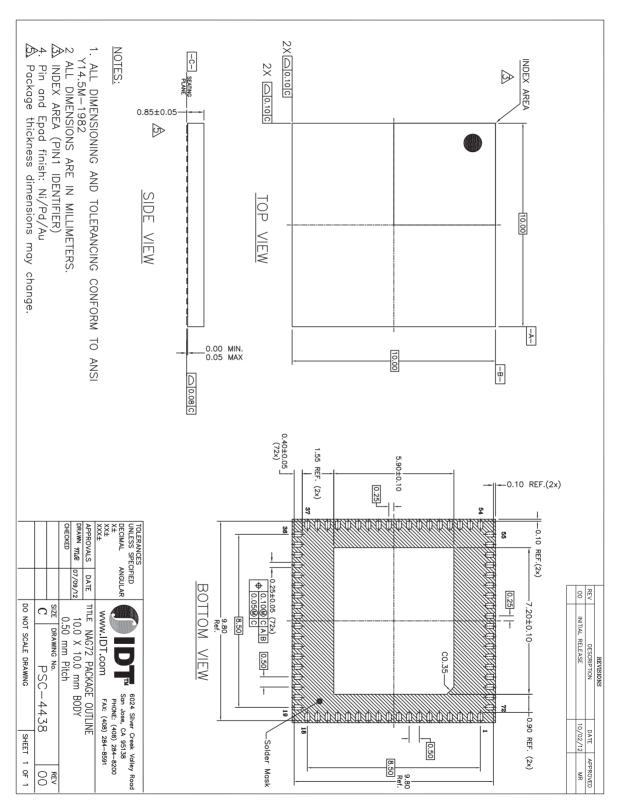

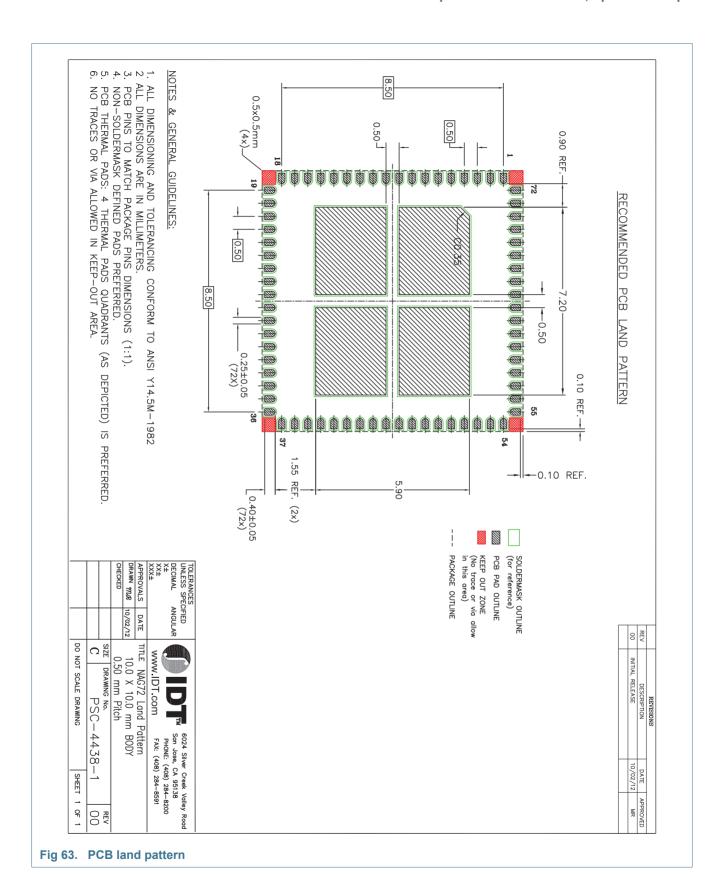

| DAC1653Q1G5NAGA  | HLA72   | HLA $10 \times 10 \times 0.85$ mm | PSC-4438 |  |  |  |  |  |

| DAC1653Q1G25NAGA | HLA72   | HLA $10 \times 10 \times 0.85$ mm | PSC-4438 |  |  |  |  |  |

| DAC1653Q1G0NAGA  | HLA72   | HLA $10 \times 10 \times 0.85$ mm | PSC-4438 |  |  |  |  |  |

| DAC1658Q1G5NAGA  | HLA72   | HLA $10 \times 10 \times 0.85$ mm | PSC-4438 |  |  |  |  |  |

| DAC1658Q1G25NAGA | HLA72   | HLA $10 \times 10 \times 0.85$ mm | PSC-4438 |  |  |  |  |  |

| DAC1658Q1G0NAGA  | HLA72   | HLA $10 \times 10 \times 0.85$ mm | PSC-4438 |  |  |  |  |  |

# 5. Block diagram

# 6. Pinning information

### 6.1 Pinning

### 6.2 Pin description

Table 2. Pin description

| Pin | Symbol                | Туре | Description                                  |

|-----|-----------------------|------|----------------------------------------------|

| 1   | $V_{DDA(out)}$        | Р    | DAC1658Q: 3.3 V analog power supply          |

|     |                       |      | DAC1653Q: 2.5 V or 3.3 V analog power supply |

| 2   | V <sub>DDA(1V2)</sub> | Р    | 1.2 V analog power supply                    |

| 3   | CLKIN_P               | I    | clock input (positive)                       |

| 4   | CLKIN_N               | I    | clock input (negative)                       |

Table 2. Pin description ...continued

| Pin | Symbol                | Type | Description                                                 |

|-----|-----------------------|------|-------------------------------------------------------------|

| 5   | $V_{DDA(out)}$        | Р    | DAC1658Q: 3.3 V analog power supply                         |

|     |                       |      | DAC1653Q: 2.5 V or 3.3 V analog power supply                |

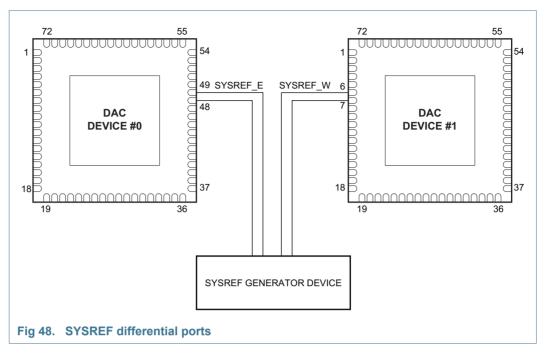

| 6   | SYSREF_W_P            | I/O  | multiple devices synchronization positive signal, west side |

| 7   | SYSREF_W_N            | I/O  | multiple devices synchronization negative signal, west side |

| 8   | $V_{DDD(1V2)}$        | Р    | 1.2 V digital power supply                                  |

| 9   | GND                   | G    | ground                                                      |

| 10  | IO0                   | I/O  | IO port bit 0                                               |

| 11  | IO1                   | I/O  | IO port bit 1                                               |

| 12  | GND                   | I    | ground                                                      |

| 13  | IO2                   | I/O  | IO port bit 2                                               |

| 14  | IO3                   | I/O  | IO port bit 3                                               |

| 15  | V <sub>DDD(1V2)</sub> | Р    | 1.2 V digital power supply                                  |

| 16  | $V_{DDJ(1V2)}$        | Р    | 1.2 V JEDEC204B interface power supply                      |

| 17  | SYNCB_AB_P            | 0    | JESD204B SYNC signal for DACs A/B (positive)                |

| 18  | SYNCB_AB_N            | 0    | JESD204B SYNC signal for DACs A/B (negative)                |

| 19  | VIN_AB_P0             | I    | DAC A/B lane 0 serial interface, positive input             |

| 20  | VIN_AB_N0             | I    | DAC A/B lane 0 serial interface, negative input             |

| 21  | VIN_AB_P1             | I    | DAC A/B lane 1 serial interface, positive input             |

| 22  | VIN_AB_N1             | I    | DAC A/B lane 1 serial interface, negative input             |

| 23  | $V_{DDJ(1V2)}$        | Р    | 1.2 V JEDEC204B interface power supply                      |

| 24  | VIN_AB_P2             | I    | DAC A/B lane 2 serial interface, positive input             |

| 25  | VIN_AB_N2             | I    | DAC A/B lane 2 serial interface, negative input             |

| 26  | VIN_AB_P3             | I    | DAC A/B lane 3 serial interface, positive input             |

| 27  | VIN_AB_N3             | I    | DAC A/B lane 3 serial interface, negative input             |

| 28  | VIN_CD_P0             | I    | DAC C/D lane 0 serial interface, positive input             |

| 29  | VIN_CD_N0             | I    | DAC C/D lane 0 serial interface, negative input             |

| 30  | VIN_CD_P1             | I    | DAC C/D lane 1 serial interface, positive input             |

| 31  | VIN_CD_N1             | I    | DAC C/D lane 1 serial interface, negative input             |

| 32  | V <sub>DDJ(1V2)</sub> | Р    | 1.2 V JEDEC204B interface power supply                      |

| 33  | VIN_CD_P2             | I    | DAC C/D lane 2 serial interface, positive input             |

| 34  | VIN_CD_N2             | I    | DAC C/D lane 2 serial interface, negative input             |

| 35  | VIN_CD_P3             | I    | DAC C/D lane 3 serial interface, positive input             |

| 36  | VIN_CD_N3             | I    | DAC C/D lane 3 2serial interface, negative input            |

| 37  | SYNCB_1_P             | 0    | JESD204B SYNC signal for DACs C/D (positive)                |

| 38  | SYNCB_1_N             | 0    | JESD204B SYNC signal for DACs C/D (negative)                |

| 39  | V <sub>DDJ_SO</sub>   | Р    | JEDEC204B SYNC output buffer power supply (1.2 V or 1.8 V)  |

| 40  | V <sub>DDD(1V2)</sub> | Р    | 1.2 V digital power supply                                  |

| 41  | V <sub>DDD_IO</sub>   | Р    | digital IO power supply (1.2 V or 1.8 V) (including SPI)    |

| 42  | SDO                   | 0    | SPI data output                                             |

| 43  | SDIO                  | I/O  | SPI data input/output                                       |

Table 2.

Pin description ...continued

| Pin | Symbol                | Type | Description                                                 |

|-----|-----------------------|------|-------------------------------------------------------------|

| 44  | RESET_N               | I    | general reset (active LOW)                                  |

| 45  | SCS_N                 | I    | SPI chip select (active LOW)                                |

| 46  | SCLK                  | I    | SPI clock input                                             |

| 47  | V <sub>DDD(1V2)</sub> | Р    | 1.2 V digital power supply                                  |

| 48  | SYSREF_E_N            | I/O  | multiple devices synchronization negative signal, east side |

| 49  | SYSREF_E_P            | I/O  | multiple devices synchronization positive signal, east side |

| 50  | V <sub>DDA(1V2)</sub> | Р    | 1.2 V analog power supply                                   |

| 51  | VIRES                 | I/O  | vi-biasing resistor                                         |

| 52  | GAPOUT                | I/O  | bandgap output voltage                                      |

| 53  | V <sub>DDA(1V2)</sub> | Р    | 1.2 V analog power supply                                   |

| 54  | $V_{DDA(out)}$        | Р    | DAC1658Q: 3.3 V analog power supply                         |

|     |                       |      | DAC1653Q: 2.5 V or 3.3 V analog power supply                |

| 55  | V <sub>DDA(1V2)</sub> | Р    | 1.2 V analog power supply                                   |

| 56  | IOUTD_P               | 0    | DAC D output current                                        |

| 57  | IOUTD_N               | 0    | complementary DAC D output current                          |

| 58  | V <sub>DDA(1V2)</sub> | Р    | 1.2 V analog power supply                                   |

| 59  | V <sub>DDA(1V2)</sub> | Р    | 1.2 V analog power supply                                   |

| 60  | IOUTC_N               | 0    | complementary DAC C output current                          |

| 61  | IOUTC_P               | 0    | DAC C output current                                        |

| 62  | V <sub>DDA(1V2)</sub> | Р    | 1.2 V analog power supply                                   |

| 63  | $V_{DDA(out)}$        | Р    | DAC1658Q: 3.3 V analog power supply                         |

|     |                       |      | DAC1653Q: 2.5 V or 3.3 V analog power supply                |

| 64  | V <sub>DDA(out)</sub> | Р    | DAC1658Q: 3.3 V analog power supply                         |

|     |                       |      | DAC1653Q: 2.5 V or 3.3 V analog power supply                |

| 65  | V <sub>DDA(1V2)</sub> | Р    | 1.2 V analog power supply                                   |

| 66  | IOUTB_P               | 0    | DAC B output current                                        |

| 67  | IOUTB_N               | 0    | complementary DAC B output current                          |

| 68  | V <sub>DDA(1V2)</sub> | Р    | 1.2 V analog power supply                                   |

| 69  | V <sub>DDA(1V2)</sub> | Р    | 1.2 V analog power supply                                   |

| 70  | IOUTA_N               | 0    | complementary DAC A output current                          |

| 71  | IOUTA_P               | 0    | DAC A output current                                        |

| 72  | V <sub>DDA(1V2)</sub> | Р    | 1.2 V analog power supply                                   |

# 7. Limiting values

Table 3. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                | Parameter                      | Conditions                                                                                                         | Min  | Max         | Unit |

|-----------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------|------|-------------|------|

| V <sub>DDA(out)</sub> | analog output supply           | DAC1658Q: 3.3 V                                                                                                    | -0.5 | +4.6        | V    |

|                       | voltage                        | DAC1653Q: 2.5 V or 3.3 V                                                                                           | -0.5 | +4.6        | V    |

| $V_{DDD(1V2)}$        | digital supply voltage (1.2 V) |                                                                                                                    | -0.5 | +1.5        | V    |

| V <sub>DDA(1V2)</sub> | analog supply voltage (1.2 V)  |                                                                                                                    | -0.5 | +1.5        | V    |

| VI                    | input voltage                  | input pins referenced to GND                                                                                       | -0.5 | <tbd></tbd> | V    |

| Vo                    | output voltage                 | pins IOUTA_P, IOUTA_N, IOUTB_P, IOUTB_N, IOUTC_P, IOUTC_N, IOUTD_P, IOUTD_N; IO0; IO1; IO2; IO3; referenced to GND | -0.5 | +4.6        | V    |

| $V_{DDD(IO)}$         | I/O digital supply voltage     | pins SDO, SDIO,SCLK, SCS_N,<br>RESET_N, JTAG, IO0,<br>RF_ENABLE/IO1                                                | -0.5 | 2.1         | V    |

| V <sub>DDD(SO)</sub>  | differential SYNC voltage      | pins SYNC_AB_P/N and SYNC_CD_P/N                                                                                   | -0.5 | 2.1         | V    |

| T <sub>stg</sub>      | storage temperature            |                                                                                                                    | -55  | +150        | °C   |

| T <sub>amb</sub>      | ambient temperature            |                                                                                                                    | -40  | +85         | °C   |

| Tj                    | junction temperature           |                                                                                                                    | -40  | +125        | °C   |

# 8. Thermal characteristics

Table 4. Thermal characteristics

| Symbol               | Parameter                                   | Conditions | Тур             | Unit |

|----------------------|---------------------------------------------|------------|-----------------|------|

| JEDEC 4L             | . board                                     |            |                 |      |

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient |            | [1] <tbd></tbd> | K/W  |

| R <sub>th(j-c)</sub> | thermal resistance from junction to case    |            | [1] <tbd></tbd> | K/W  |

| Application          | on board                                    |            |                 |      |

| R <sub>th(j-a)</sub> | thermal resistance from junction            | 6 layers   | [2] <tbd></tbd> | K/W  |

|                      | to ambient                                  | 8 layers   | [2] <tbd></tbd> | K/W  |

|                      |                                             | 12 layers  | [2] <tbd></tbd> | K/W  |

<sup>[1]</sup> In compliance with JEDEC test board; in free air with 64 thermal vias, class 5.

<sup>[2]</sup> In free air with 64 thermal vias, class 5.

### 9. Static characteristics

### 9.1 Common characteristics

Table 5. Characteristics

$V_{DDA(1V2)}$  = 1.2 V;  $V_{DDD(1V2)}$  = 1.2 V; Typical values measured at  $T_{amb}$  = +25 °C;  $R_L$  = 50  $\Omega$  ;  $I_{O(fs)}$  = 20 mA; maximum sample rate used; external PLL; no inverse (sinus x) / x; no output correction; output level = 1 V (p-p); unless otherwise specified.

| Symbol                | Parameter                                  | Conditions                                                 | Test[1]   |     | Min                     | Тур         | Max              | Unit |

|-----------------------|--------------------------------------------|------------------------------------------------------------|-----------|-----|-------------------------|-------------|------------------|------|

| $V_{DDA}$             | analog supply                              | DAC1658Q: 3.3 V                                            | С         |     | 3.15                    | 3.3         | 3.45             | V    |

|                       | voltage (3.3 V)                            | DAC1653Q: 2.5 V or 3.3 V                                   | С         |     | 2.38                    | 2.5 or 3.3  | 3.45             | V    |

| V <sub>DDD(1V2)</sub> | digital supply voltage (1.2 V)             |                                                            | С         |     | 1.14                    | 1.2         | 1.26             | V    |

| V <sub>DDA(1V2)</sub> | analog supply voltage (1.2 V               |                                                            | С         |     | 1.1                     | 1.2         | 1.3              | V    |

| $V_{DDD(IO)}$         | I/O digital                                | 1.2 V or 1.8 V for IOs                                     | С         |     | 1.14                    | 1.2         | 2.1              | V    |

|                       | supply voltage                             | and SPI signals                                            | С         |     | 1.14                    | 1.8         | 2.1              | V    |

| V <sub>DDD(SO)</sub>  | differential                               |                                                            | С         |     | 1.14                    | 1.2         | 2.1              | V    |

|                       | digital supply voltage                     |                                                            | С         |     | 1.14                    | 1.8         | 2.1              | V    |

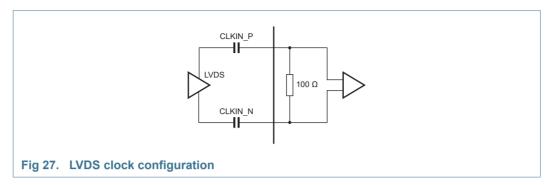

| Clock inputs          | s (pins CLKIN_P, C                         | CLKIN_N)                                                   |           |     |                         |             |                  |      |

| $V_{i}$               | input voltage                              | $ V_{gpd}  < 50 \text{ mV}$                                | С         | [2] | 825                     | -           | <tbd></tbd>      | mV   |

| V <sub>idth</sub>     | input differential<br>threshold<br>voltage | $ V_{gpd} $ < 50 mV                                        | С         | [2] | -100                    | -           | +100             | mV   |

| R <sub>i</sub>        | input resistance                           |                                                            | D         |     | -                       | 100         | -                | Ω    |

| C <sub>i</sub>        | input<br>capacitance                       |                                                            | D         |     | -                       | <tbd></tbd> | -                | pF   |

| Digital input         | ts/outputs (SYSRE                          | F_W_P/SYSREF_W_N                                           | SYSREF_   | E   | P/SYSREF_E              | _N)         |                  |      |

| Vi                    | input voltage                              | $ V_{gpd}  < 50 \text{ mV}$                                | С         | [2] | 825                     | -           | <tbd></tbd>      | mV   |

| $V_{idth}$            | input differential<br>threshold<br>voltage | $ V_{gpd}  < 50 \text{ mV}$                                | С         | [2] | -100                    | -           | +100             | mV   |

| R <sub>i</sub>        | input resistance                           |                                                            | D         |     | -                       | 100         | -                | Ω    |

| C <sub>i</sub>        | input<br>capacitance                       |                                                            | D         |     | -                       | <tbd></tbd> | -                | pF   |

| Digital input         | ts (pins SDO, SDIC                         | O, SCLK, SCS_N, RESE                                       | T_N, IO0, | 101 | , IO2, IO3)             |             |                  |      |

| V <sub>IL</sub>       | LOW-level input voltage                    |                                                            | С         |     | GND                     | -           | $0.3V_{DDD(IO)}$ | V    |

| V <sub>IH</sub>       | HIGH-level input voltage                   |                                                            | С         |     | 0.7V <sub>DDD(IO)</sub> | -           | $V_{DDD(IO)}$    | V    |

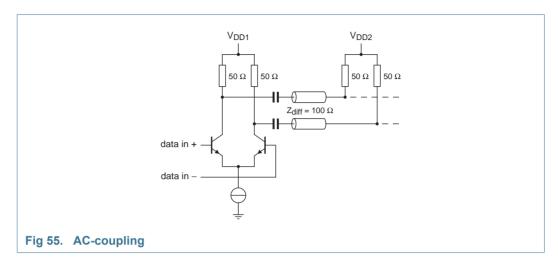

| Digital input         | ts (VINx_P/VINx_N                          | ) following the LV-OIF-                                    | 11G-SR; C | ML  | format                  |             |                  |      |

| V <sub>cm</sub>       | common-mode<br>voltage                     | AC coupling is<br>mandatory; controlled<br>by SPI register | С         |     | 0.580                   | -           | 1.126            | V    |

9 of 101

Table 5. Characteristics ...continued

$V_{DDA(1V2)}$  = 1.2 V;  $V_{DDD(1V2)}$  = 1.2 V; Typical values measured at  $T_{amb}$  = +25 °C;  $R_L$  = 50  $\Omega$ ;  $I_{O(fs)}$  = 20 mA; maximum sample rate used; external PLL; no inverse (sinus x) / x; no output correction; output level = 1 V (p-p); unless otherwise specified.

| Symbol                    | Parameter                                | Conditions                                                    | Test[1]      | Min                   | Тур          | Max                   | Unit   |

|---------------------------|------------------------------------------|---------------------------------------------------------------|--------------|-----------------------|--------------|-----------------------|--------|

| $V_{pp\text{-diff}}$      | differential                             | at 6 Gbps                                                     | С            | 80                    | -            | -                     | mV     |

|                           | peak-to-peak                             | at 7.5 Gbps                                                   | С            | 80                    | -            | -                     | mV     |

|                           | voltage                                  | at 10 Gbps                                                    | С            | 110                   | -            | -                     | mV     |

| Z <sub>diff</sub>         | differential impedance                   | controlled by SPI register                                    | I            | 71                    | 100          | 190                   | Ω      |

| Hi-Z <sub>diff</sub>      | tri-state<br>observed<br>impendance      |                                                               | D            | -                     | 64           | -                     | kΩ     |

| DR                        | data rate                                |                                                               | D            | 1                     | -            | 10                    | Gbps   |

| Digital outpu             | ts (pins SYNC_O                          | UT_P and SYNC_OUT_                                            | N)           |                       |              |                       |        |

| V <sub>cm</sub>           | common-mode voltage                      | controlled by SPI register                                    |              |                       | -            |                       |        |

|                           |                                          | $V_{DDDdif} = 1.8 V$                                          | D            | 1.0                   | -            | 1.7                   | V      |

|                           |                                          | $V_{DDDdif} = 1.3 V$                                          | D            | 0.4                   | -            | 1.2                   | V      |

|                           |                                          | $V_{DDDdif} = 1.2 V$                                          | D            | 0.4                   | -            | 1.1                   | V      |

| $V_{O(diff)(swing)}$      | swing<br>differential<br>output voltage  |                                                               | D            | 100                   | -            | 1200                  | mV     |

| Digital outpu             | ts (pins SDO, SD                         | IO)                                                           |              |                       |              |                       |        |

| $V_{OL}$                  | LOW-level output voltage                 |                                                               | С            | -                     | -            | 0.3V <sub>DDDIO</sub> | V      |

| V <sub>OH</sub>           | HIGH-level output voltage                |                                                               | С            | 0.7V <sub>DDDIO</sub> | -            | -                     | V      |

| Reference vo              | Itage output (pin                        | GAPOUT)                                                       |              |                       |              |                       |        |

| V <sub>O(ref)</sub>       | reference<br>output voltage              | T <sub>amb</sub> = 25 °C                                      | I            | -                     | 0.70         | -                     | V      |

| I <sub>O(ref)</sub>       | reference<br>output current              | external<br>voltage = 0.70 V                                  | D            | -                     | <tbd></tbd>  | -                     | μА     |

| $\Delta V_{O(ref)}$       | reference<br>output voltage<br>variation |                                                               | D            | -                     | <tbd></tbd>  | -                     | ppm/°C |

| Analog auxili             | ary outputs (only                        | y for DAC1653Q: conne                                         | cted interna | lly to the outp       | uts pins OUT | x_P/OUTx_N)           |        |

| I <sub>O(fs)</sub>        | full-scale output<br>current             | auxiliary DACs;<br>differential inputs<br>(normal resolution) | I            | -                     | 4.4          | -                     | mA     |

|                           |                                          | auxiliary DACs;<br>differential inputs (high<br>resolution)   | I            | -                     | 77.2         | -                     | μΑ     |

| $V_{O(aux)}$              | auxiliary output voltage                 |                                                               | С            | 0                     | -            | 2                     | V      |

| N <sub>DAC(aux)mono</sub> | auxiliary DAC monotonicity               | guaranteed                                                    | D            | -                     | 10           | -                     | bits   |

Quad 16-bit DAC: 10 Gbps JESD204B interface; up to 1.50 Gsps

#### Table 5. Characteristics ...continued

$V_{DDA(1V2)}$  = 1.2 V;  $V_{DDD(1V2)}$  = 1.2 V; Typical values measured at  $T_{amb}$  = +25 °C;  $R_L$  = 50  $\Omega$  ;  $I_{O(fs)}$  = 20 mA; maximum sample rate used; external PLL; no inverse (sinus x) / x; no output correction; output level = 1 V (p-p); unless otherwise specified.

| , -        | , , , ,       |                    |         | ,   | (1- 1-// |      |      |  |

|------------|---------------|--------------------|---------|-----|----------|------|------|--|

| Symbol     | Parameter     | Conditions         | Test[1] | Min | Тур      | Max  | Unit |  |

| DAC output | timing        |                    |         |     |          |      |      |  |

| $f_s$      | sampling rate | DAC165xQ1G5        | С       | -   | -        | 1500 | Msps |  |

|            |               | DAC165xQ1G25       | С       | -   | -        | 1250 | Msps |  |

|            |               | DAC165xQ1G0        | С       | -   | -        | 1000 | Msps |  |

| ts         | settling time | to = $\pm 0.5$ LSB | D       | -   | 20       | -    | ns   |  |

<sup>[1]</sup> D = guaranteed by design; C = guaranteed by characterization; I = 100 % industrially tested.

<sup>[2] |</sup>V<sub>gpd</sub>| represents the ground potential difference voltage. This is the voltage that results from current flowing through the finite resistance and the inductance between the receiver and the driver circuit ground voltages.

Integrated

Device

Technology

# 9.2 Specific characteristics

### Table 6. Specific characteristics

$V_{DDA1V2}$  = 1.2 V;  $V_{DDD1V2}$  = 1.2 V; Typical values measured at  $T_{amb}$  = +25 °C;  $R_L$  = 50  $\Omega$ ;  $I_{O(fs)}$  = 20 mA; maximum sample rate used; no inverse (sinus x) / x; no output correction; output level = 1 V (p-p); unless otherwise specified.

| Symbol                   | Parameter                                | Conditions                                                                           | Test | DAC1658<br>High com | Q:<br>ımon-mode | e   | DAC1653Q:<br>Low common-mode |             |     | Unit |

|--------------------------|------------------------------------------|--------------------------------------------------------------------------------------|------|---------------------|-----------------|-----|------------------------------|-------------|-----|------|

|                          |                                          |                                                                                      |      | Min                 | Тур             | Max | Min                          | Тур         | Max |      |

| Currents                 |                                          |                                                                                      |      |                     |                 |     | ·                            |             |     |      |

| $I_{DDA}$                | analog supply current (3.3 V)            | all use cases                                                                        | С    | -                   | 126             | -   | -                            | 246         | -   | mA   |

| I <sub>DDD(IO)</sub>     | digital supply<br>current for IO<br>pins | Link to SPI IO0/IO1/IO2/IO3 activity                                                 | С    | -                   | 2               | -   | -                            | 2           | -   | mA   |

| I <sub>DDD(SYNC)</sub>   | digital supply                           | $V_{DDD(diff)} = 1.2 V$                                                              | С    | -                   | 22              | -   | -                            | 22          | -   | mA   |

| current for<br>SYNC pins | $V_{DDD(diff)} = 1.8 V$                  | С                                                                                    | -    | 38                  | -               | -   | 38                           | -           | mA  |      |

| I <sub>DDD</sub>         | digital supply current                   | NCO off;×2 interpolation;; MDS off; invsinc off, phase correction off                |      |                     |                 |     |                              |             |     |      |

|                          |                                          | f <sub>s</sub> = 983.04 Msps                                                         | С    | -                   | 394             | -   | -                            | 394         | -   | mA   |

|                          |                                          | f <sub>s</sub> = 1228.8 Msps                                                         | С    | -                   | <tbd></tbd>     | -   | -                            | <tbd></tbd> | -   | mA   |

|                          |                                          | f <sub>s</sub> = 1474.56 Msps                                                        | С    | -                   | 548             | -   | -                            | 548         | -   | mA   |

|                          |                                          | f <sub>s</sub> = 1760.00 Msps                                                        | С    | -                   | <tbd></tbd>     | -   | -                            | <tbd></tbd> | -   | mA   |

|                          |                                          | NCO on at 150 MHz;×2 interpolation;;<br>MDS off; invsinc off, phase correction<br>on |      |                     |                 |     |                              |             |     |      |

|                          |                                          | f <sub>s</sub> = 983.04 Msps                                                         | С    | -                   | <tbd></tbd>     | -   | -                            | <tbd></tbd> | -   | mA   |

|                          |                                          | f <sub>s</sub> = 1228.8 Msps                                                         | С    | -                   | <tbd></tbd>     | -   | -                            | <tbd></tbd> | -   | mA   |

|                          |                                          | f <sub>s</sub> = 1474.56 Msps                                                        | С    | -                   | 680             | -   | -                            | 680         | -   | mA   |

|                          |                                          | f <sub>s</sub> = 1760.00 Msps                                                        | С    | -                   | <tbd></tbd>     | -   | -                            | <tbd></tbd> | -   | mA   |

| I <sub>DDA(1V2)</sub>    | analog supply current                    | $V_{DDA(1V2)} = 1.2 \text{ V}$                                                       | С    | -                   | 412             | -   | -                            | 412         | -   | mA   |

Advance data sheet

Table 6.

Specific characteristics ...continued

$V_{DDA1V2}$  = 1.2 V;  $V_{DDD1V2}$  = 1.2 V; Typical values measured at  $T_{amb}$  = +25 °C;  $R_L$  = 50  $\Omega$ ;  $I_{O(fs)}$  = 20 mA; maximum sample rate used; no inverse (sinus x) / x; no output correction; output level = 1 V (p-p); unless otherwise specified.

| Symbol             | Parameter                                                               | Conditions                                                                             | Test | DAC1658<br>High cor | BQ:<br>nmon-mode | )   | DAC1653Q:<br>Low common-mode |             |     |    |

|--------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------|---------------------|------------------|-----|------------------------------|-------------|-----|----|

|                    |                                                                         |                                                                                        |      | Min                 | Тур              | Max | Min                          | Тур         | Max |    |

| Power              | '                                                                       |                                                                                        | '    |                     |                  |     |                              |             | '   | '  |

| P <sub>tot</sub>   | total power dissipation                                                 | NCO off;×2 interpolation;; MDS off; invsinc off, phase correction off                  |      |                     |                  |     |                              |             |     |    |

|                    |                                                                         | $V_{DDA}$ = 3.3 V; all $V_{DDD}$ = 1.2 V                                               |      |                     |                  |     |                              |             |     |    |

|                    | f <sub>s</sub> = 983.04 Msps;<br>eight JESD204B lanes at<br>4.9152 Gbps | С                                                                                      | -    | 1486                | -                | -   | 1982                         | -           | mW  |    |

|                    | f <sub>s</sub> = 1228.8 Msps;<br>eight JESD204B lanes at<br>6.144 Gbps  | С                                                                                      | -    | <tbd></tbd>         | -                | -   | <tbd></tbd>                  | -           | mW  |    |

|                    |                                                                         | f <sub>s</sub> = 1474.56 Msps;<br>eight JESD204B lanes at<br>7.3728 Gbps               | С    | -                   | 1770             | -   | -                            | 2166        | -   | mW |

|                    |                                                                         | $V_{DDA}$ = 2.5 V; all $V_{DDD}$ = 1.2 V                                               |      |                     |                  |     |                              |             |     |    |

|                    |                                                                         | f <sub>s</sub> = 983.04 Msps;<br>eight JESD204B lanes at<br>4.9152 Gbps                | С    |                     | n.a.             |     | -                            | 1786        | -   | mW |

|                    |                                                                         | f <sub>s</sub> = 1228.8 Msps;<br>eight JESD204B lanes at<br>6.144 Gbps                 | С    |                     | n.a.             |     | -                            | <tbd></tbd> | -   | mW |

|                    |                                                                         | f <sub>s</sub> = 1474.56 Msps;<br>eight JESD204B lanes at<br>7.3728 Gbps               | С    |                     | n.a.             |     | -                            | 1970        | -   | mW |

|                    |                                                                         | full power-down                                                                        | С    | -                   | 12               | -   | -                            | 12          | -   | mW |

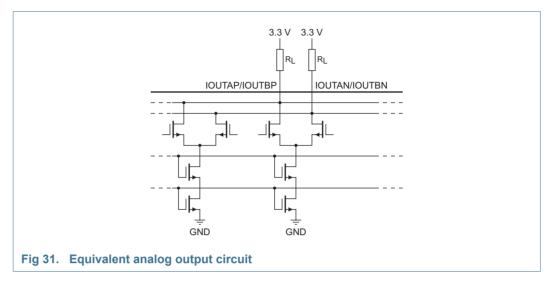

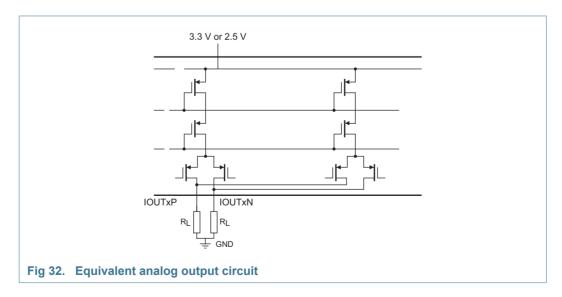

| Analog o           | utputs (pins IOUTA                                                      | _P, IOUTA_N, IOUTB_P, IOUTB_N)                                                         |      |                     |                  |     |                              |             |     |    |

| $I_{O(fs)}$        | full-scale output current                                               |                                                                                        | D    | 8.1                 | -                | 34  | 8.1                          | -           | 34  | mA |

| I <sub>O(dc)</sub> | DC output<br>current                                                    | this DC offset is to be taken into account into filter design and component connection | D    | -                   | 4                | -   | -                            | 4           | -   | mA |

AC1653Q/DAC1658

Table 6.

Specific characteristics ...continued

$V_{DDA1V2}$  = 1.2 V;  $V_{DDD1V2}$  = 1.2 V; Typical values measured at  $T_{amb}$  = +25 °C;  $R_L$  = 50  $\Omega$ ;  $I_{O(fs)}$  = 20 mA; maximum sample rate used; no inverse (sinus x) / x; no output correction; output level = 1 V (p-p); unless otherwise specified.

| Symbol Parameter   | Parameter                             | Conditions | Test |     |      |           | DAC1653Q:<br>Low common-mode |      |     | Unit |

|--------------------|---------------------------------------|------------|------|-----|------|-----------|------------------------------|------|-----|------|

|                    |                                       |            |      | Min | Тур  | Max       | Min                          | Тур  | Max |      |

| $V_{O}$            | output voltage                        |            | D    | 1.5 | -    | $V_{DDA}$ | 0                            | _    | 1.8 | V    |

| V <sub>O(cm)</sub> | common-mode output voltage            |            | D    | 2.2 | 3.05 | -         | -                            | 0.25 | -   | V    |

| R <sub>o</sub>     | output<br>resistance                  |            | D    | -   | 250  | -         | -                            | 250  | -   | kΩ   |

| Co                 | differential<br>output<br>capacitance |            | D    | -   | 5    | -         | -                            | 5    | -   | pF   |

<sup>[1]</sup> D = guaranteed by design; C = guaranteed by characterization; I = 100 % industrially tested.

Integrated

Device

Technology

# 10. Dynamic characteristics

Table 7. Dynamic characteristics DAC165xQ1G5

$V_{DDA1V2} = 1.2$  V;  $V_{DDD1V2} = 1.2$  V; Typical values measured at  $T_{amb} = +25$  °C; RL = 50  $\Omega$ ;  $I_{O(fs)} = 20$  mA; maximum sample rate used; no auxiliary DAC; no inverse (sinus x) / x; no output correction; output level = 1 V (p-p); unless otherwise specified.

| Symbol                | Parameter                      | Conditions                                                                     | Test [1] | DAC1658<br>High cor | BQ:<br>nmon-mode |     | DAC1653C<br>Low comm |             |     | Unit |

|-----------------------|--------------------------------|--------------------------------------------------------------------------------|----------|---------------------|------------------|-----|----------------------|-------------|-----|------|

|                       |                                |                                                                                |          | Min                 | Тур              | Max | Min                  | Тур         | Max |      |

| SFDR                  | spurious-free<br>dynamic range | $f_{data}$ = 737.28 MHz; $f_s$ = 1474.56 Msps;<br>B = $f_s$ / 2                |          |                     |                  |     |                      |             |     |      |

|                       |                                | $V_{DDA} = 3.3 \text{ V; } f_0 = 20 \text{ MHz}$                               |          |                     |                  |     |                      |             |     |      |

|                       |                                | at –1 dBFS                                                                     | I        | -                   | 85               | -   | -                    | 85          | -   | dBc  |

|                       |                                | at –7 dBFS                                                                     | I        | -                   | <tbd></tbd>      | -   | -                    | <tbd></tbd> | -   | dBc  |

|                       |                                | at –14 dBFS                                                                    | I        | -                   | <tbd></tbd>      | -   | -                    | <tbd></tbd> | -   | dBc  |

|                       |                                | $V_{DDA} = 3.3 \text{ V}; f_0 = 150 \text{ MHz}$                               |          |                     |                  |     |                      |             |     |      |

|                       |                                | at –1 dBFS                                                                     | 1        | -                   | 83               | -   | -                    | 81          | -   | dBc  |

|                       |                                | at –7 dBFS                                                                     | 1        | -                   | <tbd></tbd>      | -   | -                    | <tbd></tbd> | -   | dBc  |

|                       |                                | at –14 dBFS                                                                    | 1        | -                   | <tbd></tbd>      | -   | -                    | <tbd></tbd> | -   | dBc  |

|                       |                                | $V_{DDA} = 2.5 \text{ V}; f_0 = 20 \text{ MHz}$                                |          |                     |                  |     |                      |             |     |      |

|                       |                                | at −1 dBFS                                                                     | 1        |                     | n.a.             |     | -                    | 83          | -   | dBc  |

|                       |                                | at –7 dBFS                                                                     | 1        |                     | n.a.             |     | -                    | <tbd></tbd> | -   | dBc  |

|                       |                                | at –14 dBFS                                                                    | 1        |                     | n.a              |     | -                    | <tbd></tbd> | -   | dBc  |

|                       |                                | $V_{DDA}$ = 2.5 V; $f_0$ = 150 MHz                                             |          |                     |                  |     |                      |             |     |      |

|                       |                                | at −1 dBFS                                                                     | 1        |                     | n.a.             |     | -                    | 81          | -   | dBc  |

|                       |                                | at –7 dBFS                                                                     | 1        |                     | n.a.             |     | -                    | <tbd></tbd> | -   | dBc  |

|                       |                                | at –14 dBFS                                                                    | 1        |                     | n.a.             |     | -                    | <tbd></tbd> | -   | dBc  |

| SFDR <sub>(RBW)</sub> | spurious-free                  | $V_{DDA} = 3.3 \text{ V}; f_0 = 230 \text{ MHz}$                               |          |                     |                  |     |                      |             |     |      |

|                       | dynamic range restricted       | B = 300 MHz                                                                    |          |                     |                  |     |                      |             |     |      |

|                       | bandwidth                      | at –1 dBFS                                                                     | I        | -                   | <tbd></tbd>      | -   | -                    | <tbd></tbd> | -   | dBc  |

| IMD3                  | third-order intermodulation    | $V_{DDA}$ = 3.3 V; $f_{o1}$ = 20 MHz; $f_{o2}$ = 21 MHz; $-7$ dBFS per tone    | I        | -                   | 86               | -   | -                    | 86          | -   | dBc  |

|                       | distortion                     | $V_{DDA}$ = 3.3 V; $f_{o1}$ = 230 MHz;<br>$f_{o2}$ = 231 MHz; -7 dBFS per tone | I        | -                   | 84               | -   | -                    | 82          | -   | dBc  |

Advance data sheet

Table 7. **Dynamic characteristics DAC165xQ1G5** ...continued

$V_{DDA1V2}$  = 1.2 V;  $V_{DDD1V2}$  = 1.2 V; Typical values measured at  $T_{amb}$  = +25 °C; RL = 50  $\Omega$ ;  $I_{O(fs)}$  = 20 mA; maximum sample rate used; no auxiliary DAC; no inverse (sinus x) / x; no output correction; output level = 1 V (p-p); unless otherwise specified.

| AC1658O | Symbol   | Parameter              | Conditions                                 | Test<br>[1] |     |             |     | DAC1653Q<br>Low comm |             |     | Unit   |

|---------|----------|------------------------|--------------------------------------------|-------------|-----|-------------|-----|----------------------|-------------|-----|--------|

|         |          |                        |                                            |             | Min | Тур         | Max | Min                  | Тур         | Max |        |

|         | ACPR     | adjacent               | f <sub>o</sub> = 40 MHz                    |             |     |             |     |                      |             |     |        |

|         |          | channel power ratio    | 1 WCDMA carrier; B = 5 MHz                 | С           | -   | 82          | -   | -                    | 82          | -   | dBc    |

|         |          | Tallo                  | 4 WCDMA carriers; B = 20 MHz               | С           | -   | 75          | -   | -                    | 75          | -   | dBc    |

|         | ALT-ACPR | Alternate              | f <sub>o</sub> = 40 MHz                    |             |     |             |     |                      |             |     |        |

|         |          | channel power ratio    | 1 WCDMA carrier; B = 5 MHz                 | С           | -   | <tbd></tbd> | -   | -                    | <tbd></tbd> | -   | dBc    |

|         |          | Tallo                  | 4 WCDMA carriers; B = 20 MHz               | С           | -   | <tbd></tbd> | -   | -                    | <tbd></tbd> | -   | dBc    |

|         | NSD      | noise spectral density | $f_0 = 20 \text{ MHz at } -1 \text{ dBFS}$ | С           | -   | -164        | -   | -                    | -162        | -   | dBm/Hz |

<sup>[1]</sup> D = guaranteed by design; C = guaranteed by characterization; I = 100 % industrially tested.

Integrated

Device

Technology

Table 8. Dynamic characteristics DAC165xQ1G25

$V_{DDA1V2}$  = 1.2 V;  $V_{DDD1V2}$  = 1.2 V; Typical values measured at  $T_{amb}$  = +25 °C; RL = 50  $\Omega$  ;  $I_{O(fs)}$  = 20 mA; maximum sample rate used; no auxiliary DAC; no inverse (sinus x) / x; no output correction; output level = 1 V (p-p); unless otherwise specified.

| Symbol                | bol Parameter Conditions       |                                                                                |            | High con | nmon-mode   |     | Low comm |             | Unit |     |

|-----------------------|--------------------------------|--------------------------------------------------------------------------------|------------|----------|-------------|-----|----------|-------------|------|-----|

|                       |                                |                                                                                | <u>[1]</u> | Min      | Тур         | Max | Min      | Тур         | Max  |     |

| SFDR                  | spurious-free<br>dynamic range | $f_{data}$ = 614.4 MHz; $f_s$ = 1228.8 Msps;<br>B = $f_s$ / 2                  |            |          |             |     |          |             |      |     |

|                       |                                | $V_{DDA} = 3.3 \text{ V}; f_0 = 20 \text{ MHz}$                                |            |          |             |     |          |             |      |     |

|                       |                                | at -1 dBFS                                                                     | I          | -        | 85          | -   | -        | 85          | -    | dBc |

|                       |                                | at –7 dBFS                                                                     | I          | -        | <tbd></tbd> | -   | -        | <tbd></tbd> | -    | dBc |

|                       |                                | at –14 dBFS                                                                    | I          | -        | <tbd></tbd> | -   | -        | <tbd></tbd> | -    | dBc |

|                       |                                | $V_{DDA} = 3.3 \text{ V}; f_0 = 150 \text{ MHz}$                               |            |          |             |     |          |             |      |     |

|                       |                                | at -1 dBFS                                                                     | I          | -        | 83          | -   | -        | 81          | -    | dBc |

|                       |                                | at –7 dBFS                                                                     | I          | -        | <tbd></tbd> | -   | -        | <tbd></tbd> | -    | dBc |

|                       |                                | at –14 dBFS                                                                    | I          | -        | <tbd></tbd> | -   | -        | <tbd></tbd> | -    | dBc |

|                       |                                | $V_{DDA} = 2.5 \text{ V}; f_0 = 20 \text{ MHz}$                                |            |          |             |     |          |             |      |     |

|                       |                                | at -1 dBFS                                                                     | I          |          | n.a.        |     | -        | 83          | -    | dBc |

|                       |                                | at –7 dBFS                                                                     | I          |          | n.a.        |     | -        | <tbd></tbd> | -    | dBc |

|                       |                                | at –14 dBFS                                                                    | I          |          | n.a         |     | -        | <tbd></tbd> | -    | dBc |

|                       |                                | $V_{DDA} = 2.5 \text{ V}; f_0 = 150 \text{ MHz}$                               |            |          |             |     |          |             |      |     |

|                       |                                | at −1 dBFS                                                                     | I          |          | n.a.        |     | -        | 81          | -    | dBc |

|                       |                                | at –7 dBFS                                                                     | I          |          | n.a.        |     | -        | <tbd></tbd> | -    | dBc |

|                       |                                | at –14 dBFS                                                                    | I          |          | n.a.        |     | -        | <tbd></tbd> | -    | dBc |

| SFDR <sub>(RBW)</sub> | dynamic range                  | $V_{DDA} = 3.3 \text{ V}; f_0 = 230 \text{ MHz}$<br>B = 300 MHz                |            |          |             |     |          |             |      |     |

|                       | restricted<br>bandwidth        | at –1 dBFS                                                                     | I          | -        | <tbd></tbd> | -   | -        | <tbd></tbd> | -    | dBc |

| IMD3                  | third-order intermodulation    | $V_{DDA}$ = 3.3 V; $f_{o1}$ = 20 MHz; $f_{o2}$ = 21 MHz; $-7$ dBFS per tone    | I          | -        | 86          | -   | -        | 86          | -    | dBc |

|                       | distortion                     | $V_{DDA}$ = 3.3 V; $f_{o1}$ = 230 MHz;<br>$f_{o2}$ = 231 MHz; -7 dBFS per tone | I          | -        | 84          | -   | -        | 82          | -    | dBc |

| ACPR                  | adjacent                       | f <sub>o</sub> = 40 MHz                                                        |            |          |             |     |          |             |      |     |

|                       | channel power ratio            | 1 WCDMA carrier; B = 5 MHz                                                     | С          | -        | 82          | -   | -        | 82          | -    | dBc |

|                       | Tado                           | 4 WCDMA carriers; B = 20 MHz                                                   | С          | -        | 75          | -   | -        | 75          | -    | dBc |

Advance data sheet

Table 8. **Dynamic characteristics DAC165xQ1G25** ...continued

$V_{DDA1V2}$  = 1.2 V;  $V_{DDD1V2}$  = 1.2 V; Typical values measured at  $T_{amb}$  = +25 °C; RL = 50  $\Omega$ ;  $I_{O(fs)}$  = 20 mA; maximum sample rate used; no auxiliary DAC; no inverse (sinus x) / x; no output correction; output level = 1 V (p-p); unless otherwise specified.

| AC1658Q | Symbol   | Parameter              | Conditions                   | Test [1] | High con | nmon-mode   | )   | Low comm  | on-mode     |     | Unit   |

|---------|----------|------------------------|------------------------------|----------|----------|-------------|-----|-----------|-------------|-----|--------|

| õ       |          |                        |                              |          | Min      | Тур         | Max | c Min Typ |             | Max |        |

|         | ALT-ACPR | Alternate              | $f_0 = 40 \text{ MHz}$       |          |          |             |     |           |             |     |        |

|         |          | channel power ratio    | 1 WCDMA carrier; B = 5 MHz   | С        | -        | <tbd></tbd> | -   | -         | <tbd></tbd> | -   | dBc    |

|         |          | ratio                  | 4 WCDMA carriers; B = 20 MHz | С        | -        | <tbd></tbd> | -   | -         | <tbd></tbd> | -   | dBc    |

|         | NSD      | noise spectral density | $f_0$ = 20 MHz at $-1$ dBFS  | С        | -        | -164        | -   | -         | -162        | -   | dBm/Hz |

<sup>[1]</sup> D = guaranteed by design; C = guaranteed by characterization; I = 100 % industrially tested.

Integrated

Device

Technology

| Symbol                | Parameter                      | Conditions                                                                     | Test | High cor | mmon-mode   |     | Low comm | on-mode     |     | Unit |

|-----------------------|--------------------------------|--------------------------------------------------------------------------------|------|----------|-------------|-----|----------|-------------|-----|------|

| - <b>,</b>            |                                |                                                                                | [1]  | Min      | Тур         | Max | Min      | Тур         | Max |      |

| SFDR                  | spurious-free<br>dynamic range | $f_{data}$ = 491.52 MHz; $f_s$ = 983.04 Msps;<br>B = $f_s$ / 2                 |      |          |             |     |          |             |     |      |

|                       |                                | $V_{DDA} = 3.3 \text{ V; } f_0 = 20 \text{ MHz}$                               |      |          |             |     |          |             |     |      |

|                       |                                | at -1 dBFS                                                                     | I    | -        | 85          | -   | -        | 85          | -   | dBc  |

|                       |                                | at –7 dBFS                                                                     | I    | -        | <tbd></tbd> | -   | -        | <tbd></tbd> | -   | dBc  |

|                       |                                | at -14 dBFS                                                                    | I    | -        | <tbd></tbd> | -   | -        | <tbd></tbd> | -   | dBc  |

|                       |                                | $V_{DDA} = 3.3 \text{ V; } f_0 = 150 \text{ MHz}$                              |      |          |             |     |          |             |     |      |

|                       |                                | at –1 dBFS                                                                     | 1    | -        | 83          | -   | -        | 81          | -   | dBc  |

|                       |                                | at –7 dBFS                                                                     | 1    | -        | <tbd></tbd> | -   | -        | <tbd></tbd> | -   | dBc  |

|                       |                                | at –14 dBFS                                                                    | 1    | -        | <tbd></tbd> | -   | -        | <tbd></tbd> | -   | dBc  |

|                       |                                | $V_{DDA} = 2.5 \text{ V; } f_0 = 20 \text{ MHz}$                               |      |          |             |     |          |             |     |      |

|                       |                                | at –1 dBFS                                                                     | I    |          | n.a.        |     | -        | 83          | -   | dBc  |

|                       |                                | at –7 dBFS                                                                     | I    |          | n.a.        |     | -        | <tbd></tbd> | -   | dBc  |

|                       |                                | at –14 dBFS                                                                    | I    |          | n.a         |     | -        | <tbd></tbd> | -   | dBc  |

|                       |                                | $V_{DDA} = 2.5 \text{ V}; f_0 = 150 \text{ MHz}$                               |      |          |             |     |          |             |     |      |

|                       |                                | at –1 dBFS                                                                     | I    |          | n.a.        |     | -        | 81          | -   | dBc  |

|                       |                                | at –7 dBFS                                                                     | I    |          | n.a.        |     | -        | <tbd></tbd> | -   | dBc  |

|                       |                                | at -14 dBFS                                                                    | I    |          | n.a.        |     | -        | <tbd></tbd> | -   | dBc  |

| SFDR <sub>(RBW)</sub> | spurious-free                  | $V_{DDA} = 3.3 \text{ V; } f_0 = 230 \text{ MHz}$                              |      |          |             |     |          |             |     |      |

|                       | dynamic range                  | B = 300 MHz                                                                    |      |          |             |     |          |             |     |      |

|                       | restricted<br>bandwidth        | at -1 dBFS                                                                     | 1    | -        | <tbd></tbd> | -   | -        | <tbd></tbd> | -   | dBc  |

| IMD3                  | third-order intermodulation    | $V_{DDA}$ = 3.3 V; $f_{o1}$ = 20 MHz; $f_{o2}$ = 21 MHz; –7 dBFS per tone      | I    | -        | 86          | -   | -        | 86          | -   | dBc  |

|                       | distortion                     | $V_{DDA}$ = 3.3 V; $f_{o1}$ = 230 MHz;<br>$f_{o2}$ = 231 MHz; -7 dBFS per tone | 1    | -        | 84          | -   | -        | 82          | -   | dBc  |

| ACPR                  | adjacent                       | f <sub>o</sub> = 40 MHz                                                        |      |          |             |     |          |             |     |      |

|                       | channel power ratio            | 1 WCDMA carrier; B = 5 MHz                                                     | С    | -        | 82          | -   | -        | 82          | -   | dBc  |

|                       | ialio                          | 4 WCDMA carriers; B = 20 MHz                                                   | С    | -        | 75          | -   | -        | 75          | -   | dBc  |

Advance data sheet

Table 9. Dynamic characteristics DAC16QxD1G0 ...continued

$V_{DDA1V2}$  = 1.2 V;  $V_{DDD1V2}$  = 1.2 V; Typical values measured at  $T_{amb}$  = +25 °C; RL = 50  $\Omega$ ;  $I_{O(fs)}$  = 20 mA; maximum sample rate used; no auxiliary DAC; no inverse (sinus x) / x; no output correction; output level = 1 V (p-p); unless otherwise specified.

| AC1658Q | Symbol   | Parameter              | Conditions                   | Test [1] | High con | nmon-mode   | )   | Low comm  | on-mode     |     | Unit   |

|---------|----------|------------------------|------------------------------|----------|----------|-------------|-----|-----------|-------------|-----|--------|

| õ       |          |                        |                              |          | Min      | Тур         | Max | c Min Typ |             | Max |        |

|         | ALT-ACPR | Alternate              | $f_0 = 40 \text{ MHz}$       |          |          |             |     |           |             |     |        |

|         |          | channel power ratio    | 1 WCDMA carrier; B = 5 MHz   | С        | -        | <tbd></tbd> | -   | -         | <tbd></tbd> | -   | dBc    |

|         |          | ratio                  | 4 WCDMA carriers; B = 20 MHz | С        | -        | <tbd></tbd> | -   | -         | <tbd></tbd> | -   | dBc    |

|         | NSD      | noise spectral density | $f_0$ = 20 MHz at $-1$ dBFS  | С        | -        | -164        | -   | -         | -162        | -   | dBm/Hz |

<sup>[1]</sup> D = guaranteed by design; C = guaranteed by characterization; I = 100 % industrially tested.

Quad 16-bit DAC: 10 Gbps JESD204B interface; up to 1.50 Gsps

# 11. Application information

### 11.1 General description

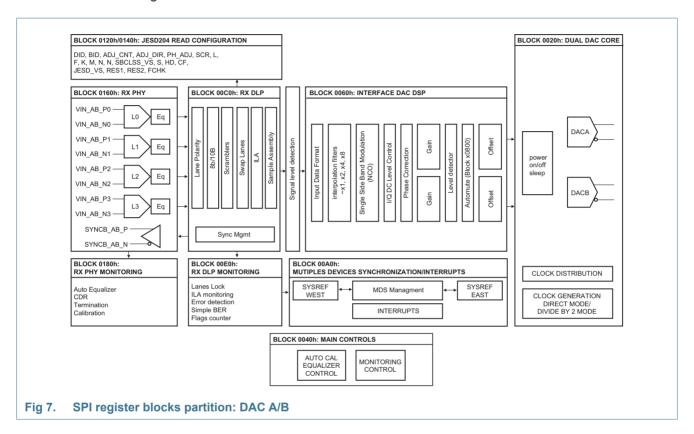

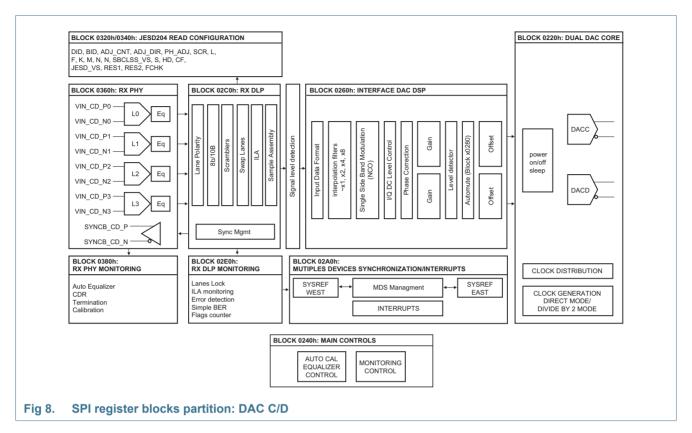

The DAC165xQ is a quad 16-bit DAC operating up to 1.50 Gsps. A maximum input data rate up to 750 Msps is supported to enable more capability for wideband and multicarrier systems. The incorporated quadrature modulators and 40-bit Numerically Controlled Oscillators (NCOs) simplify the frequency selection of the system. This is also possible because of the ×2, ×4 or ×8 interpolation filters which remove undesired images.

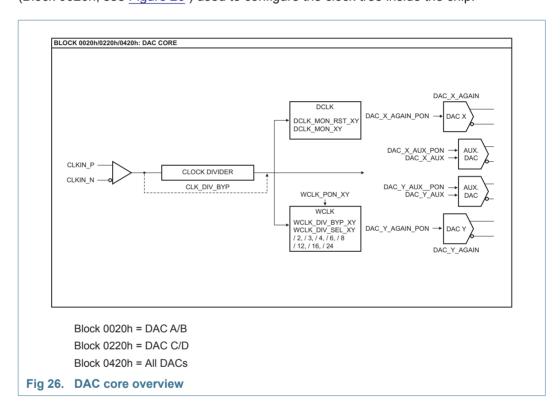

The DAC165xQ embeds four DAC channels (A, B, C and D) that can be configured as a single quad DAC (A/B/C/D) or two dual DACs (A/B and C/D). The two NCOs are linked to the A/B and the C/D dual DACs, respectively. Regarding the quad/dual mode used, the eight JESD204B lanes are configured as one single link configuration JESD204 link (one SYNC signal for a specified number of lanes), or dual link configuration JESD204B links (two SYNC signals associated with a specified number of lanes).

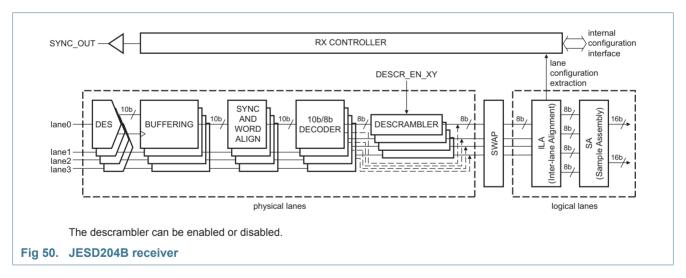

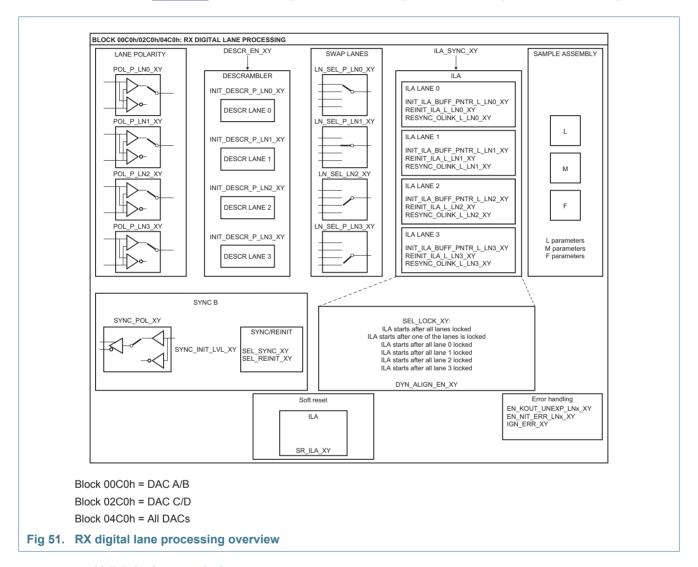

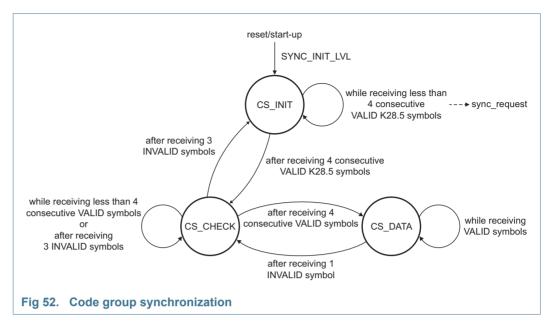

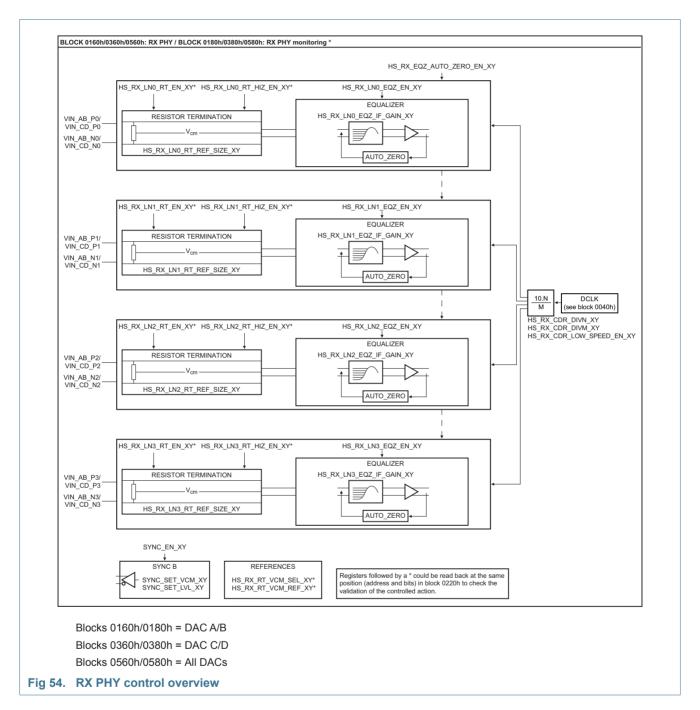

The DAC165xQ supports the following JESD204B key features:

- 10-bit/8-bit decoding

- Code group synchronization

- Initial-Lane Alignment (ILA)

- 1 + x<sup>14</sup> + x<sup>15</sup> scrambling polynomial

- Character replacement

- TX/RX synchronization management via synchronization signals

- Multiple Converter Device Alignment-Multiple Lanes (MCDA-ML) device

- Number L of serial lanes: 1, 2, 4, 8 (see LMF configuration table)

- Number M of data converters: 1, 2 or 4 (see LMF configuration table)

- Number F of octets per frame: 1, 2, 4, 6, 8 (see LMF configuration table)

- Number S of samples per frame: 1, 2 (see LMF configuration table)

- Embedded test pattern (PRBS7; PRBS15; PRBS23, PRBS31, JTSPAT, STLTP)

The DAC165xQ can be interfaced with any logic device that features high-speed SERializer/DESerializer (SERDES) functionality. This macro is now widely available in Field-Programmable Gate Array (FPGA) of different vendors. Standalone SERDES ICs can also be used.

The device includes polarity swapping for each of the lanes and additionally offers lane swapping to enhance the intrinsic board layout simplification of the JESD204B standard. Each physical lane can be configured logically as any lane number.

This device is MCDA-ML compliant, offering inter-lane alignment between several devices. An IDT proprietary mechanism in combination with the JESD204B subclass I clause enables maintenance of sample alignment between devices up to the final analog output stage. Output samples are automatically aligned to the SYSREF signal generated by a dedicated IC or by the FPGA itself. A system with several DAC165xQs can produce data with a guaranteed alignment of 1 DAC output clock period. The DAC165xQ incorporates two differential SYSREF ports (located on opposite sides of the IC). These

Quad 16-bit DAC: 10 Gbps JESD204B interface; up to 1.50 Gsps

can be programmed to act as an input or an output regarding the mode expected for the system (Normal mode, Daisy chain mode). The device also enables independent link reinitialization.

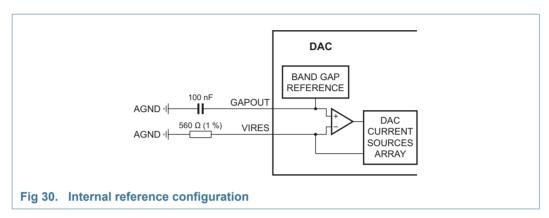

The DAC165xQ generates four complementary current outputs on pins IOUTA P/IOUTA N and IOUTB P/IOUTB N, IOUTC P/IOUTC N, and IOUTD P/IOUTD N corresponding to channel 'A', 'B', 'C', and 'D', respectively, providing a nominal full-scale output current of 20 mA. An internal reference is available for the reference current which is externally adjustable using pin VIRES.

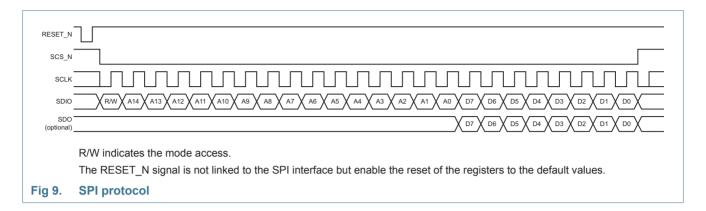

The DAC165xQ requires configuration before operating. It features an SPI slave interface to access the internal registers. Some of these registers also provide information about the JESD204B interface status. Optionally, an interrupt capability can be programmed using those registers to ensure ease of use of the device.

Because of the JESD204B standardization, the DAC165xQ does not require any adjustment from the Transmit Logic Device (TLD) to capture the input data streams. Some autolock features can be monitored using the SPI registers.

The DAC165xQ supports the following LMF configuration as described in the JESD204B standard.

Table 10. LMF configuration if DAC165xQ configures in dual JEDS204B links

| Link configuration | L-M-F | S[1] | HD[2] |

|--------------------|-------|------|-------|

| dual link          | 1-2-4 | 1    | 0     |

| dual link          | 2-2-2 | 1    | 0     |

| dual link          | 4-2-2 | 2    | 0     |

| dual link          | 4-2-1 | 1    | 1     |

| single link        | 2-4-4 | 1    | 0     |

| single link        | 4-2-2 | 1    | 0     |

| single link        | 8-4-2 | 2    | 0     |

| single link        | 8-4-1 | 1    | 1     |

<sup>[1]</sup> S is the number of samples per frame.

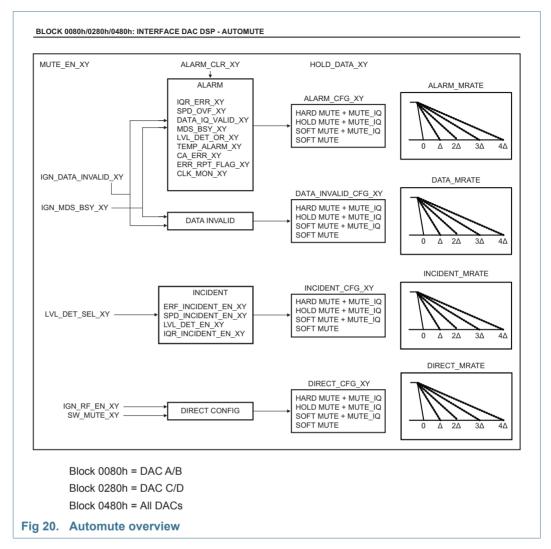

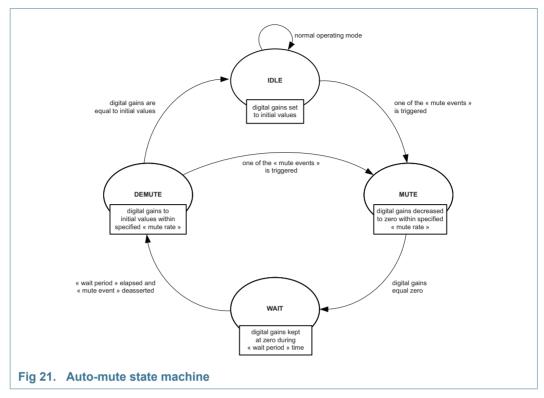

A new IDT auto-mute feature enables switching off of the RF output signal as a result of various internal events occurring.

A signal level detector allows auto-muting of the DAC outputs if they exceed the detection limit.

The DAC165xQ requires supplies of 2.5 V or 3.3 V and 1.2 V. The 1.2 V supply has separate digital and analog power supply pins.

<sup>[2]</sup> HD is the High-Density bit as described in the JESD204B specification.

Quad 16-bit DAC: 10 Gbps JESD204B interface; up to 1.50 Gsps

|                 |           | LN                      | ЛF=4:                   | 21                      |        | LN                      | ЛF=4                       | 22                      |  | LI                      | ИF=2:                  | 22                      |                         |                         | LMF       | =124                    |                        |   |  |

|-----------------|-----------|-------------------------|-------------------------|-------------------------|--------|-------------------------|----------------------------|-------------------------|--|-------------------------|------------------------|-------------------------|-------------------------|-------------------------|-----------|-------------------------|------------------------|---|--|

|                 | Lane AB0  | l <sub>AB0</sub> [15-8] | l <sub>AB1</sub> [15-8] | l <sub>AB2</sub> [15-8] |        | l <sub>AB0</sub> [15-8] | [0-7] <sub>OBO</sub> [7-0] | l <sub>AB2</sub> [15-8] |  | l <sub>AB0</sub> [15-8] | [N-0]                  | l <sub>AB1</sub> [15-8] | l <sub>AB1</sub> [17-0] | l <sub>AB0</sub> [15-8] | [7-0]     | Q <sub>AB0</sub> [15-8] | QAB <sub>0</sub> [7-0] | _ |  |

| Link AB         | Lane AB1  | [7-0]                   | [7-0]                   | [7-0]                   |        | l <sub>AB1</sub> [15-8] | [0-1] <sub>AB1</sub> [7-0] | l <sub>AB3</sub> [15-8] |  |                         |                        |                         |                         |                         |           |                         |                        |   |  |

|                 | Lane AB2  | Q <sub>AB0</sub> [15-8] | Q <sub>AB1</sub> [15-8] | Q <sub>AB2</sub> [15-8] |        | Q <sub>AB0</sub> [15-8] | QAB0[7-0]                  | Q <sub>AB2</sub> [15-8] |  | Q <sub>AB0</sub> [15-8] | QAB0[7-0]              | Q <sub>AB1</sub> [15-8] | Q <sub>AB1</sub> [7-0]  |                         |           |                         |                        |   |  |

|                 | Lane AB3  | QAB0[7-0]               | QAB1[7-0]               | QAB2[7-0]               |        | Q <sub>AB1</sub> [15-8] | Q <sub>AB1</sub> [7-0]     | Q <sub>AB3</sub> [15-8] |  |                         |                        |                         |                         |                         |           |                         |                        |   |  |

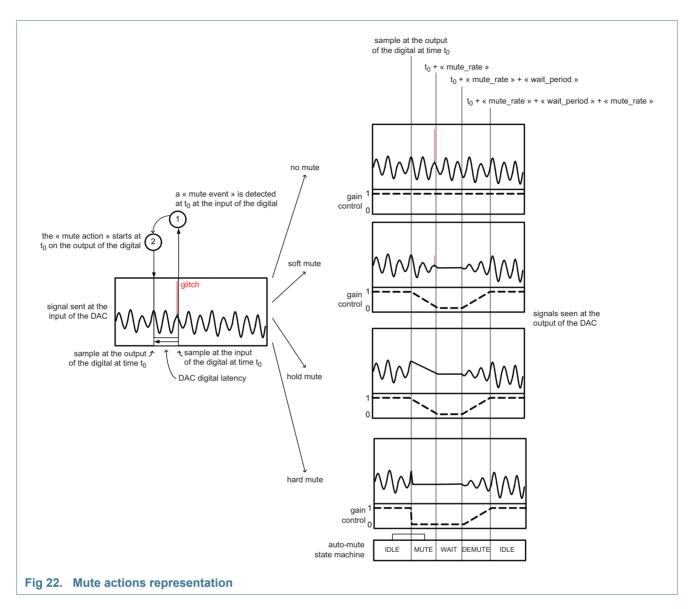

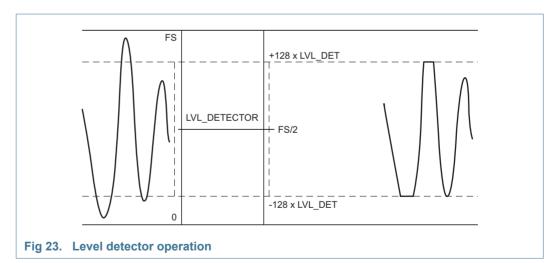

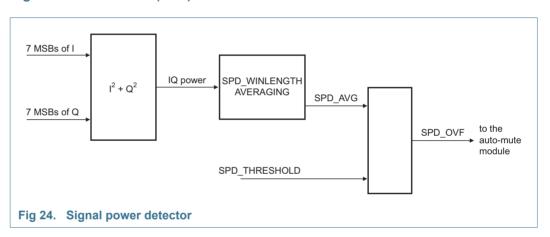

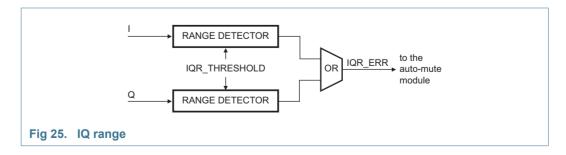

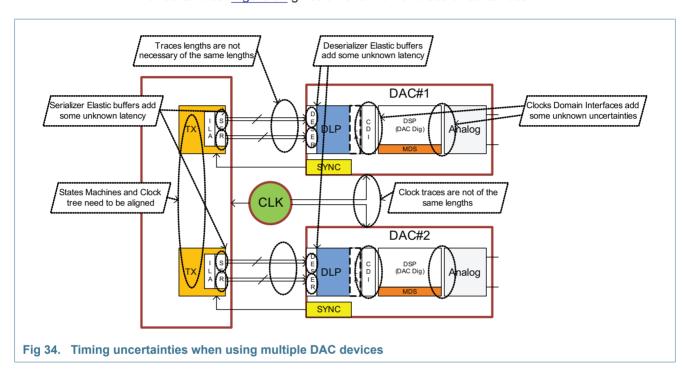

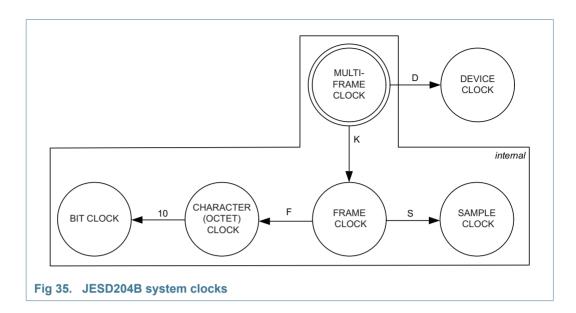

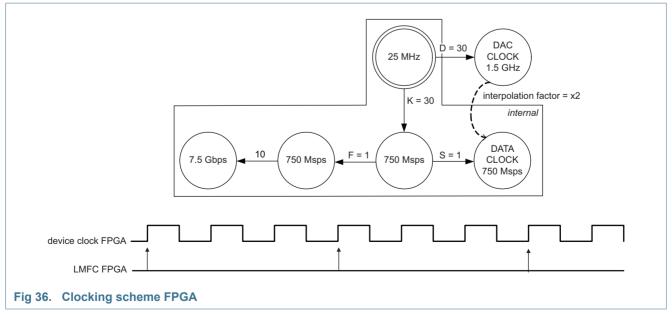

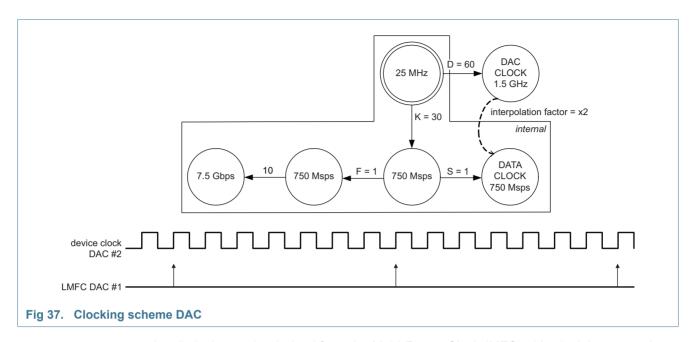

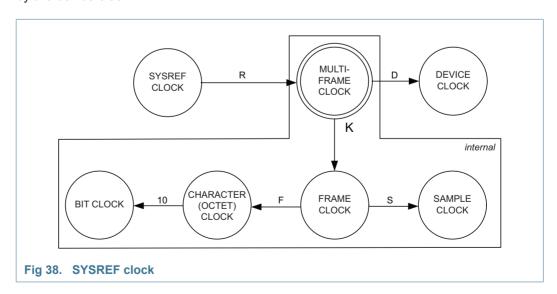

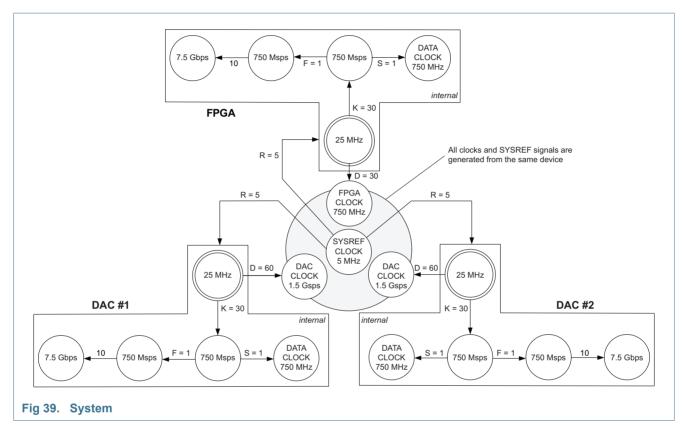

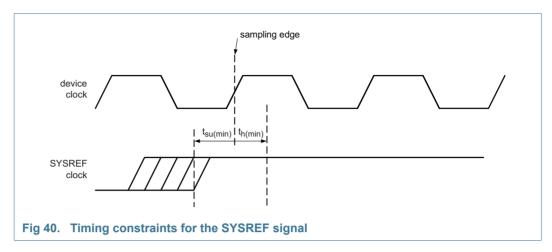

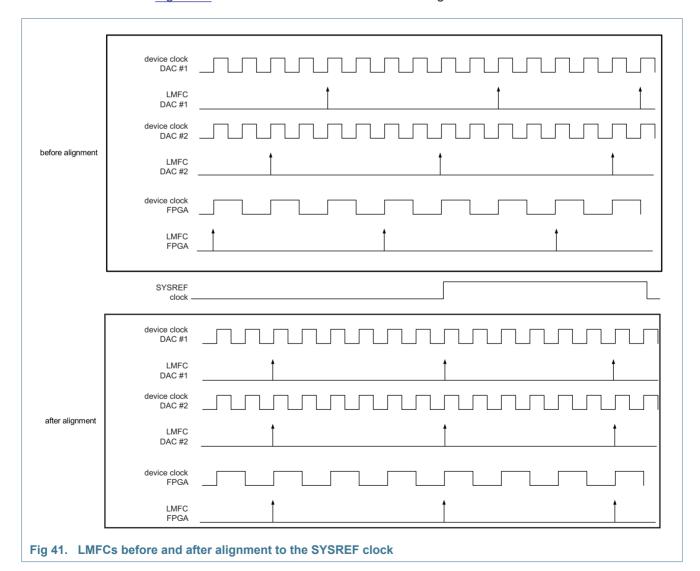

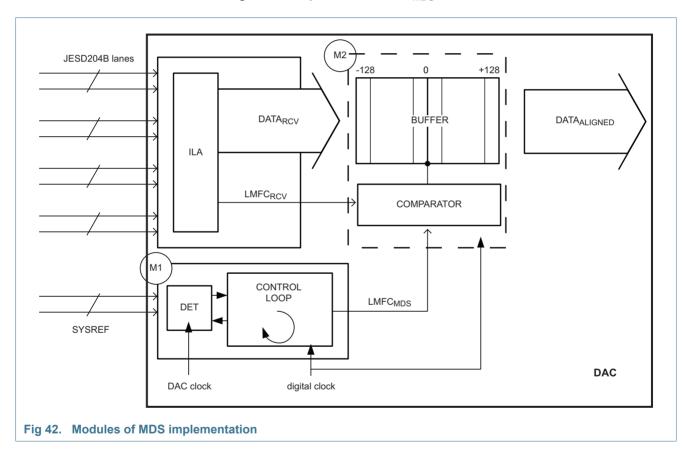

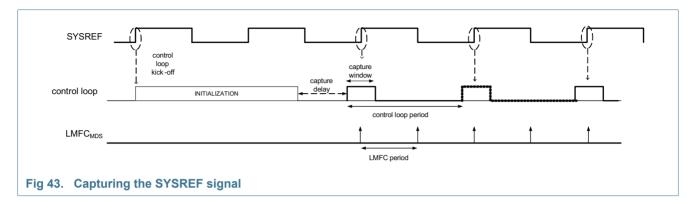

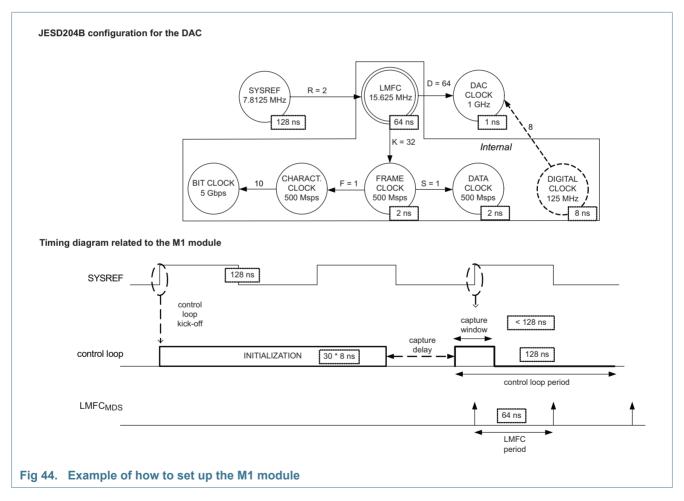

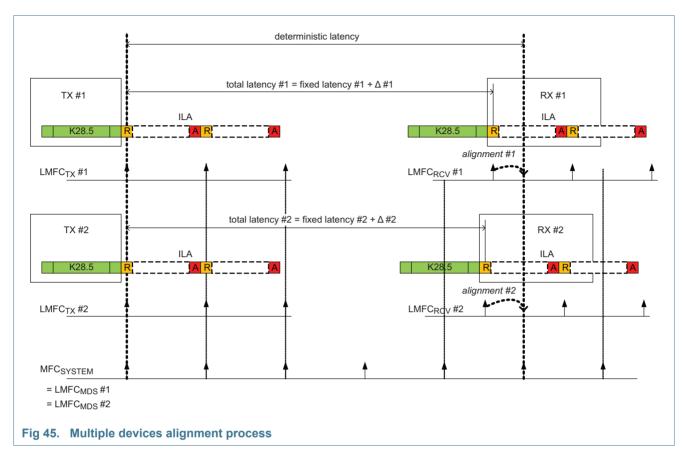

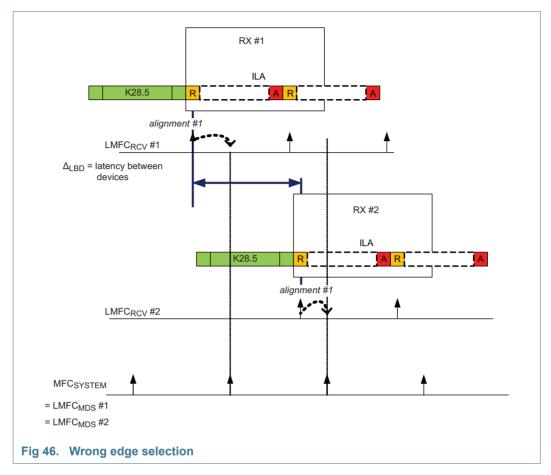

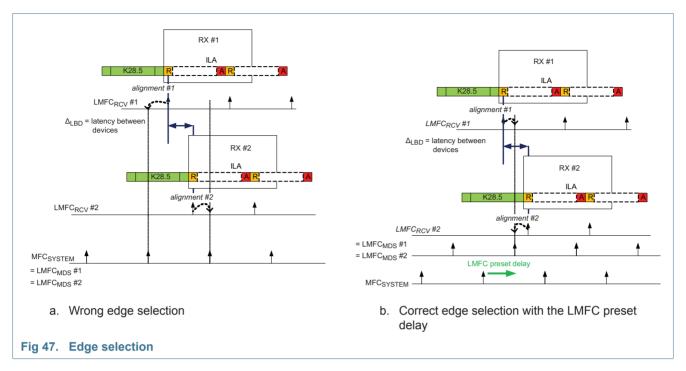

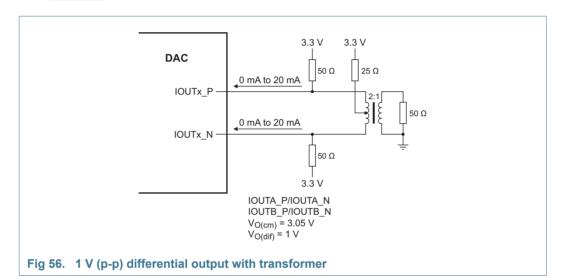

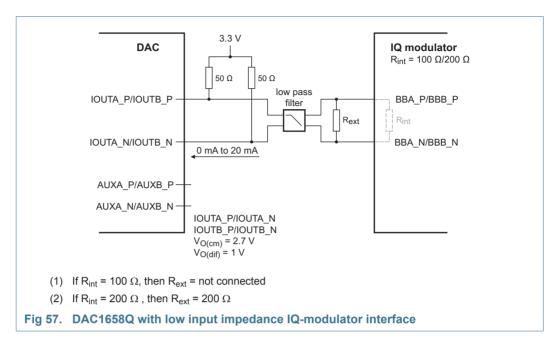

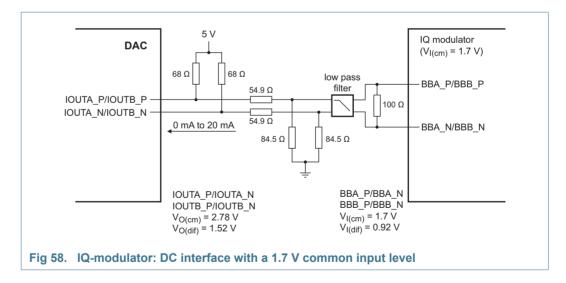

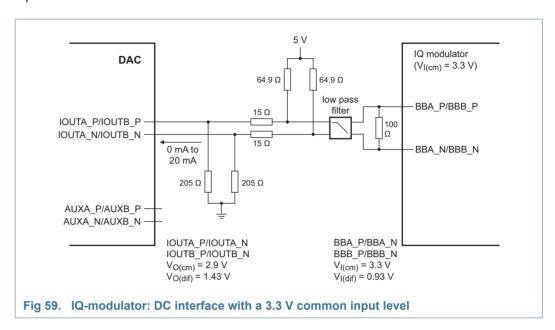

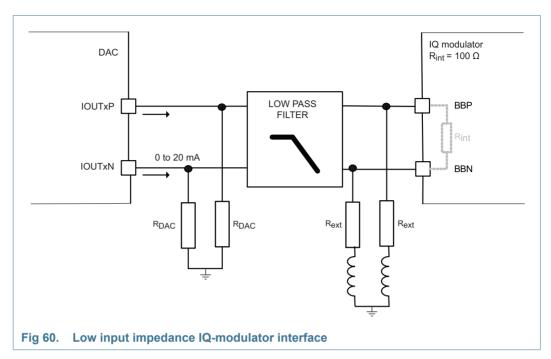

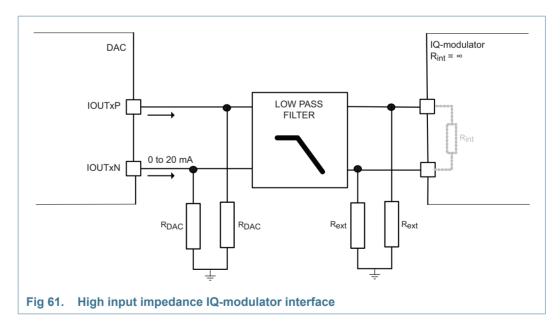

|                 | Lane CD0  | l <sub>CD0</sub> [15-8] | l <sub>CD1</sub> [15-8] | l <sub>CD2</sub> [15-8] |        | l <sub>CD0</sub> [15-8] | [CD0[7-0]                  | l <sub>CD2</sub> [15-8] |  | l <sub>CD0</sub> [15-8] | [CD0[7-0]              | l <sub>CD1</sub> [15-8] | l <sub>CD1</sub> [17-0] | l <sub>CD0</sub> [15-8] | [CD0[7-0] | Q <sub>CD0</sub> [15-8] | Q <sub>CD0</sub> [7-0] | _ |  |